2. Аналого-цифровой преобразователь ПОП.1, отличающийс я тем, что блок управления выполнен на шести одновибраторах, входы первого.третьего, четвертого и питого из которых объединены и являются входом блока управления, а выходы второго, третьего, четвертого и шестого одновибраторов являются соответственно первым, вторым, третьим и четвертым выходами блока управления, причем выходы первого и пятого одновибраторов соединены соответственно с входами второго и шесто го одновибраторов.

3. Аналого-цифровой преобразователь ПОП.1, отличающий с я тем, что кодирующий блок выполнен на сумматоре и резисторе, вход которого подк-пгочен к шине логической единицы, а выход - к первым входам сумматора, вторые входы которого являются входами кодирующего блока, вход переноса соединен с общей шиной, а выходы являются выходами кодирующего блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельно-последовательный аналого-цифровой преобразователь | 1981 |

|

SU1039025A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1984 |

|

SU1282326A1 |

| Способ следящего аналого-цифрового преобразования и устройство для его осуществления | 1983 |

|

SU1229954A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Устройство аналого-цифрового преобразования | 1988 |

|

SU1501268A2 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1193808A1 |

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1398093A1 |

| Устройство аналого-цифрового преобразования | 1987 |

|

SU1559405A2 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1202055A1 |

| Устройство для считывания графической информации | 1987 |

|

SU1506460A1 |

1. АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий блок выборки и запоминания, первый вход которого соединен с входной шиной, а выход подключен к первому входу формирователя разностного сигнала и первому входу первого цифрового амплитудного, анализатора, вторые входы которого соединены с соответствующими выходами первого блока опорных напряжений, а выходы через последовательно соединенные первый шифратор и блок памяти подключены к соответ.ствующим входам первого цифроаналогового преобразователя, выход которого соединен с вторым входом формирователя разностного сигнала, выход которого соединен с первым входом второго цифрового амплитудного айапизатора, вторые входы которого подключены к соответствующим выходам второго блока опорных напряжений, а выходы - к соответствующим входам второго шифратора, и блок управления, вход которого соединен с шиной управления, первый выход - с входом синхронизации блока памяти а второй выход - с вторым входом блока выборки и запоминания, отличающ и и с я тем, что, с целью повьш1е- НИН точности преобразования, в него введены второй и третий цифроаналоговые преобразователи, элемент ИСКЛЮЧА1аЦЕЕ ИЛИ, элемент 1ШИ-НЕ, управляемый генератор импульсов, счетчик импульсов, кодирующий блок и регистр памяти, при этом третий выход блока,, управления соединен с первым входом счетчика импульсов и с первым входом элемента tUTH-HE, а четветрый выход с входом синхронизации регистра памяти, выходы которого являются выходными шинами, входы младших разрядов соединены с соответствующими выходами второго шифратора, входы старших разрядов - с соответствую(Л щими выходами блока памяти, а входы старших разрядов объединены с соответствующими входами второго цифроаналогового преобразователя и подключены к соответствующим выходам кодирующего блока, входы которого обьединены с соответствующими входами третьего цифроаналогового преобразователя и подключены к соответствующим выходам счетчика импульсов, второй вход которого соединен с выходом управляемого генератора 4 4: импульсов, вход которого подключен к выходу элемента ИЛИ-НЕ, второй вход которого соединен с выходом элемента ИСЮПОЧАЩЕЕ 1ШИ, первый и второй входы которого соответственно подключены к выходам младших разрядов первого шифратора и блока памяти, причем выходы второго и третьего цифроаналоговых преобразователей соответственно соединены с входами второго и первого блоков опорных напряжений.

Изобретение относится к вычислительной и измерительной технике и . может быть использовано для преобразования аналоговых сигналов в цифровой код в аппаратуре автоматического контроля и-управления, например, в составе устройств ввода аналоговы сигналов-в ЭВМ.

Цель изобретения - повышение точности преобразования.

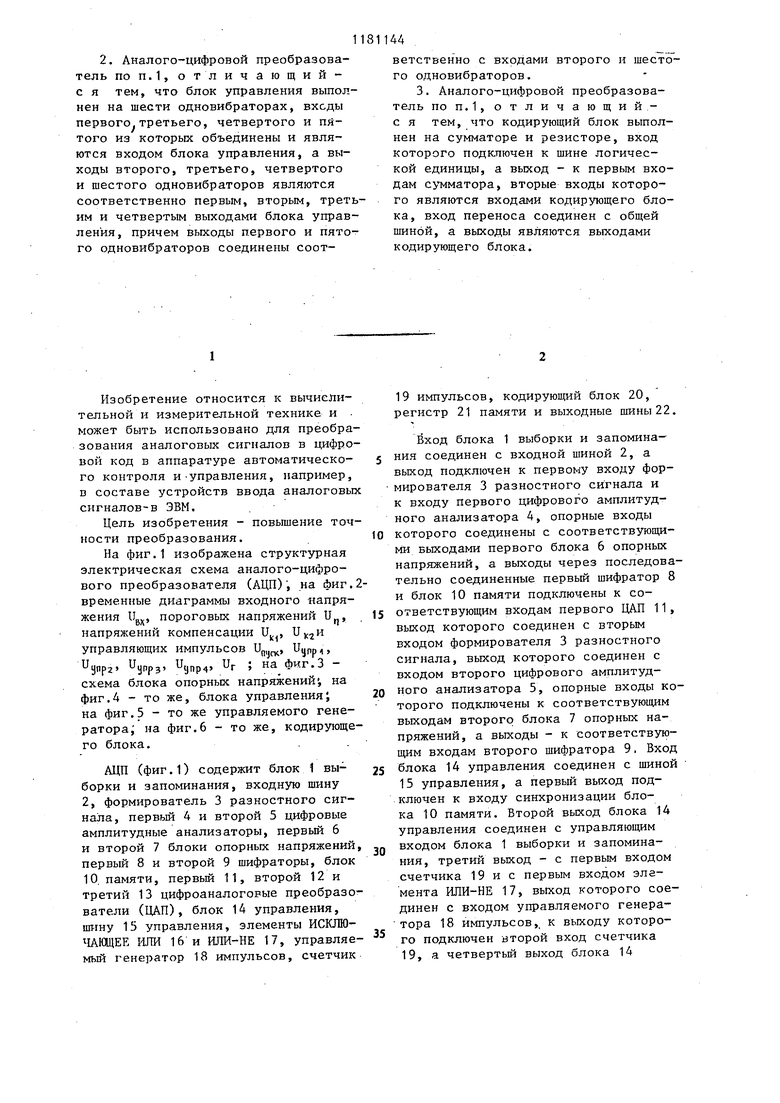

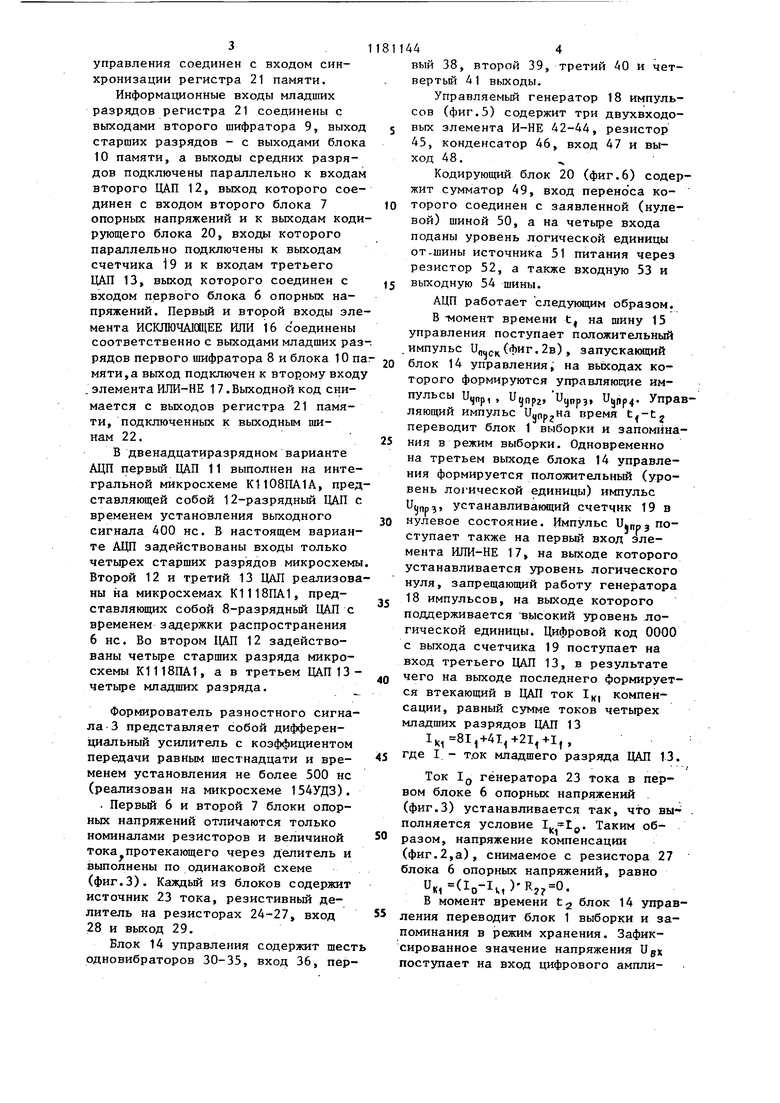

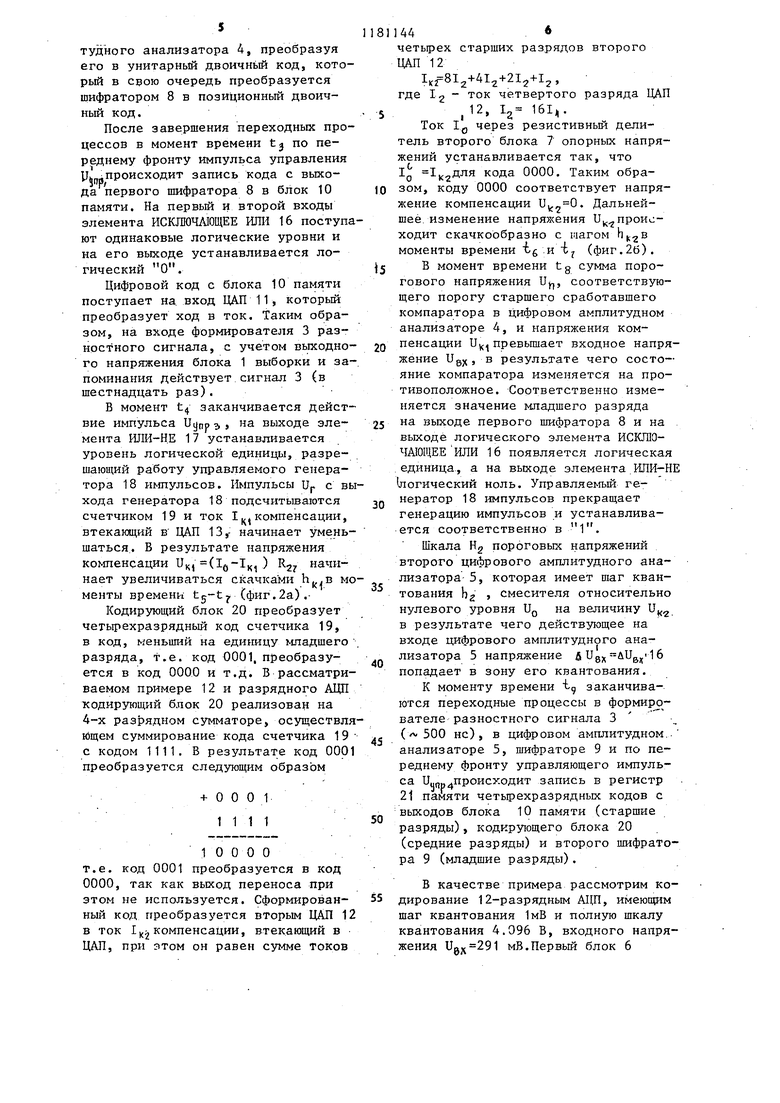

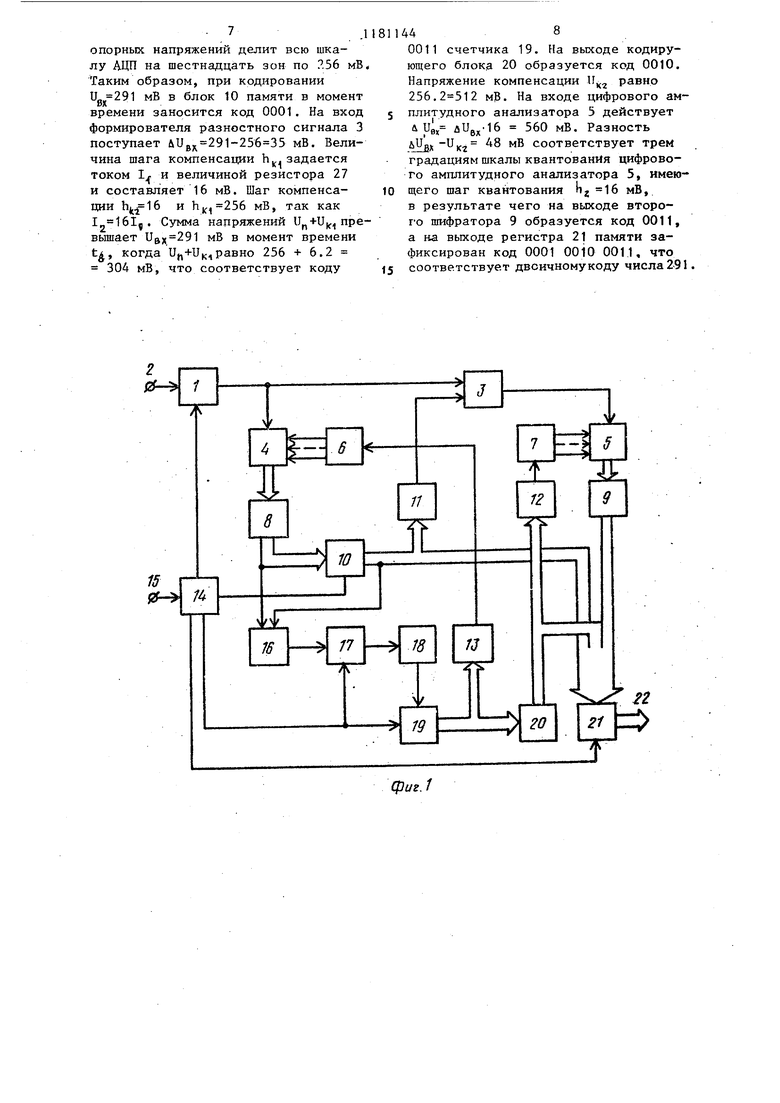

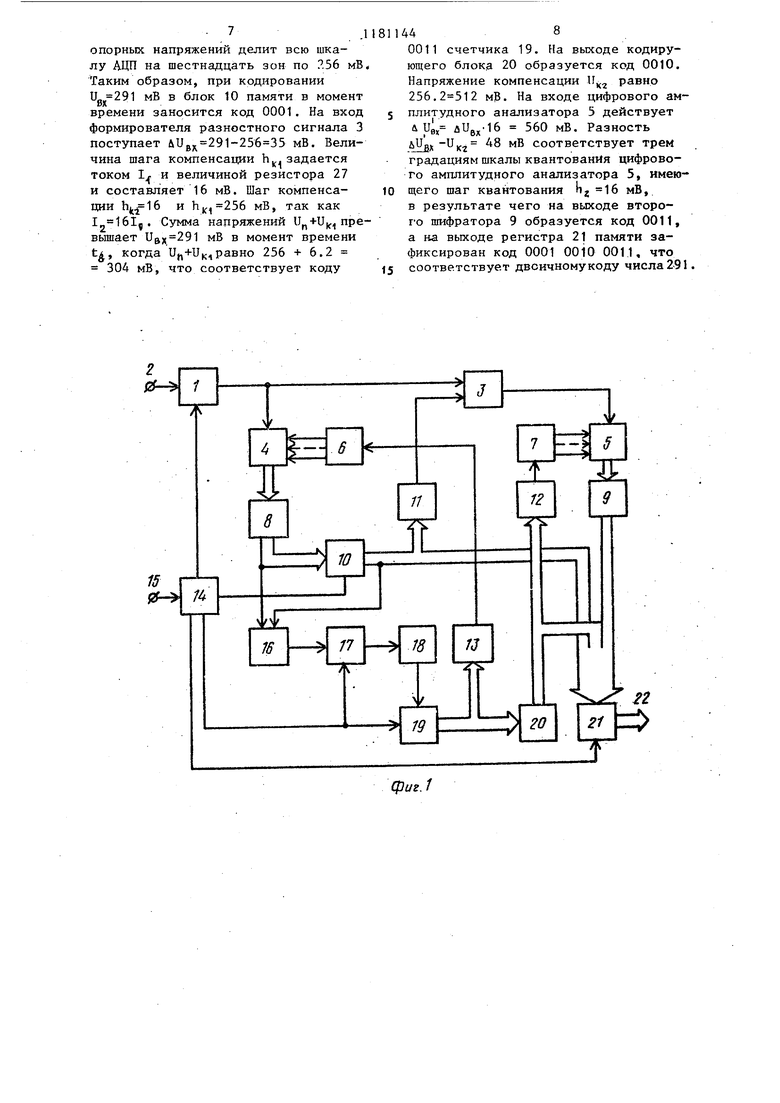

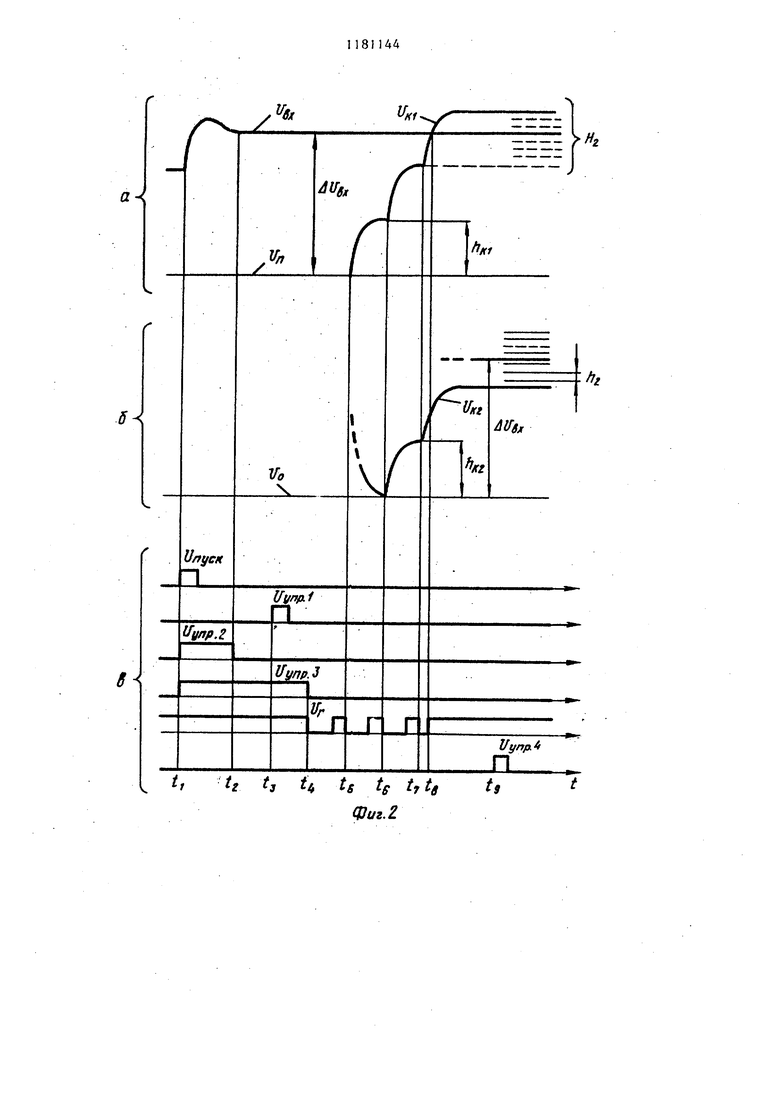

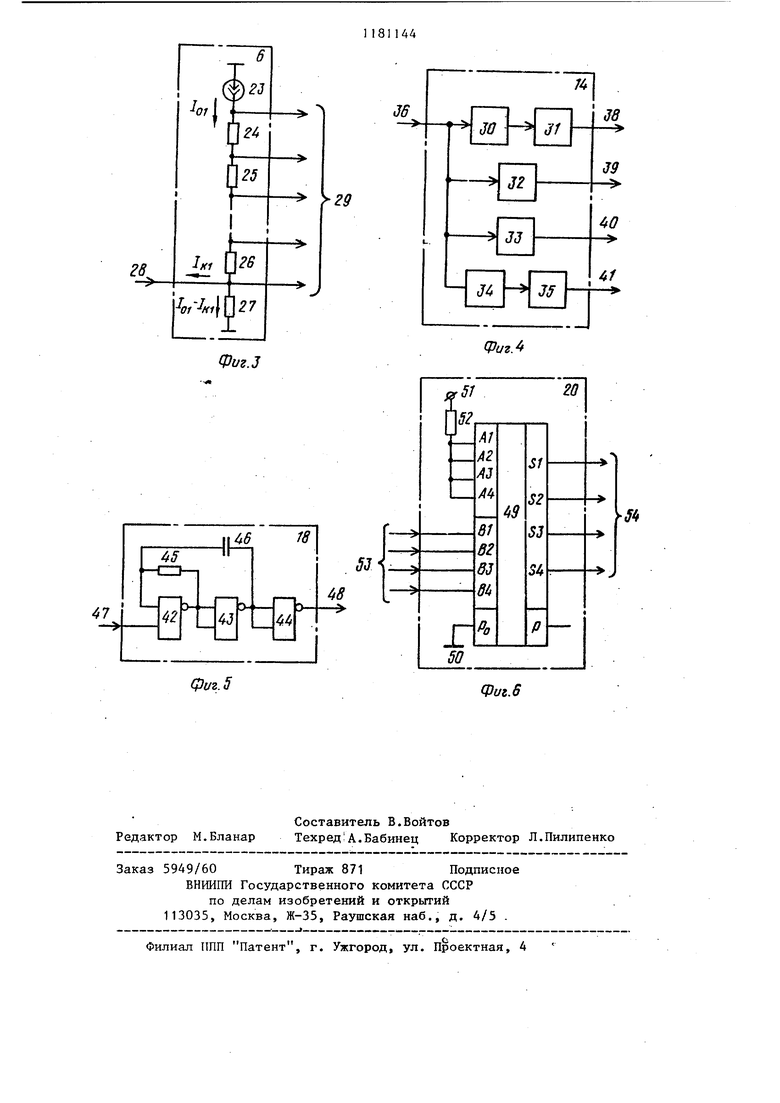

На фиг.1 изображена структурная злектрическая схема аналого-цифрового преобразователя (АЦП), на фиг.временные диаграммы входного напряжения Ugjj, пороговых напряжений U , напряжений компенсации U, , и,(и управляющих импульсов и„,, Uypp,, Uynpj, Uijppj, Uynp, Ur ; на фиг.З схема блока опорных напряжений; на фиг.4 - то же, блока управления на фиг.5 - то же управляемого генератора j на фиг.6 - то же, кодирующего блока.. .

АЦП (фиг.1) содержит блок 1 выборки и запоминания, входную шину 2, формирователь 3 разностного сигнала, первьш 4 и второй 5 цифровые амплитудные анализаторы, первый 6 и второй 7 блоки опорных напряжений первый 8 и второй 9 шифраторы, блок 10. памяти, первый 11, второй 12 и третий 13 цифроаналогорые преобразователи (ЦАП), блок 14 управления, шину 15 управления, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 16 и ИЛИ-НЕ 17, управляемьш генератор 18 импульсов, счетчик

19 импульсов, кодирующий блок 20, регистр 21 памяти и выходные шины 22.

Вход блока 1 выборки и запоминания соединен с входной шиной 2, а выход подключен к первому входу формирователя 3 разностного сигнала и к входу первого цифрового амплитудного анализатора 4, опорные входы которого соединены с соответствующими выходами первого блока 6 опорных напряжений, а выходы через последовательно соединенные первый шифратор В и блок 10 памяти подключены к соответствующим входам первого ЦАП 11, выход которого соединен с вторым входом формирователя 3 разностного сигнала, выход которого соединен с входом второго цифрового амплитудного анализатора 5, опорные входы которого подключены к соответствующим выходам второго блока 7 опорных напряжений, а выходы - к соответствующим входам второго шифратора 9. Вход блока 14 управления соединен с шиной 15 управления, а первый выход подключен к входу синхронизации блока 10 памяти. Второй выход блока 14 управления соединен с управляющим входом блока 1 выборки и запоминания, третий выход - с первым входом счетчика 19 и с первым входом элемента ИЛИ-НЕ 17, выход которого соединен с входом управляемого генератора 18 импульсов,, к выходу которого подключен второй вход счетчика 19, а четвертый выход блока 14

3

управления соединен с входом синхронизации регистра 21 памяти.

Информационные входы младигих разрядов регистра 21 соединены с выходами второго шифратора 9, выход старших разрядов - с выходами блока 10 памяти, а выходы средних разрядов подключены параллельно к входам второго ЦАП 12, выход которого соединен с входом второго блока 7 опорных напряжений и к выходам кодирующего блока 20, входы которого параллельно подключены к выходам счетчика 19 и к входам третьего ЦАП 13, выход которого соединен с входом первого блока б опорных напряжений. Первый и второй входы элемента ИСКЛЮЧА10И1ЕЕ ИЛИ 16 Соединены соответственно с выходами младших раз рядов первого шифратора 8 и блока 10 па мяти,а выход подключен к второму входу . элемента ИЛИ-НЕ 1 7. Выходной код снимается с выходов регистра 21 памяти, подключенных к выходным шинам 22.

В двенадцатиразрядном варианте АЦП первый ЦАП 11 выполнен на интегральной микросхеме К1108ПА1А, представляющей собой 12-разрядный ЦАП с временем установления выходного сигнала 400 не. В настоящем варианте АЦП задействованы входы только четырех старших разрядов микросхемы Второй 12 и третий 13 ЦАП реализованы на микросхемах К1118ПА1, представляющих собой 8-разрядный ЦАП с временем задержки распространения 6 НС. Во втором ЦАП 12 задействованы четьфе старших разряда микросхемы К1118ПА1, а в третьем ЦАП 13четьфе мпадших разряда.

Формирователь разностного сигнала 3 представляет собой дифференциальный усилитель с коэффициентом передачи равным шестнадцати и временем установления не более 500 не (реализован на микросхеме 154УДЗ). . Первый 6 и второй 7 блоки опорных напряжений отличаются только номиналами резисторов и величиной тока протекающего через делитель и выполнены по одинаковой схеме (фиг.З). Калщьй из блоков содержит источник 23 тока, резистивный делитель на резисторах 24-27, вход 28 и выход 29.

Блок 14 управления содержит шест одновибраторов 30-35, вход 36, пер11444

вый 38, второй 39, третий 40 и четвертый 41 выходы.

Управляемый генератор 18 импульсов (фиг.5) содержит три двухвходо5 вых элемента И-НЕ 42-44, резистор 45, конденсатор 46, вход 47 и выход 48.

Кодирующий блок 20 (фиг.6) содержит сумматор 49, вход переноса которого соединен с заявленной (нулевой) шиной 50, а на четьфе входа поданы уровень логической единицы от-шины источника 51 питания через резистор 52, а также входную 53 и 15 выходную 54 шины.

АЦП работает следующим образом. В -момент времени t, на шину 15 управления поступает положительный импульс и„и (фиг. 2в), запускающий 20 блок 14 управленияj на вькодах которого формируются управляющие импульсы и,пр,, ицпрг,иупрз, U,jnp4. Управляющий импульс время переводит блок 1 выборки и запомйна25 ния в режим выборки. Одновременно на третьем выходе блока 14 управления формируется положительный (уровень ло1ической единицы) импульс Uqnp, устанавливающий счетчик 19 в 30 нулевое состояние. Импульс О ступает также на первый вход элемента ИЛИ-НЕ 17, на выходе которого устанавливается уровень логического нуля, запрещающий работу генератора c 18 импульсов, на выходе которого поддерживается высокий уровень логической единицы. Цифровой код 0000 с выхода счетчика 19 поступает на вход третьего ЦАП 13, в результате Q чего на выходе последнего формируется втекающий в ЦАП ток 1,1 компенсации, равный сумме токов четьфех младших разрядов ЦАП 13

Ток IQ генератора 23 тока в первом блоке 6 опорных напряжений (фиг.З) устанавливается так, что вы .

полняется условие . Таким образом, напряжение компенсации

(фиг.2,а), снимаемое с резистора 27 блока 6 опорных напряжений, равно

ик,(1о-1л,).

В момент времени t блок 14 управления переводит блок 1 выборки и запоминания в режим хранения. Зафиксированное значение напряжения Ugx поступает на вход цифрового амплитудного анализатора 4, преобразуя его в унитарный двоичньй код, который в свою очередь преобразуется шифратором 8 в позиционный двоичный код.

После завершения переходных процессов в момент времени tj по переднему фронту импульса управления Р дпроисходит запись кода с выхода первого шифратора 8 в блок 10 памяти. На первьй и второй входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 16 поступают одинаковые логические уровни и на его выходе устанавливается логический О.

Цифровой код с блока 10 памяти поступает на. вход ЦАП 11 , который преобразует ход в ток. Таким образом, на входе формирователя 3 разностного сигнала, с учетом выходного напряжения блока 1 выборки и запоминания действует сигнал 3 (в шестнадцать раз).

В момент t заканчивается действие импульса Uijnp ъ на выходе элемента ИЛИ-НЕ 17 устанавливается уровень логической единицы, разрешающий работу управляемого генератора 18 импульсов. Импульсы и с выхода генератора 18 подсчитываются счетчиком 19 и ток 1 компенсации, втекающий в ЦАП 13,- начинает уменьшаться. В результате напряжения компенсации Уц, ( ) начинает увеличиваться скачками Ь.в моменты времени tj-t (фиг.2а) .

Кодирующий блок 20 преобразует четырехразрядный код счетчика 19, в код, меньший на единицу младшего разряда, т.е. код 0001, преобразуется в код 0000 и т.д. В рассматриваемом примере 12 и разрядного АЦП кодирующий блок 20 реализован на 4-х разрядном сумматоре, осуществляющем суммирование кода счетчика 19 с кодом 1111. В результате код 0001 преобразуется следующим образом

+ 0001 1111

10000

т.е. код 0001 преобразуется в код 0000, так как выход переноса при этом не используется. Сформированный код преобразуется вторым ЦАП 12 в ток 1, компенсации, втекающий в ЦАП, при этом он равен сумме токов

81144

четырех старших разрядов второго ДАП 12

I,8l2+4l2+2l2+l2,

где Ij четвертого разряда ЦАП 5 ,12, 12 161,.

Ток Ig через резистивный делитель второго блока 7 опорных напряжений устанавливается так, что I 1 для кода 0000. Таким образом, коду 0000 соответствует напряжение компенсации U, 0. Дальнейшее изменение напряжения U происходит скачкообразно с шагом ,ъ моменты времени t .и t (фиг.2б).

5 В момент времени tg сумма порогового напряжения U, соответствующего порогу старшего сработавшего компаратора в цифровом амплитудном анализаторе 4, и напряжения компенсации U превьш1ает входное напряжение Ug, в результате чего состояние компаратора изменяется на противоположное. Соответственно изменяется значение младшего разряда

5 на выходе первого шифратора 8 и на выходе логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 16 появляется логическая единица, а на выходе элемента ИЛИ-НЕ (логический ноль. Управляемьй генератор 18 импульсов прекращает генерацию импульсов и устанавливается соответственно в 1.

Шкала Hg пороговых напряжений второго цифрового амплитудного анализатора- 5, которая имеет шаг квантования hg , смесителя относительно нулевого уровня UQ на величину . в результате чего действующее на входе цифрового амплитудного анализатора 5 напряжение fi Ug попадает в зону его квантования.

К моменту времени tg заканчиваются переходные процессы в формирователе разностного сигнала 3 (л, 500 не), в цифровом амплитудном.. анализаторе 5, шифраторе 9 и по переднему фронту управляющего импульса UUPP происходит запись в регистр 21 памяти четырехразрядных кодов с

выходов блока 10 памяти (старшие разряды), кодирз ощего блока 20 (средние разряды) и второго шифратора 9 (младшие разряды).

В качестве примера рассмотрим кодирование 12-разрядным АЦП, имеющим шаг квантования 1мВ и полную шкалу квантования 4.096 В, входного напряжения мВ.Первый блок 6 опорных напряжений делит всю шкалу АЦП на шестнадцать зон по -56 мВ Таким образом, при кодировании UBX мВ в блок 10 памяти в момент времени заносится код 0001. На вход формирователя разностного сигнала 3 поступает ли 291-256 35 мВ. Величина шага компенсации h.. задается IC1 током 1 и величиной резистора 27 и составляет 16 мВ. Шаг компенсации и h,, 256 мВ, так как I2 16I« Сумма напряжений , превышает мВ в момент времени t, когда ,равно 256 + 6.2 304 мВ, что соответствует коду .1

фиг.1 48 0011 счетчика 19. На выходе кодирующего блока 20 образуется код 0010. Напряжение компенсации U равно 256, мВ. На входе цифрового амплитудного анализатора 5 действует U Ue, aUgj(16 560 мВ. Разность gx кг мВ соответствует трем градациям шкалы квантования цифрового амплитудного анализатора 5, имеющего шаг квантования g в мВ, в результате чего на выходе второго щифратора 9 образуется код 0011, а на выходе регистра 21 памяти зафиксирован код 0001 0010 0011, что соответствует двоичному коду числа 291.

ЙГ

а-

б

f

t ts tg tftf Фиг.2

Фиг.З

/2.1

Фиг.б

| Шило В.Л | |||

| Линейные интегральные схемы в радиоэлектронной аппаратуре | |||

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Телефонная трансляция с местной цепью для уничтожения обратного действия микрофона | 1924 |

|

SU348A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1981 |

|

SU1039025A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-09-23—Публикация

1983-12-27—Подача