Изобретение относится к электротехнике и может быть использовано в качестве измерительных органов наррабленных и дистанционных зап(ит.

Известны устройства для сравнення фаз электрических величин, реагирующие на продолжите льность импульсов совпадения и несовпадения сравниваемых величин и времени совпадения с оставшимся временем полупериода.СииГ2Т.

Наиболее близким по технической сущности к предлагаемому устройству является реле направления мощности. нулевой последовательности с регулируемыми уставками i по току и напряжению 3 содержащее усилителиограничители, селективные фильтры, двухполярные пороговые элементы, элемент совпадения, интегратор и триггер (выходной пороговый элемент).

.Достоинством органа направления Мощности является достаточно высокое быстродействие при больших кратностя входных величин, практическая независимость от частоты сети его ха- . рактеристик и высокая помехоустойчивость. Недостатком является значительная зависимость времени срабатывания от фазового сдвига и кратности входных сигналов.

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для сравнения электрических величин по фазе, содержащее формирователи прямоугольных имЛульсов из сравниваемых величин, подключенные выходами ко входам элемента фиксации совпадения знаков Сравниваемых величин, интегратор, два .пороговых элемента и выходной орган, дополнительно введены два формирователя Импульсов, элемент фик Сации несовпадения знаков сравниваемых величин,два расширителя импульсов,сумматор, два логических элемента НЕ,два логических элемента И,интегратор и логический элемент ИЛИ, при этом выходы формирователей прямоугольных импульсов из сравниваемых величин подключены ко входам элемента фиксации несовпадения знаков сравниваемых величин, а также ко входам вновь введенных формирователей импульсов, выход каждого из которых подключен ко входам соответствующих логи еского элемента НЕ, расширителя импульсов и интегратора.

выход -которого через соответствующий пороговый элемент подключен к одному из входов соответствующего логического элемента И, к другим входам кото.рого подключены выходы указанных логического элемента НЕ и расширителя импульсов, подключенного выходом также к другому входу указанного интегратора, к третьему входу которого подключен выход сумматора, подключенного входами к выходам элементов фиксации совпадения и несовпадения знаков сравниваемых величин, а выходы логических элеме-нтов И подключены ко входам логического элемента ИЛИ, на выходе которого включен выходной орган..

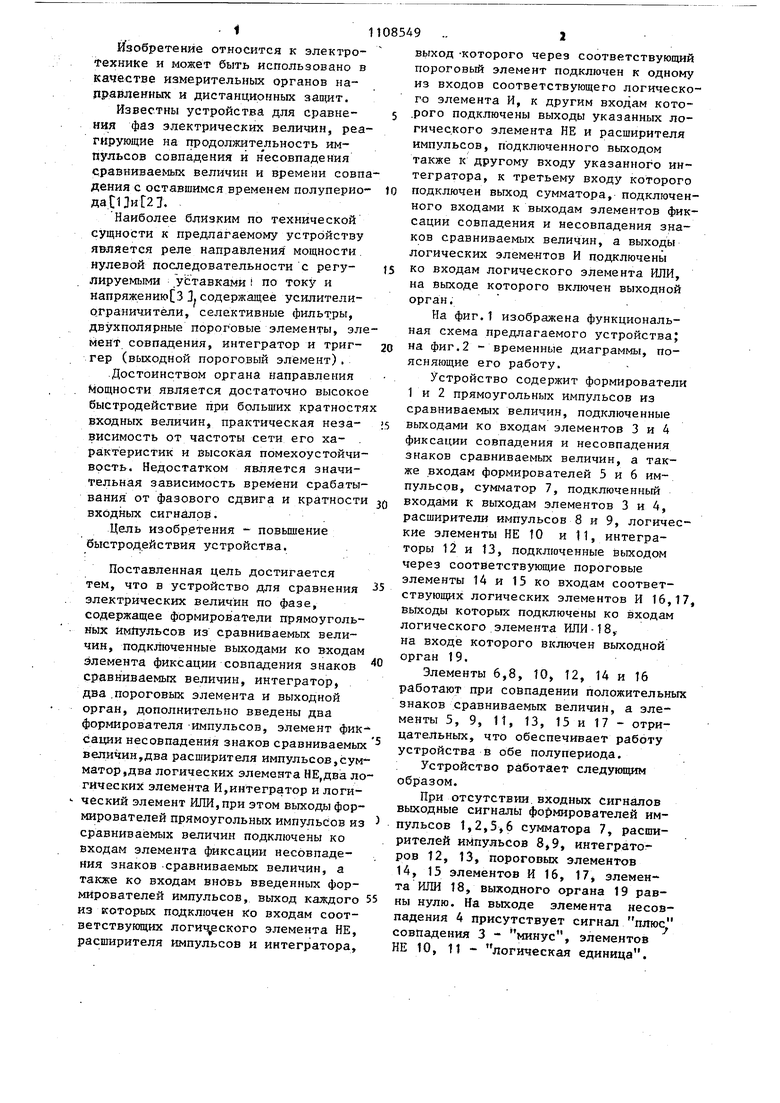

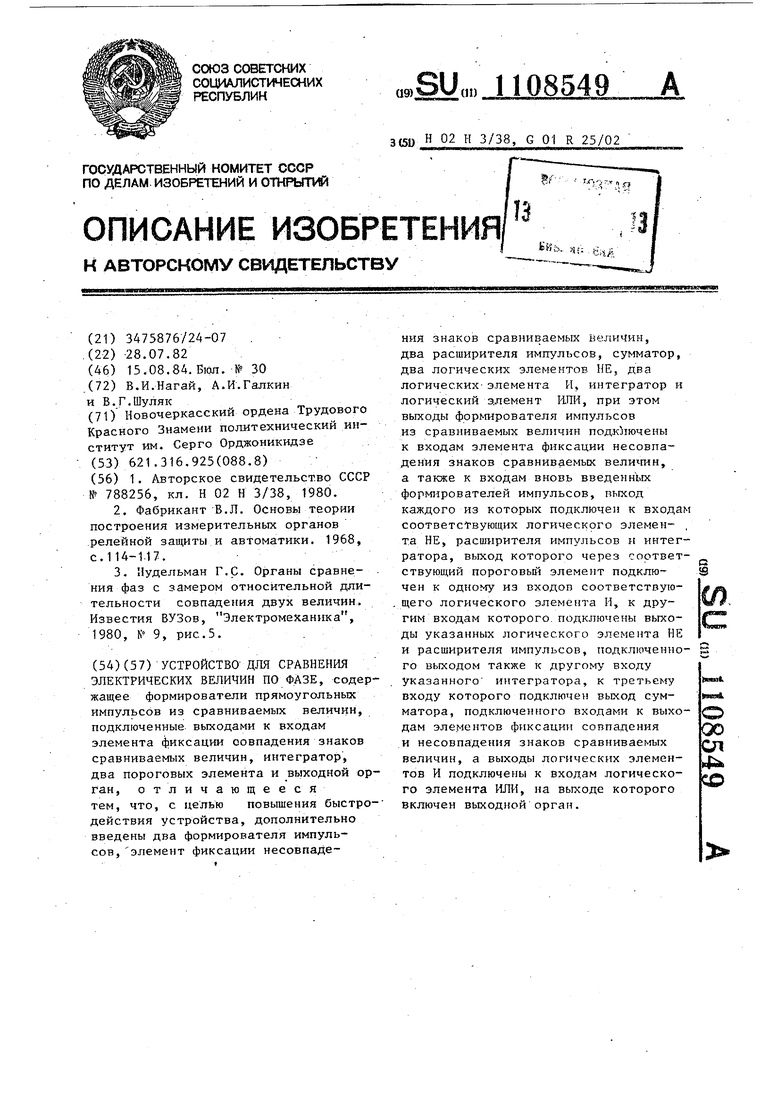

На фиг.1 изображена функциональная схема предлагаемого устройства; на фиг.2 - временные диаграммы, поясняющие его работу.

Устройство содержит формирователи 1 и 2 прямоугольных импульсов из сравниваемых величин, подключенные выходами ко входам элементов 3 и 4 фиксации совпадения и несовпадения знаков сравниваемых величин, а также входам формирователей 5 и 6 импульсов, сумматор 7, подключенный входами к выходам элементов 3 и 4, расширители импульсов 8 и 9, логические элементы НЕ tO и 11, интеграторы 12 и 13, подключенные 1выходом через соответствующие пороговые элементы 14 и 15 ко входам соответствующих логических элементов И 16,1 вьгходы которых подключены ко входам логического элемента ИЛИ -18,. на входе которого включен выходной орган 19.

Элементы 6,8, tO 12, 14 и 16 работают при совпадении положительны знаков сравниваемых величин, а элементы 5, 9, 11, 13, 15 и 17- отрицательных, что обеспечивает работу устройства в обе полупериода. ; Устройство работает следующим образом.

При отсутствии.входных сигналов выходные сигналы фо5 мирователей импульсов 1,2,5,6 сумматора 7, расширителей импульсов 8,9, интеграторов 12, 13, пороговых элементов 14, 15 элементов И 16, 17, элемента ИЛИ 18, выходного органа 19 равны нулю. На вьгходе элемента несовпадения 4 присутствует сигнал плюс совпадения 3 - минус, элементов НЕ 10, 11 - логическая единица. При подаче входных сигналов и пре вышении ими уровня формирования формируются прямоугольные импульсы, которые поступают на вкоды элементов совпадения 3 и несовпадения 4. При совпадении знаков формируамьпс импульсов не выходе элемента совпаде ния 3 появляется плюс, при несовпа дений знаков на выходе элемента несо падения 4 - минус. С выходов элементов 3 и 4 сигналы поступают на вход -сумматора 7, выходной сигнал которого отличен от нуля только в моменты совпадения или несовпадения знаков сравниваемых величин, причем в моменты Совпадения знаков на выход сумматора 7 появляется сигнал плюс а в моменты несовпадения - минус. Формирователи импульсов 5,6 формируют импульсы согласно алгоритму u, u;u.(unuj)u,, и,.и;и-.(и;.и-|и,. Uj - выходные сигналы форгде и и мирователей импульсов 1 и 2 положительной полярности; J тл и - Соответственно отрицательной полярности, и и и - выходные сигналы формирователей импульсов 5,6. Сигналы Uc и и, появляются тольк ь ь при совпадении полярностей сигналов Ц и (j , а их длительности равны длительности существования одного из импульсов г или и/ (длительности того импульса, который появляется позже). Расширители импульсов 8 и 9 расширяют соответственно импульсы и и и/ , что обеспечивает совместно С импульсами формирователей 5 и 6 пуск интеграторов 12 и 13. Сброс интеграторов 12 и 13 в исходное состоя ние (нулевое) происходит по окончаНИИ импульсов Ug и Ug . Работа устройства при иивх-, и 8X2 - ясняется временными диаграммами на фиг.2 а . При превышении Ug уровня формируются импульсы формирователей 1 и 2, при совпадении .знаков которых на выходе элемента совпадения 3 поплюс, а в оставшееся вреявляется элемента несовпадения мя - минус в моменты несовпадения знаков .сравниваемых величин - минус, а в оставшееся время - плюс. В момент tj формируются импульсы Ug и Ug что обеспечивает разрешение работы интегратору 12. ;С.момента tj до момента 4 идет заряд интегратора 12, с t Д° 5 (т.е. в паузу) состояние интеграторов остается неизменным с -t 5 до rt происходит разряд, а с t, до V состояние интегратора нецзменио. Н момент t происходит разряд (с малой постоянной времени) интегратора 12 из-за исчезновения импульса Ug и таким образом интегратор 12 подготавливается к следующему циклу работы. В промежутке времени tf.-t разрешено считывание состояние первого порогового элемента 14, так как с момента i на выхо-де элемента НЕ 10 появляется сигнал . логическая единица и на выходе расширителя 8 в данный момент сигнал равен логической единице. В данном случае выходной сигнал интегратора 12 превышает уровень срабатывания порогового элемента 14, что приводит к его срабатыванию. В момент выходе элементов И 16 и ИЛИ 18 появляется сигнал логическая единшда и устройство срабатывает. На фиг.2Б показана работа устройства при 90 Ч f; 180°. В данном случае напряжение интеграторов 12 и 13 на момент разрешения Считывания состояния пороговых элементов 14 и 15 оказывается отрицательным (т.е. ниже уровня срабатывания) и, следовательно, ройство не срабатывает. Анализ временных диаграмм работы устройства показывает, что устройство срабатывает в первый или второй полупериод после подачи входных сигналов, т.е. время срабатывания не превышает периода промьшшенной частоты. Таким образом, введение дополнительных элементов в их взаимосвязи позволяет уменьшить время срабатывания по сравнению с прототипом до периода промышленной частоты за счет сравнения времени совпадения с временем несовпадения в каждый полупериод, вьтолнить устройство, работа которого полностью не зависит от частоты сети, обеспечить его быструю переориентацию (не более ЛОЛУ периода) при изменении фазы входных величин, а также практически не зависящее от кратности и фазы входных сигналов время срабатывания.

Использование предлагаемого устройства при вьтолнении измерительных pprattoB защит элементов электрических систем позволяет повысить их быстродействие, что снижает вероятность возникновения аварий.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения фаз двух электрических величин | 1983 |

|

SU1150695A1 |

| Реле сопротивления | 1978 |

|

SU736256A1 |

| Устройство для защиты от замыкания фазы на землю в сети переменного тока | 1981 |

|

SU957336A1 |

| Устройство контроля комбинационных составляющих сигнала нелинейного четырехполюсника | 1985 |

|

SU1264111A1 |

| УСТРОЙСТВО ДЛЯ ЦЕНТРАЛИЗОВАННОЙ НАПРАВЛЕННОЙ ЗАЩИТЫ ОТ ЗАМЫКАНИЙ НА ЗЕМЛЮ | 1994 |

|

RU2071624C1 |

| Устройство для защиты сборных шин электрических станций и подстанций | 1982 |

|

SU1019539A1 |

| Орган контроля синхронизма при автоматическом повторном включении линии электропередачи | 1980 |

|

SU928495A1 |

| Реле сопротивления | 1977 |

|

SU729724A1 |

| Устройство для сравнения фаз двух электрических величин | 1977 |

|

SU957341A1 |

| Устройство для защиты силового трансформатора | 1987 |

|

SU1525798A1 |

УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ЭЛЕКТРИЧЕСКИХ ВЕЛИЧИН ЛО ФАЗЕ, содержащее формирователи прямоугольных импульсов из сравниваемых величин, подключенные выходами к входам элемента фиксации совпадения знаков сравниваемых величин, интегратор, два пороговых элемента и выходной орган, отличающееся тем, что, с целью повышения быстродействия устройства, дополнительно введены два формирователя импульсов, элемент фиксации несовпадения знаков сравниваемых величин, два расширителя импульсов, суьтатор, два логических элементов НЕ, два логических- элемента И, интегратор и логический э.лемент 1-1ПИ, при этом выходы формирователя импульсов из сравниваемых величин подключены к входам элемента фиксации несовпадения знаков сравниваемых вели1шн, а также к входам вновь введенньгх формирователей импульсов, выход каждого из которых подключен к входам соответствующих логическрго элемента НЕ, расширителя импульсов и интегратора, выход которого через соответi ствующий пороговый элемент подключен к одному из входов соответствующего логического элемента И, к другим входам которого, подключены выходы указанных логического элемента НЕ и расширителя импульсов, подключенного выходом также к дpyгo т входу iKtnl указанного интегратора, к третьему входу которого подключен выход сумматора, подключенного входами к выходам эле.ментов фиксации совпадения 00 и несовпадения знаков сравниваемых ел 4ia величин, а выходы логических элементов И подключены к входам логическо D го элемента ИЛИ, на выходе которого включен выходной орган.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сравнения фаз двух электрических величин | 1979 |

|

SU788256A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Основы теории построения измерительных органов релейной защиты и автоматики | |||

| Приспособление для контроля движения | 1921 |

|

SU1968A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Органы сравнения фаз с замером относительной длительности совпадения двух величин | |||

| Известия ВУЗов, Электромеханика, 1980, К 9, рис.5 | |||

| . | |||

Авторы

Даты

1984-08-15—Публикация

1982-07-28—Подача