1

Изобретение относится к электротехнике и может быть использовано для построения реле направления мощности, реле сопротивления и ряда других фазосравнивающих устройств.

Известны устройства сравнения фаз, основанные на определении длительности временных интервалов 1.

Они могут быть выделены в две основные группы: устройства, в которых содержится время-измерительный элемент для сравнения длительности временных интерва- ю лов (обычно интервалов совпадения знаков двух сравниваемых величин) с заданной длительностью устройства, в которых содержится время-измерительный элемент для сравнения длительности одних временных интервалов с длительностью других ин- 5 тервалов (обычно для сравнения времени совпадения знаков двух сравниваемых величин с временем их несовпадения) 3.

Устройства первой группы имеют низкую 2о помехоустойчивость и в настоящее время

находят применение, как правило, лишь в сочетании с частотно-избирательными фильтрами в преобразующей части реле.

Устройства второй группы, напротив, в последнее время все шире внедряются в практику релейной защиты.

Указанные устройства содержат блоки совпадения сравниваемых величин, интеграторы в качестве время-измерительных элементов, исполнительные органы, например в виде триггера Шмитта 4.

Наиболее близким по технической сущности к предлагаемому является устройство для сравнения фаз, относящееся ко второй группе, оно удачно сочетает в себе достоинства реле в которых осуществляется сравнение времени совпадения знаков электрических величин с временем их несовпадения с достоинствами реле двойного сравнения фаз 5.

Недостатком этого устройства для сравнения фаз является то, что время срабатывания реле, выполненного на его основе достаточно велико, хотя оно и меньще, чем у существовавших ранее устройств сравнения фаз.

Цель изобретения - повышение быстродействия устройства.

Указанная цель достигается тем, что устройство для сравнения фаз двух электрических величин, содержащее блок совпадения положительных знаков сравниваемых величин, рабочий выход которого подключен к входу заряда одного интегратора, выход которого через ограничитель напряжения подключен к одному входу сумматора, блок совпадения отрицательных знаков сравниваемых величин, рабочий выход которого подключен к входу заряда другого интегратора, выход которого через другой ограничитель напряжения подключен к второму входу сумматора, на выходе которого включен исполнительный орган, дополнительно введены два блока запрета и элемент ИЛИ, причем рабочие выходы блоков совпадения подключены к входам элемента ИЛИ выход которого подключен к управляющим входам блоков запрета, каждый из которых включен между тормозным выходом и входом разряда соответствующих блока совпадения и интегратора.

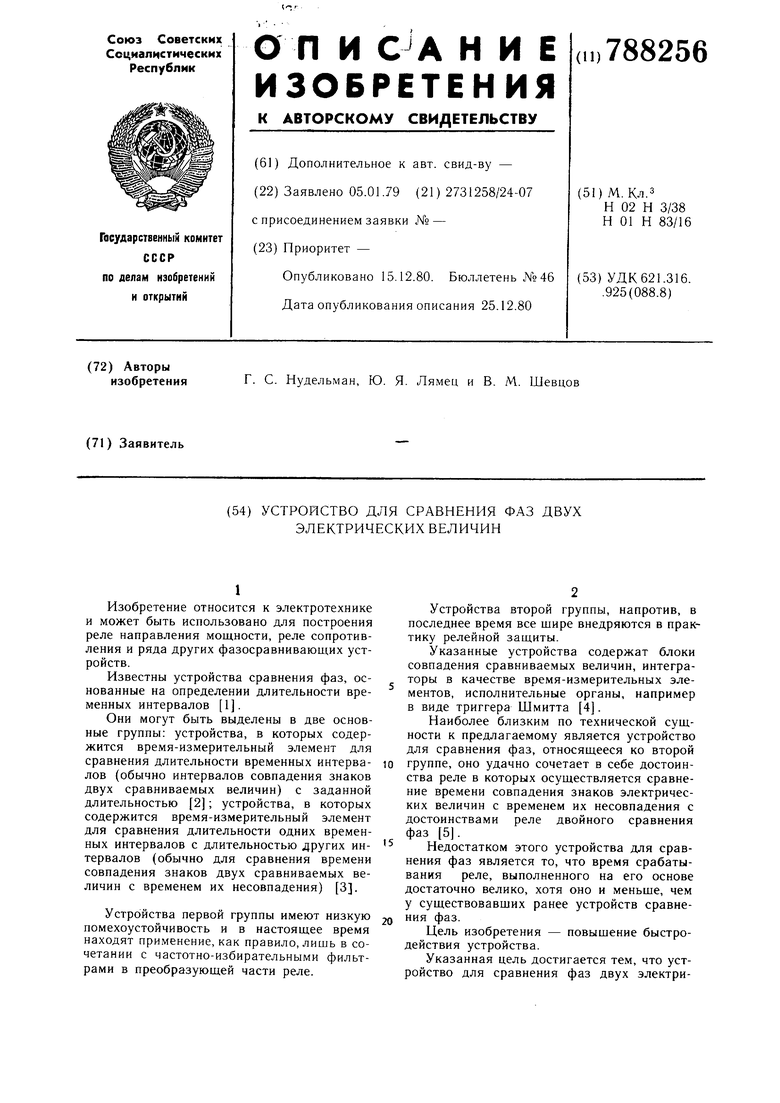

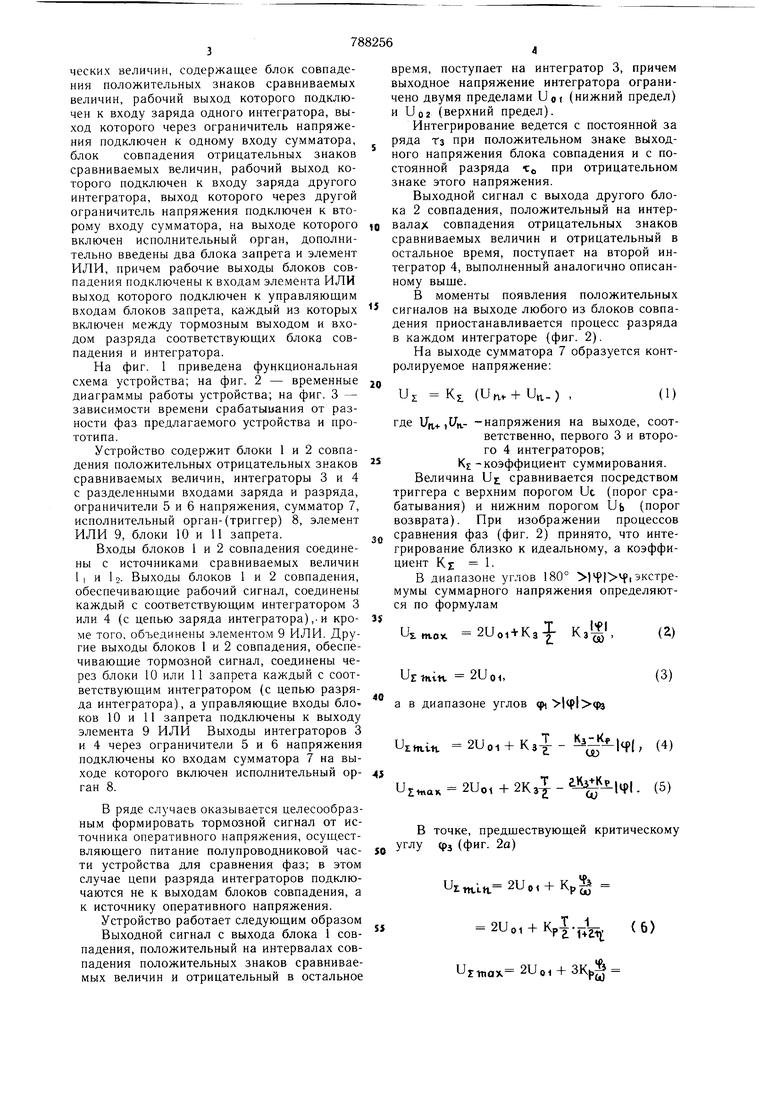

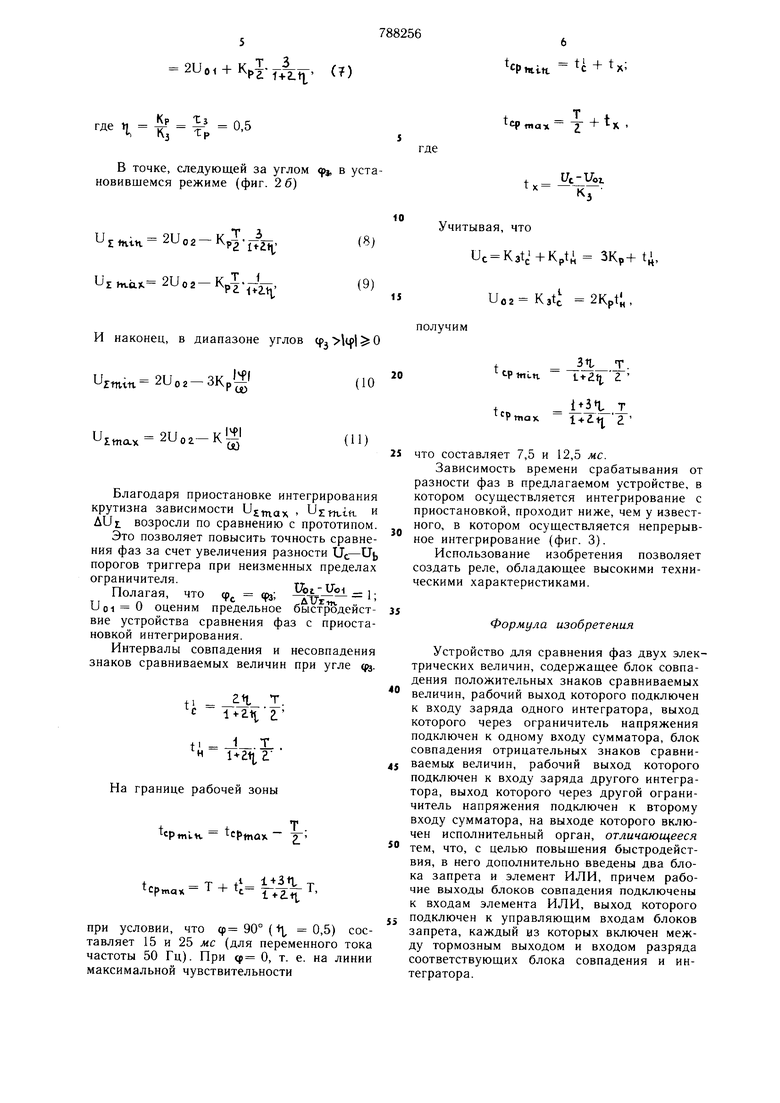

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - временные диаграммы работы устройства; на фиг. 3 - зависимости времени срабатыиания от разности фаз предлагаемого устройства и прототипа.

Устройство содержит блоки 1 и 2 совпадения положительных отрицательных знаков сравниваемых величин, интеграторы 3 и 4 с разделенными входами заряда и разряда, ограничители 5 и 6 напряжения, сумматор 7, исполнительный орган-(триггер) 8, элемент ИЛИ 9, блоки 10 и 11 запрета.

Входы блоков 1 и 2 совпадения соединены с источниками сравниваемых величин I I и 12- Выходы блоков 1 и 2 совпадения, обеспечивающие рабочий сигнал, соединены каждый с соответствующим интегратором 3 или 4 (с цепью заряда интегратора),-и кроме того, объединены элементом 9 ИЛИ. Другие выходы блоков 1 и 2 совпадения, обеспечивающие тормозной сигнал, соединены через блоки 10 или 11 запрета каждый с соответствующим интегратором (с цепью разряда интегратора), а управляющие входы бло ков 10 и 11 запрета подключены к выходу элемента 9 ИЛИ Выходы интеграторов 3 и 4 через ограничители 5 и 6 напряжения подключены ко входам сумматора 7 на выходе которого включен исполнительный орган 8.

В ряде случаев оказывается целесообразным формировать тормозной сигнал от источника оперативного напряжения, осуществляющего питание полупроводниковой части устройства для сравнения фаз; в этом случае цепи разряда интеграторов подключаются не к выходам блоков совпадения, а к источнику оперативного напряжения. Устройство работает следующим образом Выходной сигнал с выхода блока 1 совпадения, положительный на интервалах совпадения положительных знаков сравниваемых величин и отрицательный в остальное

время, поступает на интегратор 3, причем выходное напряжение интегратора ограничено двумя пределами Uof (нижний предел) и и02 (верхний предел).

Интегрирование ведется с постоянной за ряда тз при положительном знаке выходного напряжения блока совпадения и с постоянной разряда TO при отрицательном знаке этого напряжения.

Выходной сигнал с выхода другого блока 2 совпадения, положительный на интервалах совпадения отрицательных знаков сравниваемых величин и отрицательный в остальное время, поступает на второй интегратор 4, выполненный аналогично описанному выще.

В моменты появления положительных сигналов на выходе любого из блоков совпадения приостанавливается процесс разряда в каждом интеграторе (фиг. 2).

На выходе сумматора 7 образуется контролируемое напряжение:

и К (Unv-bUf,.)

(1)

где -напряжения на выходе, соответственно, первого 3 и второго 4 интеграторов; KJ:-коэффициент суммирования. Величина U сравнивается посредством триггера с верхним порогом Uc (порог срабатывания) и нижним порогом Ub (порог возврата). При изображении процессов сравнения фаз (фиг. 2) принято, что интегрирование близко к идеальному, а коэффициент К л 1.

В диапазоне углов 180° экстремумы суммарного напряжения определяются по формулам

ьтак 2Uoi + K3 Кз

Ifl

U

(2)

Ur tnitt 2Uo

(3) а в диапазоне углов f

Jirttiit 2Uoi

(4)

2Uoi + 2Кз| - .

(5)

В точке, предществующей критическому углу фз (фиг. 2а)

UinLltt 2Uo. + Kpg

2Uoi + Kp|-|; (6) Uj:inox 2Uoi + 3K,,J

2Uoi + Кьт 7-..

(7)

г n-2.

4- °

В точке, следующей за углом , в установившемся режиме (фиг. 26)

-i:fntn 2Uo2-Kp -j alj

Zhva;t- 2Uo2-Kp - -2,

и

И наконец, в диапазоне углов ф, |ц)| О

zmin- 2Uo2 -ЗКр -

2Uoi-к U)

Благодаря приостановке интегрирования крутизна зависимости , и AUt возросли по сравнению с прототипом.

Это позволяет повысить точность сравнения фаз за счет увеличения разности , порогов триггера при неизменных пределах ограничителя.

Полагая, что ср, ср,; 1и 01 О оценим предельное быстродействие устройства сравнения фаз с приостановкой интегрирования.

Интервалы совпадения и несовпадения знаков сравниваемых величин при угле й.

ti Jt. 1с n-zit г

t Т..

н 1 г1|;гНа границе рабочей зоны

Т.

«ptnlH - cpinax 2Г

f т u - т

tcpmcix- 1 + It-

при условии, что ф 90° ( 0,5) составляет 15 и 25 .«с (для переменного тока частоты 50 Гц). При ср О, т. е. на линии максимальной чувствительности

cphtitt - U + tx;

i+t..

t

Ч шан

где

Ut-l/oi

К,

Учитывая, что

Uc K3tc+Kpt ЗКр+t.

Uo2 Kstt - 2Kpt ,

получим

что составляет 7,5 и 12,5 мс.

Зависимость времени срабатывания от разности фаз в предлагаемом устройстве, в котором осуществляется интегрирование с приостановкой, проходит ниже, чем у известного, в котором осуществляется непрерывное интегрирование (фиг. 3).

Использование изобретения позволяет создать реле, обладающее высокими техническими характеристиками.

Формула изобретения

Устройство для сравнения фаз двух электрических величин, содержащее блок совпадения положительных знаков сравниваемых величин, рабочий выход которого подключен к входу заряда одного интегратора, выход которого через ограничитель напряжения подключен к одному входу сумматора, блок совпадения отрицательных знаков сравниваемых величин, рабочий выход которого подключен к входу заряда другого интегратора, выход которого через другой ограничитель напряжения подключен к второму входу сумматора, на выходе которого включен исполнительный орган, отличающееся тем, что, с целью повыщения быстродействия, в него дополнительно введены два блока запрета и элемент ИЛИ, причем рабочие выходы блоков совпадения подключены к входам элемента ИЛИ, выход которого подключен к управляющим входам блоков запрета, каждый из которых включен между тормозным выходом и входом разряда соответствующих блока совпадения и интегратора.

Источники информации, принятые во внимание при экспертизе

1.Фабрикант В. Л. Основы теории построения измерительных органов релейной защиты. М., «Высшая школа, 1968, с. 267.

2.Авторское свидетельство СССР № 146843, кл. Н 02 К 3/38, 1965.

3.Авторское свидетельство СССР № 155552, кл. G 01 Р 25/00, 1966.

4.Vitanov А., Pew N,, Tsaperkov V. Использование интегральных схем в релейной защите.-Сб. «Релейная зашита и противоаварийная автоматика, С 1 G R Е, М., «Энергия, 1976, с. 37-50.

5.Авторское свидетельство СССР

по заявке № 2548066/24-07, кл. Н 02 Н 3/38, 1978.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения фаз двух электрических величин | 1977 |

|

SU957341A1 |

| Реле сопротивления | 1978 |

|

SU736256A1 |

| Реле сопротивления | 1977 |

|

SU729724A1 |

| Устройство для сравнения фаз | 1979 |

|

SU862303A1 |

| Устройство для сравнения фаз двух электрических величин | 1980 |

|

SU947782A1 |

| Устройство для сравнения фаз | 1980 |

|

SU951537A2 |

| Устройство для сравнения фаз двух электрических величин | 1983 |

|

SU1150695A1 |

| Устройство для сравнения фаз двух электрических величин | 1990 |

|

SU1749971A1 |

| Устройство для сравнения электрических величин по фазе | 1982 |

|

SU1108549A1 |

| Реле сопротивления | 1977 |

|

SU748637A1 |

Авторы

Даты

1980-12-15—Публикация

1979-01-05—Подача