выходу триггера и второму входу вто- писи регистра, выход элемента ИЛИ роге элемента И блока управления, соединен с установочным входом счетвыход которого соединен с вхоДом за- адка адреса.

1109759

| название | год | авторы | номер документа |

|---|---|---|---|

| Число-импульсное линеаризирующее устройство с масштабированием | 1984 |

|

SU1201847A1 |

| Число-импульсное линеаризующее устройство | 1980 |

|

SU900290A1 |

| Устройство для вычисления массы нефти и нефтепродуктов в резервуарах | 1983 |

|

SU1117653A1 |

| Устройство преобразования частоты в код | 1988 |

|

SU1647918A1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР УСРЕДНЕННОЙ МОЩНОСТИ НЕСТАЦИОНАРНОЙ НАГРУЗКИ | 1992 |

|

RU2060542C1 |

| Число-импульсное линеаризующееуСТРОйСТВО C МАСшТАбиРОВАНиЕМ | 1979 |

|

SU800996A1 |

| Контроллер измерительного преобразователя | 1987 |

|

SU1462357A1 |

| Устройство для преобразования двоичной последовательности в балансный троичный код | 1991 |

|

SU1807561A1 |

| Устройство линеаризации выходных характеристик частотных датчиков | 1982 |

|

SU1100727A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МЕСТ ПОВРЕЖДЕНИЯ НАПОРНОГО ТРУБОПРОВОДА | 1992 |

|

RU2046251C1 |

ЧИСЛО-ИМПУЛЬСНОЕ ЛИНЕАРИЗУЮЩЕЕ УСТРОЙСТВО С МАСШТАБИРОВАНИЕМ, содержащее управляемый делитель частоты, счетчик адреса, блок управления, первый элемент И, переключатель каналов, первый блок памяти и двоичный умножитель, состоящий КЗ делителя частоты и элемента Ы И-ИЛИ, где N - разрядность устройства, причем вход устройства соединен с первым входом первого элемента И, выход которого соединен со счетным входом управляемого делителя частоты, управляющий вход и выход которого соединены соответственно с выходом переключателя каналов и входом делителя частоты, кодовый и импульсный выходы которого соеди- : нены соответственно с первой группой входов элемента N и-ИЛИ и счетным входом счетчика адреса, вход и выход переключателя каналов соединены соответственно с входом задания номера датчика устройства и первым адресным входом первого блока памяти. от-личающееся тем, что, с целью расширения области применения путем использования памяти низкого быстродействия без снижения быстродействия устройства, в него введейы второй блок памяти,регистр, схема сравнения, коммутатор и второй эле мент И, первый вход которого соединен с выходом элемента Ы И-ИЛИ, вторая группа входов которого подключена к соответствующим выходам коммутатора, первый и второй информационные входы которого соединены с выходами соответственно -первого и второго блоков памяти, выход регистра соединен с первым адресным входом второго и вторым адреснымувходом перво(Л го блоков памяти и первым входом схемы сравнения, второй вход которой соединен с выходом счетчика адреса и информационным входом регистра, второй адресный вход второго блока памяти соединен с выходом переключателя каналов, выход схемы сравнения соединен с управляющим входом коммутатора, выход второго элемента И со соединен с выходом устройства, причем блок управления содержит генератор, триггер, одновибратор, два СП элемента И и элемент ИЛИ, выходсо генератора соединен с входами триггера и Ъдновибратора, первыми.входами элемента ИЛИ и первого и второго элементов И блока управления и вторым входом первого элемента И устройства, второй вход второго элемента И устройства соединен с выходом первого элемента И блока управления, второй вход которого подключен к

Изобретение относится к измерительной технике и может найти применение при создании многоканальных информационных измерительных систем, предназначенных для измерения электрических и неэлектрических величин с использованием первичных преобразователей (датчиков),которые имеют нелинейную выходную характеристику. Известно число-импульсное линеаризующее устройство, содержащее блоки памяти, позволяющие использовать/ информацию с.нескольких датчиков с различной степенью нелинейности СП

Однако структура такого линеаризующего устройства существенно сужае число ПЗУ, выпускаемых в интегральном исполнении, кЬторые могли бы быть использованы в подобных устройствах, а следовательно,сужает область применения устройств линеаризации. Объясняется это тем, что современные интегральные микросхемы (ИС), например ИС ТТЛ-типа, позволяют использовать частоты до 1025 МГц, что дает возможность повысит быстродействие измерите;1ьных приборо Наиболее быстродействующие ПЗУ, которые могли бы работать на близких к этим частотам, выполняются на схемах ЭСЛ- или ТТЛ-типа. Например, ПЗУ, основанное на применении эмиттерно-связанной логики,, характеризуется временем выборки порядка 35 не, т.е. позволяет работать на частотах, равных 25-28 МГц, Однако такое

быстродействие достигается за счет большого потребления мощности. Одна интегральная микросхема такого типа потребляет мощность порядка 710 мВт. Если при этом учесть малую емкость () бит ИС, а следовательно, необходимость увеличения чиспа входов и выходов ПЗУ за счет увеличения числа используемых ИС, становятся очевидными недопустимобольшие,затраты мощности на выполнение операции линеаризации.

Существенно меньшим потреблением отличаются ИС, основанные на применении ЩП- и в особенности КМДП-струтур. Природа этих структур позволяет значительно повысить степень интеграции, а следовательно, и емкость ПЗУ с одновременным снижением потребляемой мощности. Однако время выборки этих ИС таково, что они могут работать на частотах, не превышающих 2 МГц. Как правило, для МДП-структур характерным является время выборки, равное единицам микросекунд. Следовательно, необходимо создание таких структур линеаризующих устройств, которые могли бы использовать преимущество малой потребляемой мощности таких ПЗУ и избавиться от их недостаточного быстродействия.

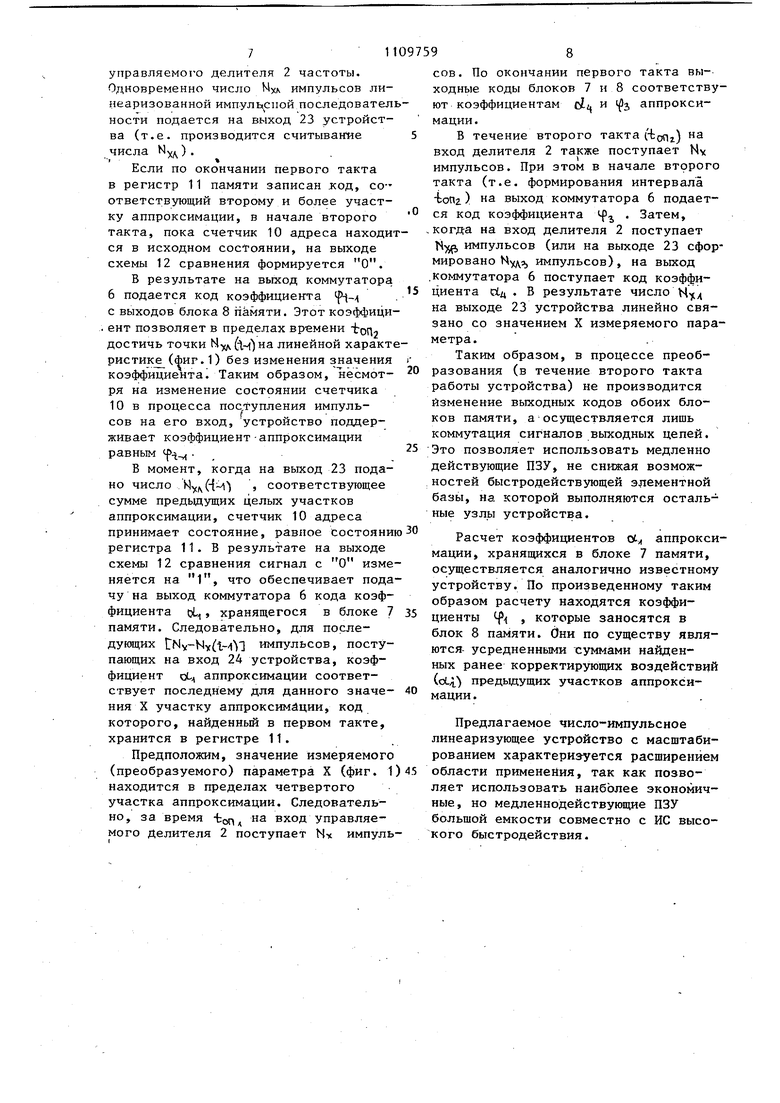

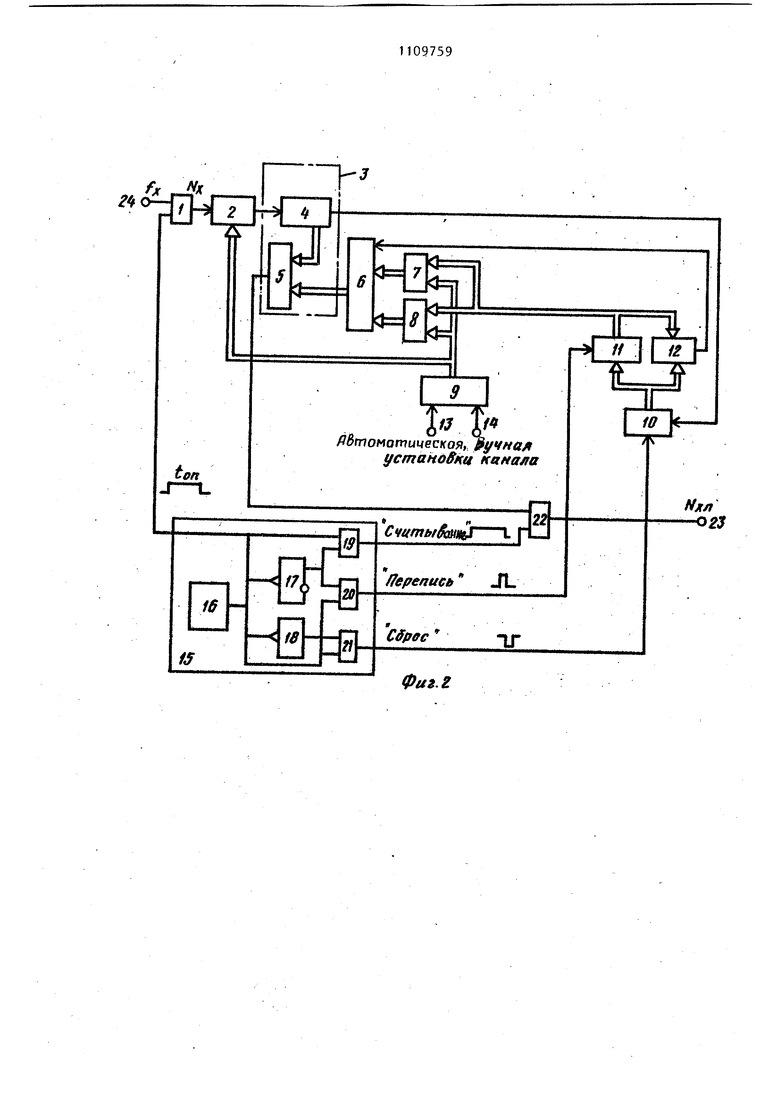

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее управляемый делитель частоты, счетчик адреса, блок управления, первый элемент И, переключатель каналов, первый блок памяти и двоичный умножитель, состоящий из делителя частоты и элемента N И-Ш1И, где N - разрядность устройства, причем вход устройства соединен с первым входом первого элемента И, выход которого соединен со счетным входом управляемого делителя частоты, управляющий вход и выход которого соединены соответственно с выходом переключателя каналов и входом делителя частоты, кодовый и импульсный выходы которого соединены соответственно с первой группой входов элемента И-ИПИ и счетным входом счетчика адреса, вход и выход переключателя каналов соединены соответственно с входом задания номера датчика устройства и первым адресным входом первого блока памяти 21. Недостатком известного устройств является невозможность применения в нем энергетически экономичных, но имеющих низкое быстродействие постоянных запоминающих устройств без снижения быстродействия. Цель изобретения - расширение области применения путем использования памяти низкого быстродействия бе снижения быстродействия устройства, Поставленная цель достигается тем, что в число-импульсное линеаризующее устройство с масштабированием содержащее управляемый делитель част тоты, счетчик адреса, блок управлени первый элемент И, переключатель каналов, первьй блок памяти и двоичный умножитель, состоящий из делителя частоты и элемента N И-ИЛИ, где N - разрядность устройства, при чем вход 1устройства соединен с первы входом первого элемента И, выход которого соединен со счетным входом управляемого делителя частоты, уцрав ляющий вход и выход которого соедине ны соответственно с выходом переключателя каналов и входом делителя частоты, кодовый и импульсный выходы которого соединены соответственно с первой группой входов элемента Ы И-ИЛИ и счетным входом счетчика адреса, вход и выход переключателя каналов соединены соответственно с входом задания номера датчика устрой ства и первым адресным входом первого блока памяти, дополнительно введены второй блок памяти, регистр схема сравнения, коммутатор и второй элемент И, первый вход которого соединен с выходом элемента N И-ИЛй, вторая группа входов которого подключена к соответствующим выходам коммутатора, первый и второй информа ционные входы которого соединены с выходами соответственно первого и второгоблоков памяти, выход регистр соединен с первым адресным входом второго и вторым адресным входом первого блоков памяти и первьм входом схемы сравнения, второй вход которой соединен с выходом счетчика адреса и информационным входом регистра, зторой адресньй вход второг блока памяти соединен с выходом переключателя каналов, выход схемы сравнения соединен с управляющим входом коммутатора, выход второго элемента И соединен с выходом устройства, причем блок управления содержит генератор, триггер, одновибратор, два элемента И и элемент ИЛИ, йыход генератора .соединен с входами три1- гера и одновибратьра, первыми входами элемента ИЛИ и первого и второго элементов И блока управления и вторым входом первого элемента И устройства, второй вход второго элемента И устройства соединен с выходом первого элемента И блока управления, второй вход которого подключен к выходу триггера и второму входу второго элемента И блока управления,выход которого соединен с входом записи регистра, выход элемента ИЛИ соединен с.установочньш входом счетчика адреса. На фиг. 1 представлены графики, поясняющие работу устройства{ на фиг. 2 - блок-схема устройства; на фиг. 3 .- временные диаграммы блока управления. Число-импульсное линеаризующее устройство с масштабированием содержит элемент И 1, управляемый делитель 2 частоты, двоичньш умножитель . 3, делитель 4 частоты, элемент Ц Н- ИЛИ 5, коммутатор 6, блоки 7 и 8 памяти, переключатель 9 каналов, счетчик 10 адреса, регистр 11, схему 12 сравнения, входы 13 и 14 устройства, блок 15 управления, генератор 16 импульсов, триггер 17, одновибратор 18, элементы И 19 и 20, элемент ИЛИ 21, элемент И 22, выход 23 и вход 24 устройства. Предлагаемое устройство работает в два такта В первом такте определяется номер того участка аппроксимации (а следовательно, значения коэффициентов аппроксимации), в пределах которого находится значение преобразуемого (измеряемого) параметра X. Во втором такте выполняется функциональное преобразование (линеаризация) с использованием найденных коэффициентов. Графики (фиг. 1) отражают зависимости нелинеаризованного MX и линеаризованного Нуу чисел импульсов от исследуемого параметра X на входе и выходе устройства линеаризации соответственно. Диапазон нелинеаризованной зависимости . разбит равномерно по оси .М на четыре участка аппроксимации. В известном устройстве в процессе его работы зависимость М -f(l)) преобразуют в линеаризованную Му q()c путем последовательной замены коэффициентов с(. , оС , сХ-з , аппроксимации каждого участка на единьй коэффициент сС по мере возрастания числа К и перехода, таким образом, от первого участка к последующим более старшим. Такая замена предполагает равное быстродействие ПЗУ и, например, делителя частоты. Устройство помимо коэффициентов ч , хранящихся в .первом блоке 7 памяти, снабжается коэффициентами ф, которые записаны во втором блоке 8 памяти. Значения обоих коэффициентов выбираются из блоков памяти по окончании первого такта работы устройства Во втором такте вначале в работу вступает коэффициент fi--i позволяющий без изменения состояния второго блока 8 памяти достичь точки (t-) после чего устройство переключается на работу с коэффициентом с , хранящимся в первом блоке 7 памяти. Таким образом, в процессе работы не производятся быстрые изменения кодов на выходах блоков 7 и 8 памяти, а следовательноJ их быстродействие

может быть существенно ниже быстродействия остальных узлов устройства. Устройство работает следующим образом. На выходе генератора 16 импульсов блока 15 управления формируются опорные временные интервалы, длитель ности которых в первом toni и втором тактах одинаковы (фиг. 3). Первому такту предшествует начальная установка (Сброс) счетчика 10 адреса нулевым потенциалом, формируемы на выходе блока 15 управления. В зависимости от номера канала, т.е. от типа датчика, переключатель 9 каналов устанавливается в соответствующее состояние, которое определяет масштабный коэффициент управляемого делителя 2 частоты. Масштаб ный коэффициент управляемого делителя 2, а также коэффициент деления делителя 4 частоты обеспечивают необходимую длину участка аппроксимации, т.е. с приходом на вход 2А устройства числа импульсов, соответствующих длине участка аппроксимации на выходе делителя 4 формируется один импульс. 11

ствует первому участку аппроксимации) в конце первого такта на выходах обоих блоков 7 и 8 памяти формируется одинаковый код, соответству9Следовательно,, по окончании време ни tppi в счетчике Ю адреса оказывается записанным код, соответствующий тому участку аппроксимации, в пределах которого находится значение параметра X. в момент окончания временного интервала триггер 17, входящий в состав блока 15 управления, устанавливается в состояние 1, разрешая тем самым импульсу с выхода одновибратора 18 поступить на вход записи регистра 11. Перепадом 0/1 этого импульса осуществляется перепись кода найденного номера участка аппроксимации с выходов счетчика 10 адреса в регистр 11. После окончания импульса Перепись на выходе блока 15 формируется отрицательный импульс Сброс, устанавливающий счетчик 10 в исходное нулевое состояние. На этом заканчивается первый такт работы устройства. Таким образом, в общем случае результатом первого такта является определение коэффициентов d-. и .i-r-) аппроксимации, коды которых формируются соответственно на выходах блоков 7 и 8 памяти. При этом следует учитывать, что (если значение X соответющий коэффициенту oL 1, первого участка аппроксимации. Если же номер адреса превышает единицу, то коэффициенту oi; первого 7 блока памяти соответствует коэффициентф. вто рого 8 блока памяти, Соответственно при работе устройства во втором такте возможны два варианта: первый - если по окончании первого такта регистр 11 оказывается в состоянии, соответствующем первому участку аппроксимации, и второй если номер участка, записанный в регистре 11, равен двум и более. Если по окончании первого такта в регистре 11 хранится код первого участка аппроксимации, сигнал (например, 1) на выходе схемы 12 сравнения обеспечивает подачу на выход коммутатора 6 кода коэффициента oL,, с выхода первого 7 блока памяти, В течение времени-iof, число yi импульсов нелинеаризованнои и немасштабированной частоты -Г, поступает на вход управляемого делителя 2 частоты. Одновременно число NXN импульсов линеаризованной импульсной последовател ности подается на выход 23 устройства (т.е. производится считыван ие Если по окончании первого такта в регистр 11 памяти записан .код, соответствующий второму и более участку аппроксимации, в начале второго такта, пока счетчик 10 адреса находи ся в исходном состоянии, на выходе схемы 12 сравнения формируется О. В результате на выход коммутатора 6 подается код коэффициента с выходов блока 8 памяти. Этот коэффици . ент позволяет в пределах вр-емени ton достичь точки Мул(1-1)на линейной характ ристику (фиг. 1) без изменения значения коэффициента. Таким образом, Ъесмотсчетчикана изменение состоянии ря 10 импульв процесса поступления сов на его вход, устройство поддерживает коэффициент-аппроксимации равным tp . В момент, когда на выход 23 подано число Ну() , соответствующее сумме предыдущих целых участков аппроксимации, счетчик 10 адреса принимает состояние, равное состояни регистра 11. В результате на выходе схемы 12 сравнения сигнал с О изме няется на 1, что обеспечивает пода чу на выход коммутатора 6 кода коэффициента oL, хранящегося в блоке 7 памяти. Следовательно, для последующих tNv-Ny tHM импульсов, поступающих на вход 24 устройства, коэффициент oL-H аппроксимации соответствует последнему для данного значения X участку аппроксимации, код которого, найденный в первом такте, хранится в регистре 11. Предположим, значение измеряемого (преобразуемого) параметра X (фиг. находится в пределах четвертого участка аппроксимации. Следовательно, за время -tot на вход управляемого Делителя 2 поступает NX импуль сов. По окончании первого такта выходные коды блоков 7 и 8 соответствуют коэффициентам cZi, и , аппроксимации. В течение второго такта опг) вход делителя 2 также поступает Ny импульсов. При этом в начале второго такта (т.е. формирования интервала ioni) на выход коммутатора 6 подается код коэффициента f, . Затем, когда на вход делителя 2 поступает Ц- импульсов (или на выходе 23 сформировано , импульсов), на выход .коммутатора 6 поступает код коэффициента йд . В результате число H-jtx на выходе 23 устройства линейно связано со значением X измеряемого параметра.. Таким образом, в процессе преобразования (в течение второго такта работы устройства) не производится изменение выходных кодов обоих блоков памяти, а осуществляется лишь коммутация сигналов выходных цепей. Это позволяет использовать медленно действующие ПЗУ, не снижая возможностей быстродействующей элементной базы, на. которой выполняются остальные узлы устройства. Расчет коэффициентов О1.„ аппроксимации, хранящихся в блоке 7 памяти, осуществляется аналогично известному устройству. По произведенному таким образом расчету находятся коэффициенты , которые заносятся в блок 8 памяти. Они по существу являются- усредненными суммами найденных ранее корректирующих воздействий (oLyt) предыдущих участков аппроксимации. Предлагаемое число-импульсное линеаризующее устройство с масштабированием характеризуется расширением области применения, так как позволяет использовать наиболее экономичные, но медленнодействующие ПЗУ большой емкости совместно с ИС высокого быстродействия. о л2

иг,1 Л/f X

РВтоматицескоя, fiyVffaA

IwT

1ескоя, fyv установки канала

1 «

ffepenuc Л.

CSfloc

ОТ

фаг. г

toni

tonZ

Фиг. 3

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Число-импульсное линеаризующее устройство | 1980 |

|

SU900290A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Число-импульсное линеаризующееуСТРОйСТВО C МАСшТАбиРОВАНиЕМ | 1979 |

|

SU800996A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| , | |||

Авторы

Даты

1984-08-23—Публикация

1983-04-18—Подача