Устройство относится к вычислительной технике и может быть использовано в системах передачи цифровой информации, когда время передачи ограничено.

Цель изобретения -.повышение быстродействия устройства.

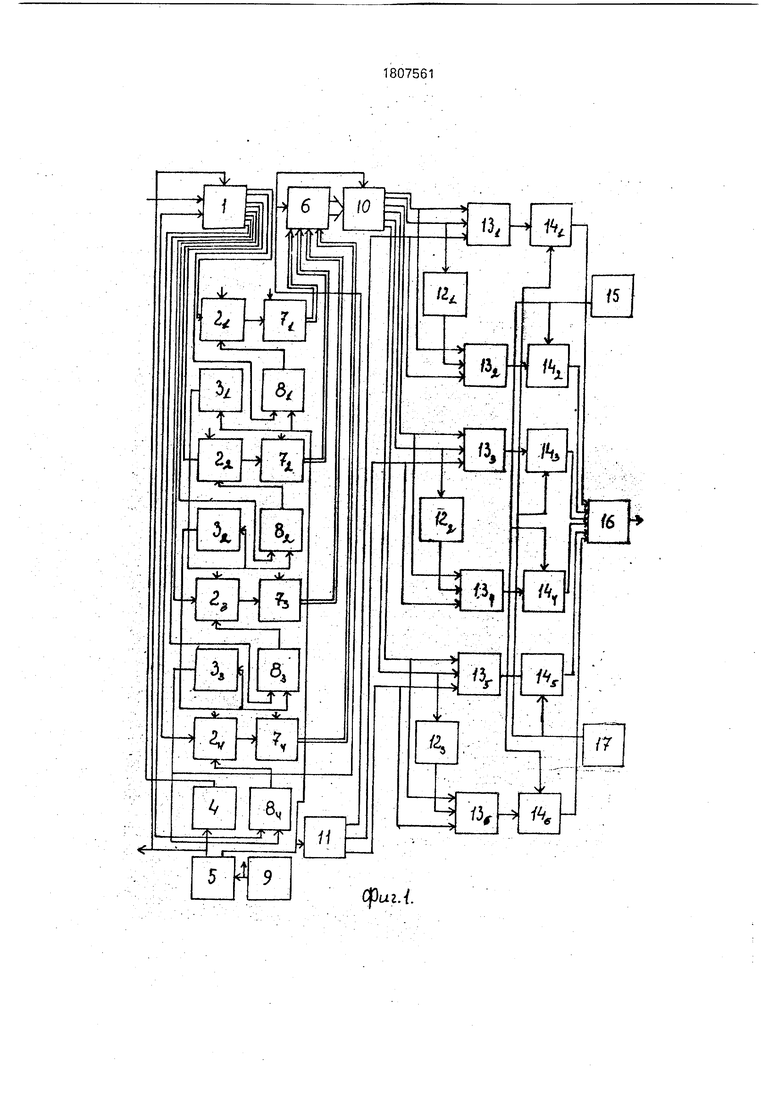

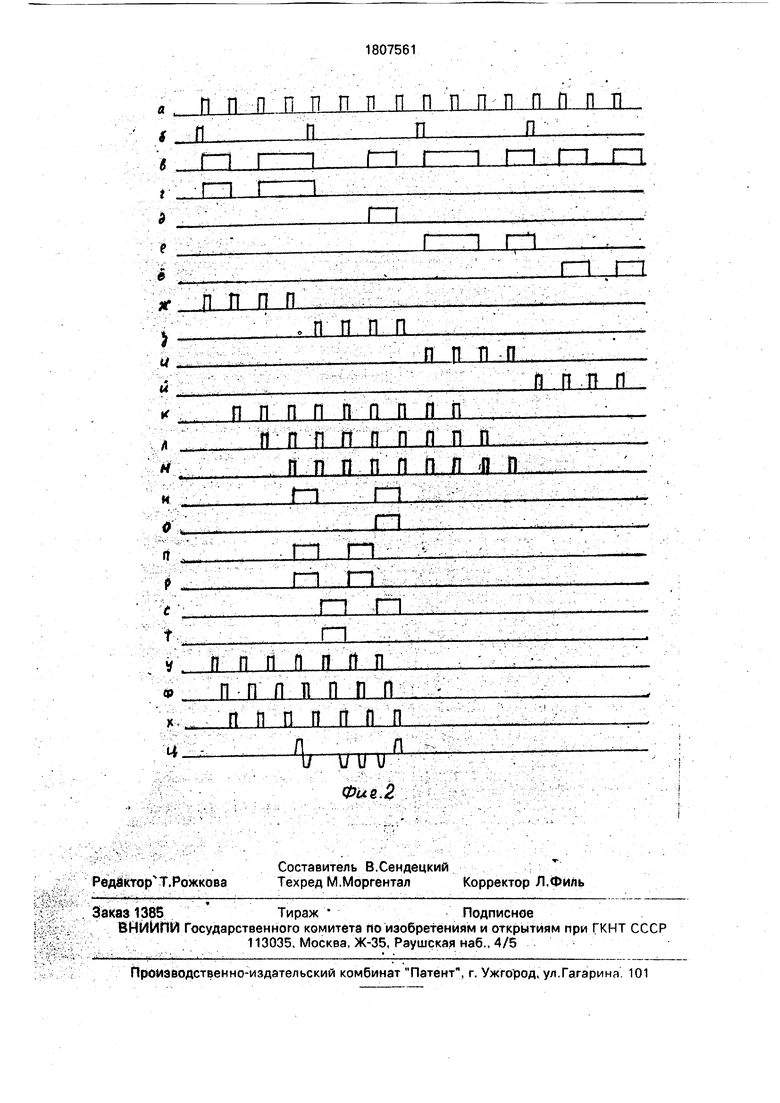

На фиг. 1 приведена функциональная схема устройства ускоренной передачи информации с преобразованием в блочный троичный код; на фиг. 2 - временные диаграммы его работы.

Устройство содержит входной коммутатор 1, блоки 21-24 памяти, ОЗУ 2, элементы задержки Si-Зз, делитель 4 частоты на четыре, переключатель 5 режимов, выходной коммутатор 6, преобразователи последовательного кода в параллельный, представляющие собою четырехразрядные сдвиговые регистры, счетчики 81-84 адреса, генератор 9 тактовой частоты, кодирующую матрицу 10, реализованную на ПЗУ, формирователь 1.1 синхроимпульсов, инверторы

121-12з, элементы И 131-13б ключи 141- 14е, генератор 1 15, формирователь балансного кода 16 в виде операционного усилителя, генератор 1 17.

Работа устройства состоит из двух, цик- лов: накопление информации и выдача информации.

В цикле накопление информации устройство работает следующим образом.

Переключатель режимов 5, имеющий два положения - Накопление и Выдача, находится в положении Накопление . Йм пульсы тактовой частоты с генератора 9 (фиг, 2,а) через переключатель 5 с его первого выхода поступают на тактовый выход устройства и далее на внешнее устройство для тактирования поступления ин- формации, а также на второй вход коммутатора 1 и вход делителя 4 частоты на 4. Выходной сигнал с делителя 4 (фиг. 2,6) поступает на управляющий вход входи pro коммутатора 1, который имеет четыре положения: он поочередно подключает первый и

второй входы соответственно к первому и второму, третьему и четвертому, пятому и шестому, седьмому и восьмому выходам. Смена положения в соответствии с управляющим сигналом с делителя 4 происходит через каждые четыре такта..

Тактированная информация (фиг. 2,в) и импульсы тактрвой частоты (фиг, 2,а), поступающие на первый и второй входы входного коммутатора 1, в первые четыре такта ripo- ходят через его выход 1 (фиг, 2,г) на первое ОЗУ через выход 2 (фиг. 2,ж) на первый счетчик 8 адреса Таким образом п|56йсхр- дйт запись в первое ОЗУ первых четырех разрядов информации. После этого rip импульсу делителя 4 входной коммутатор подключает для записи второе ОЗУ 2 (выход 3 коммутатора, фиг. 2,д) и второй счётчик 8 адреса (выход 4 коммутатора, фиг. 2,з). Вторая четверка разрядов информации зёписы- баётся во второе ОЗУ 2.;

Далее входной коммутатор подключает третье ОЗУ (выход 5, фиг. 2,е) и третий счетчик 8 адреса, (выход 6, фиг. 2,и) для записи третьей четверки разрядов информации. . : -- .... ;. . : . : .. .

Четвертая четверка разрядов эаписы- вается в четвертое ОЗУ 2 (выход 7 коммутатора 1, фиг. 2,е), и выход 8 коммутатора 1,фиг.2.й).

Пятая четверка разрядов записывается в снова подключенное первое ОЗУ 2, и так далее, до записи всей информации. На этом заканчивается цикл Накопление информации.- , :-.. .... . .. - :.

Цикл Выдача информации начинается с переводом переключателя режимов в положение Выдача. Импульсы тактовой частоты (фиг. 2,а) поступают на первый счетчик 8 адреса и инициируют воспроизведение с первого ОЗУ 2 первого разряда информации, записанного по первому адресу. Он переписывается в первый разряд преобразователя 7 последовательного кода в парал- лельный, представляющего собою сдвиговый регистр. Второй импульс тактовой частоты инициирует перезапись из первого бЗУ 2 в первый преобразователь 7 второго разряда информации.А .в этот момент первый тактовый им- пуЛьс, задержанный первой тактовой задержкой 3 на один период тактовой частоты (фиг. 2,к) способствует перезаписи из второго ОЗУ 2 во второй преобразователь 7 пятого разряда информации (первого разряда второй четверки). Когда в первый преобразователь 7 последовательного кода в параллельный будет переписываться третий разряд информации, в третий преобразователь 7 будет переписываться первый разряд третьей четверки разрядов, то есть девятый разряд информации, а во второй преобразователь 7 будет переписываться второй разряд второй четверки разрядов информации. Четвёртый тактовый импульс перезаписывает в первый преобразователь 7 четвертый разряд информации и в этот же момент первый тактовый импульс, прошедший через три такТрвые задержки 3, перезаписывает из четвёртого ОЗУ 2 в четвертый преобразователь 7 первый разряд четвертой четверки информации (тринадцатый разряд информации). Этот же импульс поступает на выходной коммутатор 6 и подключает его к первому преобразователю 7 последовательного, кода в параллельный; в котором к этому времени уже записаны четыре разряда информации. С первого преобразователя тырехразрядный параллельный код поступает через выходной коммутатор 6 на кодирующую матрицу 10, созданную на ПЗУ.; v .v.v.;V/ :-:.;: .

Кодирующая матрица 10 каждой четырёхразрядной комбинаций в двоичном коде Ставит в соответствие трёхразрядную комбинацию в троичном коде Q использованием значений 0,1-1, приче м для передачи каждого разряда используются две шины: шина значений и шина знака. Совпадающие по времени значения 1 на обоих шинах означают, что по шине значений передается -1 (см.фйг. 2,н,о; 2,п,р; 2,с,т).

Для формирования значений одного разряда в троичном коде используется один инвертор 12, два элемента И 13, Два ключа 14, а также генератор 1 15 и генератор - 17. Работа происходит следующим образом.

С первого выхода кодирующей матрицы 10 значение первого разряда поступает на первые входы первых двух элементов И 13 (фиг. 2,н). На втором выходе матрицы 10 .присутствует значение знака: 0 - плюс, 1 - минус, которое подается на второй вход элемента И 13. На третьи входы всех элементов И 13-136, подаются синхронизирующие импульсы с формирователя 11, который формирует их из тактовой последовательности импульсов путем равномерного смещения друг относительно друга в пределах периода тактовой последовательности (фиг. 2,у, 2,ф, 2,х), причем первым идет импульс для формирования первого разряда, вторым - второго разряда, третьим,-третьего,

Если с кодирующей матрицы. 10 в пер-, вом разряде поступает логический 9, то на первых входах первых двух элементов; И 13 присутствует нулевой потенциал и соединенные с ними два ключа 14 остаются закрытыми, а на формирователе 16 балансного кода также будет 0.

Если с кодирующей матрицы 10 в первом разряде поступает логическая 1 (на шине значений - потенциал логической 1 и на шине знака - ноль), то на выходе первого элемента И 13 остается нулевой потенциал и ключ 14 закрыт, а на выходе второгб элемента И 13 в момент прохождения синхроимпульса появится потенциал логической единицы, который откроет второй ключ 14 для прохождения через него логический 1 с генератора 1 15. Таким образом на формирователе 16 окажется логическая 1.

Если с кодирующей матрицы 10 в первом разряде поступает логическая -1 (на шине значений и на шине знака - потенциалы логической 1), то в момент прохождения синхроимпульса на выходе первой схемы И13 окажется потенциал логической 11 и первый ключ 14 откроется для прохождения логической -1 с генератора -1 17,

Таким образом, на формирователе 16 окажется логическая -Т1. В итоге по первому синхроимпульсу (фиг. 2,у) на формирователе 16 будет сформировано значение первого разряда балансного кода.

По второму синхроимпульсу (фиг. 2,ф), поступающему с формирователя 11 на третьи входы третьего и четвертого элементов И 13, куда поступают с кодирующей матрицы 10 значение второго разряда кода vi его знак (фиг, 2,п, 2,р), на формирователе 16 окажется сформированным значение второго разряда балансного кода.

По третьему синхроимпульсу (фиг. 2,х), поступающему с формирователя 11 СИ на третьи входы пятогр и шестого элементов И 13, куда поступают с кодирующей матрицы

10 значение третьего разряда кода и его знак (фиг. 2,с, 2,т) на формирователе 16 окажется сформированным значение третьего разряда балансного кода. 5Этим завершается преобразование первых четырех разрядов информации из двоичного кода в троичный с использованием трех его разрядов, причем длительность троичного трехразрядного блока, составит

0 25% длительности двоичного четырехразрядного блока. Второй тактовый импульс, поступивший на выходной коммутатор 6, подключит к кодирующей матрице 10 второй преобразователь 7 последовательного

5 кода в параллельный, на выходе которого будет уже присутствовать вторая четверка двоичных разрядов, выданная со второго ОЗУ 2, Третий тактовый импульс подключает к кодирующей матрице 10 третий преоб0 разователь 7 с третьей четверкой двоичных разрядов, четвертый тактовый импульс подключит четвертый преобразователь 7, а пятый тактовый импульс снова подключит первый преобразователь 7, в котором к это5 му моменту окажутся записанными следующие четыре разряда информации (пятая четверка) из первого ОЗУ 2.

Далее работа происходит аналогичным образом.

0 Формула изобретения

Устройство для преобразования двоичной последовательности в балансный троичный код, содержащее коирующую матрицу, генератор тактовой частоты, дели5 тель частоты, первый преобразователь последовательного кода в параллельный, первый элемент И и формирователь балансного кода, выход которого является информационным выходом устройства, о т л и ч а0 ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены входной и выходной коммутаторы, блоки памяти, элементы задержки, второй-четвер- тый преобразователи последовательного

5 кода в параллельный, счетчики, переключатель, второй-шестой элементы И, инверторы, ключи, генератор 1, генератор -1, формирователь синхроимпульсов, выходы которого соединены с первыми входами

0 элементов И, информационный вход вход ного коммутатора является входом устройства, выходы первой группы выходов входного коммутатора соединены с первыми входами соответствующих блоков памя5 ти, выходы которых соединены с первыми входами одноименных преобразователей последовательного кода в параллельный, выходы которых соединены с соответствующими информационными входами выходного коммутатора, выходы которого

соединены с информационными входами кодирующей матрицы, выходы второй группы выходов входного коммутатора соединены с первыми входами соответствующих счетчиков, выходы которых соединены с вторыми входами одноименных блоков памяти, выход генератора тактовой частоты соединен с третьими входами блоков памяти, вторыми входами преобразователей последовательного кода в параллельный и входом переключателя, первый выход которого является тактовым выходом устройства и соединен непосредственно и через делитель частоты с тактовым и управляющим входами входного коммутатора соответст- венно, второй выход переключателя соеди- нен непосредственно с входом формирователя синхроимпульсов и вторым входом первого счетчика и через первый элемент задержки с вторым входом второго счетчика и входом второго элемента задержки, быход которого соединен непосредственно с вторым входом третьего счетчика и через третий элемент задержки - с вторым входом четвертого счетчика и тактовыми входами выходного коммутатора и кодирующей матрицы, первый и второй выходы

которой соединены соответственно с объединенными вторыми входами первого и второго элементов И и непосредственно с третьим входом первого элемента И и через первый инвертор - с третьим входом второго элемента И, третий и четвертый выходы кодирующей матрицы соединены соответственно с объединенными вторыми входами третьего и четвертого элементов И и непосредственно с третьим входом третьего элемента И и через второй инвертор - с третьим входом четвертого элемента И, пятый и ше- стой выходы кодирующей матрицы соедине- ны соответственно с объединенными вторыми входами пятого и шестого элементов И и непосредственно с третьим входом пятого элемента И и через третий инвертор - с третьим входом шестого элемента И, выходы элементов И соединены с первыми входами одноименных ключей, выход генератора -1 соединен с.вторыми входами первого, третьего и пятого ключей, выход генератора 1 соединен с вторыми входами второго, четвертого и шестого ключей, выходы ключей соединены с соответствующими входами формирователя балансного кода.

« , П П П П П П И П П Л П П П П П Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования двоичной последовательности в блочный балансный троичный код | 1986 |

|

SU1324115A1 |

| Адаптивный групповой приемник многочастотного кода с импульсно-кодовой модуляцией | 1989 |

|

SU1830632A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ | 2007 |

|

RU2356165C1 |

| Устройство для графического отображения синтезируемой устной речи | 1986 |

|

SU1411802A1 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1987 |

|

SU1564685A1 |

| СИСТЕМА СВЯЗИ | 1996 |

|

RU2116001C1 |

| Преобразователь двоичного кода в троичный код | 1983 |

|

SU1169172A1 |

| Устройство синхронизации источников сейсмических сигналов | 1991 |

|

SU1787278A3 |

| Спироанализатор | 1986 |

|

SU1391621A1 |

Устройство ускоренной передачи информации с преобразованием в блочный троичный код предназначено для сокращения времени передачи цифровой информации по каналу связи. Цель изобретения - повышение быстродействия устройства. Устройство обеспечивает непрерывное считывание информации собственными тактами из внешнего устройства, накопление в ОЗУ и после переключения в режим, выдачу информации, считывание с ОЗУ, преобразование в блочный троичный код и выдачу во внешние устройства с последующей передачей по каналам связи: Непрерывность приема достигается тем, что информация на вход устройства поступает в каждом периоде тактового сигнала, вся работа устройства по преобразованию и записи информации синхронизируется единой тактовой частотой, Повышение быстродействия достигается тем, что принятые в течение четырех тактов четырехразрядные блоки информации в двоичном коде после преобразования выдаются затем в канал связи в течение одного периода тактового сигнала. Применяемое преобразование в блочный троичный «од позволяет принятые четырехразрядные блоки передавать в канал связи Трёхразряднймй блоками. Устройство содержит коммутаторы, блоки памяти, элементы задержки, делитель частоты, переключатель режимов, преобразователи последовательного кода в параллельный, счетчики адреса, генератбр тактовой частоты, колирующую, матрицу, формирователь синхроимпульсов, инвертор ры, элементы, ключи, генератор 1, формирователь балансного кода, генератор М. 2ил. ., .. . . ... .... . Ё 00 о а о

Авторы

Даты

1993-04-07—Публикация

1991-04-11—Подача