4i

О)

со

СП

Изобретение относится к автоматил ке и измерительной технике и может быть использовано в качестве коррек- тирукнцего звена импульсных и цифро- вых нелинейных систем управления, а также в составе цифровых измерительных средств для восстановления сигналов частотно-импульсных датчиков при выполнении динамических измере-

НИИ.

изобретения - повышение точности восстановления сигналов с измерительного преобразователя за счет компенсации его статических и дина- мических погрешностей.

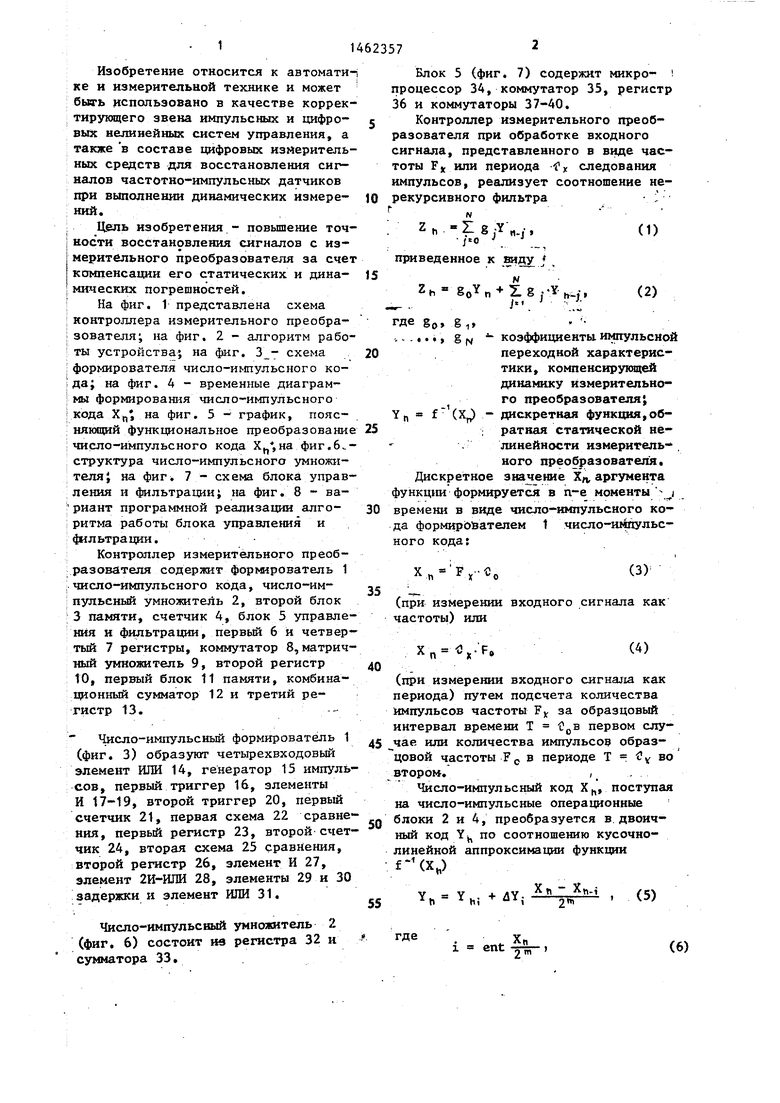

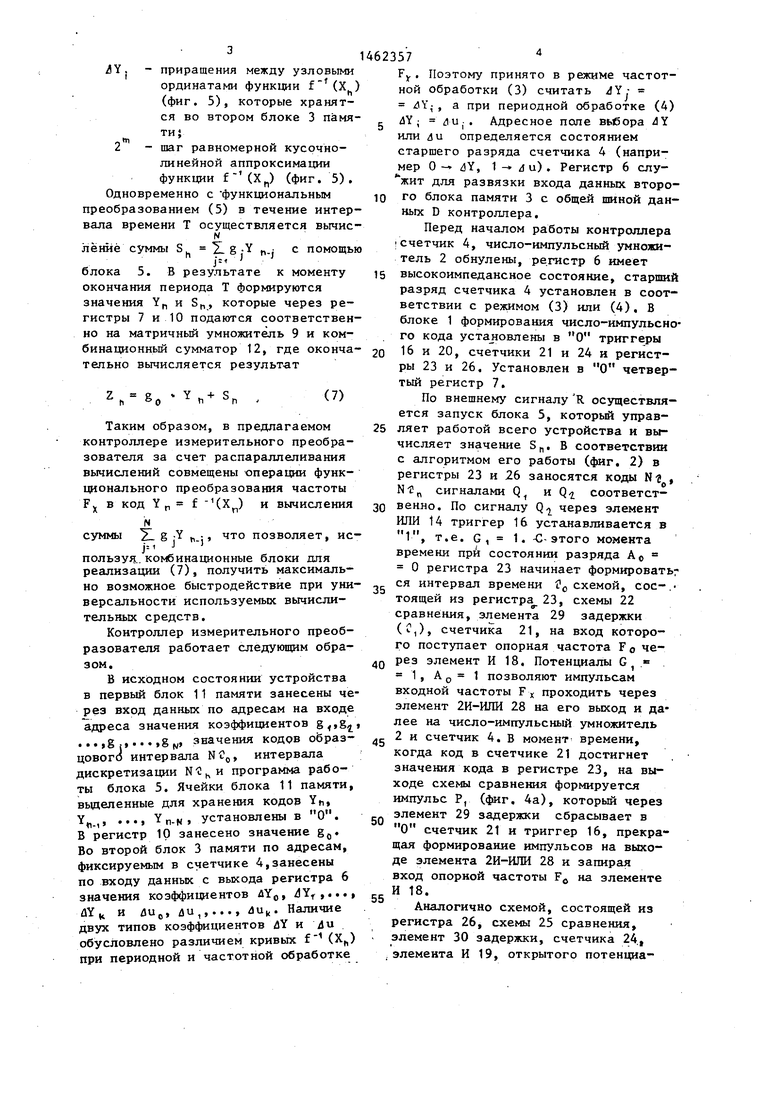

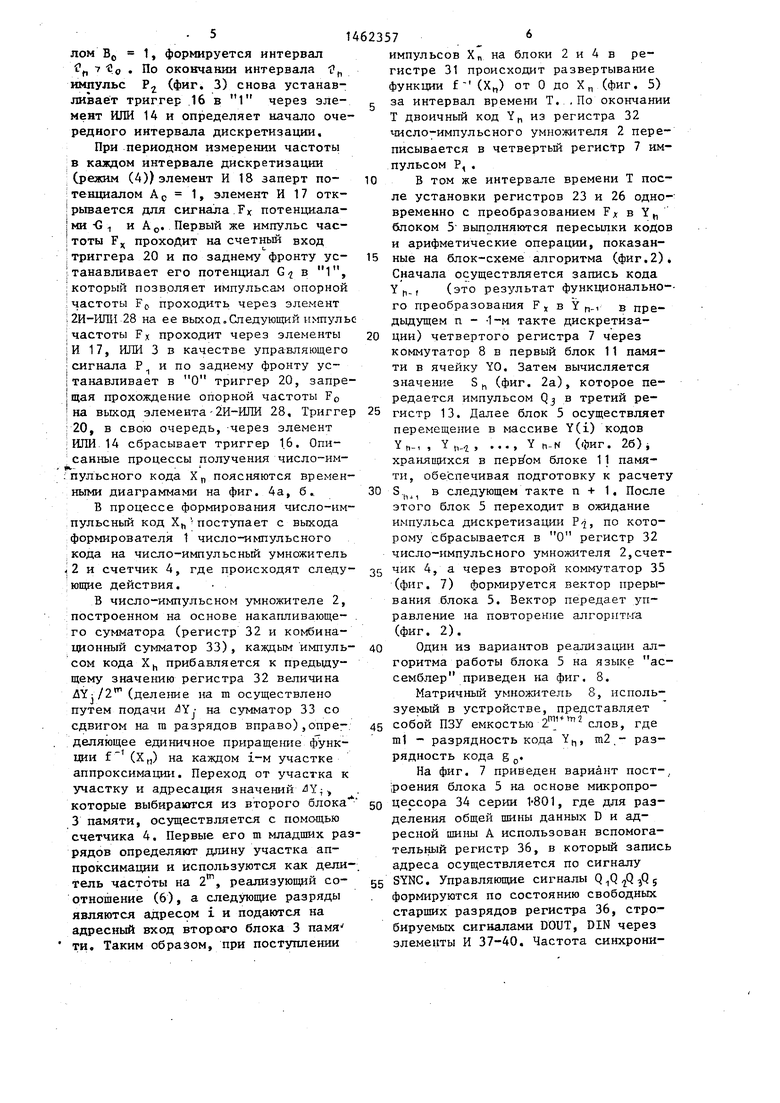

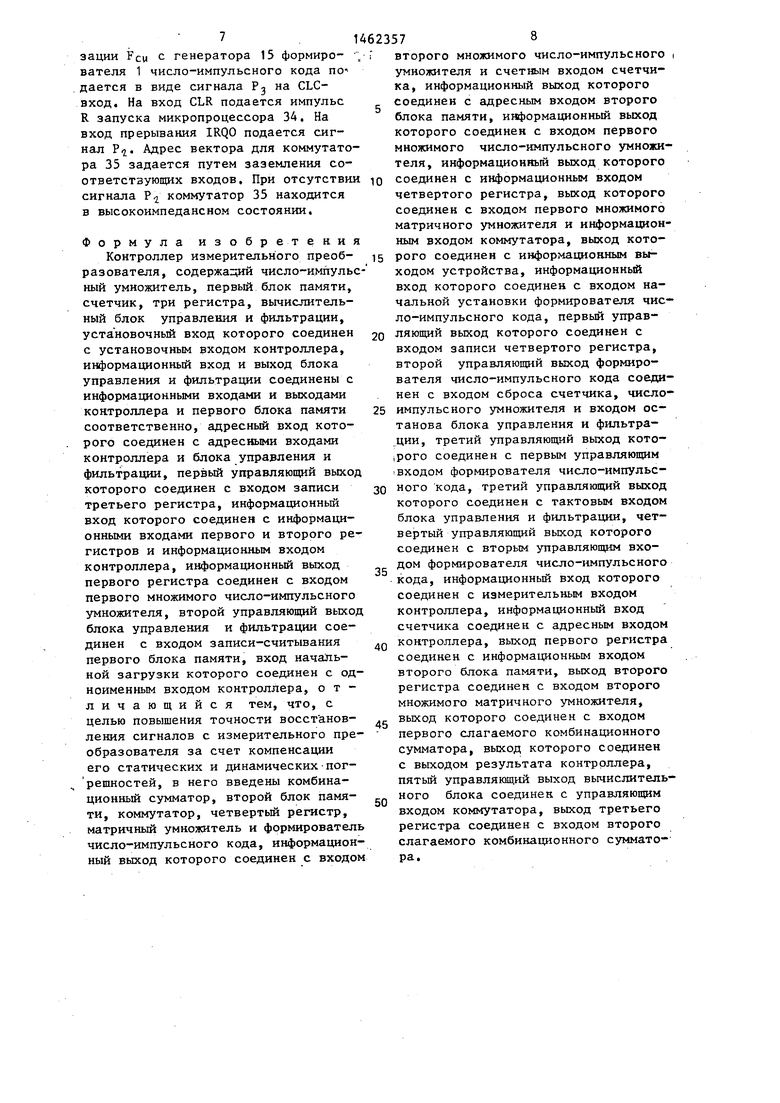

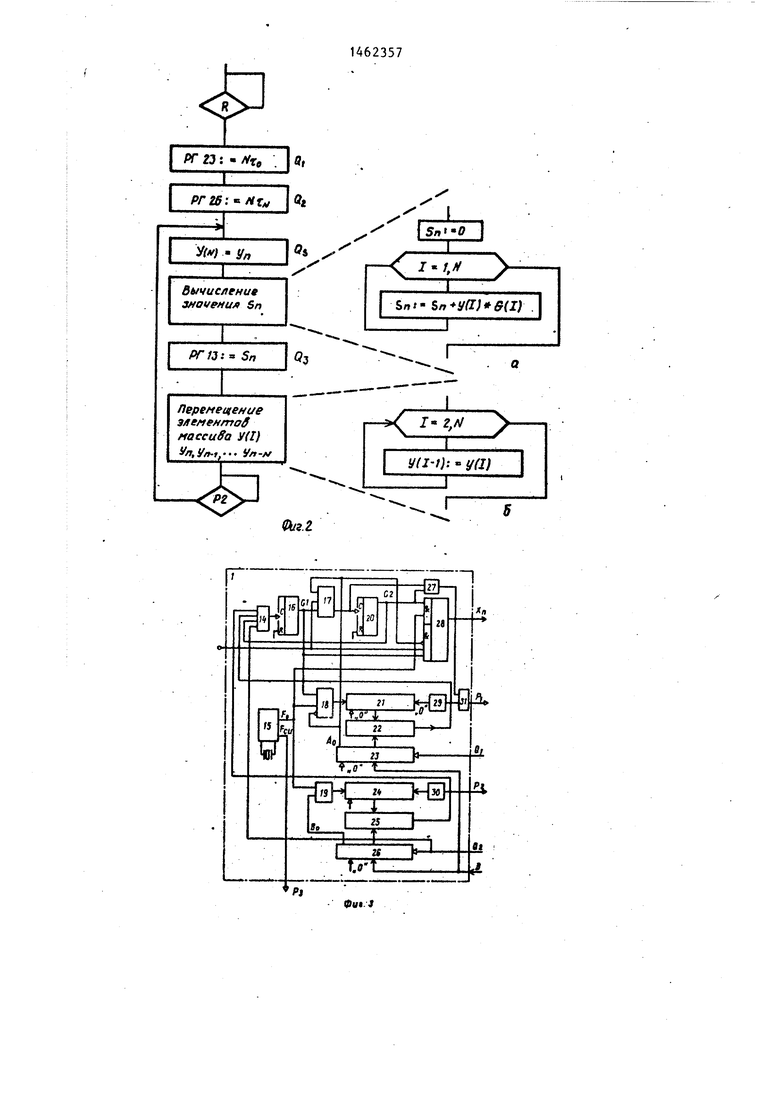

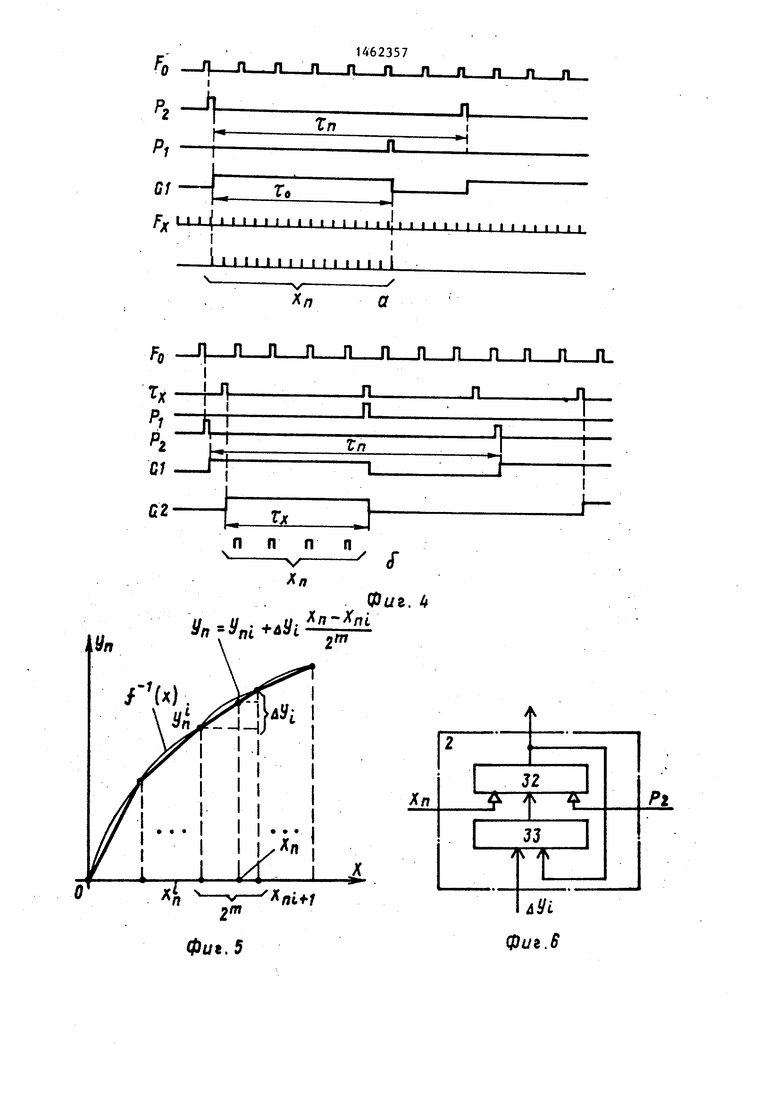

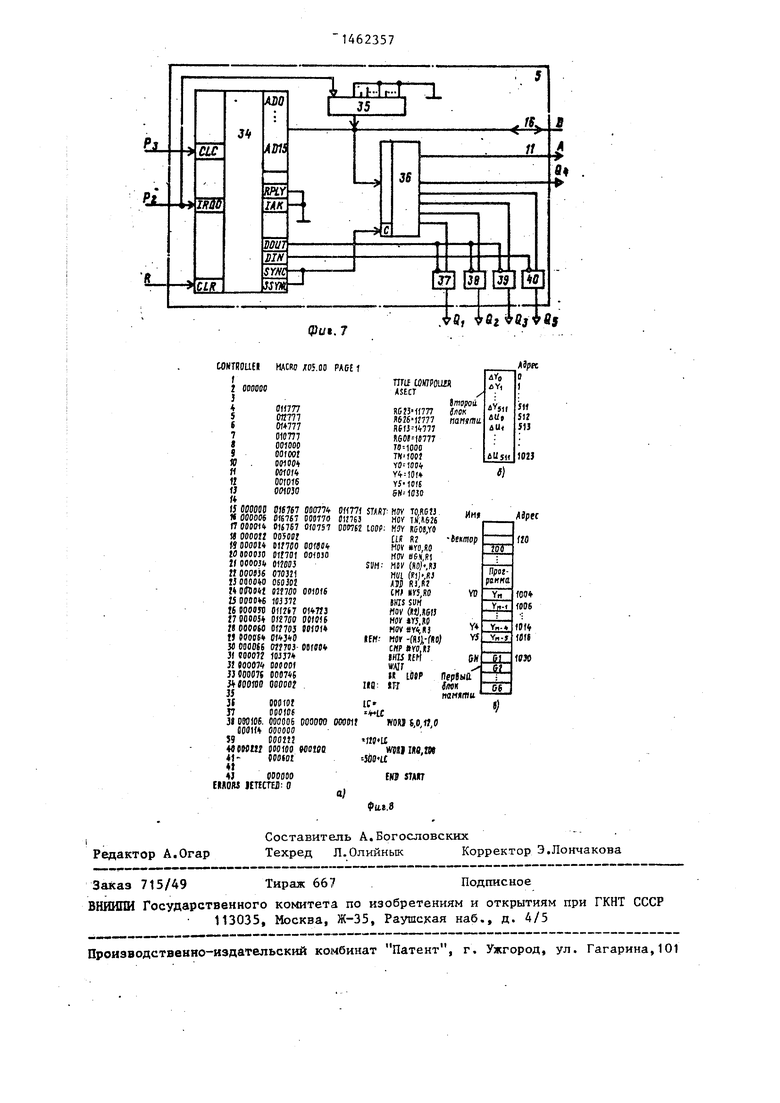

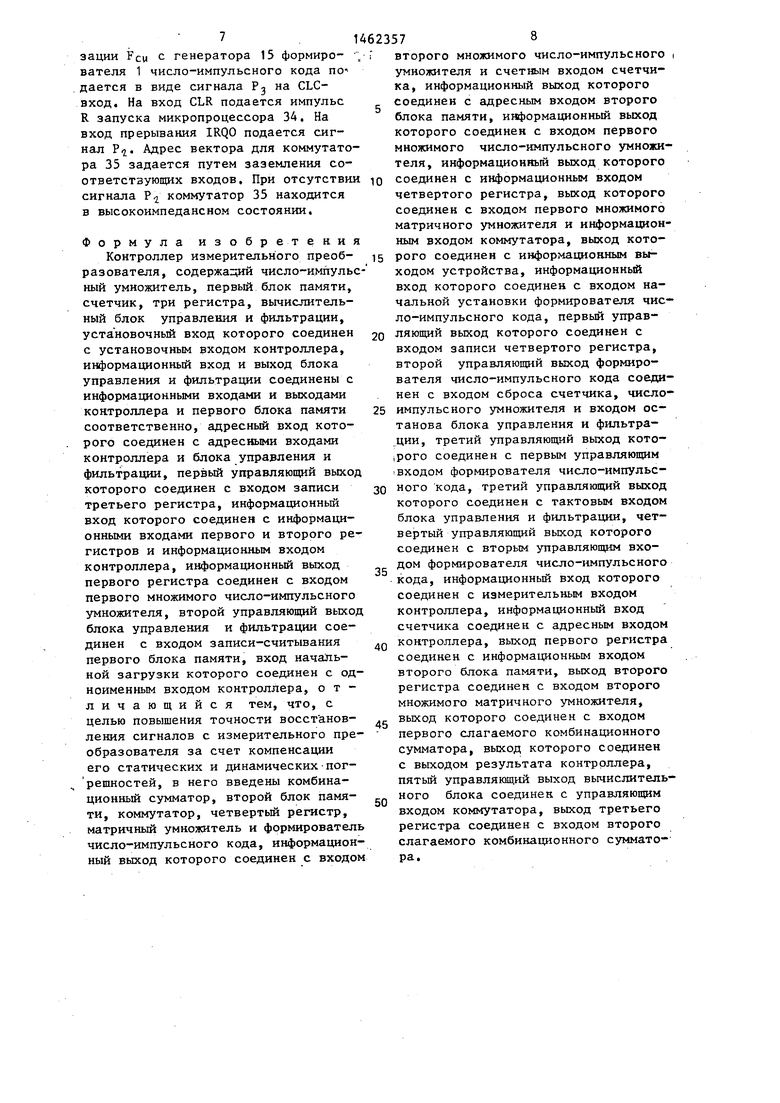

На фиг. 1 представлена схема контроллера измерительного преобра- зователя; на фиг. 2 - алгоритм работы устройства; на фиг. схема формирователя число-импульсного кода; на фиг. А - временные диаграммы формирования число-импульсного кода фиг. 5 - график, поясняющий функциональное преобразование число-импульс но г о кода Х, на фиг. 6.- структура число-импульсного умножителя} на фигi 7 - схема блока управления и фильтрации; на фиг. 8 - вариант программной реализации алго- ритма работы блока управления и фильтрации.

Контроллер измерительного преобразователя содержит формирователь 1 число-импульсного кода, число-им- пульсный умножитель 2, второй блок 3 памяти, счетчик 4, блок 5 управления и фильтрации, первый 6 и четвертый 7 регистры, коммутатор 8, матричный умножитель 9, второй регистр 10, первый блок 11 памяти, комбинационный сумматор 12 и третий регистр 13.-

Число-импульсный формирователь 1 (фиг. 3) образуют четырехвходовый элемент ШШ 14, генератор 15 импульсов, первый триггер 16, элементы И 17-19, второй триггер 20, первый счетчик 21, первая схема 22 сравне- ния, первый регистр 23, второй счетчик 24, вторая схема 25 сравнения, второй регистр 26, элемент И 27, элемент 2И-ИЛИ 28, элементы 29 и 30 :задержки и элемент ИЛИ 31.

Блок 5 (фиг. 7) содержит микро- процессор 34, коммутатор 35, регистр 36 и коммутаторы 37-40.

Контроллер измерительного преобразователя при обработке входного сигнала, представленного в виде частоты FX ипи периода fx следования импульсов, реализует соотношение нерекурсивного фильтра I

Z, Eg.Y .,(1)

/ ° . приведенное к виду

Zh- SoY + ig ..Y..,(2)

8oYn + Xgj.-Y,,.y,

где g(,, §1, , ,..,.,, g f коэффициенты, импульсно переходной характеристики, компенсируняцей динамику измерительного преобразователя} Yn f (Xj дискретная функция,об- ; ратная статической нелинейности измеритель- кого преобразователя. Дискретное значение Хл, аргумента функции формируется в п-е моменты j времени в виде число-импульсного кода формирййателем 1 число-импульсного кода:

Хп-

(3)

(при измерении входного сигнала как частоты) или

3v-F

(4)

(при измерении входного сигнала как периода) путем подсчета количества импульсов частоты Р, за образцовый интервал времени Т первом случае или количества импульсов образцовой частоты F о в периоде Т у во втором./ .

Число-импульсный код Х, поступая на число-импульсные операционные блоки 2 и 4, преобразуется в двоичный код Y по соотношению кусочно- линейной аппроксимации функции

у V .

Y - У + ЛУ Ь hi i 2

(5)

| название | год | авторы | номер документа |

|---|---|---|---|

| Контроллер измерительного преобразователя | 1988 |

|

SU1541632A1 |

| Частотный анализатор | 1990 |

|

SU1798630A1 |

| Число-импульсное линеаризующее устройство с масштабированием | 1983 |

|

SU1109759A1 |

| Цифровой преобразователь координат | 1981 |

|

SU960834A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1984 |

|

SU1238078A1 |

| Устройство для интерполяции | 1984 |

|

SU1171807A1 |

| Генератор функций | 1984 |

|

SU1241219A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 1999 |

|

RU2159952C1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2120137C1 |

| Генератор сигналов сложной формы | 1985 |

|

SU1280597A1 |

Изобретение относится к автоматике и измерительной технике и может быть использовано в качестве корректирующего звена импульсных и цифровых нелинейных систем управления, а также в составе цифровых измерительных средств для восстановления сигналов частотно-импульсных датчиков при выполнении динамических измерений. Цель изобретения - повышение точности восстановления сигналов с измерительного преобразователя за счет компенсации его статических и динамических погрешностей. Для достижения цели в контроллер, содержапщй число-импульсный умножитель 2, первый блок 11 памяти, счетчик 4, регистры 6, 10, 13, блок 5 управления и фильтрации, дополнительно введены комбинационный сумматор 12, второй блок 3 памяти, ком гутатор 8, четвертый регистр 7, матричный умножитель 9 и формироваг-. тель 1 число-импульсного кода с feo- ответствующими связями. 8 ил. а сл

Число-импульсный умножитель 2 (фиг. 6) состоит ив регистра 32 и сумматора 33.

где

i ent

Х„

(6)

Y. - приращения между узловыми Y , Поэтому принято в режиме частотординатами функции f (X ) (фиг. 5), которые хранятся во втором блоке 3 памяти;

2 - шаг равномерной кусочно- линейной аппроксимации функции f (Xj) (фиг. 5). Одновременно с функциональным преобразованием (5) в течение интервала времени Т осуществляется вычисNлёниё суммы S 2- g -Y p.j с помощью

j: I

блока 5. В результате к моменту окончания периода Т формируются значения Y, и S, которые через регистры 7 и 10 подаются соответственно на матричный умножитель 9 и комбинационный сумматор 12, где окончательно вычисляется результат

10

15

20

ной обработки (3) считать Y

Y. ,

1

а при периодной обработке (4) dY ; uUj- Адресное поле выЗора /3Y или 4U определяется состоянием старшего разряда счетчика 4 (например О - ijY, 1 - ли). Регистр 6 слу- жит для развязки входа данных второго блока памяти 3 с общей шиной данных D контроллера.

Перед началом работы контрсхллера счетчик 4, число-импульсный умножитель 2 обнулены, регистр 6 имеет высокоимпедансное состояние, старший разряд счетчика 4 установлен в соответствии с режимом (3) или (4). В блоке 1 формирования число-импульсного кода уста новлены в О триггеры 16 и 20, счетчики 21 и 24 и регистры 23 и 26, Установлен в О четвертый регистр 7.

g,

Y.+ S,

(7)

Таким образом, в предлагаемом контроллере измерительного преобразователя за счет распараллеливания вычислений совмещены операции функционального преобразования частоты F. в код YP f

-Чх)

и вычисления

N

ЧТО позволяет, ис-

суммы Ц g .Y .,

J-.1 J

пользуя., комбинационные блоки для реализации (7), получить максимально возможное быстродействие при универсальности используемых вычислительных средств.

Контроллер измерительного преобразователя работает следующим образом.

В исходном состоянии устройства в первый блок 11 памяти занесены через вход данных по адресам на входе Адреса значения коэффициентов g,,g ...,g ,,....BN значения кодов образцового интервала NC, интервала дискретизации программа работы блока 5. Ячейки блока 11 памяти, вьделенные для хранения кодов Y,

Y.,Yn.K, установлены в О.

В регистр 10 занесено значение g. Во второй блок 3 памяти по адресам, фиксируемым в счетчике 4,занесены по входу данных с выхода регистра 6 значения коэффициентов ЛУ, /)YY,...

aY

и йи

о

ди ,...,

4Ub. Наличие

двух типов коэффициентов к Ли обусловлено различием кривых f (Х) при периодной и частотной обработке

0

5

0

0

5

ной обработки (3) считать Y

Y. ,

1

а при периодной обработке (4) dY ; uUj- Адресное поле выЗора /3Y или 4U определяется состоянием старшего разряда счетчика 4 (например О - ijY, 1 - ли). Регистр 6 слу- жит для развязки входа данных второго блока памяти 3 с общей шиной данных D контроллера.

Перед началом работы контрсхллера счетчик 4, число-импульсный умножитель 2 обнулены, регистр 6 имеет высокоимпедансное состояние, старший разряд счетчика 4 установлен в соответствии с режимом (3) или (4). В блоке 1 формирования число-импульсного кода уста новлены в О триггеры 16 и 20, счетчики 21 и 24 и регистры 23 и 26, Установлен в О четвертый регистр 7.

По внешнему сигналу R осуществляется запуск блока 5, которьй управ- 5 ляет работой всего устройства и вычисляет значение S. В соответствии с алгоритмом его работы (фиг, 2) в регистры 23 и 26 заносятся коды N Z , N-J сигналами Q и Q соответст- 0 венно. По сигналу Q через элемент ИЛИ 14 триггер 16 устанавливается в 1, т.е. G, 1. -С-этого момента времени при состоянии разряда АС О регистра 23 начинает формироватьг 2 ся интервал времени f хемой, сое-,- тоящей из регистра 23, схемы 22 сравнения, элемента 29 задержки (С,), счетчика 21, на вход которого поступает опорная частота FO че- 0 рез элемент И 18. Потенциалы G, . 1, А р 1 позволяют импульсам входной частоты Г проходить через элемент 2И-ШШ 28 на его выход и далее на число-импульсный умножитель 5 2 счетчик 4. В момент времени, когда код в счетчике 21 достигнет значения кода в регистре 23, на выходе схемы сравнения формируется импульс Р, (фиг. 4а), который через элемент 29 задержки сбрасывает в О счетчик 21 и триггер 16, прекращая формирование импульсов на выходе элемента 2И-ИЛИ 28 и запирая вход опорной частоты на элементе И 18.

Аналогично схемой, состоящей из регистра 26, схемы 25 сравнения, элемент 30 задержки, счетчика 24., элемента И 19, открытого потенциалом в.

7 «о

1, формируется интервал По окончании интервала

h

импульс Р (фиг. 3) снова устанавливает триггер 16 в 1 через элемент ИЛИ 14 и определяет начало очередного интервала дискретизации.

При периодном измерении частоты в каждом интервале дискретизации (режим (4))элемент И 18 заперт потенциалом АС 1, элемент И 17 отк- рьгаается для сигнала.Fjf потенциалами -G , и Ар. Первый же импульс частоты F проходит на счетный вход триггера 20 и по заднему фронту устанавливает его потенциал G в 1, который позволяет импульсам опорной частоты F(5 проходить через элемент 2И-ИП11 28 на ее вьгход .Следующий импульс частоты FX проходит через элементы И 17, ИЛИ 3 в качестве управляющего сигнала Р и по заднему фронту усчп

35

40

танавливает в О триггер 20, запрещая прохождение опорной частоты FO iна выход элемента 28, Триггер 25 :20, в свою очередь, -через элемент I ИЛИ 14 сбрасывает триггер 1.6, Опи санные процессы получения число им

; пульсного кода Х, поясняются временными диаграммами на фиг. 4а, б.

В процессе формирования число-импульсный код поступает с выхода формирователя 1 число-импульсного кода на число-импульсный умножитель

2 и счетчик 4, где происходят следующие действия,

В число-импульсном умножителе 2,

построенном на основе накапливающе- . го сумматора (регистр 32 и комбинационный сумматор 33), каждым импульсом кода Х прибавляется к предьщу- щему значению регистра 32 величина ДУ:/2 (деление на m осуществлено путем подачи -AY; на сумматор 33 со сдвигом на m разрядов вправо),опре-. деляющее единичное приращение функции f (X„) на каждом i-м участке аппроксимации. Переход от участка к участку и адресация значений -ЗУ, которые выбираются из второго блока 3 памяти, осуществляется с помощью счетчика 4. Первые его m младших разрядов определяют длину участка аппроксимации и используются как делитель частоты на 2, реализующий соотношение (6), а следующие разряды являются ад;ресом i и подаются на адресный вход второго блока 3 памя ти. Таким образом, при поступлении

14623576

импульсов Хп на блоки 2 и 4 в регистре 31 происходит развертывание функции f (Xf,) от О до Хп (фиг. 5)

с за интервал времени Т, , По окончании Т двоичный код Yf, из регистра 32 число-импульсного умножителя 2 переписывается в четвертьш регистр 7 импульсом Р, .

10 В том же интервале времени Т после установки регистров 23 и 26 одно- временно с преобразованием FX в Y блоком 5 выполняются пересылки кодов и арифметические операции, показан15 ные на блок-схеме алгоритма (фиг.2). Сначала осуществляется запись кода Yfi.t (это результат функционально-- го преобразования F, в Y -1 в предыдущем п - -I-M такте дискретиза20 ции) четвертого регистра 7 через коммутатор 8 в первый блок 11 памяти в ячейку YO, Затем вычисляется значение S , (фиг, 2а), которое передается импульсом QJ в третий регистр 13, Далее блок 5 осуществляет перемеще1гие в массиве Y(i) кодов

Yn-,

ti-i j

Y h-N (фиг, 26) j

хранящихся в первом блоке 11 памяти, обеспечивая подготовку к расчету

30 S

|И1

в следующем такте п + 1. После

этого блок 5 переходит в ожидание импульса дискретизации P/j, по которому сбрасывается в О регистр 32 число-импульсного умножителя 2,счетчик 4, а через второй коммутатор 35 (фиг. 7) формируется вектор прерывания блока 5, Вектор передает управление на повторение anropuTt-fa (фиг. 2).

Один из вариантов реализации алгоритма работы блока 5 на языке ассемблер приведен на фиг, 8,

Матричный умножитель 8, исполь- зуемьй в устройстве, представляет собой ПЗУ емкостью слов, где ml - разрядность кода Yj,, m2,- разрядность кода g р,

На фиг, 7 приведен вариант пост-, роения блока 5 на основе микропроцессора 34 серии 1-801, где для разделения общей шины данных D и адресной шины А использован вспомогательный регистр 36, в который запись адреса осуществляется по сигналу 55 SYNC. Управляющие сигналы формируются по состоянию свободных старших разрядов регистра 36, стро- бируемых сигналами DOUT, DIN через элементы И 37-40. Частота синхрони45

50

Yn-,

ti-i j

Y h-N (фиг, 26) j

хранящихся в первом блоке 11 памяти, обеспечивая подготовку к расчету

5

0

0 S

|И1

в следующем такте п + 1. После

этого блок 5 переходит в ожидание импульса дискретизации P/j, по которому сбрасывается в О регистр 32 число-импульсного умножителя 2,счетчик 4, а через второй коммутатор 35 (фиг. 7) формируется вектор прерывания блока 5, Вектор передает управление на повторение anropuTt-fa (фиг. 2).

Один из вариантов реализации алгоритма работы блока 5 на языке ассемблер приведен на фиг, 8,

Матричный умножитель 8, исполь- зуемьй в устройстве, представляет собой ПЗУ емкостью слов, где ml - разрядность кода Yj,, m2,- разрядность кода g р,

На фиг, 7 приведен вариант пост-, роения блока 5 на основе микропроцессора 34 серии 1-801, где для разделения общей шины данных D и адресной шины А использован вспомогательный регистр 36, в который запись адреса осуществляется по сигналу 5 SYNC. Управляющие сигналы формируются по состоянию свободных старших разрядов регистра 36, стро- бируемых сигналами DOUT, DIN через элементы И 37-40. Частота синхрони5

0

зации FCM с генератора 15 формиро- вателя 1 число-импульсного кода по дается в виде сигнала РЗ нэ CLC- вход. На вход CLR подается импульс R запуска микропроцессора ЗА. На вход прерывания IRQO подается сигнал . Адрес вектора для коммутатора 35 задается путем заземления со- ответстзующих входов. При отсутствии сигнала Р- коммутатор 35 находится в высокоимпедансном состоянии.

Формула изобретения

Контроллер измерительного преоб- разователя, содержаний число-импульсный умножитель, первый блок памяти, счетчик, три регистра, вычислительный блок управления и фильтрации, установочньй вход которого соединен с установочным входом контроллера, информационный вход и выход блока управления и фильтрации соединены с информационными входами и выходами контроллера и первого блока памяти соответственно, адресный вход которого соединен с адресными входами контроллера и блока управления и фильтрации, первый управляющий выход которого соединен с входом записи третьего регистра, информационный вход которого соединен с информационными входами первого и второго регистров и информационным входом контроллера, информационный выход первого регистра соединен с входом первого множимого число-импульсного умножителя, второй управляющий выход блока управления и фильтрации соединен с входом записи-считывания первого блока памяти, вход начальной загрузки которого соединен с одноименным входом контроллера, отличающийся тем, что, с целью повышения точности восст анов- ления сигналов с измерительного преобразователя за счет компенсации его статических и динамическихпог- решностей, в него введены комбинационный сумматор, второй блок памя- ти, коммутатор, четвертый регистр, матричный умножитель и формирователь число-импульсного кода, информационный выход которого соединен с входом

5 0 5 о Q g

5

второго множимого число-импульсного I умножителя и счетным входом счетчика, информационный выход которого соединен с адресным входом второго блока памяти, информационный выход которого соединен с входом первого множимого число-импульсного умножителя, информационный выход которого соединен с информационным входом четвертого регистра, выход которого соединен с входом первого множимого матричного умножителя и информационным входом коммутатора, выход которого соединен с информационным выходом устройства, информационный вход которого соединен с входом начальной установки формирователя число-импульсного кода, первый управляющий вькод которого соединен с входом записи четвертого регистра, второй управляющий выход формирователя число-импульсного кода соединен с входом сброса счетчика, число- импульсного умножителя и входом останова блока управления и фильтрации, третий управляю1ций выход кото- iporo соединен с первым управляющим iвходом формирователя число-импульсного кода, третий управляющий выход которого соединен с тактовым входом блока управления и фильтрации, четвертый управляющий выход которого соединен с вторым управляющим входом формирователя число-импульсного кода, информационный вход которого соединен с измерительным входом контроллера, информационный вход счетчика соединен с адресным входом контроллера, выход первого регистра соединен с информационным входом второго блока памяти, выход второго регистра соединен с входом второго множимого матричного умножителя, выход которого соединен с входом первого слагаемого комбинационного сумматора, выход которого соединен с выходом результата контроллера, пятьм управляющий выход вычислительного блока соединен, с управляющим входом коммутатора, выход третьего регистра соединен с входом второго слагаемого комбинационного сумматора.

I ЙГгД; //TO |g

I P/- g;«yyfv

I yw-y/, g

- -HT----I

x

вычисление SMOveMUA Sn

Й/г.2

i5/i «Q I

I .ff

(I)ff(I)

p- I г/Г

ya-/;.- - y/x;

- 1462357

0 -Т П ППп п q п П

гЧ

Гп

PI-T

« М I

/V, -J -п-п-п-пп п п п п п п

Хл

J2

д ;

Рг

J3

/ f

лУ1 фиг,6

CONTROUfI HACfW TCS.OO

ттп опт

Of+777 015777 051000 OOfOO

оят motit oorots оивзо

(J OMOSfl 0)ff767 0(1077 V N 000006 IH6767 000770 f7JOOI7U 0)S767 Of0757

И оооиг 00500

fJOOOOH OOfSO Woooojo Bomo

H 0000 01ШЗ W050JJ« 070321

Hojoow оболг ttomio; дгпло mm

i50080« Ш37г

16 000J5t) (ff7S7

1700005 ШПгО OdfCU

гЮОООИ Of 703 80JOf

t) ОСОСГН

50 0000(6 OOfCO

3( C0007 1QJJ7

32 600074 OOIOOf

5300007( 00074$

nioom 00000

35

Jt

57

000fOf 000№

л mm mom mm

COOIH000000

яDfffl«2

4d{Hm000190 tCHWu

1-tOOIOl

«t

43000000

ок кпсти: о

1C

OWOI WOUJ i,e W 5

-MO U

Ш1 ue,m

fW STAIT

0/

-MO U

Ш1 ue,m

fW STAIT

$u.t.d

| Число-импульсное линеаризирующее устройство с масштабированием | 1984 |

|

SU1201847A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Генератор функций | 1984 |

|

SU1241219A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-02-28—Публикация

1987-02-02—Подача