Изобретение относится к вычислительной технике, в частности, касается схем синхронизации резервных каналов при несинхронном их тактировании и может быть использовано в высоконадежных цифровых устройствах.

Известен резервированный делитель частоты (а.с. СССР №1608793), содержащий в каждом канале деления частоты первый сдвиговый регистр, тактовый вход которого соединен с входной шиной, инверсный выход последнего разряда - с соответствующим входом мажоритарного элемента каждого канала деления частоты, выход которого подключен к выходной шине, и с первым входом элемента неравнозначности своего канала деления частоты, выход которого соединен с первым входом элемента И, второй сдвиговый регистр, информационный вход которого соединен с выходной шиной, прямой выход последнего разряда - с информационным входом первого сдвигового регистра, прямой выход предпоследнего разряда которого соединен с вторым входом элемента неравнозначности, тактовый вход - с вторым входом элемента И, выход которого соединен с тактовым входом второго сдвигового регистра.

Известен резервированный делитель частоты (а.с. СССР №1774495), содержащий в каждом канале деления частоты два регистра сдвига, первый из которых содержит n триггеров, а второй - два триггера, элемент неравнозначности, элемент И и мажоритарный элемент, тактовый вход первого регистра соединен с тактовым входом делителя и с первым входом элемента И, второй вход которого соединен с выходом элемента неравнозначности, а выход - с тактовым входом второго регистра, информационный вход которого соединен с выходом мажоритарного элемента, а прямой выход - с информационным входом первого регистра, инверсный выход которого соединен с первым входом элемента неравнозначности, первый регистр содержит n≥3, второй вход элемента неравнозначность соединен с информационным входом (n-2)-го триггера первого регистра, а входы мажоритарных элементов делителя подключены к инверсным выходам (n-1)-х триггеров первых регистров.

Оба вышеперечисленные резервированные делители частоты являются кольцевыми делителями и для делителей частоты с большим коэффициентом деления требуется большое количество триггеров (так для деления на 8-4 триггера, а для деления на 32768-16384 триггера), что усложняет схему и понижает надежность.

Задачей изобретения является повышение коэффициента деления и надежности делителей частоты при асинхронных входных сигналах.

Указанная цель достигается тем, что в резервированный делитель частоты, содержащий в каждом канале деления частоты два регистра сдвига, первый из которых содержит n≥3 триггеров, а второй - два триггера, элемент неравнозначности, элемент И и мажоритарный элемент, тактовый вход канала делителя соединен с тактовым входом первого регистра и с входом элемента И, второй вход которого соединен с выходом элемента неравнозначности, а выход - с тактовым входом второго регистра, информационный вход которого соединен с выходом мажоритарного элемента, а прямой выход - с входом элемента неравнозначности и с информационным входом первого регистра, инверсный выход n-го триггера которого соединен с вторым входом элемента неравнозначности, а входы мажоритарных элементов делителя соединены с инверсными выходами (n-1)-х триггеров первых регистров, в каждый канал введены элемент И-НЕ, счетчик, второй мажоритарный элемент, второй элемент неравнозначности, инвертор, в каждом канале выход мажоритарного элемента соединен с первым входом элемента И-НЕ, второй вход которого соединен с выходом инвертора, а выход с счетным входом счетчика, старший разряд которого соединен с входом второго элемента неравнозначности и входом второго мажоритарного элемента своего канала и соответствующими входами вторых мажоритарных элементов других каналов, а выход второго мажоритарного элемента соединен с вторым входом второго элемента неравнозначности и выходной шиной, выход второго элемента неравнозначности соединен с входом инвертора.

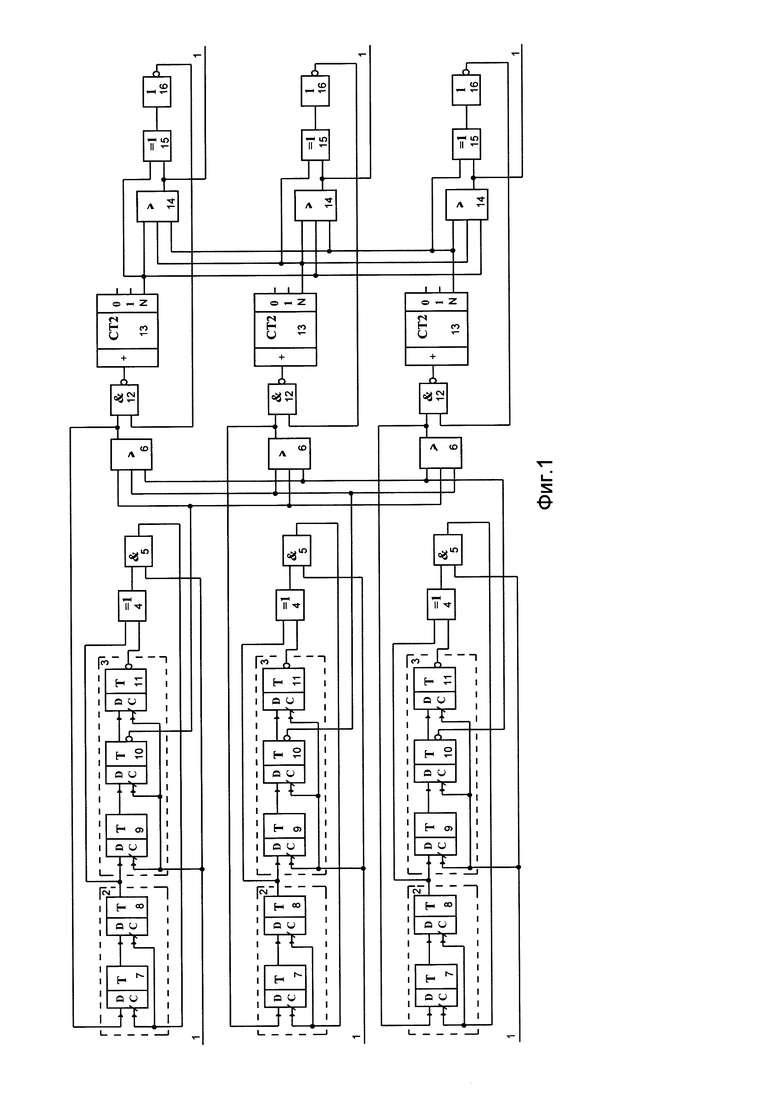

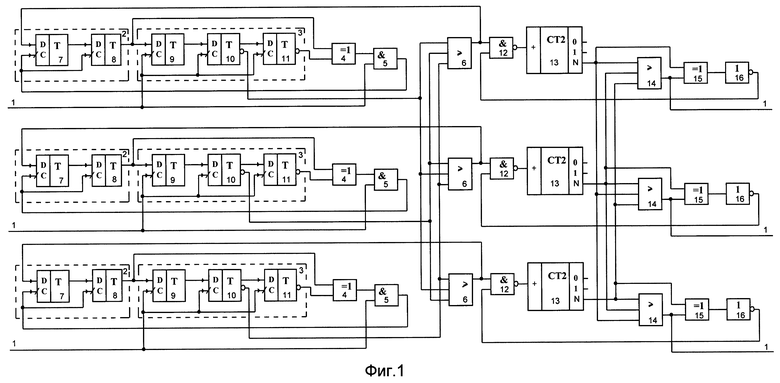

На фиг. 1 представлена структурная схема резервированного делителя частоты.

Схема резервированного делителя частоты в каждом канале содержит:

1 - тактовый вход канала делителя, 2 - второй регистр сдвига, 3 - первый регистр сдвига, 4 - элемент неравнозначности, 5 - элементы И, 6 - мажоритарный элемент, 7 - первый триггер второго регистра, 8 - второй триггер второго регистра, 9 - (n-2)-триггер первого регистра, 10 - (n-1)-триггер первого регистра, 11 - n - триггер первого регистра, 12-элемент И-НЕ, 13-счетчик, 14-второй мажоритарный элемент, 15 - второй элемент неравнозначности, 16 - инвертор, 17 - выходная шина.

В каждом канале тактовый вход канала делителя (1) соединен с тактовым входом первого регистра (3) и с первым входом элемента И (5), второй вход которого соединен с выходом элемента неравнозначности (4), а выход - с тактовым входом второго регистра (2). Информационный вход второго регистра (2) соединен с выходом мажоритарного элемента (6), а прямой выход - с входом элемента неравнозначности (4) и с информационным входом первого регистра (3). Инверсный выход первого регистра сдвига (3) от n-го триггера соединен с вторым входом элемента неравнозначности (4). Входы мажоритарного элемента (6) делителя соединены с инверсными выходами (n-1)-х триггеров первых регистров (3), а выход - с входом элемента И-НЕ (12). Второй вход элемента И-НЕ (12) соединен с выходом инвертора (16), а выход с счетным входом счетчика (13). Старший разряд счетчика (13) соединен с входом второго элемента неравнозначности (15) и входом второго мажоритарного элемента (14) своего канала и соответствующими входами вторых мажоритарных элементов (14) других каналов. Выход второго мажоритарного элемента (14) соединен с вторым входом второго элемента неравнозначности (15) и выходной шиной (17). Выход второго элемента неравнозначности (15) соединен с входом инвертора (16).

Устройство работает следующим образом.

В исходном состоянии, после включения питания или после сбоя, триггеры и счетчики устанавливаются в произвольное состояние, при этом на выходах мажоритарных элементов (6) всех каналов всегда будут одинаковые логические значения (лог.0 или лог.1).

Тактовые входы каналов (1), вторые (2), первые (3) регистры сдвига, элемент неравнозначности (4), элементы И (5), мажоритарный элемент (6), охваченные обратной связью, представляют мажоритарно резервированный кольцевой делитель частоты с коэффициентом деления равным 2⋅(n+2), где n≥3 число триггеров первого сдвигового регистра (3). Первый сдвиговый регистр (3), элемент неравнозначности (4), элементы И (5) формируют два импульса двух тактов для записи и хранения в триггерах (7, 8) второго регистра сдвига (2) синхронного значения выходного сигнала делителя, сформированного на мажоритарных элементах (6). Далее это значение сдвигается на n триггерах первого сдвигового регистра (3) до формирования двух тактов записи следующего полупериода делителя. Синхронное значение вырабатывается в пределах среднего значения периода асинхронных входных сигналов на тактовых входах каналов (1).

По тактовым входам каналов (1) сигналы приходят несинхронно на тактовый вход первого регистра сдвига (3) и вход элемента И (5). Тактовые сигналы устанавливают триггера 9, 10, 11 в одно произвольное значение (a1), а инверсные выходы триггеров 10 и 11 - в противоположное инверсное значение  В результате на выходах мажоритарных элементов (6), т.е. на выходе кольцевого делителя, формируется среднее для каналов значение

В результате на выходах мажоритарных элементов (6), т.е. на выходе кольцевого делителя, формируется среднее для каналов значение  за такт до записи во вторые регистры сдвига (2). На входах элементов неравнозначности (4) устанавливаются противоположные значения сигналов, а на выходах - значение лог.1, что разрешает прохождение тактовых сигналов через элементы И (5) на тактовые входы вторых регистров сдвига (2) в следующем такте. Тактовые сигналы первого, второго триггеров второго регистра (7, 8) устанавливают ранее сформированное инверсное значение

за такт до записи во вторые регистры сдвига (2). На входах элементов неравнозначности (4) устанавливаются противоположные значения сигналов, а на выходах - значение лог.1, что разрешает прохождение тактовых сигналов через элементы И (5) на тактовые входы вторых регистров сдвига (2) в следующем такте. Тактовые сигналы первого, второго триггеров второго регистра (7, 8) устанавливают ранее сформированное инверсное значение  при этом на входах элементов неравнозначности (4) устанавливаются равнозначные значения сигналов, а на выходах - значение лог.0, что запрещает прохождение тактовых сигналов через элементы И (5) на тактовые входы вторых регистров сдвига (2). Таким образом, самоустановка в этой части схемы (триггеры 9, 10, 11, 7, 8) при совпадении состояний одноименных триггеров разных каналов производится за 5 тактов и менее для n=3. В случае несовпадения состояний одноименных триггеров разных каналов возникает ситуация несовпадения входа и выхода мажоритарного элемента (6) в одном из каналов. Несовпадение одного из каналов не влияет на выходные значения мажоритарных элементов (6) и работу делителя. До установка значения

при этом на входах элементов неравнозначности (4) устанавливаются равнозначные значения сигналов, а на выходах - значение лог.0, что запрещает прохождение тактовых сигналов через элементы И (5) на тактовые входы вторых регистров сдвига (2). Таким образом, самоустановка в этой части схемы (триггеры 9, 10, 11, 7, 8) при совпадении состояний одноименных триггеров разных каналов производится за 5 тактов и менее для n=3. В случае несовпадения состояний одноименных триггеров разных каналов возникает ситуация несовпадения входа и выхода мажоритарного элемента (6) в одном из каналов. Несовпадение одного из каналов не влияет на выходные значения мажоритарных элементов (6) и работу делителя. До установка значения  в триггера 9, 10, 11 первого регистра не совпавшего канала происходит во время работы исправных каналов не влияя на работу делителя. Установленное в триггерах 8 значение

в триггера 9, 10, 11 первого регистра не совпавшего канала происходит во время работы исправных каналов не влияя на работу делителя. Установленное в триггерах 8 значение  устанавливается тактовыми сигналами (1) первых регистров (3) в триггеры 9, 10, 11.

устанавливается тактовыми сигналами (1) первых регистров (3) в триггеры 9, 10, 11.

На такте записи триггеров 10 на инверсных выходах и на выходах мажоритарных элементов (6) формируется значение, инверсное предыдущему тактированному значению выхода мажоритарных элементов (6). Новое инверсное значение сдвигается триггерами 11, 7, 8, 9, 10 следующими 5 тактами (n+2 такта) до следующего инвертирования и далее процесс повторяется, а на выходах мажоритарных элементов (6) формируются синхронные сигналы с коэффициентом деления, равным удвоенной сумме триггеров первого регистра сдвига и второго регистра сдвига (n1), 2⋅(n+2).

С выходов мажоритарных элементов (6) синхронные сигналы далее поступают также на входы элементов И-НЕ (12).

В исходном состоянии выходные значения старших разрядов N счетчиков (13) во всех каналах совпадают, поступают на входы элементов неравнозначности (15) и входы вторых мажоритарных элементов (14), входные и выходные значения вторых мажоритарных элементов (14) совпадают, на входах элементов неравнозначности (15) формируются равные значения, на выходе - лог.0, на выходах инверторов (16) формируется лог.1, которая поступает на вторые входы элементов И-НЕ (12) и разрешает прохождение синхронных выходных сигналов мажоритарных элементов (6) на счетные входы счетчиков (13). Счетчики (13) производят двоичный счет периодов входных синхронных сигналов и на выходе старшего разряда N формируют выходные синхронные сигналы с коэффициентом деления, равным 2N+1, где N разрядность старшего разряда может иметь значения 0, 1, 2, 3, …, или 2n2, где n2=N+1 число счетных триггеров счетчика.

При сбое в счете в одном из каналов, когда на выходах старших разрядов устанавливается состояние противоположное состоянию на выходах вторых мажоритарных элементов (14), на выходах вторых элементов неравнозначности (15) устанавливается единичное состояние, а на выходах инверторов (16) - нулевое. Элемент И-НЕ (12) закрывается и на счетный вход счетчика (13) в сбившемся канале не поступают импульсы, а в исправных каналах продолжается счет. Когда исправные каналы досчитывают до значения старшего разряда N сбившегося канала в текущем или следующем периоде старшего разряда N, значение старшего разряда становится равным состоянию на выходах вторых мажоритарных элементов (14), на выходах вторых элементов неравнозначности (15) устанавливается нулевое состояние, а на выходах инверторов (16) - единичное. Элемент И-НЕ (12) открывается и на счетный вход счетчика (13) в ранее сбившемся канале поступают импульсы и канал продолжает синхронно считать вместе с исправными каналами.

Предлагаемый резервированный делитель частоты имеет коэффициент деления fвх/fвых=2⋅n1⋅2N+1=2⋅n1⋅2n2.

Введение счетчиков (13), элементов И-НЕ (12), вторых мажоритарных элементов (14), элементов неравнозначности (15), инверторов (16) позволило повысить коэффициент деления резервированного делителя частоты в n1⋅2n2/(nl+n2) раз по отношению к резервированному делителю на регистрах сдвига.

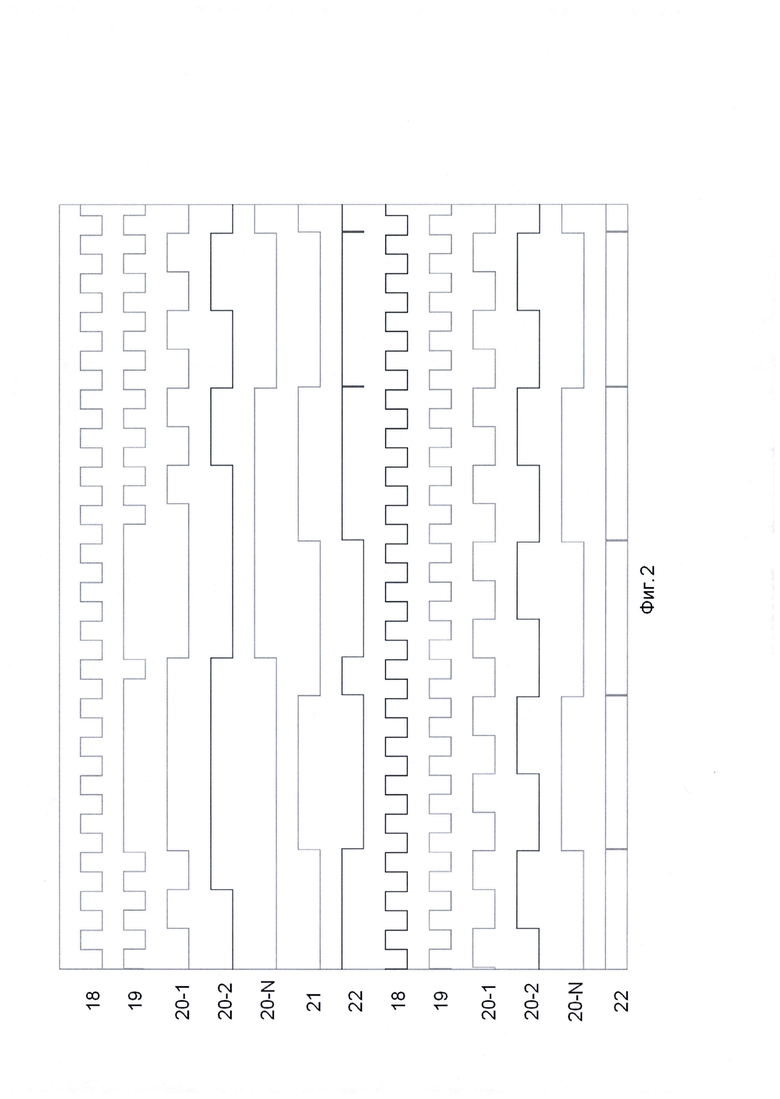

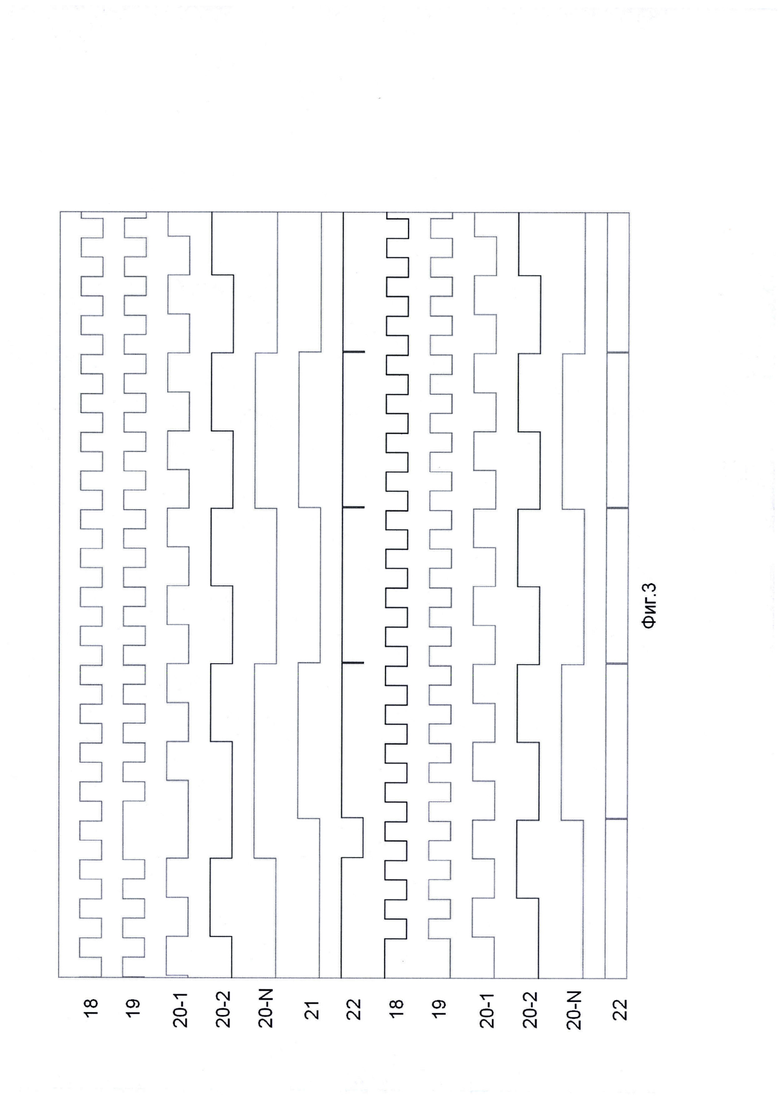

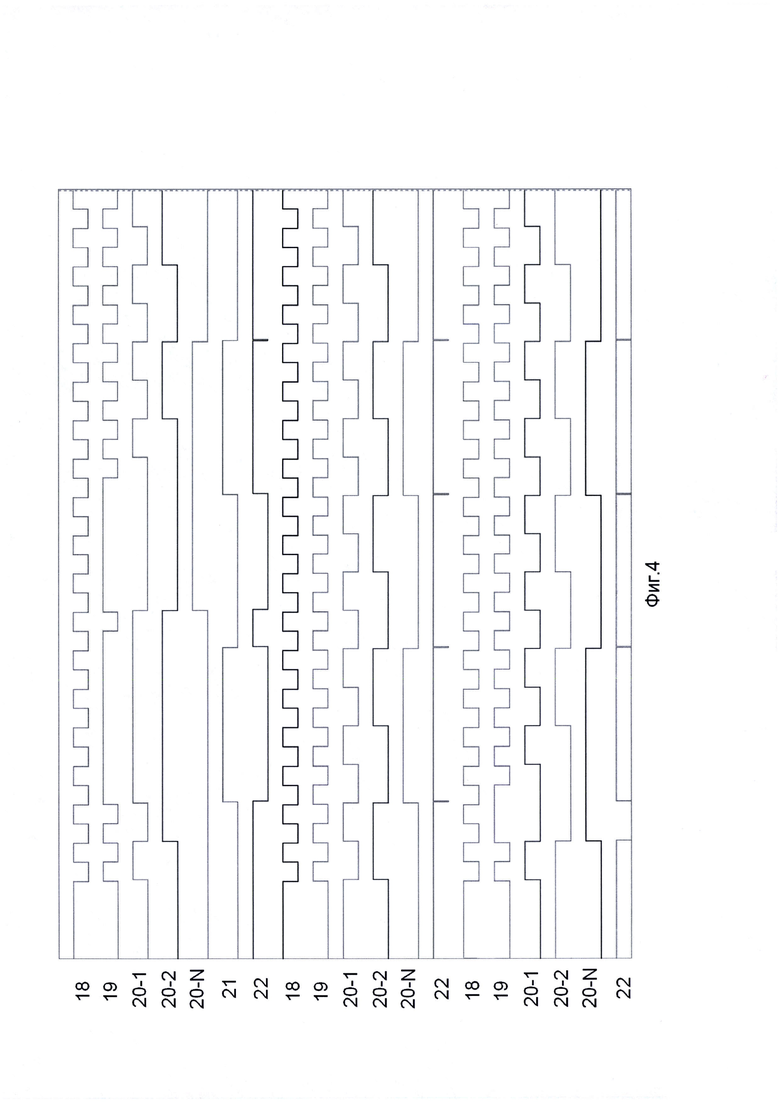

На фиг. 2…4 представлены временные диаграммы, поясняющие принцип работы предлагаемого устройства, где:

18 - сигналы на выходах мажоритарных элементов 6,

19 - сигналы на выходах элементов И-НЕ 12,

20-1 - сигналы на выходах первых разрядов счетчиков 13,

20-2 - сигналы на выходах вторых разрядов счетчиков 13,

20-N - сигналы на выходах старших разрядов счетчиков 13,

21- сигналы на выходах вторых мажоритарных элементов 14 и на выходных шинах 17,

22 - сигналы на выходах инверторов 16.

На фиг. 2 представлены временные диаграммы, где счетчики 13 в сбившемся канале установлены в состояние ООО, а в исправных каналах - в состояние 001.

На фиг. 3 представлены временные диаграммы, где счетчик 13 в сбившемся канале установлен в состояние 001, а в исправных каналах - в состояние 000.

На фиг. 4 представлены временные диаграммы при расфазировке всех каналов.

Как видно, из временных диаграмм время восстановления после сбоя составляет от одного до двух периодов старших разрядов делителя.

Таким образом, происходит фазирование каналов делителя при асинхронных входных сигналах.

Временные диаграммы фиг. 2-4 являются результатом компьютерного моделирования и подтверждают возможность осуществления заявленной схемы и достижения технического результата. Проведенные испытания макета схемы подтвердили результаты моделирования и показали осуществимость и работоспособность схемы резервированного делителя частоты в рабочих диапазонах напряжения питания и температуры.

Техническим результатом является построение делителей частоты с увеличенным коэффициентом деления и большей надежностью при асинхронных входных сигналах.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированный делитель частоты | 1990 |

|

SU1780187A1 |

| МАЖОРИТАРНО-РЕЗЕРВИРОВАННЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2015617C1 |

| Резервированный делитель частоты следования импульсов | 1981 |

|

SU953744A1 |

| Резервированный делитель частоты | 1983 |

|

SU1109910A1 |

| Трехканальное резервированное запоминающее устройство | 1984 |

|

SU1215133A1 |

| Резервированный счетчик импульсов | 1983 |

|

SU1089762A1 |

| Устройство фазовой автоподстройки частоты | 1990 |

|

SU1829115A1 |

| Многоканальное резервированное счетное устройство | 1983 |

|

SU1099389A1 |

| Резервированный счетчик импульсов | 1981 |

|

SU987815A1 |

| Резервированный делитель-формирователь | 1986 |

|

SU1368982A1 |

Изобретение относится к цифровой технике в делителях частоты с большим коэффициентом деления при асинхронных входных сигналах и может быть использовано в космической, авиационной, кораблестроительной и других отраслях. Техническим результатом является построение делителей частоты с увеличенным коэффициентом деления и большей надежностью при асинхронных входных сигналах. Устройство содержит в каждом канале первый и второй регистры сдвига, элемент неравнозначности, элемент И, в него введены счетчик, второй мажоритарный элемент, второй элемент неравнозначности, инвертор, элемент И-НЕ. 4 ил.

Резервированный делитель частоты, содержащий в каждом канале деления частоты два регистра сдвига, первый из которых содержит n≥3 триггеров, а второй - два триггера, элемент неравнозначности, элемент И и мажоритарный элемент, тактовый вход канала делителя соединен с тактовым входом первого регистра и с первым входом элемента И, второй вход которого соединен с выходом элемента неравнозначности, а выход - с тактовым входом второго регистра, информационный вход которого соединен с выходом мажоритарного элемента, а прямой выход - с первым входом элемента неравнозначности и с информационным входом первого регистра, инверсный выход n-го триггера которого соединен с вторым входом элемента неравнозначности, а входы мажоритарных элементов делителя соединены с инверсными выходами (n-1)-х триггеров первых регистров, отличающийся тем, что в каждый канал введены элемент И-НЕ, счетчик, второй мажоритарный элемент, второй элемент неравнозначности, инвертор, в каждом канале выход мажоритарного элемента соединен с входом элемента И-НЕ, второй вход которого соединен с выходом инвертора, а выход - со счетным входом счетчика, старший разряд которого соединен с первым входом второго элемента неравнозначности и входом второго мажоритарного элемента своего канала и соответствующими входами второго мажоритарного элемента других каналов, а выход второго мажоритарного элемента соединен со вторым входом второго элемента неравнозначности и выходной шиной, выход второго элемента неравнозначности соединен с входом инвертора.

| Резервированный делитель частоты | 1991 |

|

SU1774495A1 |

| Резервированный делитель частоты | 1988 |

|

SU1608793A1 |

| Резервированный делитель частоты | 1990 |

|

SU1780187A1 |

| Делитель частоты следования импульсов с программным управлением | 1982 |

|

SU1027831A1 |

| JP 2013009368 A, 10.01.2013 | |||

| US 8736317 B2, 27.05.2014 | |||

| РЕЗЕРВИРОВАННЫЙ СЧЕТЧИК | 2003 |

|

RU2264690C2 |

Авторы

Даты

2022-12-05—Публикация

2022-06-15—Подача