менно соединен с вторым управляющим входом четвертого ключевого элемента входом считывания выходного кодового регистра и входом триггера, первый выход которого подключен к управляющему входу первого ключевого элемента, а второй - к управляющему входу второго ключевого элемента и входу третьего ключевого элемента, второй крайний вывод декадного делителя соединен с одноименными полю12301

сами источников опорного напряжения старшего и младших разрядов и первым выходом коммутатора, остальные выходы которого соединены с одноименными полюсами источников опорного напряжения старшего и младших разрядов, первый вход коммутатора подключен к общий шине, а второй его вход соединен с аналоговым выходом управляемого источника опорного напряжения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения амплитуды одиночных импульсных сигналов | 1980 |

|

SU960644A1 |

| Устройство для измерения максимального значения сигналов | 1977 |

|

SU739424A1 |

| Следящий аналого-цифровой преобразователь | 1978 |

|

SU738150A1 |

| Аналого-цифровой преобразователь считывания | 1977 |

|

SU677097A1 |

| Преобразователь напряжения в код | 1977 |

|

SU728222A1 |

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1979 |

|

SU964981A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU970680A1 |

| Аналого-цифровой преобразователь последовательного уравновешивания | 1981 |

|

SU1030965A1 |

| Цифровое измерительное стробоскопическое устройство | 1978 |

|

SU748253A1 |

| Устройство для измерения амплитуды импульсных сигналов | 1984 |

|

SU1223154A1 |

УСТРОЙСТВО ;ШЯ ИЗМЕРЕНИЯ АМПЛИТУЛЫ ОДИНОЧНЫХ И тУЛЬС11ЫХ СИГНАЛОВ, содержащее выходной кодовый регистр, декадный делитель, декаду измерительных компараторов, источник опорного напряжения старшего разряда, два дополнительных компаратора, пиковый детектор, линию задержки, четьфе ключевых элеИента, причем выходы измерительных |сомпаратороБ подключены к входам выходного кодового регистра, вход пикового детектора и вход линии задержки присоединены к входу устройства, первые входы измерительных компараторов соединены с соответст.вукщими выходами декадного делителя, их вторые входы соединены параллельно, а выход линии задержки соединен с первым входом первого дополнительного компаратора, о тличающееся тем, что с целью его упрощения и повьвпения надежности, в него дополнительно введены управляемьоЧ источник опорного напряжения, кодовый выход которого соединен с входом выходного кодового регистра, а к диалоговому выходу присоединен первый крайний вывод декадного делителя, источники опорного напряжения младших разрядов, блок ключей считывания, коммутатор, тактовый генератор, злемент временной задержки, триггер и распределитель, выходы которого соединены с входами блока ключей считывания,, выходы которого соединены с кодовыми входами упраьлясмого источника опорного напряжения, второй вход первого дополнительного компаратора соединен с общей шиной, первый вход второго дополнительного компаратора соединен с входом пикового детектора, а второй вход пторого дополнительного компаратора - с его выходом, подключенным K- входу первого ключевого элементаj выход которого соединен с выходом второго ключевого злемента и соедиIненными параллельно вторыми входами измерителып 1Х компараторов, выход линии задержки подключен к входу второго ключевого элемента, выход первого дополнительного компаратора связан с управляющим входом третьего ключевого элемента, выход которого соединен с выходом устройства, первый управляющий вход четвертого ключевого элемента соединен с выходом второго дополнительного кокшаратора, вход четвертого ключевого элемента подключен к выходу тактового генератора, а выход соединен с управляющим входом блока ключей считывания и входом элемента временной задержки, выход которого соединен с входами переключения коммутатора и распределителя , кодовые входы которого связаны с выходами измерительных компараторов, а один из выходов одновре

Изобретение относится к измерительной технике и может быть использовано в электроизмерительных устройствах и системах для определения максимального значения кратковременньгх одиночных и редко повторяющихся импульсных сигналов.

Известно устройство для измерения максимального значения сигнала, содержащее выходной кодовый регистр, многоразрядный декадный делитель, группу компараторов, первый вход каждого из которых подсоединен к соответствующей ступени младшей декады многоразрядного декадного делителя, ступени старших декад которого шунтированы группой ключевых элементов, а выходы подключены к входам выходного кодового регистра 1.

Недостаток устройства - увеличение динамической погрешности результата измерения с уменьшением продолжительности измеряемого импульса, обусловленное последовательным во времени уравновешиванием измеряемой величины.

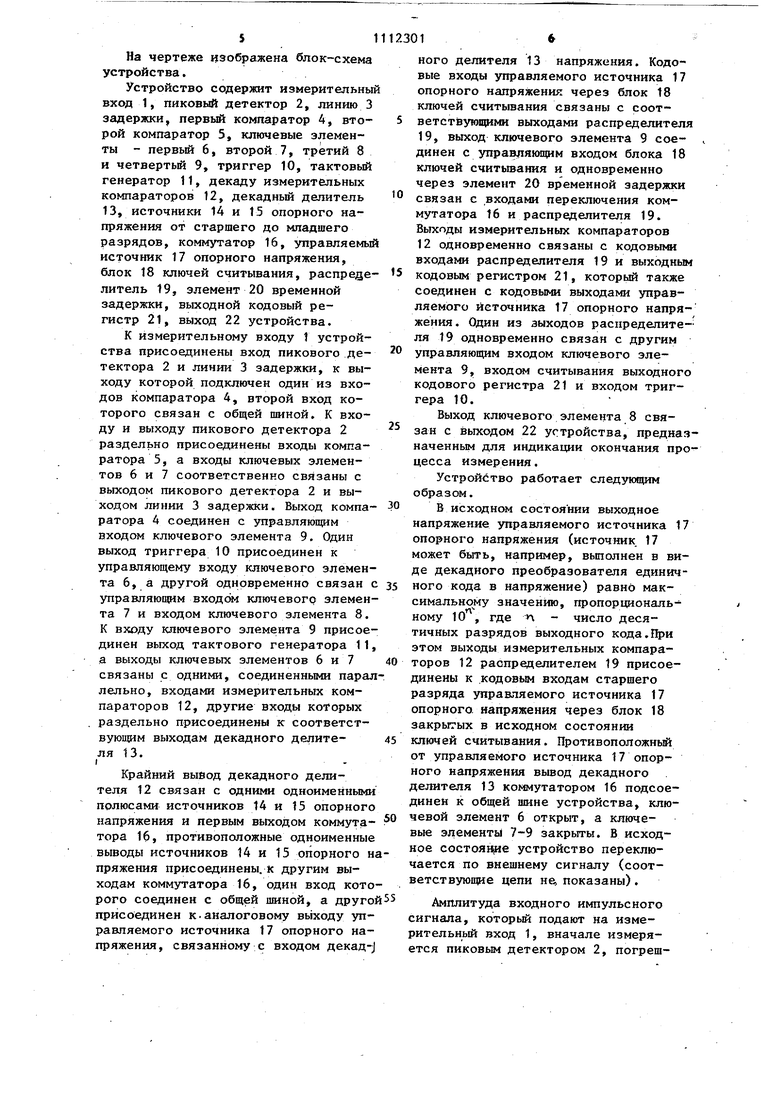

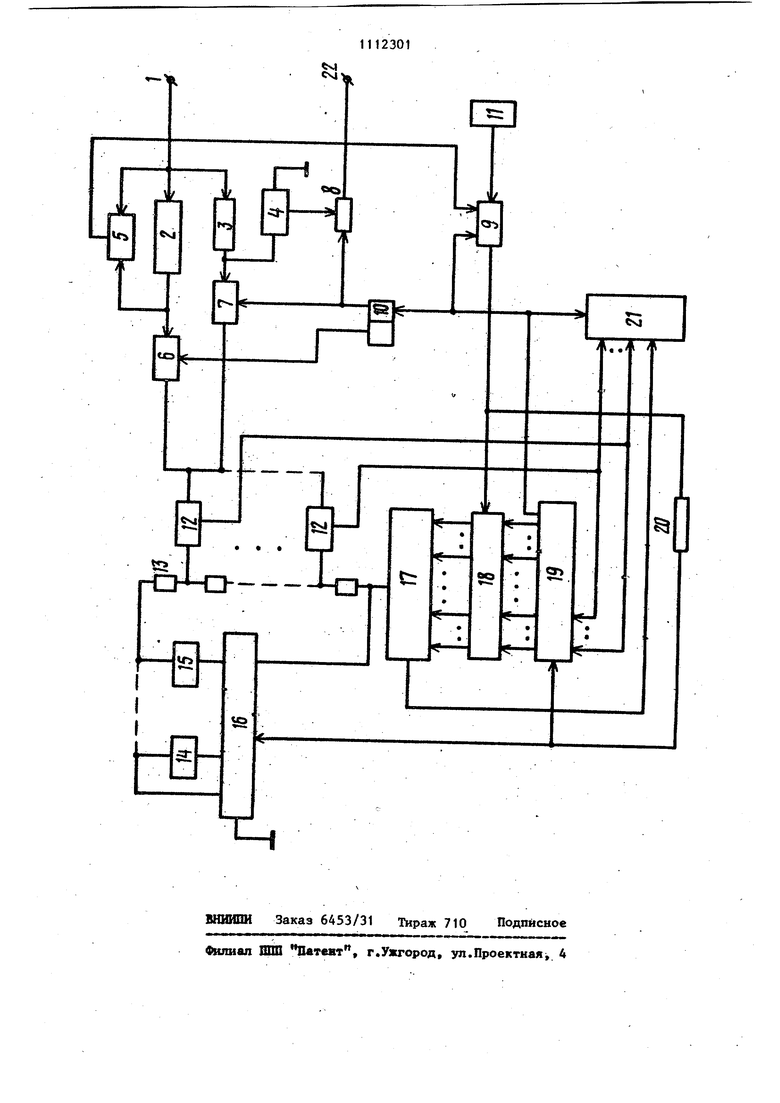

Наиболее близким по технической сущности к предлагаемому является устройство для измерения амплитуды одиночных импульсных сигналов, содержащее выходной кодовый регистр, многоразрядный декадный делитель, декаду измерительных компараторов, первьй вход каждого из которых подсоединен к соответствукнцей ступени младшей декады многоразрядного декадного делителя, ступени старших декад которого шунтированы группой ключевьк элементов, а выходы подключены к входам выходного кодового регистра, источник опорного напряжения, два преобразователя единичного кода в напряжение, пиковый детектор, линию задержки, два дополнительных декадных делителя, дополнительные ключевые элементы, две дополнительные группы компараторов, первые входы одной, из которых подключены к соответствующим ступеням младших декад первого дополнительного декадного делителя, ступени старших декад которого зашунтированы дополнительными ключевыми элементами, а первые входы другой подключены к соответствуннцим ступеням второго дополнительного декадного делителя, линия задержки подключена между вторыми входами группу компараторов и входом пикового детектора j выход которого подключен к вторым входам каадого компаратора дополнительных групп компараторов, декадный делитель и первый дополнительный декадный делитель включены между шиной нулевого потенциала и выходом источника ОПОРНОГО; напряжения, к котором подключен входом первый преобразователь единичного кода в напряжение выход которого соединен с входом второго преобразователя единичного кода в напряжение, кодовыми выходами подключенного к выходам части компараторов первой дополнительной группы компараторов и управляющим входом части группы ключевых элемен тов, шунтирукицих часть ступеней старших декад многоразрядного декадного делителя, кодовые входы первого преобразователя единичного 3 кода в напряжение подключены к выходам компараторов второй дополнительной группы компараторов и управляющим входом другой части ключевых элементов группы ключевых элементов шунтирующих другую часть ступеней старших декад многоразрядного декадного делителя, и дополнительной груп пы ключевых элементов, а выходы преобразователей единичного кода в напряжение подключены к входам выходного кодового регистра 21. Недостатками известного устройства являются относительная сложность так как .оно содержит многоразрядные резистивные д лители напряжения с декадакш компараторов в соответствии с числом десятичных разрядов кода .измеряемой величины и аналоговые ключи для коммутацииСтупеней делите лей, и связанная с ней недостаточная надежность. Цель изобретения - упрощение устройства и повышение его надежности. Поставленная цель достигается тем, что в устройство для измерения амплитуды одиночных импульсных сигна лов, содержащее выходной кодовый ре гистр, декадный делитель, декаду из мерительных компараторов, источник опорного напряжения старшего разряда, два дополнительных компаратора, пиковый детектор, линию задержки, четыре ключевых элемента, причем выходы измерительных компара торов подключены к входам выходного кодового регистра, вход пикового детектора и вход линии задержки присоединены к входу устройства, первые входы измерительных компараторов соединены с соответствующими выходами декадного делителя, их вторые входы соединены параллельно, а выход линии задержки связан с пер вым входом первого дополнительного компаратора, дополнительно введены управляемый источник опорного напряжении, кодовый выход которого связан с входом выходного кодового регистра, а к аналоговому выходу присоединен первый крайний вывод декадного делителя, источники опор ного напряжения младших разрядов, блок ключей считывания, коммутатор, тактовый генератор, элемент временной задержки, триггер и распределитель, выходы которого соединены с 14 , входами блока ключей считывания, связанного своими выходами с кодовыми входами управляемого источника опорного напряжения, второй вход первого дополнительного компаратора соединен с общей шиной, входы второго дополнительногокомпаратора раздельно присоединены к входу и выходу пикового детектора, выход пикового детектора соединен с входом первого ключевого элемента, выход готорого одновременно связан с выходом второго ключевого элемента и соединенными параллельно вторыми входами измерительных компараторов, выход линии задержки присоединен к входу второго ключевого элемента, выход первого дополнительного компаратора связан с управляющим входом третьего ключевого элемента, выход которого присоединен к выходу устройства, первый управляющий вход четвертого ключевого элемента соединен с выходом второго дополнительного компаратора, вход четвертого ключевото элемента присое диней к выходу тактового генератора, выход одновременно связан с управляющим входом блока ключей считывания и входом элемента временной задержки, выход которого присоединен к входам переключения коммутатора и распределителя, кодовые входы которого связаны с выходами измерительных компараторов, а один из выходов одновременно соединен с вторым управляющим входом четвертого ключевого элемента, входом считывания выходного кодового регистра и входом триггера, один выход которого присоединен к управляющему входу первого ключевого элемента, а другой его выход одновременно связан с управляющим входом второго ключевого элемента и входом, третьего ключевого элемента, другой крайний вывод декадного делителя одновременно связан с одними одноименными полюсами источников опорного напряжения старшего и младших разрядов и первым выходом коммутатора, к другим выходам которого раздельно поисоединены противоположные одноименные полюса указанных источников опорного нагфяжения, первый вход коммутатора присоединен к общей шине устройства, а второй его вход соединен с аналоговым выходом управляемого источника опорного направления. 5 На чертеже изображена блок-схема устройства. Устройство содержит измерительны вход 1, пиковый детектор 2, линию 3 задержки, первый компаратор 4, второй компаратор 5, ключевые элементы - первьй 6, второй 7, третий 8 и четвертый 9, триггер 10, тактовый генератор 11, декаду измерительных компараторов 12, декадньй делитель 13, источники 14 и 15 опорного напряжения от старшего до младшего разрядов, коммутатор 16, управляемый источник 17 опорного напряжения, блок 18 ключей считывания, распреде литель 19, элемент 20 временной задержки, выходной кодовый регистр 21, выход 22 устройства. К измерительному входу 1 устройства присоединены вход пикового детектора 2 и линии 3 задержки, к выходу которой подключен один из входов компаратора 4, второй вход которого связан с общей шиной. К входу и выходу пикового детектора 2 раздельно присоединены входы компаратора 5, а входы ключевых элементов 6 и 7 соответственно связаны с выходом пикового детектора 2 и выходом линии 3 задержки. Выход компаратора 4 соединен с управляюпр1м входом ключевого элемента 9. Один выход триггера 10 присоединен к управляющему входу ключевого элемен та 6, а другой одновременно связан управляющим входсм ключевогр элемен та 7 и входом ключевого элемента 8. К входу ключевого элемента 9 присое динен выход тактового генератора 11 а выходы ключевых элементов 6 и 7 связаны с одними, соединенными пара лельно, входами измерительных компараторов 12, другие входы которых раздельно присоединены к соответствующим выходам декадного делитеЛЯ 1 3. Крайний вывод декадного делителя 12 связан с однш«1 одноименным полюсами источников 14 и 15 опорног напряжения и первым выходом коммута тора 16, противоположные одноименны выводы источников 14 и 15 опорного пряжения присоединены, к другим выходам KOMMjnraTopa 16, один вход кот рого соединен с общей шиной, а друг присоединен к.аналоговому выходу уп равляемого источника 17 опорного на пряжения, связанному с входом декад 1 ного делителя 13 напряжения. Кодовые входы управляемого источника 17 опорного напряжения через блок 18 ключей считывания связаны с соответствующими выходами распределителя 19, выход ключевого элемента 9 соединен с управляющим входом блока 18 ключей считьтания и одновременно через элемент 20 временной задержки связан с входами переключения коммутатора 16 и распределителя 19. Выходы измерительных компараторов 12 одновременно связаны с кодовыьш входами распределителя 19 и выходным кодовым регистром 21, который также соединен с кодовыми выходами управляемого источника 17 опорного напряжения. Один из выходов распределите-ля 19 одновременно связан с другим управляющим входом ключевого элемента 9, входом считывания выходного кодового регистра 21 и входом триггера 10. Выход ключевого элемента 8 связан с выходом 22 устройства, предназначенным для индикации окончания процесса измерения. Устройство работает следующим образом. В исходном состоянии выходное напряжение управляемого источника 17 опорного напряжения (источник 17 может быть, например, выполнен в виде декадного преобразователя единичного кода в напряжение) равно максимальному значению, пропорциональному 10 , где п - число десятичных разрядов выходного кода.При этом выходы измерительных компараторов 12 распределителем 19 присоединены к кодовым входам старщего разряда управляемого источника 17 опорного, напряжения через блок 18 закрытых в исходном состоянии ключей считывания. Противоположньй от управляемого источника 17 опорного напряжения вьшод декадного делителя 13 коммутатором 16 подсоединен к общей шине устройства, ключевой элемент 6 открыт, а ключевые элементы 7-9 закрыты. В исходное состояние устройство переключается по внешнему сигналу (соответствующие цепи не, показаны). Амплитуда входного импульсного сигнала, которьй подают на измерительньй вход 1, вначале измеряется пиковым детектором 2, погрешность которого находится в пределах младшего разряда кода. Вьгходное напряжение пикового детектора 2, расширенное на уровне максимума входного импульсного сигнала, сравнивается с помощью компаратора 5 непосредственно с входным импульсным сигналом. Благодаря некоторой задержке формирования расширенного напряжения на выходе пикового детек тора 2 компаратор 5 фиксирует превьшение выходным напряжением детектора 2 текущего значения напряжения входного импульсного сигнала пр уменьшении последнего. Сформированны при этом на выходе компаратора 5 единичный сигнал деблокирует ключевой элемент 9, после чего начинается кодирование амплитуды измеряе мого импульсного сигнала подекадным сравнением. Выходное напряжение пикового детектора 2 в первом такте кодирования сравнивается в измерительных компараторах 12 с опорными уровнями квантования, образованными делителем 13, |шаг которых пропорционален единице старшего разряда, кода т.е. При этом число сработ вимх компараторов 12 (напряжение на измерительно входе которых превьш1ает напряжение соответствующих уровней квантования на опорном входе; равно К1 - значению старшего разряда кода измеряемой величины (,1,...,9). Первыми же после деблокирования ключевого элемента 9 тактовым сигналом тактового генератора 11 опрашиваются ключи считывания блока 18 ключей считывания и в соответствии с числом нулевых сигналов несработав ших измерительных компараторов 12 от ключается соответствующее число ступеней напряжений старшего разряда . управляемого источника 17 опорного напряжения. Подобное отключение ступеней старшего разряда в источнике 17 достигается, например, включением на соответствующих кодовых входах этого источника элементов НЕ. Таким образом, в первом такте кодирования после получения кода К1 старшего разряда напряжение управляемого источника 17 опорного напряжения устанавливается эквивалентным значению старшего разряда кода К1- С задержкой в элементе 20 временной задержки, необходимой для форt18 мирования кода К1 и установления соответствующего напряжения управляемого источника 17 опорного напряжения, тактовый сигнал переключает распределитель 19 и коммутатор 16 из первого, исходного, во второе положение. При этом выходы измерительных компараторов 12 присоединяются через соответствующие ключи блока 18 ключей считывания к цепям кодовых входов второго старшего разряда управляемого источника 17 опорного напряжения, а присоединенный к общей шине вывод декадного делителя 13 отключается от этой шины и к декадному делителю 13 подключается параллельно источник 14 опорного напряжения. Напряжение источника 1А опорного напряжения равно единице старшего разряда кода, т.е. . Это напряжение суммируется с установленным напряжением управляемого источника 17 опорного напряжения и поэтому до появления второго тактового сигнала на ступенях декадного делителя 13 устанавливаются уровни напряжения с шагом, пропорциональным . Каждый из этих уровней по абсолютной величине оказывается эквивалентным К1 Ю + Р. где р 1,2,..i,9 - номер ступени декадного делителя 13. С появлением второго и последующего тактовых сигналов такты кодирования и формирования кодов последующих разрядов повторяются аналогично описанному. После формирования кода предпоследнего младшего разряда и переключения распределителя 19 сигналом, формируемым на его выходе, блокируется ключевой элемент 9, что исключает дальнейшую передачу тактовых сигналов от тактового генератора 11 и переключается триггер 10, что приводит к блокированию ключевого элемента 6 и деблокированию ключевых элементов 7 и 8. Таким образом, после получения кода предпоследнего младшего разряда на ступенях декадного делителя 13 устанавливаются уровни напряжения с шагом, пропорциональным единице младшего разряда кода, выходное напряжение управляемого источника 17 опорного напряжения оказывается равным измеряемой величине входного импульсного сигнала с точностью до единицы предпоследнего младшего разряда кода, а к входам измерительных компараторов 12 вместо пикового детектора 2 оказывается подключенной линия 3 задержки.

Величину времейной задержки линии 3 задержки выбирают в соответствии с временем получения кодап-1 старших разрядов, т.е. равной сумме периодов соответствующего числа тактов.

В последнем такте кодирования уровня напряжения декадного депителГя 13 с помощью измерительных компараторов 12 сравниваются непосредственно с измеряемым импульсным сигналом, задержанным в линии 3 задержки на указанное выше время. По мере нарастания измеряемого импульсного сигнала компараторы 12 последователь но срабатьюают, их сигналы запоминаются выходным кодовым регистром 21. В этот регистр, подготовленный для записи в предпоследнем такте кодирования соответствующим выходню сигналом распределителя 19, переписываются из регистра управляемого источника 17 опорного напряжения также

и коды старших разрядов. I

После перехода измеряемого импульсного сигнала через максимум в регистре 21 оказьдаается записанным код, эквивалентный амплитуде этого сигнала. Уменьшение величины

импульсного сигнала, например до нулевого уровня, фиксируется компар атор см 4, шлход ной сигнал кoтopo го через деблокированный в предпоследнем такте кодирования ключевой элемент 8 передается на выход 22 устройства в качестве сигнала окончания процесса измерения. По этому сигналу код может быть считан из регистра 21 для дальнейшей обработки, после чего устройство можно переключить в исходное состояние с одновременным сбросом регистра.

Использование одной шкалы квантов с изменяющейся ценой деления и упрощение принципа формирования шагов квантования позволяют использовать лишь один декадный делитель вместо нескольких многоразрядных,

ступени которых коммутировались аналоговыми ключами, и резко снизить число активных элементов. В свою очередь упрощение предлагаемого устройства позволит снизить показатель

интенсивности отказов и соответственно повысить надежность устройства. Использование щ остого декадного делителя и исключение аналоговых ключей в предлагаемом устройстве снимает систематические погрешности

и погрешности, вносимые нелиней- ; ностью аналоговых ключей при использовании многоразрядных делителей на;1ряжения.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для измерения максимального значения сигналов | 1977 |

|

SU739424A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для измерения амплитуды одиночных импульсных сигналов | 1980 |

|

SU960644A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-09-07—Публикация

1982-03-12—Подача