тическим отказоку, непосредственно в процессе измерения.

Целью изобретения является повышение достоверности результата преобразования.

Поставленная цель достигается тем, что согласно способу аналогоцифрового преобразования полученный после, вычитания остаток уравновешивающего напряжения уменьшают на половину числа единичных ступеней напряжения, пропорциональных определяемому разряду кода, сравнивают его с измеряемым сигналом, определяют знак рассогласования и соответственно изменяют уравновешивающее напряжение ступенями/ пропорциональными данному и последующим разрядам кода до изменения.знака рассогласования.

В УСТРОЙСТВО для осуществления указанного способа, содержащее сравнивающее устройство, первый вход которого к шине измер:51емого сигнала, второй вход соединен с выходом декадного преобразователя единичного кода в напряжение, входы которого соединены с выходами декадных регистров, генератор тактовЕЛх сигналов, десятично-декадный делитель напряжения, включенный между оРщей шиной и опорным источником, к выходам которого.подключены первые входты декадных компараторов и компараторов старшей декады, вторые входы которых соединены с шиной измеряемого сигнала, управляющие входы - с шиной строб-сигналов, а выходы компараторов старшей декады подключены к соответствующим входам старшего декадного регистра, введены два элемента ИЛИ, два элемента Н и в каждую декаду, кроме старшей, блок анализа с декадным триггером и декадным элементом И, выход кото.рого соединен с первым, входом блока анализа и первым входом декадного триггера, первый вход - с выходом сравнивающего устройства, второй вход - с первьам выходом предыдущего блока анализа, кроме декадного элемента И, соответствующего старшему блоку анализа, второй вход последнего соединен с выходом -первого элемента ИЛИ, второй вход декадного триггера данной декады подключен к выходу декадного триггера следующей декады, а выход - ко второму входу блока анализа данной декады и шине сброса перовой группы соединенных последовааельМо триггеров соответствующего декадного регистра, а выход декадного триггера, соответствующего старшему блоку анализа, подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с шиной строб-сигнала,второй выход блока анализа соединен с управляющим входом первой группы триггеров соответствующего декадног

регистра, управляющий вход второй группы соединенных последовательно триггеров которого подключен к третьему выходу соответствующего блока анализа, а шина сброса указанных триггеров - к,пятому входу блок

;анализа и к выходу соответствующего декадного компаратора, кроме младшего блока анализа, третий вход блока анализа соединен с выходом последнего триггера первой группы триггеров соответствующего декадного регистра, выход последнего триггера второй группы триггеров которого соединен с четвертым входом блока анализа, кроме младшего, в котором указанный выход через первый элемент НЕ подключен к первому входу элемента и, второй вход которого через второй элемент НЕ соединен с

первым выходом младшего блока анализа и шиной сигнала Конец преобразования , шестой вход блока анализа каждой декады соединен с выходом генератора тактовых сигналов, а четвертый выход - с соответствующим входом второго элемента ИЛИ,, управляющий вход которого подключен к выходу элемента И, а выход - к шине сигнала ошибки преобразования.

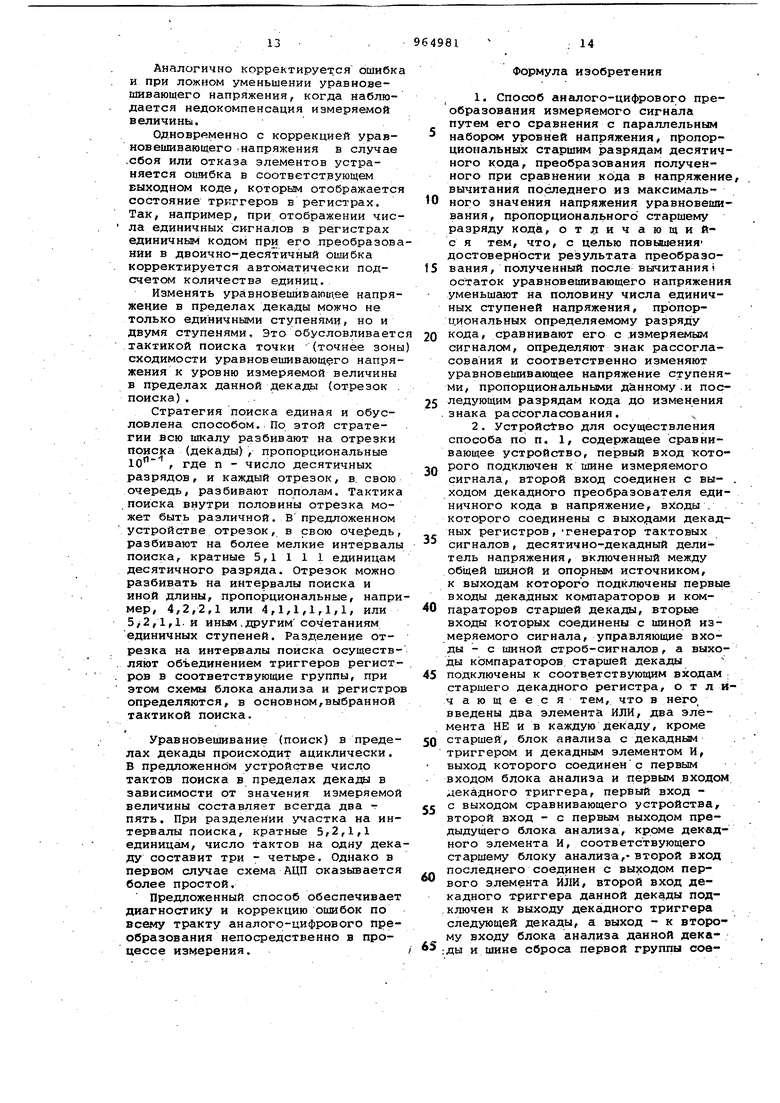

Блок анализа содержит элементы НЕ, И, ИЛИ, одновибратор и два триггера, входы которых соответственно подключены к второму и третьему выходам блока анализа и к выходам первого и второго элементов И, первые входы которых соединены соответственно с первьр4И выходами второ го и первого триггеров, вторые выходы которых подключены соответственно к первым входам- третьего и четвертого элементов И, второй вход TpeTbefo элемента И соединен с перBbw входом Первого элемента . И и через первый элемент НЕ - с первым входом блока анализа первым входом второго элемента И, вторым -входом четвертого элемента И и через одновибратор - с первым входе пятого элемента И, выход которого соединен со вторыми входами первого и второго элементов И, второй выход - с пятым входом блока анализа, второй вход которого соединен с первым входом шестого элемента И и -третьим входом пятого элемента И, четвертый вход последнего подключен к второму входу шестого элемента И и через второй элемент НЕ к первому выходу блока анализа и выходу элемента ИЛИ первый вход которого через третий элемент НЕ соединен с четвертым входом.блока анализа, ;второй и третий входы - с выходами соответственно третьего и четвертого элементов И, четвертый вход- - с пятьал входом .блока анализа, третий вход которого соединен с третьим входом шестого элемента И, выход которого подключен к пятому выходу блока анализа. На фиг.1 представлена блок-схема предложенного устройства; на фиг.2 блок-схема блока анализа. Устройство содержит декадный преобразователь единичного кода в напряжение 1 (ПЕКН), сравнивающее устройство 2,-декадный регистр 3 старшего разряда с триггерами 4, декадные регистры 5 и 6 соответственно промежуточных и младшего разрядов с выходом 7 сигнала, соответствующего максимальнсилу уровню напряжения данной декады ПЕКН, выходом 8 сигнала, соответствующего нулевом iуровню напряжения данной декады ПЕК входами 9 и 10 сигнала параллельног сброса и сигналов последовательного переключения в нулевое состояние группы из четырех триггеров соответ ственно, входами 11 и 12 сигналов последовательного переключения в единичное состояние и сигнала парал лельного сброса в нулевое состояние группы из пяти триггеров, блок анализа 13 с входсяй 14 сигнала знака уравновешивания, выходами 15 и 16 тактовых сигналов, входами 17 и 18 сигналов, соответствующих максимальному и нулевому уровням данной .декады напряжения ПЕКН, выходсм 19 сигнала окончания уравновешивания в пределах данной декады напрязЬения ПЕКН, входом 20 тактовых сигналов, входом 21 сигнала декадного компаратора, выходом 22 сигнала ошибки, входом 23 сигнала начала уравновешивания в пределах данной декады напряжения ПЕКН, декадные элементы И 24, декадные триггеры 25, первый 26 и второй 27 элементы НЕ, элемент И 2В, первый 29 и второй 30 элементы ИЛИ, шину сигнала конца преобразования 31, генератор тактовых сигналов 32, компараторы старшей декады 33, декадные компараторы 34, десятично-дексшный делитель напряжения 35, опорный источник 36 шину строб-сигналов 37, шину измерительного сигнала 38, шину сигнала ошибки преобразования 39. Блок-схема блока анализа 13 содержит первый элемент НЕ 39, одновибратор 40, первый, второй и трети элементы И 41-43, второй элемент НЕ 44, первый 45 и второй 46 триггеры, четвертый 47 и-пятый 48 элементы И, элемент ИЛИ 49, третий эле мент НЕ 50, шестой элемент И 51. АЦП работает следующ 1М образом. В исходном состоянии на опорный вход сравнивающего устройства 2 с выхода декадного преобразователя 1 единичного кода в напряжение (ПЕКН) подается максимальное уравновешивающее напряжение, равное пределу преобразования и пропорциональное величине Ю , где п - число десятичных разрядов кода, отображаю- . щего измеряемую величину. ПЕКН 1 содержит декады резисторов , номинал резисторов каждой декады отличается от декады соседнего разряда на десятичный порядок, Декады резисторов обра.зуют делитель, управляемый соответствующими декадами аналоговых ключей ПЕКН, коммутируемых триггерами 4 соответствующих декадных регистров 3,5 и 6. Триггеры 4 в каждом регистре 5 и в регистре 6 объединены в две группы по пять и по четыре триггера в группе. Каждая группа триггеров, за исключением группы из четырех триггеров регистра 6 младшей декады, управляются параллельно по входам 9 и 12 .этих регистров. Вместе с тем, тригге йл в группах включены каскадно и могут последовательно переключаться в нулевое положение (группы из четырех триггеров) или в единич- нов положение (группы из пяти триггеров) в соответствии с тактовыми сигналами, поступающими на соответствующие входы 10 или 11 через блок 13 анализа (выходы 16 и 15) от генератора 32 тактовых сигналов. АЦП запускается внешними стробсигналами, подводикими к входной шине 37 устройства и далее к ..стробируем№4 компараторам 33 и 34, а также к элементу ИЛИ 30. Напряжение опорного источника 36, равное пределгУ преобразования, порциональному 10, распределяется по ступеням десятично-декадного делителя напряжения 31 в виде ряда параллельных уровней, которые поступают на опорные входы соответствующих компараторов 33 и 34. Шаг уровней задают равным единицам одного или нескольких старших разрядов (компараторы 33) и декадным уровням последующих разрядов (компараторы 34) вплоть до младшего предпоследнего, равного десяти единицам (квантам) младшего разряда. Компараторы 33 и 34 используются для грубого параллельного сравнения измеряемой величины, подводимой к входной шине 33. Грубое параллельное сравнение измеряемой величины на. уровне декад нескольких старших разрядов с единичным шагом требует большого числа, компараторов 33, поэтому параллельное сравнение с шагом, пропорциональным единице разряда, в большинстве случаев целесообразно выполнять лишь на уровне одного старшего разряда. Сравнивающее устройство и каждый из компараторов 33 и 34 выдает

единичный сигнал, если напряжение на его опорном входе превыиает напряжение на измерительном входе а в противном вьвдается нулевой сигнал.

. Допустим, что измеряемая величина находится в пределах старшей декады. Поэтому с поступлением стробсигнала ни один из компараторов 34 не срабатывает, а единичный сигнал выдает сравнивающее устройство 2 и один или возможно несколько компараторов 33, опорное напряжение навходах которых превышает на соответствующее число единиц старшего разряда измеряемое напряжение (с точностью до единицы соответствующего старшего разряда). По единичным сигналам компараторов 33 переключаются в нулевое положение соединенные с ними триггеры 4 регистра.3 старшей екады, и напряжение уравновешивания на выходе ПЕКН 1 скачком уменьшается на соответствующее число ступеней. дновременно по строб-сигналу и единичному сигналу сравнивающего устройства 2, переданным через соответствующий элемент И 21, включается управляемый этим элементом триггер 25. Сигналы с выходов элемента И 24 и триггера 25 поступают в соответствующий блок анализа 13. Одновременно сигналом данного триггера 25 через элемент ИЛИ 30 обеспечивается в дальнейшем передача единичного сигнала сравнивающего устройства 2 соответствующим элементом И 24. Сигнал триггера 25 поступает далее на вход 12 соответствующего регистра 5, параллельно переключает в нулевое положение пять триггеров регистра 5, и напряжение уравновешивания скачком уменьшается еще на пять ступеней, но уже декады соседнего первого из промежуточных разрядов. Дальнейшее управление процессом уравновешивания выполняется по сигналам блоков анализа 13.

Каждый блок анализа 13 анализиует знак рассогласования в процессе уравновешивания измеряемой величины напряжением ПЕКН 1 и в зависимости от знака обеспечивает передачу тактовых сигналов в направлении увеличения (переключение триггеров из нулевого в единичное состояние тактовыми сигналами, поступающими на вход 11 регистра) или уменьшения (переключение триггеров в нулевое состояние тактовыми сигналами, поступающими на вход 10 регистра) выходного напряжения уравновеаотвания преобразователя 1 в пределах данной декады.

Блок анализа уравновешивания .работает следующим образом.

По адиничному сигналу сравнивающего устройства 2, поступившему на вход 14 блока, запускается одновибратор 40. Одновибратор, переключаясь на короткое время, равное времени задержки срабатывания сравнивающего устройства 2 и других элементов, нулевым сигналом блокирует передачу тактовых сигналов через элемент И 48 в блок. Это необходимо для того, чтобы в случае изменения сигнала сравнивающего устройства 2 после скачкообразного уменьшения уравновешивающего напряжения, которое может оказаться меньше измеряемой величины, исключить влияние задержки сигнала этого устройства на работу схемы и, тем самым, обеспечить нужное направление уравновешивания.

После возвращения одновибратора 40 в устойчивое состояние элемент И 48 блока анализа оказывается открытым для тактовых сигналов, так как на входе 23 блока присутствует единичный сигнал начала уравновешивания, поступивший с подключенного к этому входу блока соответствующего триггера 25. Если после скачкообразного на половину первой из промежуточных декад уменьшения уравновешивающего напряжения оказывает, что измеряемая величина меньше установившегося уровня уравновешивающего напряжения, то блок анализа обеспечивает передачу тактовых сигналов с выхода 16 на вход 10 связанного с ни декаднрго регистра для последовательного переключения в нулевое состояние четырех оставшихся в единичном состоянии триггеров.

При этом, с каждым тактовым сигналом упомянутые триггеры последовательно переключаются в нулевое положение до установления уровня уравновешивающего напряжения, меньшего (с точностью до одной ступени данной декады) измеряемой величины.

Если после упомянутого скачкообразного на половину первой из прсмежуточных декад уменьшения уравновешивающего напряжения оказывается, что измеряемая величина превышает усгановивишйся уровень уравновешивающего напряжения, то блок анализа обеспечивает передачу тактовых сигналов с выхода 15 на вход 11 регистра для последовательного переключения в единичное состояние пяти триггеров , сброшенных перед этим в нулевое состояние. При этом с каждым тактовым сигналом упомянутые триггеры последовательно вновь переключаются в единичное состояние до тех пор, пока уровень уравновешивающего напряжения не превысит (с точностью до одной ступени данной декады) измеряемой величины. Триггеру 45 и 46 блока анализа указывают знак (направление изменения) уравновешивающего

напряжения.

ЕСЛИ с поступлением строб-сигнала после первого на пять ступеней уменьшения уравновешивающего напряжения сравнивающее устройство продолжает выдавать единичный сигнал (преобразуемая величина меньше напряжения уравновешивания), то с поступлением первого же тактового сигнала после окончания сигнала одновибратора 40 .открывается элемент И 42 переключается .триггер 46, и уравновешивающее напряжение начинает последовательно уменьшаться с каждым тактовьм сигналом на величину ступени данной декады. При этом изменение единичного значения сигнала сравнивающего устройства 2 на нулевое значение (конец уравновеишвания в пределах данной декады с недЬкомпенсацией) фиксируется появлением единичного сигнала на выходе злемента И 43 (при наличии единичного сигнала триггера 46). Этим сигналом, переданным через элемент ИЛИ 49 на выход 19 блока анализа (выход сигнала конца декадного уравновешивания) и инвертированным элементом НЕ 44, блокируется элемент И 48, и, тем самым, запрещается дальнейшая передача тактовых сигналов через данный блок анализа в управляемый им декадный регистр.

Если с поступлением строб-сигнала запуска АЦП после скачкообразного уменьшения на пять ступеней уравновешивающего напряжения сравнивающее устройство 2 выдает нулевой сигнал (измеряемая величина больше установленного уровня напряжения уравновешивания), то с поступлением, первого же тактового сигнала после окончания сигнала одковибратора 40 открывается элемент И 41, переключается -триггер 45, и уравновешивающее напряжение начинает вновь последовательно увеличиваться с каждым тактовым сигналом на величину -ступени данной декады. При этом изменение нулевого значения сигнала измерительного компаратора вновь на единичное (окончание уравновешивания в пределах данной декады с превышением) фиксируется появлением единичного сигнала на выходе элемента И 47. В соответствии с этим сигналом, аналогично описанному выше, блокируется дальнейшее поступление тактовых сигналов через блок анализа в управляемый этим блоком декадный триггерный регистр.

Для исключения возможного паразитного колебательного процесса и ошибок уравновешивания при изменении сигнала измерительного компаратора элементы И 41 и 42 в блоке анализа блокируются сигналами триггеров 46 и 45 соответственно таким образом, что первый из сработавших тригге- ,

ров блокирует элемент И в цепи за- пуска другого триггера.

Сигнал конца уравновешивания, появившийся на выходе 19 блока анализа, передается в элемент И 24 (см,фиг.1), подключенный к этому выходу, и воздействует на соседнюю более младшую декаду ПЕКН 1 аналогично строб-сигналу.

Далее процесс уравновешивания

0 продолжается в пределах соседней декады более младшего разряда аналогично вышеописанному. При этом выходным сигналом триггера 25, поступающим на вход 13 данного блока

5 анализа, одновременно переключается в нулевое положение триггер в аналогичной цепи блока анализа, управляющего декадой предьщущего старшего -разряда ПЕКН, с целью блокировки передачи тактовых сигналов через

0 этот блок анализа при изменении сигнала сравнивающего устройства 2 в процессе дальнейшего уравновешивания. Подобньм образом- уравновешивание выполняется декада за дека5дой, вплоть до декады младшего разряда. Сигнал,появившийся.на выходе 19 блока анализа, управляющего регистром 6 и соответствующей младшей декадой ПЕКН 1, является сигналом

0 окончания работы АЦП, и с выходной шины 31 передается в устройство об работки или регистрации для считывания полученного кода.

Если промежуточные десятичные

5 разряды кода измеряемой величины равны Нулю, то в процессе последовательного уравновешивания переключаются в нулевое состояние соответствующие-декадные регистры 5. В этом

0 случае сигналом конца уравновешивания в пределах декады является нулевой сигнал первого из триггеров данного регистра, формируемый при его переключении и соответствующий нулевому уровню данной декады ПЕКН 1.

5 Этот сигнал с выхода 8 каждого промежуточного регистра 5 передается в блок анализа 13 (вход 18). В блоке анализа нулевой сигнал этого триггера инвертируется элементом

0 НЕ 50 (см.фиг.2) и черезэлемент ИЛИ 49 передается на выход 19 блока. В декаде младшего разряда указанный сигнал не требуется передавать в соответствующий блок анализа, он

5 используется только для диагностики ошибки.

Если измеряемая величина оказывается меньше уровня уравновешивающего напряжения, соответствующего

0 одному или нескольким промежуточным разрядам кода, то уравновешивание происходит следующим образом.

Соответствующими единичными сигналами компараторов 33 и 34 переклю5чаются в нулевое состояние регистр

3 и группы из четырех триггеров соответствуюошх регистров 5t При этом в соответствующих анализа по единичным сигналам декадных компараторов 34, переданным через вход 21 блока, элемент ИЛИ 49 и элемент НЕ 44, блокируется передача тактовых сигналов в соответствующие декадные регистры аналогично вышеописанному. Одновременно единичный сигнал декадного компаратора, посту пивший на вход 21 блока анализа,

через элемент ИЛИ 49 передается на выход 19 данного блока анализа в качестве сигнала конца декадного уравновешивания, после чего параллельно сбрасываются в нулевое состояние пять триггеров соседнего регистра аналогично описанному выше, Группа из пяти триггеров первого из промежуточных регистров 5 переключается по строб-сигналу запуска АЦП, переданному через элемент ИЛИ 30. Указанные переключениятpиг геров регистров, отключение декад ключей и скачкообразный спад уравновешивающего напряжения ПЕКН выполняются во всех декадах параллельно, после чего начинается последовательное уравновешивание измеряемой величины аналогично описанному выше. Код измеряемой величины отображается числом оставшихся в единичном (состоянии триггеров 4 всех регистров.

После считывания кода АЦП устанавливают в исходное состояние (цепи сброса не изображены) и выполняется. (следующий цикл преобразования.

При аппаратурной реализации опи.санного способа благодаря знакопеременному подекадному изменению уравновешивающего напряжения, сходящегося к уровню измеряемой величины с превьошением этого уровня и недокомпенсацией в отдельных декадах, обеспечивается обнаружение ошибки

преобразования по всему тракту АЦП в целом. Ошибка обнаруживается, если при последовательном ступенчатом возрастании уравновешивающего напряжения в пределах половины декады любого из промежуточных и младшего разрядов 5 и 6, сравнивающее устройство не зафиксирует превышение уравнивающим напряжением уровня измеряемой величины. Ошибку определяет элемент И 51 блока анализа (см.фиг.2). Совпадение в этом элементе единичного сигнала триггера . старшего разряда регистра, соответствующего максимальному уровню напряжения этой декады ПЕНК 1 (выход 7 в регистрах 5 и 6), и единичного сигнала конца декадного уравновеши-. вания на выходе элемента ИЛИ 49 блока анализа говорит об отсутствии ошибки. Отсутствие сигнала на выходе

элемента ИЛИ 49 блока анализа при появлении единичного сигнала максимального значения выходного напряжения декады является признаком ошибки уравновешивания и отображается появлением единичного сигнала на выходе 22 блока анализа, который передается далее через элемент ИЛИ 29 на шину АЦП. Для исключения ложной сигнализации логический анализ наличия ошибки выполняется с учетом третьего сигнала - единичног сигнала начала уравновешивания в пределах данной декады, поступающего на вход 23 блока анализа. Ошибка обнаруживается также, если при последовательном уменьшении уравновешивающего напряжения сравнивающее устройство 2 не зафиксирует того, что уравновешивающее напряжение оказалось меньше уровня измеряемой величины или равным ему. Этому соответствует нулевое значение сигнала конца уравновешивания на выходе . 19 блока анализа, подключенного к регистру 6 младшего разряда, при появлении нулевого значения сигнала Соответствующего триггера 4 на выходе 8 регистра 6. Указанные сигнал анализируются элементами НЕ 26 и 27 и И 28 и результирующий сигнал сигнал наличия ошибки - передается через элемент ИЛИ 29 на соответст.вующую шину 39, ,

При появлении ошибки процесс аналого-цифрового преобразования прекращается и полученный результат не учитывается при дальнейшей обработке данных, либо вообще не вводится в ЦВМ. При этом систематический от каз диагностирует ЦВМ в случае последовательного числа ошибочных результатов .

Помимо сигнализации ошибки по всей шкале измеряемой величины рассмотренный способ обеспечивает такж возможность коррекции ошибки. Если произошло ложное включение ступеней ПЕКН, то сравнивающее устройство 2 ф1:ксирует перекомпенсацию и вьщает сигнал на уменьшение напряжения ПЕКН 1. При этом последовательньм выключением ступеней (уменьшением напряжения) данной декады ПЕКН ошибка может быть исключена. Если число выключаемых ступеней не компенсирует число ложно включенных ступеней уравновешивающего напряжения данной декады, то при постоянстве знака рассогласования фо1 «ируется сигнал ошибки. При ложном включении пяти ступеней напряжения младшей декады ПЕКН ошибка п&сле коррекции лз-за недокомперсации на одну ступень будет :мйнймальной и равной единице младшего разряда кода.

Аналогично корректируется ошибка и при ложном уменьшении уравновешиваюшего напряжения, когда наблюдается нелокомпенсация измеряемой величины.

Одновременно с коррекцией уравновешивающего Напряжения в случае .сбоя или отказа элементов устраняется ошибка в соответствующем выходном коде, которым отображается состояние триггеров в регистрах. Так, например, при отображении числа единичных сигналов в регистрах единичным кодом при его преобразовании в двоично-десятичный ошибка корректируется автоматически подсчетом количества единиц.

Изменять уравновешивающее напряжение в пределах декады можно не только единичными ступенями, но и двумя ступенями. Это обусловливаетс тактикой поиска точки (точнее зоны сходимости уравновешивающего напряжения к уровню измеряемой величины в пределах данной декады (отрезок . поиска). .

Стратегия поиска единая и обусловлена способом. По этой стратегии всю шкалу разбивают на отрезки поиска (декады), пропорциональные , где п - число десятичных разрядов, и каждый отрезок, в. свою очередь, разбивают пополам. Тактика поиска внутри половины отрезка может быть различной. В предложенном устройстве отрезок, в свою очередь, разбивают на более мелкие интервалы поиска, кратные 5,1 1 1 1 единицам десятичного разряда. Отрезок можно разбивать на интервалы поиска и иной длины, пропорциональные, например, 4,2,2,1 или 4,1,1,1,1,1, или ,1,1. и иньяи .другимсочетаниям единичных ступеней. Разделение отрезка на интервалы поиска осуществляют объединением триггеров регистров в соответствующие группы, при этом схемы блока анализа и регистров определяются, в основном,выбранной тактикой поиска.

Уравновешивание (поиск) в пределах декады происходит ациклически. В предложенном устройстве число тактов поиска в пределах декады в зависимости от значения измеряемой величины составляет всегда два пять. При разделении участка на интервалы поиска, кратные 5,2,1,1 единицам, число тактов на одну декаду составит три - четыре. Однако в первом случае схема АЦП оказывается более простой.

Предложенный способ обеспечивает диагностику и коррекцию ошибок по всему тракту аналого-цифрового преобразования непосредственно в процессе измерения.

Формула изобретения

1.Способ аналого-цифрового преобразования измеряемого сигнала путем его сравнения с параллельным набором уровней напряжения, пропорциональных старшим разрядам десятичного кода, преобразования полученного при сравнении кода в напряжение, вычитания последнего из максималь0ного значения напряжения уравновешивания, пропорционального старшему разряду кода, отличающийс я тем, что, с целью повышениядостоверности результата преобразоsвания, полученный после вычитания остаток уравновешивающего напряжения уменьшгиот на половину числа единичных ступеней напряжения, пропорциональных определяемому разряду кода, сравнивают его с .измеряемым

0 сигналом, определяют знак рассогласования и соответственно изменяют уравновешивающее напряжение ступенями, пропорциональными данному .и последующим разрядам кода до изменения

5 .знака рассогласования.

2.Устройство для осуществления способа по п. 1, содержащее сравнивающее устройство, первый вход которого подключен к шине измеряемого

0 сигнала, второй вход соединен с вы- . ходом декадного преобразователя единичного кода в напряжение, входы . которого соединены с выходами декадных регистров,-генератор тактовых

5 сигналов, десятично-декадный делитель напряжения, включенный между общей шидой и опорным источником,

к выходам которого подключены первые входы декадных компараторов и ком0параторов старшей декады, вторые входы которых соединены с шиной измеряемого сигнала, управляющие входы - с шиной строб-сигналов, а выходы компараторов, старшей декады

5 подключены к соответствующим входам ; старшего декадного регистра, о т л ичающееся тем, что в него введены два элемент ИЛИ, два элемента НЕ и в каждую декаду, кроме старшей, блок анализа с декадным

0 триггером и декадным элементом И, выход которого соединенс первым входом блока анализа и первым входом, декадного триггера, первый вход с выходом сравнивающего устройства,

5 второй вход - с первым выходом предыдущего блока анализа, кроме декадного элемента И, соответствующего старшему блоку анализа,- второй вход последнего соединен с выходом пер0вого элемента ИЛИ, второй вход декадного триггера данной декады подключен к выходу декадного триггера следующей декады, а выход - к второму входу блока анализа данной дека5;ды и шине сброса первой группы соединенных последовательно триггеров соответствующего декадного регистра а выход декадного триггера, соответствующего старшему блоку анализа подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с шиной строб-сигнала, второй выход блока анализа соединен с управляющим входом первой группы триггеров соответствующего декадног регистра, уп авляющий вход второй группы соединенных последовательно триггеров которого подключен к третьему выходу соответствующего блока анализа, а шина сброса указанных триггеров. - к ПЯТОМУ входу блока анализа и к выходу соответствующего декадного компаратора, кром младшего блока анализа, третий вход блока анализа соединен с выходом последнего триггера первой группы триггеров соответствующего декадног регистра, выход последнего триггера второй группы триггеров которого соединен с четвертым входом блока анализа, кроме младшего, в котором указанный выход через первый элемент НВ подключен к первому входу элемента И, второй вход которого через второй элемент НЕ соединен с первым выходом младшего блока анализа и шиной сигнала Конец преобразования , шестой вход блока анализа каждой декады соединен с выходом генератора тактовых сигнало а четвертый выход - с соответствующим входом второго элемента ИЛИ, управляющий вход которого подключен к выходу элементами, а выход к шине сигнала ошибки преобразовани

3. Устройство по п, 2, отличающееся тем, что блок анализа содержит элементы НЕ, И, ИЛИ, одновибратор и два триггера, входы которых соответственно подключены к второму и третьему входам блока

анализа и к выходам первого и второгц элементов И, первые входы которых соединены соответственно с первыми выходами второго и первого триггеров , вторые входы которых подключены соответственно к первым входам третьего и четвертого элементов И, второй вход третьего элемента И соединен с первьм входом .первого элемента И и через первый элемент

НЕ - с первым входом блока анализа, первым входом второгр элемента И, вторым входом четвертого элемента И и через одновибратор - с первым входом пятого элемента И, выход которого соединен со вторыми входами первого и второго элементов И, второй выход - с пятым входом блока анализа, второй вход которого соединен с первым входом шестого элемента И и третьим входом пятого элемента И, четвертый вход последнего пЬдключен к второму входу шестого элемента И и через второй элемент НЕ - к первому выходу блока анализа

5 и выходу элемента ИЛИ, первый вход которого через третий элемент НЕ соединен с четвертьм входом блока анализа, второй и третий в.ходы - с выходами соответственно,третьего и четвертого элементов И, четвертый вход - с пятБМ входом блока анализа,. . третий, вход которого соединен с третьим входом шестого элемента И, выход которого подключен к пятому выходу блока анализа.

Источники информации принятые во внимание при экспертизе

1.Полупроводникойые кодирующие и декодирующие преобразователи. Под ред. В.Б. Смолова, 1967, с. 151.

2.Преобразование информации в аналого-цифровых вычислительных устройствах и системах. Под ред. Г.М. Петрова, 1973, с. 265 (прототип) .

21 2t

0l/f.Z

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь последовательного уравновешивания | 1981 |

|

SU1030965A1 |

| Аналого-цифровой преобразователь считывания | 1977 |

|

SU677097A1 |

| Устройство для измерения амплитуды одиночных импульсных сигналов | 1980 |

|

SU960644A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU970680A1 |

| Устройство для измерения амплитуды одиночных импульсных сигналов | 1982 |

|

SU1112301A1 |

| Следящий аналого-цифровой преобразователь | 1978 |

|

SU738150A1 |

| Следящий аналого-цифровой преобразователь | 1984 |

|

SU1228282A1 |

| Устройство для измерения максимального значения сигналов | 1977 |

|

SU739424A1 |

| Преобразователь напряжения в код | 1977 |

|

SU728222A1 |

| Многоканальный аналого-цифровой преобразователь | 1980 |

|

SU993468A1 |

Авторы

Даты

1982-10-07—Публикация

1979-08-10—Подача