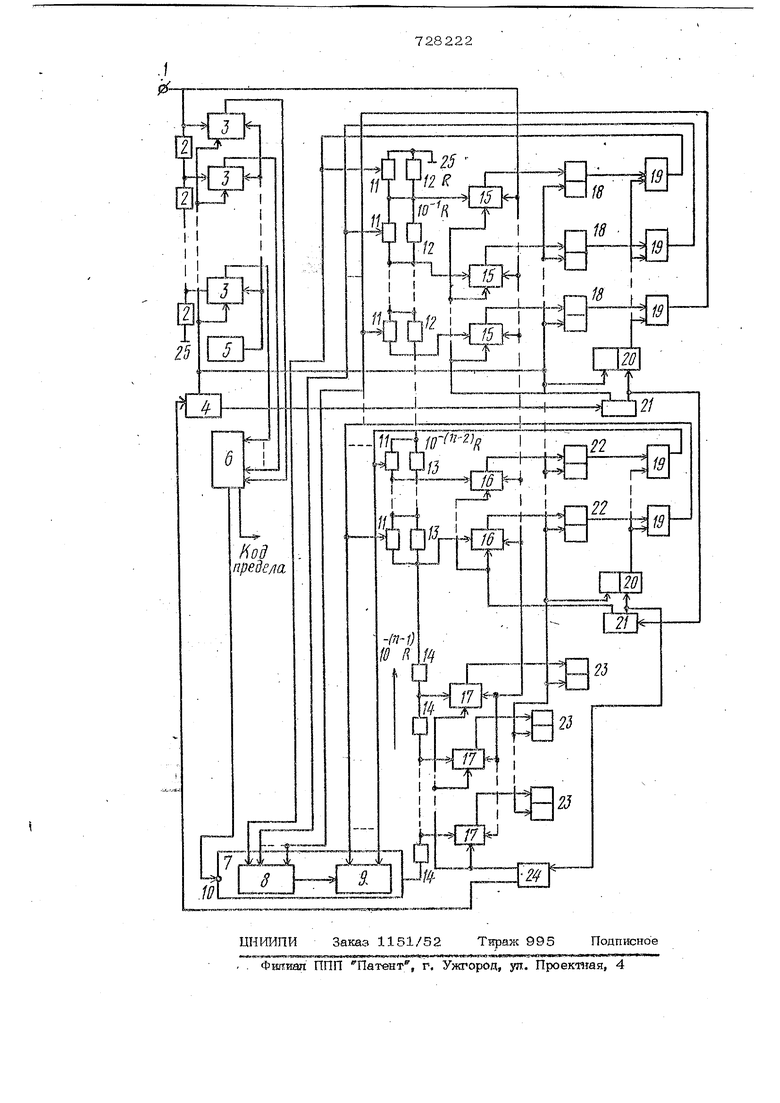

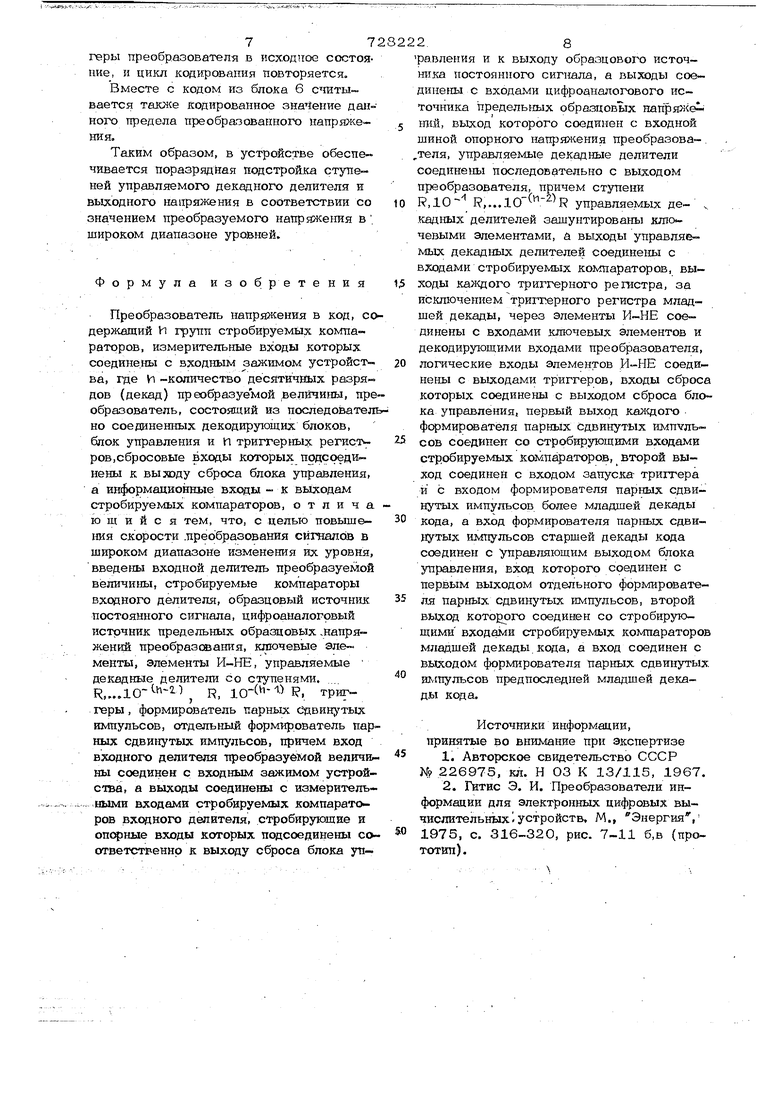

Изобретение относится к цифровой измерительной и вычислительной технике и может быть использовано в цифровых измерительных установках и системах для цифрового измерения (кодирования) сиг налов напряжения в широком диапазоне их уровня и спектра. Известен преобразователь напрян ения в код (ПНК) параллельного считьшания с поразрядным распространением сигнала, который содержит ряд каскадов сравнения - компараторов кодируемого и образцового (от1орно)го) напряжений, каждый из которых формирует весовой ток для соседних каскадов более младших разрядов, пропорциональный разности сравнивае мых сигналов. Весовые токи преобразуют ся специальными элементами в образцовые напряжения |l , Недостатком устройства является снижение его быстродействия при расширении пределов измерения по уровню измеряемой величины, так как при этом требует ся дополнительное время на анализ н выбор предела. Известен преобразователь;напряжения в код, содержащий И групп стробируемых компараторов, измерительные входы которых соединеЕгы с входным зажимом устройства, где h- количество десятич- . tfflix разрядов (декад) преобразуемой величины, преобразователь, состоящий из последовательно соединенных декодирующих блоков, блока управления и триггерных регистров, сбросовые входы которых подсоединены к входу сброса блока управления, а ин(}юрмац ионные входы - к выходам стробируемых компараторов 2. Недостатком устройства является наличие большого числа преобразователей кода в Напряжение в каскаде, каждый из которых формирует опорное напряжение для отдельного компаратора данного каскада. Кроме того, при расширении рабочего диапазона уровней измеряемой величины снижется быстродействие устройства, так как требуется доттолннтель ное. время на выбор предела измерения. Иелыо изобретения являетсяповьпяёние .скорости преобразовшшя сигналов в широком диапазоне изменений их уровня. Для этого в тфеобразователь напряжения в код, содержащий h групп стро бируедмых компараторов, преобразователь, блок управления, П триггерных регис1 ров, введены . входной делитель преобра35-емой величины; стробируе1у1ые компара тбры входного, делителя, образцовый ис,трчиик постоянного сигнала, цифроана- логрвый источник предельных образцовых напряжений преобразования, ключевые элементы, элементы , управляемые дёкад1-1ые делители со ступенями R,.., ,. триггеры, фор мирователь парных сдвинутых импульсов, отдельный формирователь napraix сдвинутых импульсов, причем вход входного делителя преобразуемой величины соединен с входным зажимом и устройства, и входы соединены с измерительными входами стробируемых компараторов входного де. лителя, стробирующие и опорные входы которых подсоединены соответственно к выходу сброса блока управления и к выходу образцового источника постояннохх) сигнала, а выходы соединены с входами цифроаналогового источника предельЕих образцовых напряшсений, выход которого соединен со входной шиной опорнохчэ напряжения преобразователя, управляемгле декадные делители соединены послед она, тельно с выходом преобразователя, при-. чем ступени R, ,... уп-равляемых декадных делителей зашунтировагш ключевыми элементами, а вькоды управляемых декадшлх делителей соэди гюны с -входами стробируемых компара- торов, выходы трилгерного регистра за исключением тригг рного регистра младшей декады, черер элементы И-НЕ соединены с входами {бяочевых эле ментов и декодирукяцшли входами преобразсавателя, попагческие входы элементов Й-НЁ соединены с выходами триггеров, входы сброса /которых сседияены с ёыходом сброса бло1ш управления, первый вы ход каждого ффмирователя парных сдвинутых импульсов соединен со стробирующвми входами стробируемых компараторо второй выход соединен с входом запуска триггера и с входом формирователя парных сдвинутых импульсов более младшей декады кода, а вход формирователя пар|Ных сдвинутых импульсов старшей декады кода соединен с управлжощим выходом блока управления, вход Кот.ороГо со&дй йен с первым выходом отдельного формирователя парных сдвинутых импульсов,, второй выход которого соединен со стробирующими входами.стробируе1Д4х компараторов младшей декады кода, а вход соединен с выходом формирователя сдвинутых импульсов предпоследней младшей де1{ады кода« . На чертеже приведена структурная электрическая схема устройства.; Устройство содержит входной зажим 1 устройства; входной делитель 2 преобразуемой величины; стробируемые компараторы 3 входного делителя; блок 4 управления; образцовый источник 5 постоянного сигнала; цифроаналоговый источник 6 предельных обра:зцовых напряжений преобразования; преобразователь 7 параллельного едишгчнохх) кода в образцовое опорное напряжение; декодирующие блоки 8, 9 преобразователя 7 соответственно от : старшей до предпоследней младшей декады; входную шину. 10 опорного напряжения; ключевые элементы 11; управляемые декадные делители 12, 13, 14 соответственно со ступенями ) стробируемые компараторы 15-формиро ватели кода старшей декады; стробируемые комп аторы 16,17- формирователи кода соответственно предпоследней младшей и младшей декад; триггерный регистр 18 старшей декады кода; логические элементы И-НЕ 19; триггер 20„ формирователь 21 парных сдвинутых импульсов; трипгерные регистры 22, 23 соответственно .предпсюледней младшей и младшей декад кода; отдельный формирователь 24 парнь х CiDiви0yтыx импульсов; общую шину 25.-. -. Устройство работает следующим образом. Преобразуемая (кодируемая) величина, поступающая на входной зажим 1, передается непосредственно, на измерительные входы всех стробируемых компараторов 14, 15, 16, а через ступени входного делителя 2 одновременно и на стробируе1Л 1ё компараторы 3. Число ступеней ВХОДНО1Х) делителя выбирают исходя из; требуемого количества пределов измерений, а соотношение величин ступеней в соответствии со значением младшегч) тфедела. На опорный, вход всех стробируемых комйараторов 3 подается опорное напряжение образцового источника 5, равное младшему пределу измерений. Измеряема ведичи1ш распределяется по стробируемы компараторам 3 в соответствии со ступе нями входного делителя 2, уменьшаясь в направлении стробируемого компаратора наибольшего из. пределов, подключенного к послед ней ступени входного делителя 2. Так как в устройстве операции вьтолня ются с десятичным позиционным (параллельным единичным) кодом, то ступени входного делителя выбираются равными R, 101,: .. .., , где к - число пределов измерения; п;редставтгющее собой натуральный ряд. При сравнении измеряемого напряже .ния с опорным в стробируетуых компараторах 3 часть из них в соответствии с пределом измеряемой величины срабо тает и переключит цифроаналоговый источник 6 таким образом, что на его выходе появится напряжение,ипр равное пределу измеряемой величины. Это напря жение в качестве опорного подводится к входу 10 преобразователя 7. Описанный такт работы выполняется в соответствии с сигналом стробирования, формируемым в блоке- 4, который передается на cooTV ветствуюший вход стробируемых icoMnapaторов 3. Этим же сигналом ,элементы и все устройстве устанавливаются (сбрасываются) в исходное состояние. К выходу преобразователя 7 подключены управляемые декадные делители 12 13, 14, которые содержат соответствейгно по9 ступеней,, 9 ступеней, R-10-,..., 9 ступеней R-IO и 10 ступеней R10 . В исходном состоянии все ключевые элементы 11 рт крыты, сопротивление управляемых декадных делителей 12, 13, 14 максимально и на выходе преобразователя 7 напряжение равно выбранному пределу, которое распределяется с постоянным приращением. i По сигналу, поступившему из блока 4 в формирователь 21, формируется импульс стробирования стробируемых компараторов 15, и часть из них, в соответ ствии со значением К (К 1...9)- старшехчз разряда кода измеряемой вeличишЛi сработает и переключит подключенный к. шш триггерный регистр IS старшего разряда кода.- С задержкой, необходимой для срабатывания стробируемых компараторов 15 и переключения триггерного регистра 18, в формирователе 21 формируется второй импульс. Этот импульс переключает триггер 2О, выходной сиггтл которого поступает на группу злемейтов И-НЕ 19, подключеш1ых к триггерному регистру 18. При этом на выходе элементов И-НЕ 19 в цепи не сработавших стробируемых компараторов 15 появятся сигналы, которые включат соответи. ствуюшие ключевые элементы 11 и переключат декодирующий блок 8. На преобразователя 7 установится.напряжение UQ, , равное преобразуемому округленному на уровне старшего разряда кода преобразуемой величины до бли}кайшего большего целого значения. Второй задержанный импульс, сформированный в формирователе 21, передаетчся в аналогичный формирователь 21 в цепи стробирования стробируемых компа- раторов 16 следуюших ступеней делителя, равных О,1 R (на чертеже не обозначены). Формируется код К,, , который запоминается в соответствующем триггер ном регистре, и опорное напряжение (J изменяется на и on 2 измеряемому, округленному На уровне второго десятичного разряда преобразуемой величины до блилсайшегч большего целого значения. Далее процесс формирования кодов повторяется. По мере формирования код6в К и напряжений отключаются (шунтируются) соответствующие ступени управляемых декадных делителей 12, 13, бла-. годаря чему приращение напряжения на -нешунтированной ступени и подключенному к ней стробируемому компаратору все время остается неизменным. Посте формирования кода К на выходе преобразователя 7 установится напряладние и оп (n--i) - соответствующем отдельном формирователе 24 будет сформирован импульс стробирования стробируемых компараторов 17, которые выдадут код к, младшей декады. Этот код запишется в триггерном регистре 23 младшей декады кода. Тем самым будет сформирован импульс стробирования стробируемых компараторов 17, которые выдадут код KVI младшей декады. Этот код запишется в триггераом регистре 23 младшей декады кода. Тем самым будет завершен цикл преобразования входной величины, о чем соответствующий формирователь 24 сигнализирует блоку 4. Разряды кода по этому сигналу могут быть считаны из триггерных регист ров 18 22, 23 (цепи считывания на чертеже не указаны), после чего блок управления сбрасывает все триггеры преобразователя Б исходиое состояние, и цикл кодирования повторяется. Вместе с кодом из блока 6 считы вается таклсе кодированное значение данного предела преобразованного напряжеНИН, Таким образом, в устройстве обеспечивается поразрядная Г одстрой.ка ступеней управляемого декадногчэ делителя и выходного напряжения в соответствии со значением преобразуемого напряжения в; широком диапазоне уровней. Формула изобретения Преобразователь напряжения в код, со держащий И групп стробируемых компараторов, измерительные входы которых соедине.ны с входным зажимом устройства, где h -количество десятичных разрядов (декад) преобразуемой величины, пре образователь, состоящий из последовател но соединенных декодирующих блоков, блок управления и И триггерных регистров,сбросовые входы которых подсоединены к выходу сброса блока управления, а информационные входы - к выходам стробируемых компараторов, отлича ющийся тем, что, с целью повышения скорости .преобразования сйтеалов в широком диапазоне изменения их уровня, введены входной делитель преобразуемой величины, стробируемые компараторы входногч) делителя, образцовый источник постоянного сигнала, цифроаналоговый истрчник предельных образцовых .напряжений преобраз(жашгя, ключевые эле менты, элементы И-НЕ, управляемые декадные делители со ступенями. R,... R, I, триггеры , формирователь парных Сдвинутых импульсов, отдельный формирователь пар ных сдвинутых импульсов, причем вход входного делителя тфеобразуемой вепичи ны соединен с входным зажимом устройства, а выходы соединены с измерительными входами стробируемых компараторов входного делителя, стробируюшие и )шде входы которых подсоединены со ответственно к выходу сброса блока уп- равлеиия и к выходу образцового источника постоянного сигнала, а выходы соединены с входами цифроаналогового источника предельных образцовых напряже НИИ, выход которого соединен с входной шиной опорного напряжения преобразова-. теля, управляемые декадные делители соединены последовательно с выходом преобразователя, причем ступени R,10- R. управляемых де- , .кадных делителей зашунтированы кшочевыми элементами, и выходы управляемых декадных делителей соединены с входами стробируемых компараторов, выходы каждого триггерного регастра, за исключением триггерного регистра младшей декады, через элементы И-НЕ сое динены с входами ключевых элементов и декодирующими входами преобразователя, логические входы элементов И-НЕ соединены с выходами тр1иггеров, входы сброса которых соединены с выходом сброса блока управления, первый выход калсдого формирователя парных сдвинутых ИМПУЛЬСОВ соединер со стробирующими входами стробируемых компараторов, второй выход соединен с входом запуска- триггера и с входом формирователя парных сдвинутых импульсов более младшей декады кода, а вход формирователя парных сдвинутых импульсов старшей декады кода соединен с управляющим выходом блока управления, вход которого соединен с первым выходом отдельного формирователя парных сдвинутых импульсов, второй выход которого соединен со стробирующими входами стробируемых компараторов младшей декады кода, а вход соединен с выходом формирователя парных сдвинутых. иЬ пульсов предпоследней младшей декады кода. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР №226975, кл. Н ОЗ К 13/115, 1967. 2.Гитнс Э. И. Преобразователи информации для электронных цифровых вычислительных 1 устройств, М., Энергия / 1975, с. 316-320, рис. 7-11 б,в (прототип) . т

,4 4-«s«.4I-««-/f.,n / I i I , u г--СШи I I P Т 1l«™, J ™Ij 1 W.™-W«™Jj

Авторы

Даты

1980-04-15—Публикация

1977-07-01—Подача