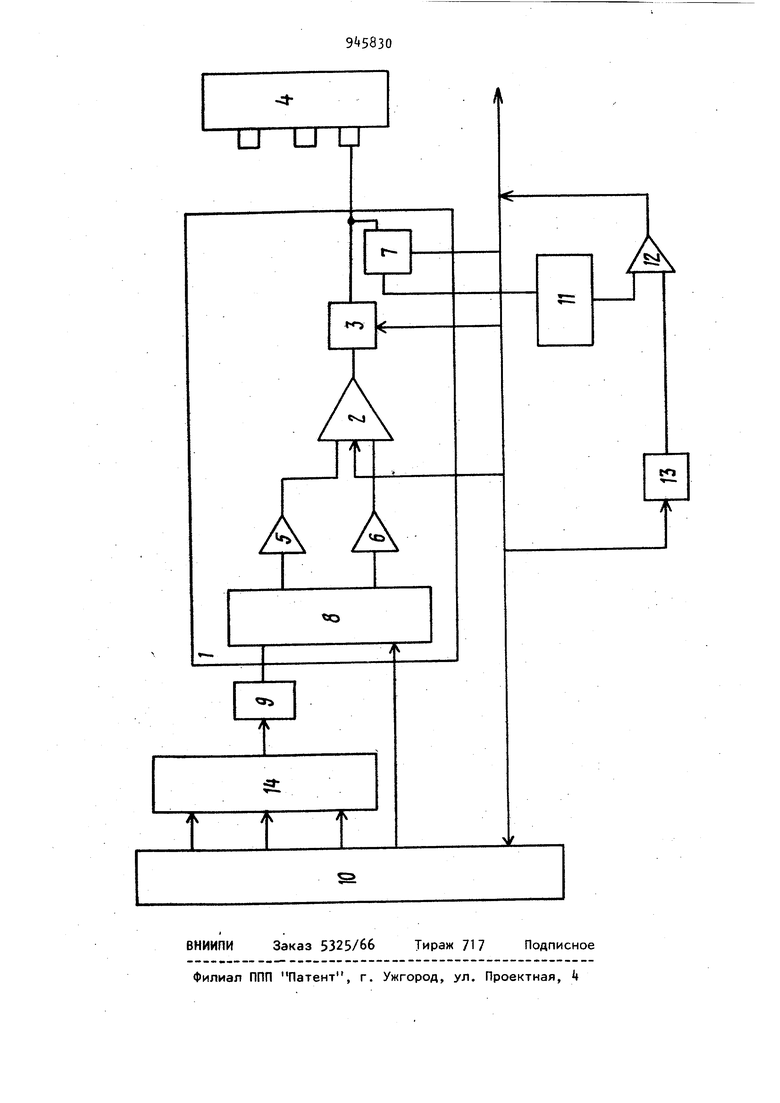

Изобретение относится к контроль но-измерительной технике и может быт использовано при контроле электронны блоков. Известно устройство для контроля электронных схем, содержащее блок управления, коммутатор, аналоговые элементы памяти, элементы коммутации, цифроаналоговый преобразовател формирователь входных сигналов 1. Недостатком этого устройства является низкая достоверность контроля из-за отсутствия предварительной калибровки входных уровней, используемых для контроля электронного блока. Наиболее близким к изобретению техническим решением является устройство для тестового контроля цифровых узлов цифровой вычислительной машины, содержащее блок управления, включающий регистр управления и регистр теста, цифроаналоговый преоб разователь, включающий блок опорных напряжений, дешифратор и переключатель, компаратор 2 . Недостатком известного устройства является низкое быстродействие, обусловленное тем, что калибровка входных напряжений происходит каждый раз при подаче нового контролируемого теста, при этом требуются значительные затраты времени на срабатывание цепи обратной связи формирователя для установления входного сигналаЦель изобретения - повышение быстродействия устройстваПоставленная цель достигается тем, что в выходной узел тестера для контроля электронных блоков, содержащий блок памяти, блок управления, соединенный первым выходом через первый цифроаналоговый преобразователь с первым входом компаратора, введены второй цифроаналоговый преобразователь, масштабирующий преобразователь по числу выводов электронного блока, коммутатор, первый и второй аналоговые элементы памяти, формиро ватель входных сигналов, первый и второй элементы коммутации, причем первый вход коммутатора соединен через второй цифроаналоговый преобра зователь и блок памяти с вторым выходом блока управления, второй вход с третьим выходом блока управления, первым и вторым выходами соответственно через первый и второй элемен ты аналоговой памяти - с первым и вторым входа 1и формирователя входных сигналов, третий вход которого соединен с четвертым выходом блока управления, выход - с входом первого элемента коммутации, соединенного вторым входом с пятым выходом блока управления, выходом - с входом контролируемого электронного блока и пер вым входом второго элемента коммутации, второй вход которого соединен с шестым выходом блока управлени выход через масштабирующий преобразователь с входом блока управления. На чертеже приведена блок-схема выходного узла. Выходной узел содержит блок 1 фор мирования входных сигналов, формирователь 2 входных сигналов, первый элемент 3 коммутации, контролируемый электронный блок , первый 5 и второй 6 аналоговые элементы памяти, второй элемент 7 коммутации, коммутатор 8, второй цифроаналоговый преобразователь 9, блок 10 управления, масштабирукяций преобразовател П, компаратор 12, первый цифроанало говый преобразователь 13 и блок 1 памяти. Выходной узел тестера для контрол электронных блоков содержит блок управления, соединенный первым выходом с первым входом формирователя уровней, вторым выходом с входом пер вого цифроаналогового преобразователя , соединенного выходом с первым входом компаратора. Устройство работает в режимах калибровки и формирования сигналов. В режиме калибровки, например высокого уровня, блок 10 управления включает формирователь 2 соответству ющего блока 1 формирования сигналов в режим формирования на выводе контролируемого блока 4 сигнала высокогоуровня. Одновременно блок управления замыкает элементы 3 и 7 на входе и соответственно на выходе цифроаналогового преобразователя 13 устанавливает сигнал, соответствующий эталонному сигналу высокого, уровня и, управляя коммутатором 8, обеспечивает прохождение сигнала от преобразователя 9 через элемент памят14 5 на вход формирователя 2. Компаратор 12 сравнивает уровень сигнала на выводе контролируемого блока , приведенный с помощью преобразователя 11 к масштабу преобразователя 13 с эталонным сигналом и выдает результат сравнения в блок 10 управления, который включает блок 1A памяти в режим записи по установленному адресу, соответствующему данному выводу блока k, состояния компаратора 12. Информация на выходе блока И памяти преобразуется в аналоговый сигнал, который через коммутатор 8 поступает на вход соответствующего аналогового элемента 5 памяти и далее поступает на вход высокого уровуровня формирователя 2, с выхода которого через элемент 3 коммутации поступает на вывод контролируемого блока 4. С вывода блока через элемент 7 и преобразователь 11 фактический уровень сигнала поступает на вход компаратора 12, где сравнивается с эталонным уровнем сигнала, поступающим с выхода преобразователя 13 Информация по установленному адресу в блоке I памяти с помощью компаратора 12 и блока 10 управления измедо тех пор, пока компаратор няется 12 не зафиксирует равенство фактического уровня сигнала на контролируемом выводе его эталонному значению. . В режиме калибровки (сигнал низкого уровня) устройство работает аналогично. По окончании калибровки в соответствующих ячейках блока И памяти записаны цифровые эквиваленты эталонных уровней сигналов с учетом погрешностей цифроаналогового преобразователя 9, аналоговых элементов 5 памяти, формирователей 2 и элемента коммутации 3. Проведение калибровки обеспечивает автоматическую компенсацию погрешностей, обусловленных временным и температурным дрейфом параметров преобразователя Э, элементов 5 и 6, формирователя 2 и. элемента 3 за счет того, что входные уровни на блок устанавливаются с учетом этих погрешностей.

в режиме формирования входных сиг налов цифровая информация о величине входного уровня данного вывода по сигналу с блока 10 переписывается из соответствующей ячейки памяти блока через преобразователь 9 и коммутатор 8 в элемент 5 аналоговой памяти, хранящий значение высокого уровня напряжения, и элемент 6 аналоговой памяти , хранящий значение низкого уровня напряжения по данному выводу блока .

По сигналу с блока 10, поступающему на вход.формирователя 2 и определяющему, какой логический уровень необходимо сформировать на данном выводе, в данном тесте формирователь 2 пропускает на вход блока уровень логического нуля с элемента 6 или уровень логической единицы с элемента 5.

Таким образом, введение преобразователей, а также соответствующее выполнение блока формирования уровней позволяет производить калибровку однократно перед режимом контроля и формирования входных сигналов, а не при каждой очередной смене кон- тролирующего теста, как в известном устройстве, что повышает быстродействие устройства.

Формула изобретения

Выходной узел тестера для контроля электронных блоков, содержащий блок памяти, Злок управления, соединенный первым выходом через первый цифроаналоговый преобразователь с

5830

первым входом компаратора, отличающийся тем, что,с целью повышения быстродействия узла в него введены второй цифроаналоговый

5 преобразователь, масштабирующий преобразователь по числу выводов электронного блока, коммутатор,первый и второй аналоговый элементы . памяти, формирователь входных сигналов, первый и второй элементы коммутации, причем первый вход коммутагора соединен через второй цифроаналоговый преобразователь и блок памяти с вторым выходом блока управления, второй вход - с третьим выходом блока управления, первым и вторым выходами соответственно через первый и второй аналоговые элементы памятис первым и вторым входами формирователя входных сигналов, третий вход которого соединен с четвертым выходом блока управления, выход - с входом первого элемента коммутации, соединенного вторым входом с пятым выходом блока управления, быход - с входом контролируемого эталонного блока и первым входом второго элемента коммутации, второй вход которого соединен с шестым выходом блока управления, выход через масштабирунхций преобразователь - с входом блока управления.

Источники информации, принятые во внимание при экспертизе 1.Патент США № 36228/6,

кл. 32it-73, 1971.

2. Авторское свидетельство СССР № , кл. G 06 F ll/0tt 1978 (прототип).

U ULJ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля параметров электронных схем | 1982 |

|

SU1112324A1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Устройство контроля параметров | 1990 |

|

SU1800447A1 |

| Устройство для контроля цифровыхСХЕМ | 1979 |

|

SU849217A1 |

| Устройство для контроля больших интегральных схем памяти | 1980 |

|

SU926727A1 |

| Устройство для записи и контроля программируемых блоков постоянной памяти | 1978 |

|

SU911613A2 |

| Устройство для контроля схем цифровых вычислительных машин | 1978 |

|

SU734691A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 1991 |

|

RU2106677C1 |

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

A

Авторы

Даты

1982-07-23—Публикация

1980-09-22—Подача