ков формирователя адреса записи соединены соответственно с первыми и вторыми входами ервого и второго дешифраторов устройства, выход первого регистра формирователя адреса записи соединен с адресным входом постоянной памяти формирователя адреса задней, выход которой соединен с информационными входами второг и третьего регистров формирователя адреса записи, выходы которых соединены соответственно с информационным входом первого накапливающего сумматора и с информационным входом второго накапливающего сумматора,входы синхронизации которых соединены со счетными входами первого, второго и третьего счетчиков формирователя адреса записи и с первым выходом делителя частоты импульсов формирователя адреса записи, второй выход которого соединен с входом разрешения чтения постоянной памяти формирователи адреса записи,и с входами записи второго и третьего регистров формирователя адреса записи,выходы первого и второго накапливающих сумматоров соединены соответственно с информационными входами младших разрядов первого и второго счетчиков формирователя адреса записи, выход переполнения третьего счетчика формирователя адреса запис соединен с первым входом элемента РШИ формирователя адреса записи, выход которого соединен с входо блокировки работы делителя частоты импульсов формирователя адреса записи, четвертый выход первой группы выходов синхронизатора устройства соединен со счетным входом счетчика устройства, первый, второй, третий и четвертый информационные входы первого и второго коммутаторов соединены соответственно с выходом второго дешифратора устройства, с пятым выходом первой группы выходов .синхронизатора устройства, с первым выходом регистра устройства и с вторым выходом регистра устройства, группы управляющих входов первого и второго коммутаторов соединены с группой выходов постоянной памяти блока выбора памяти, выходы первого и второго коммутаторов соединены соответст.венно с информационными входами блоков памяти первой и второй групп, шестой и седьмой выходы первой группы выходов синхронизатора устройства соединены соответственно со счетным входом счетчика блока выбора памяти и с управляющим входом третьего коммутатора, первый и второй информационные входы которого соединены соответственно с выходами блоков памяти первой и второй групп, группа информационных выходов счетчика блока выбора памяти соединена с группой входов дешифратора блока выбора памяти, группа выходов которого соединена через регистр блока выбора памяти с группой адресных входов постоянной памяти блока выбора памяти, выход третьего коммутатора соединен с информационным входом четвертого коммутатора, группа управляюш 1х входов которого соединена с второй группой выходов синхронизатора устройства, выход четвертого коммутатора является выходом устройства, отличающееся тем, что, с целью повыщения быстродействия, оно дополнительно содержит пятый шестой, седьмой и восьмой коммутаторы, два формирователя исполнительного адреса, каждый из которых содержит четыре коммутатора и два регистра, формирователь режимов работы, содержащий два дешифратора, формирователь условий записи, содержащий схему сравнения, дешифратор , элемент ИЛИ и элемент И, причем группа информационных выходов счетчика устройства соединена с первыми группами информационных входов первого, второго и третьего коммутаторов каждого формирователя исполнительнога адреса и с группами входов первого и второго дешифраторов формирователя режимов работы, первый вход второй группы информационных вхдов первого коммутатора каждого формрователя исполнительного адреса соединен с первым входом первой группы информационных входов четвертого коммутатора каждого формирователя исполнительного адреса, с информационным выходом первого счетчика формирователя адреса записи, с первым входом первой группы информационных входов схемы сравнения и с первым входом депмфратора формирователя условий записи, второй вход второй группы информационных входов первого коммутатора кавдого формирователя исполнительного адреса соединен с вторым входом первой группы

информационных входов четвертЬго коммутатора каждого формирователя исполнительного адреса, с информационным выходом второго счетчика формирователя адреса записи, с вторым входом первой группы информационных входов схемы сравнения и с вторьм входом дешифратора формирователя условий записи, восьмой выход первой группы выходов синхронизатора устройства соединен с управляющими входами первого, второго, третьего и четвертого коммутаторов казкдого формирователя исполнительного адреса вторые группы информационных входов второго и третьего коммутаторов каждого формирователя исполнительного адреса соединены с группой выходо.в постоянной памяти блока выбора памяти, с первыми группами информационны входов пятого, шестого, седьмого и восьмого коммутаторов и с второй группой информащюнных входов схемы сравнения, выход которой соединен с первым входом элемента ИЛИ формирователя условий записи, второй вход которого соединен с выходом дешифратора формирователя условий записи, выход элемента ИЛИ формирователя условий соединен с первым входом элемента И формирователя условий записи и с вторым входом элемента ИЛИ формирователя адреса записи, второй вход элемента И формирователя .условий записи соединен с девятым выходом первой группы выходов синхронизатора устройства, выход элемента И формирователя условий записи соединен с пятыми информационными входами первого и второго коммутаторов, выходы второго и третьего коммутаторов каждого формирователя исполнительного адреса соединены

5043

соответственно с входами записи первого и второго регистров каждого формирователя исполнительного адреса, выходы первого и четвертого коммутаторов каждого формирователя исполнительного адреса соединены соответственно с информационными входами первого и второго регистров каждого формирователя исполнительного адреса, выход первого регистра каждого формирователя исполнительного адреса соединен с вторым информационным входом четвертого коммутатора каждого формирователя исполнительного адреса, выход первого дешифратора устройства соединен с первыми управляющими входами пятого и седьмого коммутаторов, выход первого дешифратора формирователя режимов работы соединение вторыми управляющими входами пятого и седьмого коммутаторов, i -е выходы ( 1,2, ...,П) пятого и седьмого коммутаторов соединены соответственно с входами синхронизации 1 -го блока памяти первой и второй групп, выход второго дешифратора формирователя режимов работы соединен с управляющими входами шестого и восьмого коммутаторов, выходы которых сое динены соответственно с входами чте. ния, записи блоков памяти первой и второй групп, выходы первого и второго регистров первого формирователя исполнительного адреса соединены соответственно с адресными входами младших и старших разрядов блоков памяти первой группы, выходы первого и второго регистров второго формирователя исполнительного адреса соединены соответственно с адресными входами младших и старших разрядов блоков памяти второй группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения видеосигнала | 1987 |

|

SU1555918A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1233149A1 |

| Устройство для отображения информации | 1986 |

|

SU1367037A1 |

| Контурная система программного управления | 1989 |

|

SU1681298A1 |

| Устройство для опроса информационных каналов | 1982 |

|

SU1062677A1 |

| Устройство для отображения информации | 1983 |

|

SU1193722A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1984 |

|

SU1241281A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для сигнализации с индикацией местоположения аварийного объекта | 1982 |

|

SU1121689A1 |

УСТРОЙСТВО ДЛЯ ВВОДА И ВЫВОДА ДИНАМИЧЕСКИ ИЗМЕНЯЮЩЕЙСЯ ИНФОРМАЦИИ, содержащее входной запоминающий блок, блок анализа команд, содержащий счетчик, регистр, делитель частоты импульсов, блок дешифраторов и элемент И, счетчик, формирователь адреса записи,, содержащий три регистра, делитель частоты импульсов, два накапливающих сумматора, постоянную память, три счетчика и элемент ИЛИ, два дешифратора, регистр, четьфе коммутатора, блок выбора памяти, содержащий счетчик, дешифратор,регистр и постоянную память, блок элементов И, синхронизатор и две группы П блоков памяти (),причем информационньй вход входного запоминающего блока является входом устройства, вход чтения-записи входного запоминающего блока соединен с первым выходом первой группы выходов синхронизатора, адресньй вход входного запоминающего блока соединен с информационным выходом счетчика блока анализа команд, информационный вход которого соединен с информационным входом регистра блока анализа команд и-с первым выходом входного запоминающего блока, второй выход которого соединен с информационным входом первого регистра формирователя адреса записи и третьего счетчика формирователя адреса записи и с информационными входами старших разрядов первого и второго счетчиков формирователя адреса записи, третий выход входного запоминающего блока соединен с информационным входом регистра устройства, счетный вход делителя частоты импульсов соединен с вторым выходом первой группы выходов синхронизатора, пер(Л вый и второй выходы дешифратора блока анализа команд соединены соответственно с входом записи-чтения регистра устройства и с входами записи первого регистра формирователя адреса и первого, второго и третьего счетчиков формирователя адреса записи, тактовый вход делителя частоты импульсов формирователя адреса запиУ1 си соединен с третьим выходом первой группы выходов Синхронизатора, 4 счётный вход счетчика блока анализа команд соединен с входом записи регистра блока анализа команд и с выходе элемента И блока анализа ко.манд, первый и второй выходы которого, соединены соответственно с выходом делителя частоты импульсов блока анализа команд и с третьим выходом дешифратора блока анализа команд,вход которого соединен с выходом регистра блока анализа команд, информацион ные выходы второго и третьего счетчи

Изобретение относится к электронньм дискретным устройствам автоматики, телемеханики и вычислительной техники и предназначено для ввода, обработки и вывода динамически изме няющеййя информации.

Известно устройство для ввода и вьшода динамически изменяющейся информации, содержащее источник информации, соединенный со спецвычислите-г лем и процессором,которьй связан с синхронизатором и через схему управления соединен с выходным накопителем Cll Недостатком устройства является наличие в аппаратуре выходного накопителя, емкость которого (в битах) определяется максимальной информативностью периферийного оборудования что увеличивает затраты оборудования стоимость, энергопотребление и снижа ет надежность изделия. Наиболее близким по технической сущности к изобретению является устройство, содержащее входной запоминающий блок, блок анализа кома.нд содержащий счетчик, регистр, делитель частоты импульсов, блок дешифраторов и элемент И, счетчик, формирователь адреса записи, содержащий три регистра, делитель частоты импульсов, два накапливающих сумматора постоянную память, три счетчика и элемент ИЛИ, два дешифратора, регистр, .четыре коммутатора, блок выбора памяти, содержащий счетчик, дешифратор, регистр и постоянную память, синхронизатор и две группы п блоков Памяти (tlV2), причем информационный вход входного запоминающего блока является входом устройства, вход чтения-записи запоминающего бло ка соединен с первым выходом первой группы выходов синхронизатора, адрес ный вход входного запоминающего блока - с информационным выходом счетчика блока анализа команд, информационный вход которого соединен с информационньм входом регистра блока анализа команд и с первым выходом входного запоминающего блока, второ , выход которого соединен с информацио ным входом первого регистра формирователя адреса записи и третьего счет чика формирователя адреса и с информационными входами старпшх разрядов первого и второго счетчиков формиро вателя адреса записи, третий выход входного запоминающего блока - с информационным входом регистра устрой ства, счетный вход делителя частоты импульсов - с вторым выходом первой группы выходов синхронизатора,первы и второй выходы дешифратора блока анализа команд - соответственно с входом записи-чтения регистра устройства и с входами записи первого регистра формирователя адреса записи и первого, второго и третьего счетчиков формирователя адреса за134 писи, тактовый вход делителя частоты импульсов формирователя адреса записи - с третьим выходом первой группы выходов синхронизатора, счетный вход счетчика блока анализа команд - с входом записи регистра блока анализа команд и с выходом элемента И блока анализа команд, первый и второй входы которого соединены соответственно с выходом .делителя частоты импульсов блока анализа команд и с третьим выходом дешифратора блока анализа команд, вход которого соединен с выходом регистра блока анализа команд, информационные выходы второго и третьего счетчиков формирователя адреса записи - соответственно с первыми и вторыми входами первого и второго дешифраторов устройства, выход первого регистра формирователя адреса записи соединен с. адресным входом постоянной памяти формирователя адреса записи, выход которой соединен с информационными входами второго и третьего регистров формирователя адреса записи, выходы которых соединены соответственно с информационным входом первого накапливающего сумматора и с информационным входом второго накапливающего сумматора, входы синхронизации которых соединены со счетными входами первого, второго и третьего счетчиков формирователя адреса записи и с первым выходом делителя частоты импульсов формирователя адреса записи, второй выход которого соединен с входом разрешения чтения постоянной памяти формирователя адреса записи и с входами записи второго и третьего регистров формирователя адреса записи, выходы первого и второго накапливаюш:их сумматоров - соответст1венно с информационными входами младших разрядов первого и второго счетчиков формирователя адреса записи, выход переполнения третьего счетчика формирователя адреса записи соединен с первым входом элемента ИЛИ формирователя адреса записи, выход которого соединен с входом блокировки работы делителя частоты импульсов формирователя адреса записи, четвертьй выход первой.группы выходов синхронизатора устройства - со счетным входом счетчика устройства, первый, второй, третий и четвертый информа5 . ционные входы первого и второго ко мутаторов - соответственно с выходо второго дешифратора устройства, с пятым выходом первой группы выходов синхронизатора устройства, с первым выходом регистра устройства и с вторым выходом регистра устройства, группы управляющих входов первого и второго коммутаторов соединены с группой выходов постоянной памяти блока выбора памяти, выходы первого и второго коммутаторов соединены со ответственно с информационными вход ми блоков памяти первой и второй групп, шестой и седьмой выходы первой группы выходов синхронизатора устройства соединены соответственно со счетным входом счетчика блока вы бора памяти и с управляющим входом третьего коммутатора, первый и второй информационные входы которого соединены соответственно с выходами блоков памяти первой и второй групп группа информационных выходов счетчика блока выбора памяти - с группой входов дешифратора блока выбора памяти, группа выходов которого соединена через регистр блока выбор памяти с группой адресных входов постоянной памяти блока выбора памя ти, выход третьего коммутатора с информационным входом четвертого коммутатора, группа управляющих входов которого соединена с вторбй группой выходов синхронизатора устройства, вьгход четвертого коммутатора является выходом устройства 2. Структура известного устройства позволяет снизить объем выходного накопителя за счет разбиения послед него на четыре зоны, управляемые независимо. При этом если содержимое первой зоны выходного накопителя считьгеается синхронно с работой периферийного оборудования, то в три других зоны записывается та информация, которая должна будет считываться по окончании работы с первой зоной. Такая организация выходного накопителя приводит к необходимости предварительной сортировки статичес кой информации и к необходимости решения.программно-аппаратными сред ствами в реальном масштабе времени задачи привязки к зонам выходного накопителя динамически изменяю 3 .щейся информации. Это влечет за собой дополнитепьные затраты времени на предварительную сортировку информации. Целью изобретения является повышение быстродействия устройства за счет разгрузки программных средств и канала обмена с внешними вычислительными средствами, Поставленная цель достигается тем, что в устройство для ввода и вывода динамически изменяющейся информации, содержащее входной запоминающий блок, блок анализа команд, содержащий,счетчик, регистр, делитель частоты импульсов, блок дешифраторов и элемент И, счетчик, формирователь адреса записи, содержащий три регистра, делитель частоты импульсов, два накапливающих сумма- . тора, постоянную память, три счетчика и элемент ИЛИ, два дешифратора, регистр, четыре коммутатора, блок выбора памяти, содержащий счетчик, дешифратор, регистр и постоянную память, синхронизатор и две группы И блоков памяти (), причем информационный вход входного запоминающего блока является входом устройства, вход чтения-записи входного запоминающего блока соединен с первым выходом первой группы выходов синхронизатора, адресный вход входного запоминающего блока - с информационным выходом счетчика блока анализа команд, информационный вход которого соединен с информационным входом регистра блока анализа команд и с первым выходом входного запоминающего блока, второй выход которого соединен с информационным входом первого регистра формирователя адреса записи и третьего счетчика формирователя адреса записи и с информационными входами старших разрядов первого и второго счетчиков формирователя адреса записи, третий выход входного запоминающего блока - с информационным входом регистра устройства, счетный вход делителя частоты импульсов - с вторым выходом первой группы выходов синхронизатора, первый и второй выходы дешифратора блока анализа команд соответственно с входом записи-чтения регистра устройства и с входами записи первого регистра формирователя адреса и первого, второго и .711 третьего счетчиков формирователя адр са записи, тактовый вход делителя частоты импульсое формирователя адреса записи - с третьим выходом первой группы выходов синхронизатора, счетный вход счетчика блока анализа команд - с входом записи регистра блока анализа команд и с выходом элемента И блока анализа команд, ,. первьй и второй выходы которого соед нены соответственно с выходом делителя частоты имПуЛьсов блока анализа команд и с третьим выходом дешифратора блока анализа команд, вход которого соединен с выходом регнстра блока анализа команд, информационные выходы второго и третьего счетчиков формирователя адреса записи соединены соответственно с пе выми и вторыми входами первого и второго дешифраторов устройства, выход первого регистра формирователя адреса записи соединен с адресным входом постоянной памяти формировате ля адреса записи, выход которой соединен с. информационньгми входами второго и третьего регистров формиро вателя адреса записи, выходы которых соединены соответственно с информационным входом первого накапливающе сумматора и с информационным входом второго накапливающего сумматора,вхо ды синхронизации которых соединены со счетными входами первого, второг и третьего счетчиков формирователя адреса записи и с первым выходом де лителя частоты импульсов формироват ля адреса записи, вто4)ой выход кото рого соединен с входом разрешения чтения постоянной памяти формироват ля адреса записи второго и третьего регистров формирователя адреса записи, выходы первого и второго нака ливающих сумматоров - соответственно с информационными входами младших разрядов первого и второго счетчиков формирователя адреса записи, выход переполнения третьего счетчика формирователя адреса записи - с первым входом элемента lilDi формирователя адреса записи, выход которого соединен с входом блокировки работы д JЛИтeля частоты импульсов формирователя адреса записи четвертый выход первой группы выходов синхронизатора устройства - со счетным входом счетчика устройства, первьй, второй, третий и четвертьй информационные входы первого и второго коммутаторов соединены соответственно с входом второго дешифратора устройства, с пятым выходом первой группы выходов синхронизатора устройства, с первым выходом регистра устройства и с вторым выходом регистра устройства, группы управляющих входов первого и второго коммутаторов соединены с группой вьпсодов постоянной памяти блока выбора памяти, выходы первого и второго коммутаторов - соответственно с информационными входами блоков памяти первой и второй групп, шестой и седьмой выходы первой группы выходов синхронизатора устройства - соответственно со счетным входом счетчика блока выбора памяти и с управляющим входом третьего коммутатора, первьй и второй информационные входы которого соединены соответственно с выходами блоков памяти первой и второй групп, группа информационных выходов счетчика блока выбора памяти - ,с группой входов дешифратора блока выбора памяти, группа выходов которого соединена через регистр блока выбора памяти с группой адресных входов постоянной памяти блока выбора памяти, выход третьего коммутатора - с информационным входом четвертого коммутатора, группа управляющих входов которого соединена со второй группой выходов синхронизатора устройства, выход четвертого коммутатора является выходом устройства, введены пятьй, шестой, седьмой и восьмой коммутаторы, два формирователя исполнительного адреса, каждьй из которых со- , держит четыре коммзтатора и два регистра, формирователь режимов работы, содержащий два дешифратора, формирователь условий записи, содержащий схему сравнения, дешифратор, элемент ИЛИ и элемент И, причем группа информационных выходов счетчика устройства соединена с первыми группами информационных входов первого, второго и третьего коммутаторов каждого формирователя исподнительного адреса и с группами входов первого и второго дешифраторов формирователя режимов работы, первый вход второй группы информационных входов первого коммутатора каждого формирователя исполнительного адреса - с первым входом первойгруппы информационньгх входов

9

четвертого коммутатора каждого формирователя исполнительного адреса, с информационным выходом первог счетчика формирователя адреса записи, с первым входом первой группы информационных входов схемы сравнения и с первым входом дешифратора формирователя условий записи, второ вход второй группы информационных входов первого коммутатора каждого формирователя исполнительного адреса - с вторым входом первой группы информационных входов четвертого коммутатора каждого формирователя исполнительного адреса, с информационным выходом второгосчетчика форг-шрователя адреса записи, с вторым входом дешифратора формировател условий записи, восьмой выход первой группы выходов синхронизатора устройства - с управляющими входами первого, второго, третьего и четвертого коммутаторов каждого формирователя .исполнительного адреса,вторые группы информационных входов второго и третьего коммутаторов каждого формирователя исполнительного адреса - с группой выходов постоянной памяти блока выбора памяти, с первыми группами информационных входов пятого, шестого, . седьмого и восьмого коммутаторов и с второй группой информационных входов схемы сравнения, выход которой соединен с первым входом элемента ИЛИ формирователя условий записи, второй вход которого соединен с входом дешифратора формирователя условий записи, выход элемента ИЛИ формирователя условий - с первым входом элемента И формирователя условий записи и с вторым входом элемента ИЛИ формирователя адреса записи, второй вход элемента И формирователя условий записи с девятым выходом первой группы выходов синхронизатора устройства, выход элемента И формирователя условий записи - с пятыми информационными входами первого и второго коммутаторов, выходы второго и трет его коммутаторов каждого формирователя исполнительного адреса соединены соответственно с входами записи первого и второго регистров каждого формирова теля ирполнительного адреса, выходы первого и четвертого коммутаторов каждого формирователя исполнительного адреса 504310

соответственно с информационными входами первого и второго регистров каждого формирователя исполнительного адреса, выход первого ре5 гистра каждого формирователя исполнительного адреса - с вторым информационным входом четвертого коммутатора формирователя исполнительного адреса, выход первого дешифратора устройст0 ва - с первыми управляющими входами пятого и седьмого коммутаторов, выходы первого дешифратора формирователя режимов работы соединены с вторыми управляющими входами пятого и седь5 мого коммутаторов, 1 -е выходы ( 1,2,...,П) пятого и седьмого коммутаторов --соответственно с входами синхронизации 1-го блока памяти первой и второй групп, выход второго

20 дешифратора формирователя режимов работы - с управляющими входами шестого и восьмого коммутаторов, выходы которых соединены соответственно с входами чтения, записи блоков памяти

25 первой и второй групп, выходы первого и второго регистров первого формирователя исполнительного адреса соответственно с адресными входами младших и старших разрядов блоков

30 памяти первой группы, выходы первого и второго регистров второго формирователя исполнительного адреса соответственно с адресными входами младших и старших разрядов блоков

35 памяти второй группы.

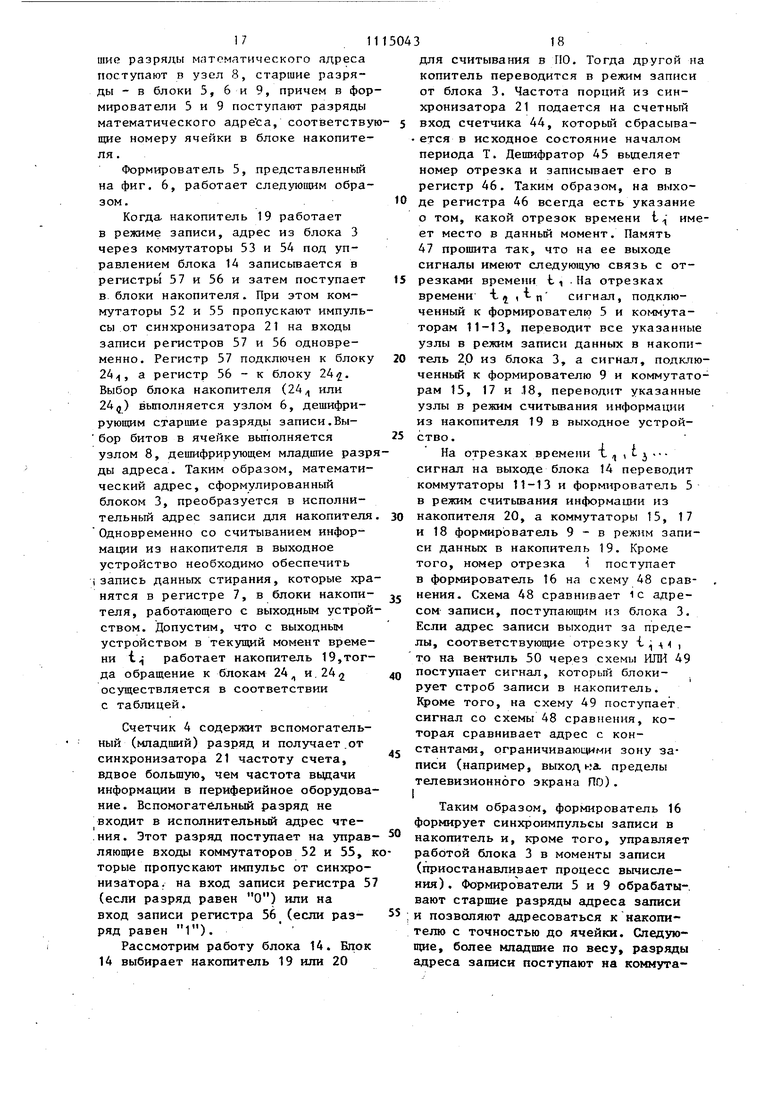

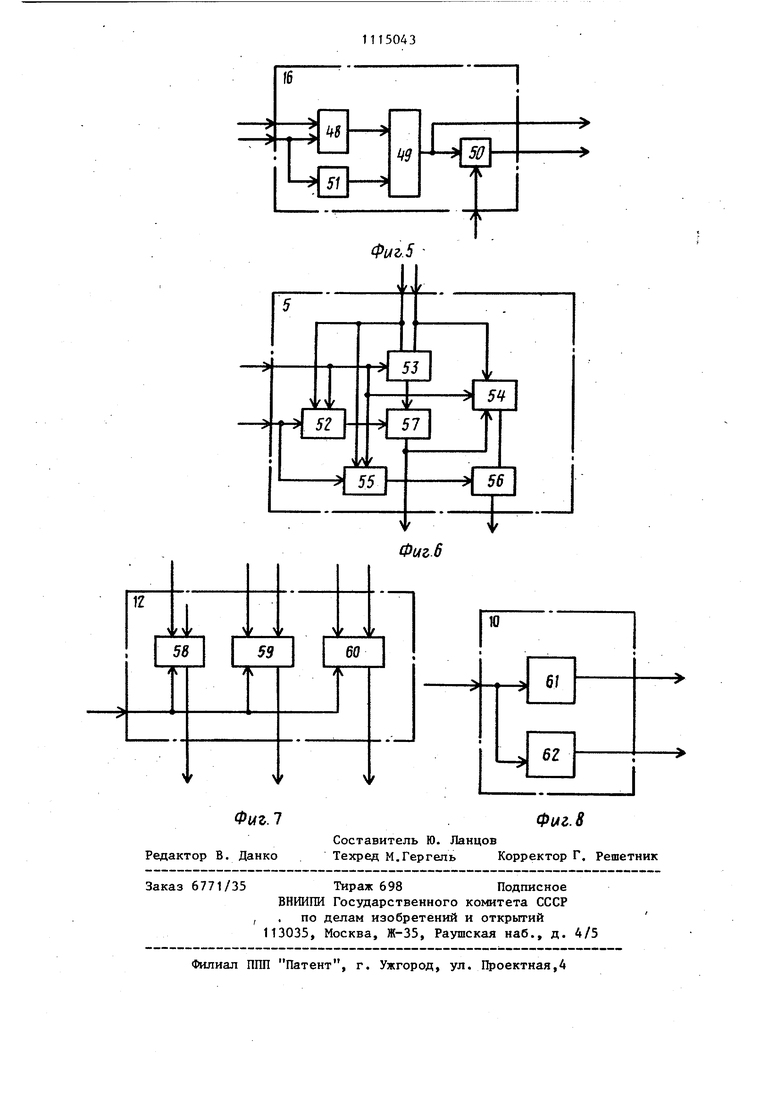

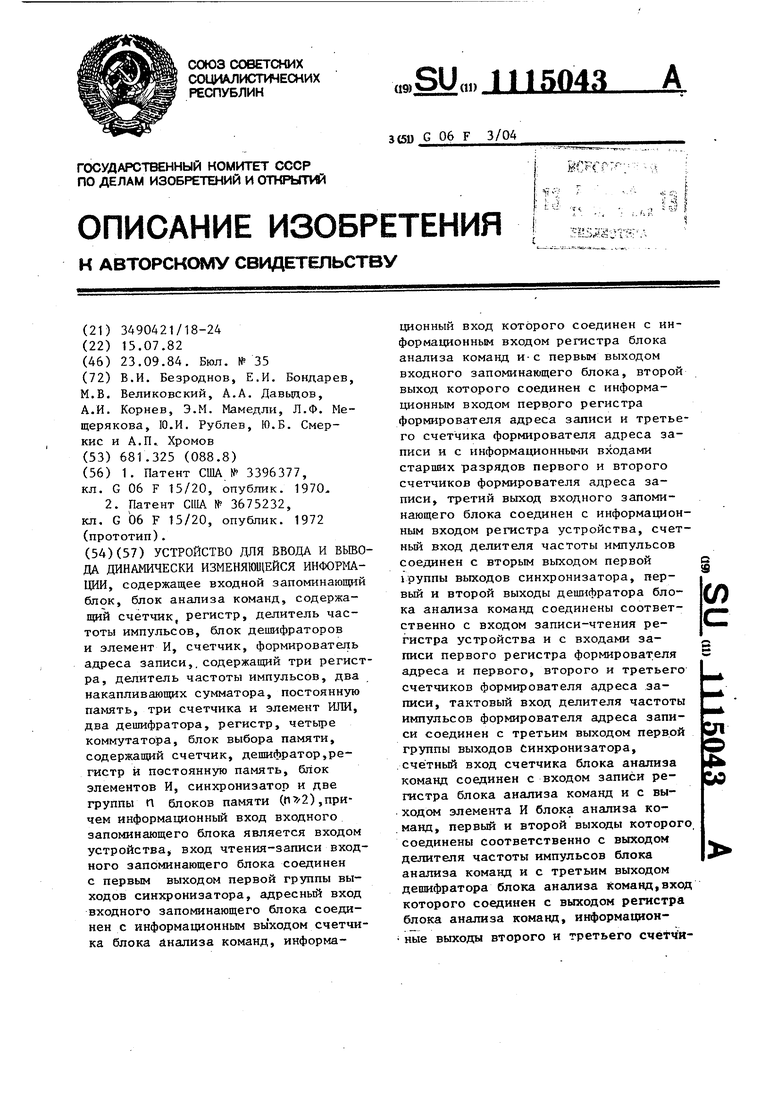

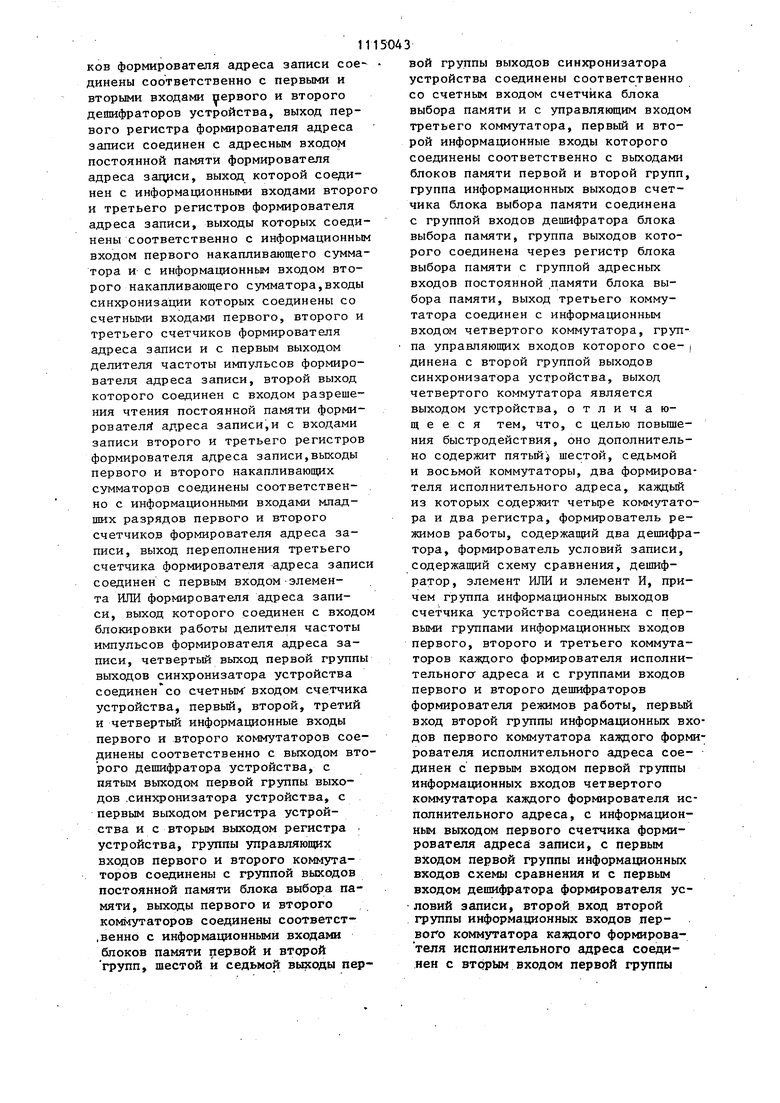

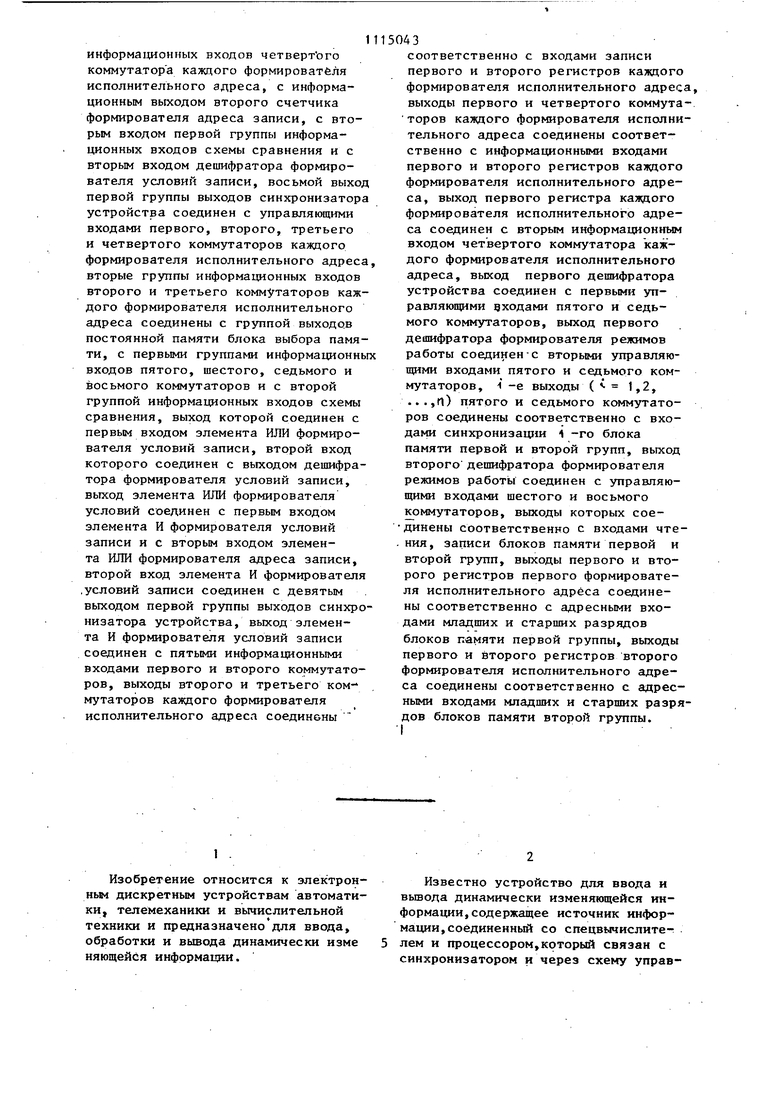

На фиг.1 представлена функциональная схема устройства; на фиг.2 функциональная схема блока анализа

40 команд; на фиг. 3 - функциональная схема формирователя адреса записи; на фиг. 4 - функциональная схема блока выбора памяти; на фиг. 5 функциональная схема формирователя

45 условий записи; на фиг. 6 - функциональная схема формирователя испол-нительного адреса, на фиг. 7 - функциональная схема коммутатора на фиг. 8 - функциональная схе50 ма формирователя режимов работы.

Устройство содержит (фиг.1) входной запоминающий блок 1, блок 2, 5S анализа команд, формирователь 3 адреса записи, счетчик 4, первый формирователь 5 исполнительного адреса, первый дешифратор 6, регистр 7,второй дешифратор 8, второй формирователь 9 исполнительного адреса,формирователь 10 peipHMOB работы, пятый 11, первый 12 и шестой 13 коммутаторы, блок 14 выбора памяти, второй коммутатор 15, формирователь 16 условий записи, седьмой 17 и восьмой 18 коммутаторы, первьй 19 и второй 20 накопители, синхронизатор 21, третий коммутатор 22, первую группу блоков , памяти, вторую группу блоков (,, четветрьй коммутатор 25, вход 26, выход 27.

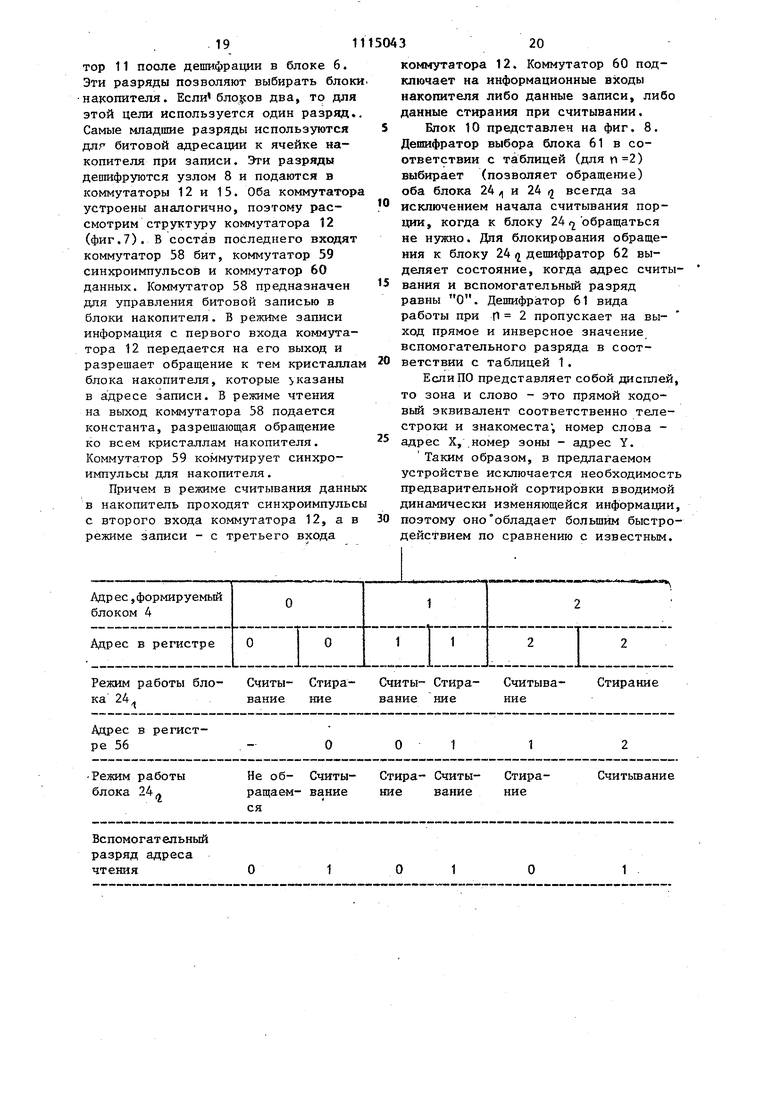

Елок анализа команд (фиг.2) содержит счетчик 28, элемент И 29, делитель 30 частоты импульсов,регистр 31 и блок 32 дешифраторов.

Формирователь адреса записи (фиг.З) содержит регистры 33-35, накапливающие сумматоры 36 и 37, постоянную память 38, счетчики 39-41, элемент ИЛИ 42 и делитель 43 частоты импульсов.

Блок выбора памяти (фиг.4) содержит счетчик 44, дешифратор 45, регистр 46 и постоянную память 47.

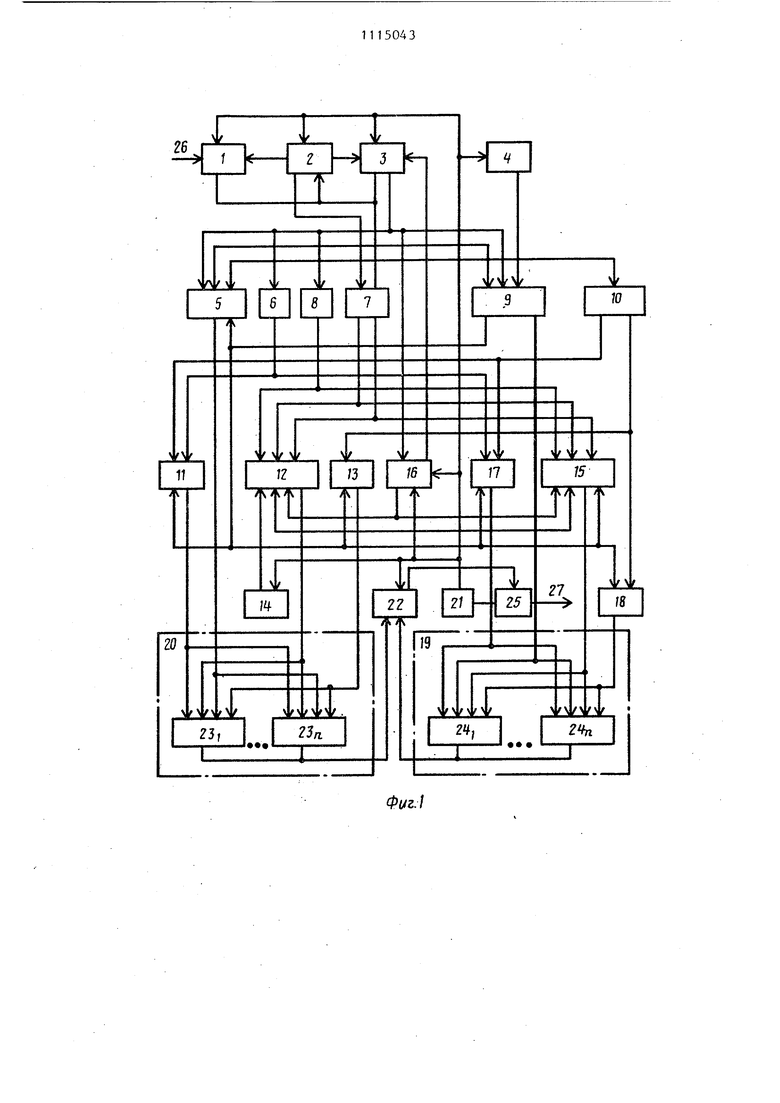

Формирователь условий записи (фиг.5) содержит схему 48 сравнения, элемент ИЛИ 49, элемент И 50 и дешифратор 51.

Формирователь исполнительного адреса (фиг.6) содержит коммутаторы 52-55 и регистры 56 и 57.Коммутаторы (фиг.7) содержат в своем составе коммутаторы 58-60.

Формирователь режимов работы (фиг.8) содержит дешифраторы 61 и 62.

Устро Йство работает следующим образом.

Синхронизатор 21 вырабатывает метки BpeMeHHj которые поступают во все блоки. Внешние вычислительные средства записывают в блок 1 сжатое описание элементов выходной информации (т.е. информация, .которая должна вьщаваться на вход 27 устройства), а также данные для ;стирания (очищения) накопителей 19 -и 20.

Выходная информация разделена на порции, имеющие определенный смысл для периферийного оборудования (по), которое подключено к выходу предлагаемого устройства.Порция, например, может содержать прямой кодовый эквивалент (бит в памяти - точка изображения) одной телестроки. Работу рассмотрим для случая, когда выходная информация выдается в ПО циклически (регенеративно) с некоторым периодом Т (например., Т 40 мс). При этом время Т делится на V равных отрезков t .j.-.tv (V - четное). Отрезок времени t соответствует i -му такту работы ПО. В течение каждого отрезка t в ПО выдается m порций выходной информации, обеспечивающих работу ПО в i-м такте. Всего за период Т на выход поступает m -v различных порций выходной информации. Величины m и V зависят от быстродействия блоков 2 и 3 и требований, предъявляемых периферийным оборудованием (например, V 4$ m 128; V 8, m 64).

Объем каждого накопителя (19 или 20) разделен на зоны. Каждая зона содержит одну порцию выходной информации.

Стирание (очищение) накопителей 19 и 20 заключается в том, что накопители приводятся в требуемое исходное состояние. При этом в ячейке накопителей 19 и 20 записывается некоторая (наперед заданная внешними вычислительными средствами) исходна информация: данные стирания. В частном случае данные стирания - это все нули, или все единицы. В общем случае данные стирания носят более сложный характер и неодинаковы для разных порций выходной информации.

Выходная информация, вьщаваемая в ПО из накопителей 19 и 20, состоит из данных стирания, на которые (как на фон) наложены данные записи

Данные записи записываются в накопители 19 и 20 по адресам, формулируемым формирователем 3, и являются развернутым представлением элементов, сжатое описание которы записано в блок 1 внешними вычислительными средствами. Обработка блокми 2 и 3 сжатого описания элементов выходной информации заключается

в получении развернутого представления этих элементов в соответствии с алгоритмами, учитьшающими специфику ПО. Например, при отображении динамической графической информации элементами выходной информации являются векторы, дуги, символы и т.д. Сжатое описание вектора представляет собой координаты начальной точки, угол наклона и длину. Развернутое представление вектора это последовательность адресов (вь1ход формирователя 3) точек этого вектора с одновременным указанием данных записи - кода цвета точек (черный, белый, серый, красный, синий и т.д.). При этом, естественно, код цвета должен отличаться от соответствующих данных стирания (если данные стирания - все нули, то код цвета - единица). Для получения развернутого представления элементов формирователь 3 содержит ПЗУ (например, ПЗУ синусов, ПЗУ сим волов и т.д.), счётчики, регистры, сумматоры, узлы управления.Можно сказать, что сжатое описание микропрограмма, реализуемая блоками 2 и 3. В течение отрезка времени t ( 1 1,3,5...,У-1) одновременно осуществляются следующие процессы: зоны накопителя 19 вьдаются на выход (через коммутаторы 22 и 25), что обеспечивает -и такт работы ПО накопитель 19 очишается (стирается) в освободивпшеся после считывания ячейки записываются данные стирания, соответствующие порциям выходной информации для отрезка времени t;J42 t накопитель 20 (очищенный нужным образом в момент времени ) записываются через коммутатор 12 по адресам формирователя 5 подготовленные формирователем 3 данные записи (развернутое представление элементов), соответствующие отрезку времени t. . В следующий отрезок времени ( ,4,6,... ,V) накопители 19 и 20 меняются ролями, и одновремен но осуществляются, следующие процессы m зон накопителя 20 вьщаются на выход, обеспечивая (1+1)-й такт работы noj а накопитель 20 записываются дан ные стирания, соответствующие отрезк времени i, в накопитель 19 (очищенный соответствующим образом в течение отрезка времени) поступают данные записи, соответствующие отрез ку времени t t (индекс в выражении t ; вычисляется по модулю j 1 V-1, то 1 -И V, 1 например если +2 v+1). Блоки 2 и 3 в течение каждого отрезка времени (т,е, с периодом T/v 3,14 обеспечивает обработку (или, по крайней мере, просмотр) всего массива сжатых описаний, хранящихся в блоке 1. Однако в накопитель (20, если i 1,3,5,7, или 19, если 1 2,4,6, 8) поступают только данные записи, соответствующие отрезку to/i Это обеспечивается совместной работой блоков 14, 16 и 21. Синхронизатор 21 вырабатывает метки времени, по которым блоки 14 и 16 с помощью счетчиков, схем сравнения и дешифраторов, входящих в их состав, определяют, какой отрезок времени имеет место. Блок 14 определяет 1,3,5 или i 2,4,6 и тем самым выбирает, какой из накопителей 19 и 20 работает с формирователем 3 (на запись), а какой - с выходньм коммутатором 22 (на считывание). При i 2,4,...,V на запись работает накопитель 19,при 1,3,5...,V-1 на запись работает накопитель 20. Соответствующие сигналы посьиаются блоком 14 в формирователи 5 и 9 и в блоки 11-13,15-18.Формирователь 16 учитыва ет особенности данного отрезка времени и окончательно решает,необходимо ли записывать в накопитель данные записи по адресу, полученному формирователем 3 в текущий момент времени. Например, при отображении динамической информации с черезстрочной разверткой при V 4, г 128 отрезки времени t;, и 11 соответственно верхняя и нижняя половина изображения четного полукадра, отрезки i. t - соответственно верхняя и нижняя псшовина изобра;жения нечетного полукадра. Адрес данных записи под управлением блока ,14 подключается через формирователи 5 и 9 к входам накопителей 19 и 20. Счетчик 4, связанный с выходом синхронизатора 21, в темпе, учитывающем особенности ПО, формирует адреса чтения информации, хранимой в накопителях 19 и 20. Адрес чтения (адрес выходной информации) состоит из двух независимых составлякяцих: номера зоны накопителя и номера слова в зоне. Подключение адресов чтения к входам накопителей 19 и 20 осуществляется соответственно че . „ рез формирователи 5 и 9 под управлением блока 14. По сигналам с выхода блока 2 данные стирания и данные записи из

1511

блока 1 записьгааются в соответствующие разряды регистра 7. Данные записи (второй выход, регистра 7) и данные стирания (первый выход регистра 7) под управлением блока 14 подаются через коммутаторы 12 и 15, к входам накопителей 19 и 20.

Формирователь 16, представляющий собой комбинационную схему, вырабатывает условия записи регенерируемой блоком 3 информации с учетом следующих условий, адреса записи (второй вход), поступающего из блока 3, особенностей отрезка времени (например, четный/нечетный полукадр, третий вход 7), поступающих из синхронизатора 21, и номера 1 отрезка 1 1 (первый вход), поступающего из блока 14,

С целью обеспечения одновременности (в отрезок времени) процессов считывания выходной информации из накопителя и записи в этот же накопитель данных стирания, соответствующих отрезку времени i 4-1 и 20 организованы с расслоением ;на П блоков.

Пусть, например, п 2 и накопитель 20 работает с выходным устройством. Тогда первьй блок накопителя (т.е. блок 23i) содержит слова с нечетными номерами для всех (П зо а второй блок накопителя (блок 23) содержит слова с четными номерами всех m зон. Сигналы на входы накопителя 20 подаются таким образом, что в тот момент, когда из блока 23 считывается слово с номером (2i+1), в блок 23 записьшаются данные стирания на место считанного ранее слова с номером , (в этом случае исполнительные адреса в блоках .23 и 23 отличаются на единицу

Затем из блока 23 считывается слово с номером , а в блок 23/ записываются данные стирания на место слова с номером (в этом случае исполнительные адреса в блоках 23 и 232 совпадают. Таким образом, блоки 23 и 23 поочередно меняются ролями. Дальнейшее описание работы устройства проведем для случая И 2.,

Рассмотрим совместную работу блоков 2 и 3 по формированию адресов записи.

Делитель 30 блока 2, получая сигналы с второго выхода первой гру

04316

пы выходов синхронизатора 21, формирует метки времени, по которьгм счетчик 28 команд с периодом T/V обращается в блок 1 за очередной ко5 мандой сжатого описания элементов выходной информации. Данные из блока 1 поступают в регистр 31 и далее на дешифратор 32.

. Дешифратор 32 по коду операг и,

О содержащемуся в команде, формирует управляющие сигналы, которые стробируют запись очередной команды в соответствующие регистры формирователя 3 или в соответствующие разряды

5 регистра 7.

Если очередное слово, считанное из блока 1 в блок 2, является командой построения (например, командой построения вектора), то дешифратор

0 32 формирует строб для записи этого слова в регистр 33 угла или в один из счетчиков 39-41. Если же слово, считанное из блока 1, является данными для стирания или для запи5 си, то оно записывается в регистр 7. Рассмотрим процесс формирования адресов записи блоком 3. После записи сжатого описания изображения делитель 43 дает команду на запись

0 синуса и коеинуса угла, код которого хранится в регистре 33, в регистры 34 и 35. Затем начинается процесс формирования адресов.. Накапливаюп1ие сумматоры 36 и 37,сум5 мируя значение синусов и косинусов, формируют дробную часть адреса. Каждый переход через единицу дробной части адреса на выходе сумматора 36 и 37 да.ет команду на единич0 ное приращение соответственно для счетчиков 39 и 40. Каждое суммирование синусов и косинусов дает команду на вьиитание для счетчика 41 длины. Процесс формирования адре5 сов точек, описьшающих очередной элемент изображения, продолжается до тех пор, пока не спищется (станет равным нулю) код длины в.счетчике 41. Математический адрес

50 записи, сформированный блоком 3, поступает в блоки 6 и 8 и идентичные формирователи 5 и 9 исполнительного адреса.

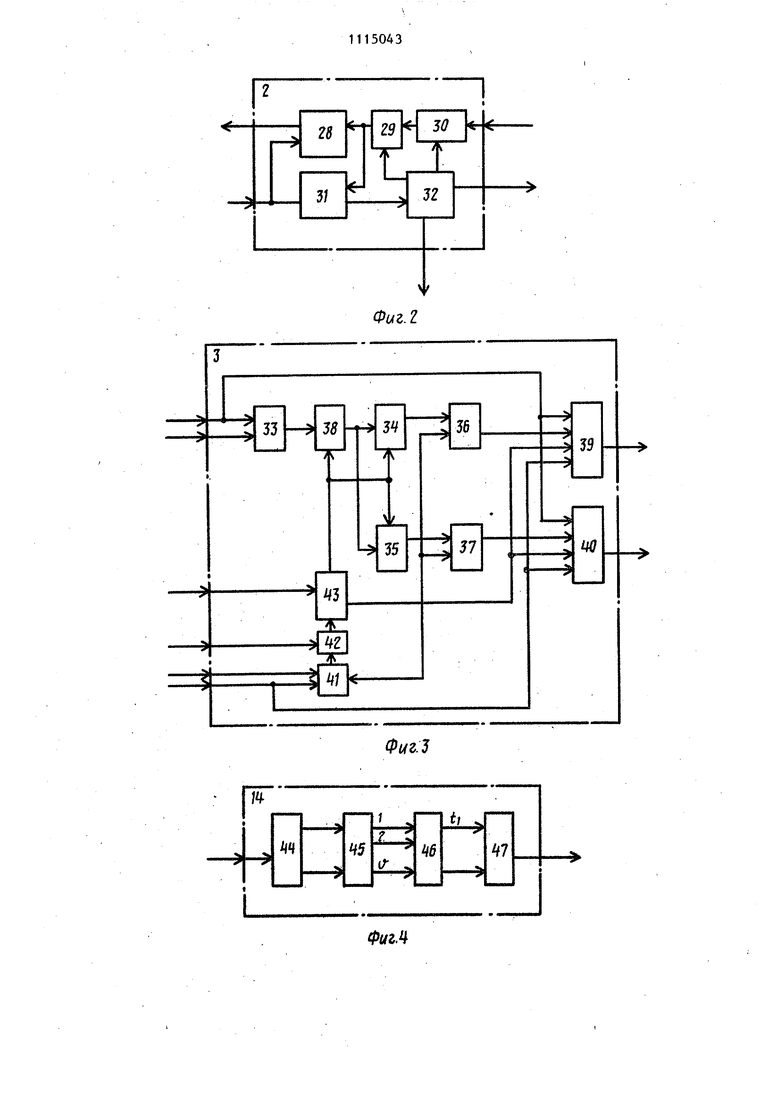

Блоки 6 и 8 и формирователи 5 и 5 9 осуществляют привязку математических адресов записи выходной информации, формулируемых блоком 3, к адресам накопителей 19 и 20. Младшие разряды математического адреса поступают в узел 8, старшие разряды - в блоки 5, 6 и 9, причем в фор мирователи 5 и 9 поступают разряды математического адреса, соответств щие номеру ячейки в блоке накопите ля . Формирователь 5, представленный на фиг. 6, работает следующим обра зом. Когда накопитель 19 работает в режиме записи, адрес из блока 3 через коммутаторы 53 и 54 под управлением блока 14 записьгеается в регистры 57 и 56 и затем поступает в блоки накопителя. При этом коммутаторы 52 и 55 пропускают импуль сы от синхронизатора 21 на входы записи регистров 57 и 56 одновременно. Регистр 57 подключен к блок 24, а регистр 56 - к блоку 242Выбор блока накопителя (24 или 245) выполняется узлом 6, дешифрирующим старшие разряды записи.Выбор битов в ячейке вьшолняется узлом 8, дешифрирующем младшие разр ды адреса. Таким образом, математический адрес, сформулированный блоком 3, преобразуется в исполнительный адрес записи для накопителя Одновременно со считыванием информации из накопителя в выходное устройство необходимо обеспечить (запись данных стирания, которые хр нятся в регистре 7, в блоки накопи теля, работающего с выходным устро ством. Допустим, что с выходным устройством в текущий момент време ни t работает накопитель 19,тог да обращение к блокам 24 и.242 осуществляется в соответствии с таблицей. Счетчик 4 содержит вспомогательный (младший) разряд и получает.от синхронизатора 21 частоту счета, вдвое большую, чем частота выдачи информации в периферийное оборудова ние. Вспомогательный разряд не входит в исполнительный адрес чте.НИН. Этот разряд поступает на управ ляющие входы коммутаторов 52 и 55, торые пропускают импульс от синхронизатора, на вход записи регистра 5 (если разряд равен О) или на вход записи регистра 56(если разряд равен 1). Рассмотрим работу блока 14. Блок 14 выбирает накопитель 19 или 20 18 для считывания в ПО. Тогда другой на копитель переводится в режим записи от блока 3. Частота порций из синхронизатора 21 подается на счетный вход счетчика 44, которьй сбрасывается в исходное состояние началом периода Т. Дешифратор 45 вьоделяет номер отрезка и записывает его в регистр 46. Таким образом, на выходе регистра 46 всегда есть указание о том, какой отрезок времени t имеет место в данный момент. Память 47 прошита так, что на ее выходе сигналы имеют следующую связь с отрезками времени t ) .На отрезках времени t i -n сигнал, подключенный к формирователю 5 и коммутаторам 11-13, переводит все указанные узлы в режим записи данных в накопитель 2,0 из блока 3, а сигнал, подключенный к формирователю 9 и коммутаторам 15, 17 и .18, переводит указанные узлы в режим считьгоания информации из накопителя 19 в выходное устройство. На отрезках времени Т /, , t сигнал на выходе блока 14 переводит коммутаторы 11-13 и формирователь 5 в режим считывания информации из накопителя 20, а коммутаторы 15, 17 и 18 формирователь 9 - в режим записи данных в накопитель 19. Кроме того, номер отрезка i поступает в формирователь 16 на схему 48 сравнения. Схема 48 сравнивает ic адреСОМ записи, поступающим из блока 3. Если адрес записи выходит за пределы, соответствующие отрезку i . /( , то на вентиль 50 через схемы ИЛН 49 поступает сигнал, которьй блокирует строб записи в накопитель. Кроме того, на схему 49 поступает сигнал со схемы 48 сравнения, которая сравнивает адрес с константами, ограничивающими зону записи (например, выход на. пределы телевизионного экрана ПО). Таким образом, формирователь 16 формирует синхроимпульсы записи в накопитель и, кроме того, управляет работой блока 3 в моменты записи (приостанавливает процесс вычисления) . Формирователи 5 и 9 обрабаты-, вают старшие разряды адреса записи и позволяют адресоваться к накопителю с точностью до ячейки. Следующие, более младшие по весу, р 1зряды адреса записи поступают на коммутатор 11 после дешифрации в блоке 6. Эти разряды позволяют выбирать бло накопителя. Еслибло сов два, то для этой цели используется один разряд Самые младшие разряды используются длг битовой адресации к ячейке накопителя при записи. Эти разряды дешифруются узлом 8 и подаются в коммутаторы 12 и 15. Оба коммутатор устроены аналогично, позтому рассмотрим структуру коммутатора 12 (фиг.7). В состав последнего входя коммутатор 58 бит, коммутатор 59 синхроимпульсов и коммутатор 60 данных. Коммутатор 58 предназначен для управления битовой записью в блоки накопителя. В режиме записи информация с первого входа коммута тора 12 передается на его выход и разрешает обращение к тем кристалл блока накопителя, которые указаны в адресе записи. В режиме чтения на выход коммутатора 58 подается константа, разрешающая обращение ко всем кристаллам накопителя. Коммутатор 59 коммутирует синхроимпульсы для накопителя. Причем в режиме считывания данн в накопитель проходят синхроимпуль с второго входа коммутатора 12, а режиме записи - с третьего входа

Считы- СтираРежим работы блока 24., вание ние

блока 24,

ращаем- ванне ся

Вспомогательный разряд адреса чтения

Считыва- Стирание

Считы- Стиравакие ние ние 320 коммутатора 12. Коммутатор 60 подключает на информационные входы накопителя либо данные записи, либо данные стирания при считывании. Блок 10 представлен на фиг. 8. Дешифратор выбора блока 61 в соответствии с таблицей (для ) выбирает (позволяет обращение) оба блока 24 ,| и 24 ij всегда за исключением начала считывания порции, когда к блоку 24/ обращаться не нужно. Для блокирования обращения к блоку 24 ( дешифратор 62 выделяет состояние, когда адрес считывания и вспомогательный разряд равны О. Дешифратор 61 вида работы при П 2 пропускает на выход прямое и инверсное значение вспомогательного разряда в соответствии с таблицей 1. Если ПО представляет собой дисплей, то зона и слово - это прямой кодовый эквивалент соответственно телестроки и знакоместа; номер слова адрес X, .номер зоны - адрес Y. Таким образом, в предлагаемом устройстве исключается необходимость предварительной сортировки вводимой динамически изменяющейся информации, поэтому оно обладает большим быстродействием по сравнению с известным.

рг

Фиг.г

Ф14г:

Фиг, 5

Фиг.б

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3396377, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Кинематографический аппарат | 1923 |

|

SU1970A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3675232, кл, G 06 F 15/20, опубпик | |||

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

Авторы

Даты

1984-09-23—Публикация

1982-07-15—Подача