Изобретение относится к цифровой ычислительной технике, конкретнее к устройствам для обработки цифровых анных, и может быть использовано ля решения дифференциальных уравнений в частных производных.

Цель изобретения - повышение производительности устройства.

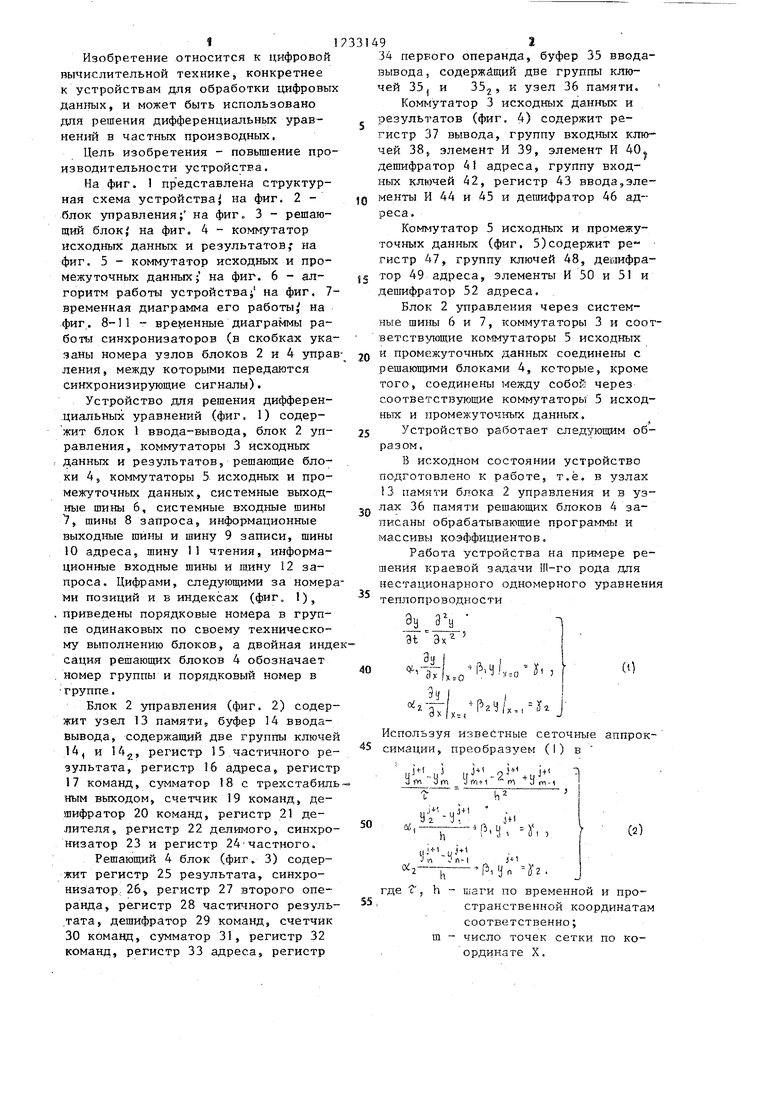

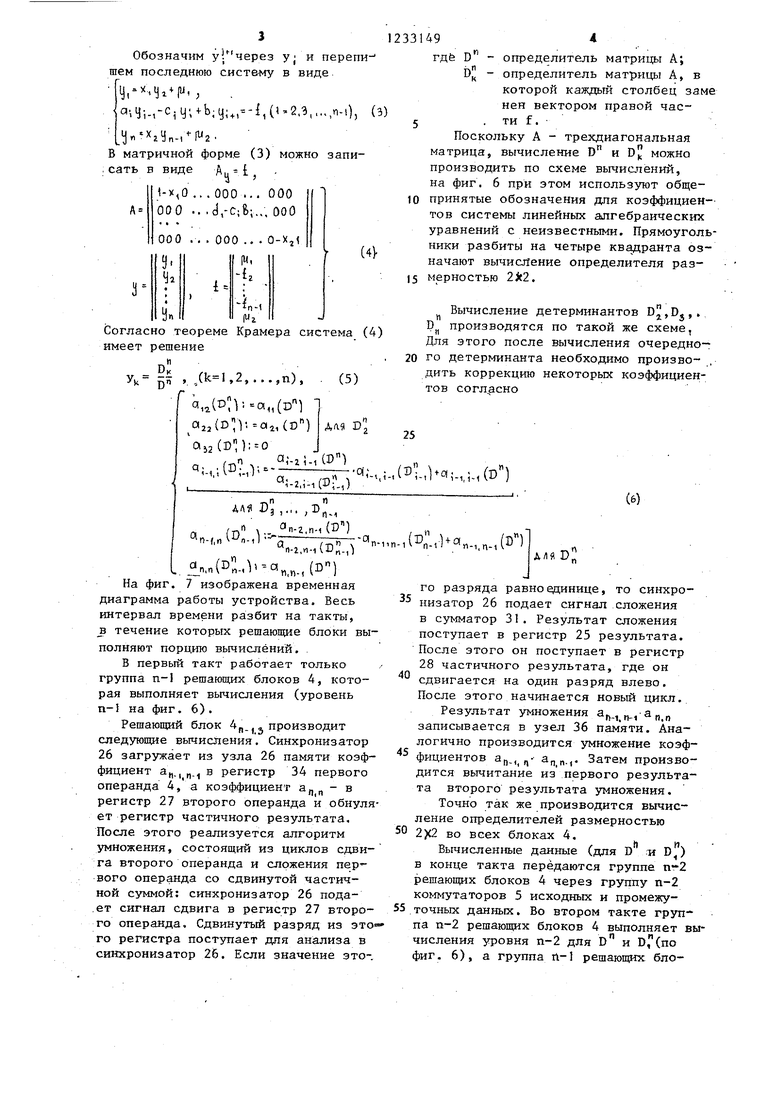

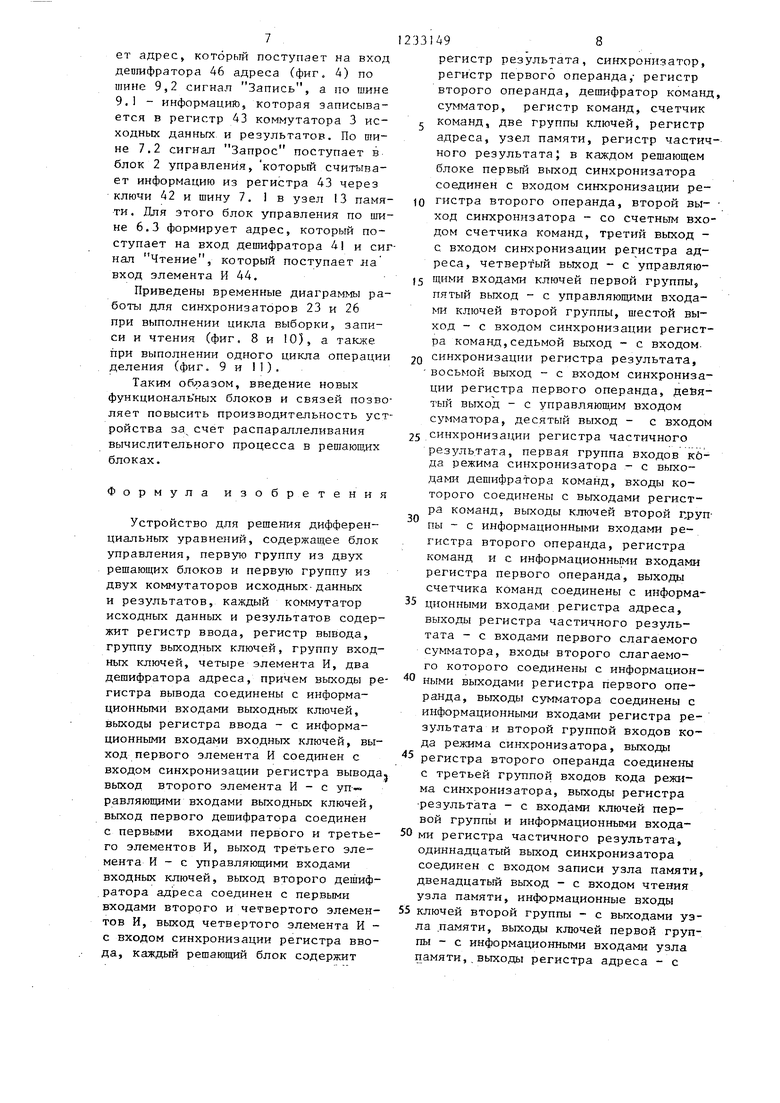

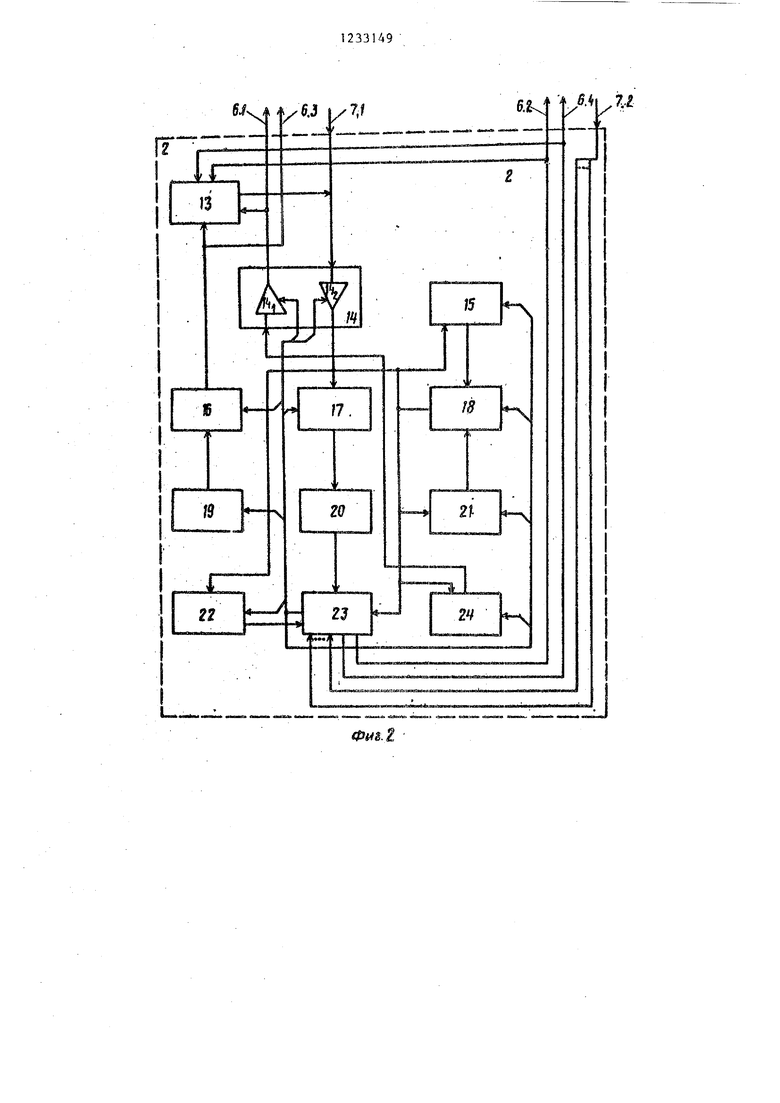

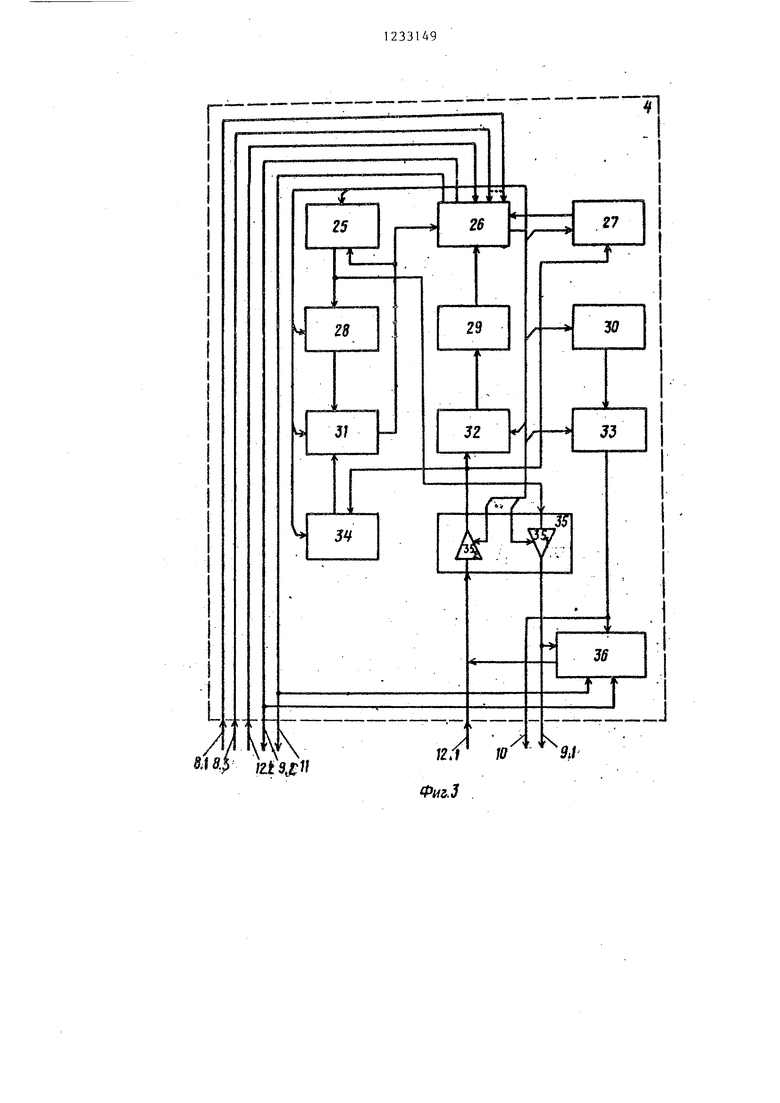

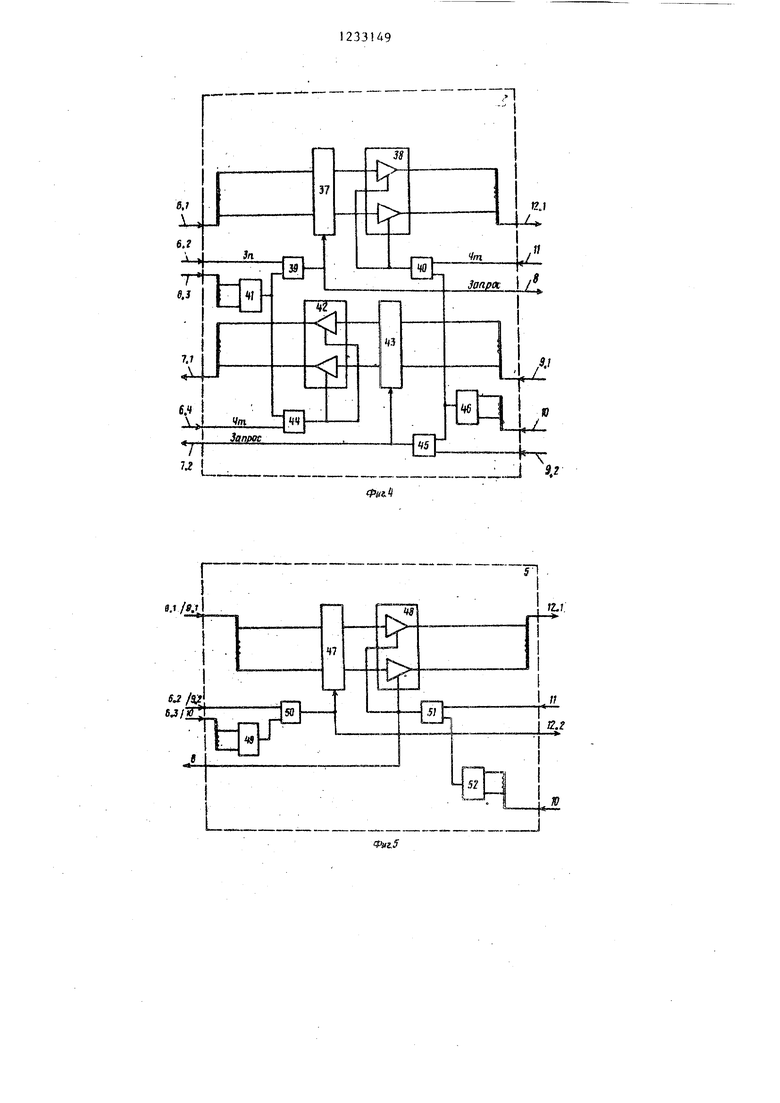

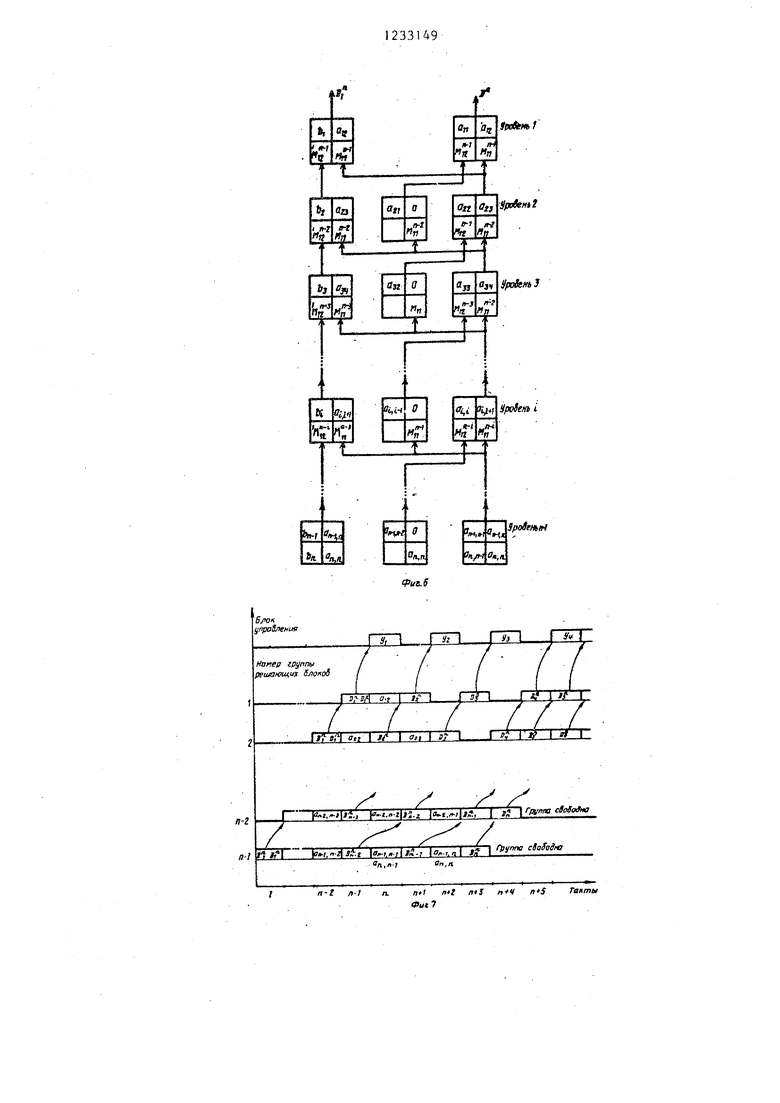

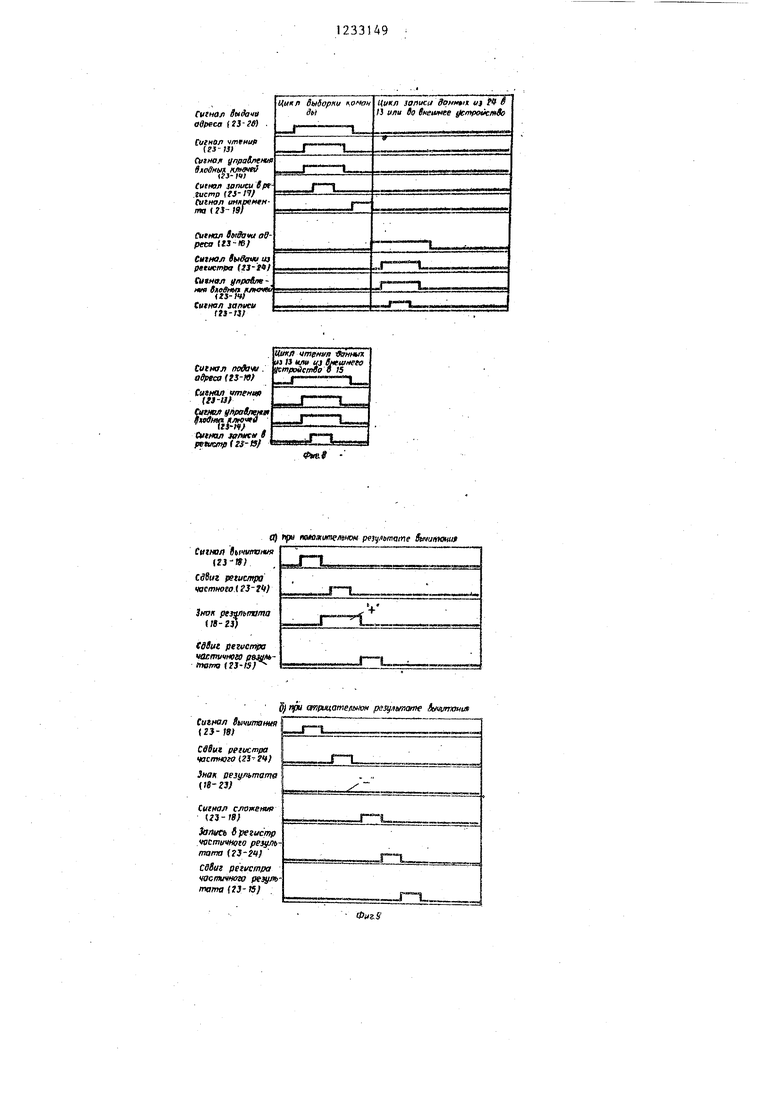

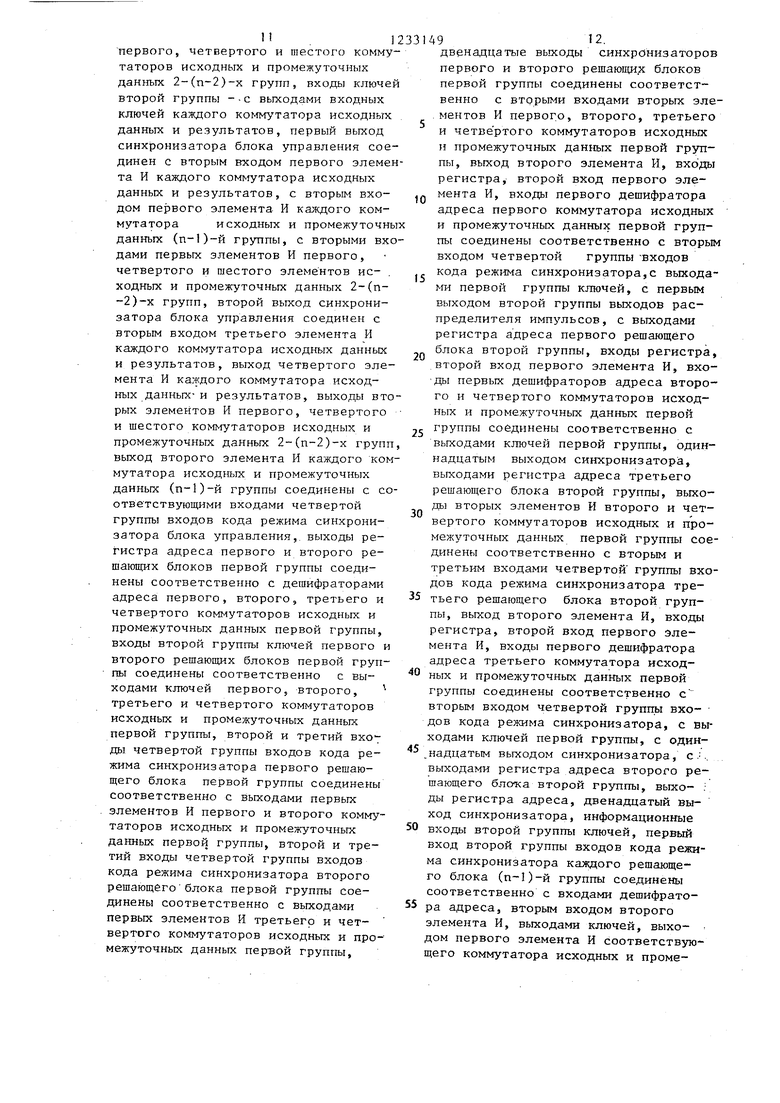

На фиг. 1 пр едставлена структурная схема устройстваi на фиг. 2 - блок управления; на фиг. 3 - решающий блок, на фиг. 4 - коммутатор исходных данных и результатов на фиг. 5 - коммутатор исходных и промежуточных данных; на фиг. 6 - алгоритм работы устройства; на фиг. 7- временная диаграмма его работы на фиг. 8-11 временные диаграммы работы синхронизаторов (в скобках указаны номера узлов блоков 2 и 4 управ- ления, между которыми передаются синхронизирующие сигналы).

Устройство для решения дифферен- .циальных уравнений (фиг. 1) содержит блок I ввода-вывода, блок 2 управления , коммутаторы 3 исходных данных и результатов, решающие блоки 45 коммутаторы 5 исходных и промежуточных данных, системные вьщод- ные шины 6, системные входные шины 7, шины 8 запроса, информационные выходташ шины и шину 9 записи, шины 10 адреса, шину 11 чтения, информационные входные шины и тину 12 запроса. Цифрами, сле цующими за номера- йи позиций и в индексах (фиг,, 1)

приведены порядковые номера в группе одинаковых по своему техническому выполнению блоков, а двойная индексация решающих блоков 4 обозначает

номер группы и порядковый номер в группе.

Блок 2 управления (фиг. 2) содержит узел 13 памяти, буфер 14 ввода- вывода, содержащий две группы ключей 14, и 14, регистр 15 частичного результата, регистр 16 адреса, регистр 17 команд, сумматор 18 с трехстабиль- ным выходом, счетчик 19 команд, дешифратор 20 команд, регистр 21 делителя, регистр 22 делимого, синхронизатор 23 и регистр 24 частного,.

Решающий 4 блок (фиг 3) содержит регистр 25 результата, синхронизатор. 26,, регистр 27 второго операнда, регистр 28 частичного результата, дешифратор 29 команд, счетчик 30 команд, сумматор 31, регистр 32 команд, регистр 33 адреса, регистр

0

34 первого операнда, буфер 35 ввода- вывода, содержащий две группы ключей 35j и 352, узел 36 памяти.

Коммутатор 3 исходных данных и результатов (фиг, 4) содержит регистр 37 вывода, группу входных ключей 38,, элемент И 39, элемент И 40, дешифратор 41 адреса, группу входных ключей 42, регистр 43 ввода,элементы И 44 и 45 и дешифратор 46 адреса.

Коммутатор 5 исходных и промежуточных данных (фиг, 5)содержит ре гистр 47, группу ключей 48, дешифра- 5 тор 49 адреса, элементы И 50 и 51 и дешифратор 52 адреса. .

Блок 2 управления через системные шины 6 и 7, коммутаторы 3 и соответствующие коммутаторы 5 исходных и промежуточных данных соединены с решающими блоками 4, которые, кроме того, соединены между собой через соответствующие коммутаторы- 5 исходных и промежуточных данных.

Устройство работает следующим образом.

В исходном состоянии устройство подготовлено к работе, т.е. в узлах 13 памяти блока 2 управления и в уз- „ лах 36 памяти решающих блоков 4 за- писань обрабатываюшие программы и массивы коэффициентов.

Работа устройства на примере решения краевой Зс1дачи Ifl-го рода для нестационарного одномерного уравнения теплопроводности

о л i li j 9t Зх

За 17

Зя

I 1 II II ,

I

5

5

XrO

3,

(О

(Х

Р2Ч/,,,21г

Используя известные сеточнь е аппрок- 45 симации, преобразуем (1) в

о т

- J 44J hvi -я т 3 m -1

yfIJ ° ,

h J+1

(2)

i - - -qJ

J n

,

где с

л-1

2.

h - шаги по временной и пространственной координатам соответственно;

m - число точек сетки по координате X.

Обозначим уi через у; и перепи- шем последнюю систему в виде

У,-Х,Чг(и, ,

а ,Ч-,м-С,Ч; Ь;у;„ Ч,(1-2,3,,..,n.i, (Э)

,,. в матричной форме (3) можно запиСогласно теореме Крамера система (4) имеет решение

D:

D

. 2, . .. ,ti),

a,,(,,( 1 a2.(D:v.-ai,(c)

(5)

AW Dj

Q52(D)

ч;К.О--

n n

AAfl Dj ,.,. ,Э„,,

,п(о1Л -0.„,„ ,(В) .

Ha фиг. 7 изображена временная диаграмма работы устройства. Весь интервал времени разбит на такты, ъ течение которых решающие блоки выполняют порцию вычислений.

В первый такт работает только группа п-1 решающих блоков 4, которая выполняет вычисления (уровень п-1 на фиг. 6).

Решающий блок производит следующие вычисления. Синхронизатор

(6)

Л/1Й D,

го разряда равно единице, то синхро- низатор 26 подает сигнал сложения в сумматор 31. Результат сложения поступает в регистр 25 результата. После этого он поступает в регистр 28 частичного результата, где он сдвигается на один разряд влево. После этого начинается новый цикл.

Результат умножения а„., , записывается в узел 36 памяти. Аналогично производится умножение коэф40

26 загружает из узла 26 памяти коэф- фициентов Эд.,- п.п-с Затем произвофициент а., „. в регистр 34 первого операнда 4, а коэффициент а„ - в регистр 27 второго операнда и обнуляет регистр частичного результата, После этого реализуется алгоритм умножения, состоящий из циклов сдвига второго операнда и сложения первого операнда со сдвинутой частичной суммой: синхронизатор 26 пода- ,ет сигнал сдвига в регистр 27 второго операнда. Сдвинутый разряд из го регистра поступает для анализа в синхронизатор 26. Если значение это50

дится вычитание из первого результата второго результата умножения.

Точно так же производится вычисление определителей размерностью 2X2 во всех блоках 4.

Вычисленные данные (для D :и D) в конце такта передаются группе п-2 решающих блоков 4 через группу п-2 коммутаторов 5 исходных и промежу- 55 точных данных. Во втором такте груп- па п-2 решающих блоков 4 выполняет вы числения уровня п-2 для D и D(no фиг. 6), а группа rt-l решающих бло

(Э)

4).

где D - определитель матрицы А; - определитель матрицы А, в

которой каждый столбец заме иен вектором правой части f.

Поскольку А - трехдиагональная матрица, вычисление D и D, можно производить по схеме вычислений, на фиг, 6 при этом используют общепринятые обозначения для коэффициен-- тов системы линейных алгебраических уравнений с неизвестными. Прямоугольники разбиты на четыре квадранта означают вычисление определителя раз- 15 мерностью ,

10

D..

Вычисление детерминантов Dj,Dj,

. производятся по такой же схеме, Для этого после вычисления очередно-: 20 го детерминанта необходимо произво- , дить коррекцию некоторых коэффициентов согласно

25

(6)

Л/1Й D,

го разряда равно единице, то синхро- низатор 26 подает сигнал сложения в сумматор 31. Результат сложения поступает в регистр 25 результата. После этого он поступает в регистр 28 частичного результата, где он сдвигается на один разряд влево. После этого начинается новый цикл.

Результат умножения а„., , записывается в узел 36 памяти. Аналогично производится умножение коэф40

50

дится вычитание из первого результата второго результата умножения.

Точно так же производится вычисление определителей размерностью 2X2 во всех блоках 4.

Вычисленные данные (для D :и D) в конце такта передаются группе п-2 решающих блоков 4 через группу п-2 коммутаторов 5 исходных и промежу- 55 точных данных. Во втором такте груп- па п-2 решающих блоков 4 выполняет вчисления уровня п-2 для D и D(no фиг. 6), а группа rt-l решающих блоков 4 вычисления своего уровня для т.д. В тактах п-2, п и п+2 группы SjAj,..,п-1 решающих блоков 4 1; оизводят коррекцию коэффициентов в соответствии с формуламиТб). Анало.гичную коррекцию коэффициентов группа 1 решающих блоков 4 производит в такт п, а группа 2 решающих блоков 4 - в такты п- и п+1.

По мере получения значений детерминантов группа 1 решающих блоков 4 через группу 1 коммутатора 3 исходных данных и результатов передает их в блок 2 управления., который вычисляет значения искомой функции в узлах сетки.

Деление в блоке 2 управления производится путем определенного числа циклов вычитания делителя из делимо- го и сдвига последнего. Перед началом деления делимое из узла 13 памяти поступает в регистр 15 частичного результата.

Цикл проводят следующим образом.

По сигналу синхронизатора 23 в суматоре 18 из частичного результата вычитается делимое. Результат вычитания заносится в регистр 15 частич . ного результата, а знак результата- (1 соответствует знаку +, О - знаку -) из сумматора 18 поступает в синхронизатор 23 и по сигналу из синхронизатора 23 заносится сдвигом в регистр 24 частного,.

Если знак результата вычитания оказался положительным, производится сдвиг информации в регистр,15 частичного результата на один разряд влево и цикл заканчивается. Если же знак результата вычисления ока . зался отрицательным, то на сумматоре 18 производится сложение частичного результата и делителя (восстановление), после чего производится сдвиг содержимого регистра i 5 частичного результата на один разряд влево.

Начиная с такта п+5 с выхода группы решающих блоков 4, значения детерминантов поступают в блок 2 управления.

Группа п-1 решающих блоков 4 освобождается после такта п+З, а каждая последующая группа п-2, п-З и т.д, освобождается на такт .позже. Поэтому с п+4 устройство Может начать вычисления следующей краевой задачи.

0

5

0

5

0

5

0

5

Детально рассматривают передачу глнформации из блока 2 управления в регааюш е блоки 4, решающего блока 4 i-й грлгппы в решающий блок 4 ()-й группы и первой группы решающих блоков 4 в блок 2 управления.

Блок 2 управления вырабатывает (фиг. 1 ,, 4 и 5) по шине 6.3 адрес кoм тaтopa 3 исходных данньгх и результатов или адрес коммутатора 5 исходных и промежуточных данных, в, зависимости от номера решающего блока 4, по шине 6.2 сигнал Запись, по которому слово из узла 13 памяти блока 2 по информационной шине 6«1 записывается в регистр 34 вывода или регист 47 соответствующего коммутатора 3 1Ш1И 5. При этом с выхода соответствующего элемента И 39 или 50 сигнал Запрос по шине 8 или 2.2 поступает в распределитель 26 импульсов решающего блока 4 (фиг.З).

По это:угу сигналу решающий блок 4 обращается к комм татору 3 или 5 как к внешнему устройству и считывает информацию с регистра 37 или 47 вывода через ключи 38 или 4В по шине 12,1 в узел 36 памяти решающего блока- 4. Далее аналогично передаются остальные данные.

Передача информации, например, из решающего блока 4,, в решающий блок 4,.; осуществляется через Коммутатор 5 исход п 1х и промежуточных данных. Для этого решающий блок 4, выставляет на шинах 10 адрес комму- , татора , а по шине 9,2 сигнал Запись по которому информация через шины 9 Л записывается в регистр 47 (фиг. 5) При записи информации в регистр 47 с выхода элемента И 50 формируется сигнал Запрос, который по шине 12.2 поступает в решающий блок 4, . Решающий блок 4(2 перехо- дит к чтению информации и выдает по шинам 0 адрес, который поступает на вход де1Шг--фратора 52 адреса, а по шипе II - сигна-п Чтение. Информация через ключ и 48 из регистра 47 по шинам 2 . 1 считывается в узел 36 памяти решающего блока з по шине 8 ответный сигнал сообщает решающему блоку 42; о TOMj ЧТО МОЖНО перзда- вать следующее слово.

Результат вычислений из первой группы решающих блоков 4 передается в блок 2 управления. Для этого решающий блок 4 по шине 10 вьтрабатывает адрес, который поступает на вход депшфратора 46 адреса (фиг. 4) по шине 9,2 сигнал Запись, а по шине 9.1 - информацию, которая записывается в регистр 43 коммутатора 3 исходных данных и результатов. По шине 7.2 сигнал Запрос поступает в блок 2 управления, который считывает информацию из регистра 43 через ключи 42 и шину 7. 1 в узел 13 памяти. Для этого блок управления по шине 6.3 формирует адрес, который поступает на вход дешифратора 41 и синал Чтение, который поступает ла вход элемента И 44.

Приведены временные диаграммы работы для синхронизаторов 23 и 26 при выполнении цикла выборки, записи и чтения (фиг. 8 и 10), а также

при выполнении одного цикла операции деления (фиг. 9 и И).

Таким образом, введение новых функциональ ных блоков и связей позволяет повысить производительность устройства за, счет распараллеливания вычислительного процесса в решающих блоках.

Формула изобретения

Устройство для решения дифферен- циальньгх уравнений, содержащее блок управления, первую группу из двух решающих блоков и первую группу из двух коммутаторов исходных-данных и результатов, каждый коммутатор исходных данных и результатов содержит регистр ввода, регистр вывода, группу выходных ключей, группу входных ключей, четыре элемента И, два дешифратора адреса, причем выходы регистра вывода соединены с информационными входами выходных ключей, выходы регистра ввода - с информационными входами входных ключей, выход первого элемента И соединен с входом синхронизации регистра вывода выход второго элемента И - с уп-. равляющими входами выходных ключей, выход первого дешифратора соединен с первыми входами первого и третьего элементов И, выход третьего элемента И - с управляющими входами входных ключей, выход второго дешифратора адреса соединен с первыми входами второго и четвертого элементов И, выход четвертого элемента И - с входом синхронизации регистра ввода, каждый решающий блок содержит

331498

регистр результата, синхронизатор, регистр первого операнда,- регистр второго операнда, депшфратор команд, сумматор, регистр команд, счетчик

г команд, две группы ключей, регистр адреса, узел памяти, регистр частичного результата; в каждом решающем блоке первый выход синхронизатора соединен с входом синхронизации реto гистра второго операнда, второй вы- ход синхронизатора - со счетным входом счетчика команд, третий выход - с входом синхронизации регистра адреса, четвертый выход - с управляю15 щими входами ключей первой группы, пятый выход - с управляющими входами ключей второй группьг, шестой выход - с входом синхронизации регистра команд,седьмой выход - с входом.

2Q синхронизации регистра результата, восьмой выход - с входом синхронизации регистра первого операнда, дейя- тый выход - с управляющим входом сумматора, десятый выход - с входом

25 синхронизации регистра частичного

результата, первая группа входов кб- да режима синхронизатора - с выходами дешифратора команд, входы которого соединены с выходами регистра команд, выходы ключей второй группы - с информационными входами регистра второго операнда, регистра команд и с информационньтми входами регистра первого операнда, выходы счетчика команд соединены с информа35 ционными входами регистра адреса, выходы регистра частичного результата - с входами первого слагаемого сумматора, входы второго слагаемого которого соединены с информационными выходами регистра первого операнда, выходы сумматора соединены с информационными входами регистра результата и второй группой входов кода режима CHiixpoHHsaTopa, выходы

5 регистра второго операнда соединены с третьей группой входов кода режима синхронизатора, выходы регистра -результата - с входами ключей первой группы и информационными входа30

40

50

ми регистра частичного результата.

одиннадцатый выход синхронизатора соединен с входом записи узла памяти, двенадцатый выход - с входом чтения узла памяти, информационные входы 55 ключей второй группы - с выходами узла .памяти, выходы ключей первой группы - с информационными входами узла памяти,,выходы регистра адреса - с

дресными входами узла памяти, выходы ыходных ключей группы и входы реистра ввода каждого коммутатора ис- одных данных и результатов первой руппы соединены i соответственно с нформационными входами ключей втоой группы и выходами ключей первой группы соответствующего решающего блока первой группы, входы второго ешифратора адреса , второй вход четвертого элемента И, второй вход вто рого элемента И и выход первого элемента И каждого коммутатора исходных данных и результатов первой группы соединены соответственно -с выходами регистра адреса, одиннадцатым и двенадцатым выходами синхронизатора и первым входом четвертой группы входов кода режима синхронизатора соответствующего решающего блока первой группы, отличающееся тем, что, с целью повьппения производительности, в него введены (п-2) группы из трех решающих блоков и (п-) группа коммутаторов исходных и промежуточных данных, из которых первая группа содержит четыре коммутатора исходных и промежуточных данных, (п-1)-я группа коммутаторов содержит три коммутатора исходных и промежуточньрс данных, а остальные группы коммутаторов - по восемь коммутаторов исходных и промежуточных данных 5 каждый коммутатор исходных и промежуточных; данных содерж; т регистр, группу ключей, два элемен- та И, два дешифратора адреса,, причем выходы регистра соединены с информационными входами ключей, выход первого дешифратора адреса соединен .с первым входом первого элемента 1Л, 1зыход которого соединен с си}пк:рони- зирующим входом регистра, выход второго дешифратора адреса соединен с первым входом второго элемента И, выход которого соединен с управляющими входами ключей, блок управления содержит узел памяти, две группы зшючей, регистр адреса, регистр команд, регистр частичного результата; счетчик команд, дешифратор команд, сумматорз регистр делителя, регистр делимого, синхронизатор, регистр ча- ;тного, выходы регистра адреса соединены с адресными входами узла па- мяти, выходы первой группы ключей соединены с информацион тыми входами узла.памяти, информационные ВЫХОДЕ. которого соединены с информационш,

5

0

5

0

5

0

0

ми входами второй группы ключей, первый Бькод синхронизатора соединен с входом записи узла памяти, второй вьжод - с входом чтения узла памяти, первый выход синхронизатора - с управляющим входом счетчика команд, второй выход - с управляющим входом регистра адреса, третий выход - с управляюгдими входами первой группы ключей, четвертый выход - с управляюпдз-гми входами второй группы ключей,- пятый выход - с управляющим входом регистра команд, шестой выход - с управляющим входом регистра частичного результата, седьмой выход - с управляюшцим входом сумматора, восьмой выход - с управляющим )зходом регистра делителя, девятый выход - с; управляюш 1М входом регистра частного, десятьй выход - с управляющим входом регистра делителя первая группа входов кода режима синхронизатора соединена с выходами дещифрато- ра команд, входы которого соединены с выходами регис1 ра команд, зьгходы ключей второй группы - с входами регистра команд информационными входами регистра частичного результата, регистра делимого, регистра делителя и выходами сумматора, выходы счетчика команд - с входами регистра адреса, выходы регистра частичного результата - с входами первого слагаемого сумматора, входы второго слагаемого кО Торого соединены с выхода- 1-ш регистра делителя, выходы сум- матера - с второй группой входов кода режима синхронизатора.и с вхо- дам.и регистра частного, выходы которого соединены с информационными иходамк к.шочей г(ервой группы, вы- хо,цы ре.гистра делимого - с третьей группой входов кода режима . синхронизатора, выходь регистра адреса - с входами первого дешифратор а адреса каждого коммутатора исходных данных и результатов, с входами дешифратора адреса каждого ког-шутатора ис- ходнь х и промежуточных данных (п-)-й группы5 с входами дешифраторов адреса первого.J четвертого и шестого комг- утаторов исходных и промежуточных данных 2-(п-2}-х групп, выходы первой группы ключей соединены с входами регистра вывода каждого коммутатора исходных данных и результатов, с входами рег истра каждого коммутатора исходн1,х и промежуточных данных (п-1)-й группы, с входами регистров

первого, четвертого и шестого коммутаторов исходных и промежуточных данных 2-(п-2)-х грунп, входы ключе второй группы --с выходами входных ключей каждого коммутатора исходных данных и результатов, первый выход синхронизатора блока управления соединен с вторым входом первого элемета И каждого коммутатора исходных данных и результатов, с вторым вхо- дом первого элемента И каждого коммутатора исходных и промежуточн данных (п-1)-й группы, с вторыми вхдами первых элементов И первого, четвертого и шестого элементов ис- ходных и промежуточных данных 2-(п- -2)-х групп, второй выход синхронизатора блока управления соединен с вторым входом третьего элемента И каждого коммутатора исходных данных и результатов, выход четвертого элемента И каждого коммутатора исходных данных- и результатов, выходы втрых элементов И первого, четвертого и шестого коммутаторов исходных и промежуточных данных 2-(п-2)-х груп выход второго элемента И каждого комутатора исходных и промежуточных данных (п-1)-й группы соединены с сответствующими входами четвертой группы входов кода режима синхронизатора блока управления,, выходы регистра адреса первого и второго решающих блоков первой группы соединены соответственно с дешифраторами адреса первого, второго, третьего и четвертого коммутаторов исходных и промежуточных данных первой группы, входы второй группы ключей первого второго решающих блоков первой группы соединены соответственно с выходами ключей первого, второго, третьего и четвертого коммутаторов исходных и промежуточных данных первой группы, второй и третий входы четвертой группы входов кода режима синхронизатора первого решающего блока первой группы соединены соответственно с выходами первых элементов И первого и второго коммутаторов исходных и промежуточных данных первой группы, второй и третий входы четвертой группы входов кода режима синхронизатора второго решающего блока первой группы соединены соответственно с выходами первых элементов И третьего и четвертого коммутаторов исходных и промежуточных данных первой группы.

5

0

Q s

0

5

0

5

двенадцатые выходы синхронизаторов первого и второго решаюпц х блоков первой группы соединены соответственно с вторыми входами вторых элементов И первого, второго, третьего и четве ртого коммутаторов исходных и промежуточных данных первой группы, выход второго элемента И, входы регистра, второй вход первого элемента И, входы первого дешифратора адреса первого коммутатора исходных и промежуточных данных первой группы соединены соответственно с вторым входом четвертой группы -входов кода режима синхронизатора,с выходами первой группы ключей, с первым выходом второй группы выходов распределителя импульсов, с выходами регистра адреса первого решающего блока второй группы, входы регистра, второй вход первого элемента И, вхо- ды первых дешифраторов адреса второго и четвертого коммутаторов исходных и промежуточных данных первой группы соединены соответственно с выходами ключей первой группы, одиннадцатым выходом синхронизатора, выходами регистра адреса третьего решающего блока второй группы, выходы вторых элементов И второго и четвертого коммутаторов исходных и промежуточных данных первой группы соединены соответственно с вторым и третьим входами четвертой группы входов кода режима синхронизатора третьего решающего блока второй группы, выход второго элемента И, входы регистра, второй вход первого элемента И, входы первого дешифратора адреса третьего коммутатора исходных и промежуточных данных первой группы соединены соответственно с вторым входом четвертой группы входов кода режима синхронизатора, с выходами ключей первой группы, с один- .надцатым выходом синхронизатора, с:-.. выходами регистра адреса второго решающего блока второй группы, выхо- ды регистра адреса, двенадцатый выход синхронизатора, информационные входы второй группы ключей, первый вход второй группы входов кода режима синхронизатора каждого решающего блока (п-1)-й группы соединены соответственно с входами дешифратора адреса, вторым входом второго элемента И, выходами ключей, выхо- . дом первого элемента И соответствующего коммутатора исходных и проме13

жуточных данных. (п-1)-й группы, выходы регистра адреса, двенадцатый выход синхронизатора, информационные входы ключей второй группы первого решающего блока i-й группы соединены соответственно с выходами дешифратора адреса, вторым входом второго элемента И, выходами ключей второго и третьего коммутаторов исходных и промежуточных данных i-й группы, второй и третий входы второй группы входов кода режима синхронизатора первого решающего блока i-й группы соединены соответственно с выходом первого элемента И второго и третьего коммутаторов исходных и промежуточных данных i-й группы, выходы регистра- адреса, двенадца- тьй выход синхронизатора, информационные входы второй группы ключей, второй вход второй группы входов кода режима синхронизатора второго решающего блока i-й группы соединены соответственно с входами дешифратора адреса, вторым входом второ- го элемента И, выходами ключей, выходом- первого элемента И пятого коммутатора исходных и промежуточных данных i-й группы, выходы регистра адреса, двенадцатый выход синкрони- затора, информационные входы второй группы ключей третьего решающего блока i-й группы соединены соответственно с входами дешифратора адреса вторым входом второго элемента И, выходами ключей седьмого и восьмого коммутаторов исходных и промежуточных данных i-й группы, второй и третий входы второй группы входов кода режима синхронизатора третьего реша- кяцего блока i-й группы соединены соответственно с выходом; первых элементов И седьмого и восьмого коммутаторов исходных и промежуточных данных (i+)-u группы, выход второго

элемента И, входы регистра, второй вход первого элемента И, входы первого дешифратора адреса второго коммутатора исходньпс и промежуточных данных i-й группы соединены соответственно с вторым входом четвертой группы входов кода режима синхронизатора, выходами ключей первой группы, одиннадцатым выходом синхронизатора, с выходами регистра адреса первого решающего блока (i+l)-u группы, вькод второго элемента И, входы регистра, второй вход первого элемента И, входы первого дешифратора адреса седьмого коммутатора исходных и промежуточных данных i-й группы соединены соответственно с вторым, входом четвертой группы входов кода ре- ткнма синхронизатора, вьгходат га ключей первой группь, одиннадцатым выходом синхронизатора, выходами регистра адреса второго решающего блок-i (i+l)-й группы, первого дешифратора адреса третьего, пятого и восьмого коммутаторов исходных и пром :жуточ- ных данных i-й. группы соединены с выходами регистра адреса третьего решающего блока (i+l)-й группы, входы регистра третьего, пятого и восьмого коммутаторов исходных и промежуточ- BbDC данных i-й группы соединены с вькодами первой группы ключей третьего решающего блоха (i+l)- группы, вторые входы первых элементов И третьего, пятого и восьмого коммутаторов исходных и промежуточных данных i-й группы соединены с одиннадцатым выходом синхронизатора третьего решающего блока (i+)-й группы, выходы вторых элементов И третьего, пятого и восьмого коммутаторов исходных и промежуточных данных i-й группы соединены с четвертой группой входов кода режима синхронизатора третьего решающего блока ()-й группы.

0HS.l

I

L

Ш 8.

lit 9

12.1 Фиъ.З

37

:л

б.} 1

6, г

Jn

е.з

GJ

-U.

а

V/n

,ff

Запрос 12

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1233148A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Система обработки нечеткой информации | 1987 |

|

SU1444803A1 |

| Устройство для решения дифференциальных уравнений | 1985 |

|

SU1348854A1 |

| Процессор | 1977 |

|

SU691858A1 |

| Устройство для решения дифференциальных уравнений | 1986 |

|

SU1383391A1 |

| Устройство для решения дифференциальных уравнений | 1982 |

|

SU1104513A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для решения дифференциальных уравнений | 1985 |

|

SU1330635A1 |

Изобретение относится к цифровой вычислительной технике, к устройствам для обработки цифровых данных и может быть использовано для решения дифференциальных уравнений в частных производных. Цель изобретения - повышение производительности устройства. Цель изобретения достигается за счет введения в устройство, групп из трех решающих блоков и групп коммутаторов исходных и промежуточных данных с соответствующими функциональными связями между ними и известными блоками устройства. Устройство работает более производительно за счет распараллеливания вычислительного процесса в решающих блоках. П ил. с S INO СО 00 4 СО

А.

.3.1

М

Чт

Запрос

/ j 7

45

Ч

e.t/ш

N

ЗД

Т

Z,r.

w

w/Ftt

50

«

a

ff,f

SjvK gnpaSjKHuf

tT-lf gt; I tf I an ff i If I a

n-Z

.X . . . .

.., .-г .г. I Vt., I гГуГдгпаа

,- Aiit V. 1°/.-,., I cloMxa

Л-/ Л-/ n. i4t /tfS n S Такты Фа 7

n..rt

rviHO/i 1нвач11 affpfca гз-ге)

С(/гнол 4mfHuft (is-ш

Сигна/i gnpaSfltHif 9 овн1м nmava

(J-tvi Cvtmji записи t/It .iucmp /7/ Сигнал инкремента (гз- 191

Cuttofl tSava ов- peca

Сигнал йывааи из IKtucmtta (tJ- ttl

CutMtjt gfipa&K- MHi вчавнт длкпж

Стнвл затки

Cut нал оовачи. offfeca (гз-Ю

CuSHoa тггений f«-W/

Стал ynpattmui

ТгДТЛ

O/««w юписи и fftaaapllS-e

Htnra 4mffafi Лгнних a a иле из tMeuiwty устройства в iS

пмажит аьнон ре|у, Stft/jittOHut

f-ТЗноя ptivibnama и-гз5

(8вие fiezucrr ае/пичного рвмл- tnomo сгзг-w;

Sf ripii af piinaitie/itn, o резуяыг ате iavunxJHia

jr-.

.

.

Сигнал выдачи ев реса ff6-J3l

CutHO чтен1- я

iff-36

Сигнал упрайлгния iuSHHf 1 /1ючя}1Я-Л,

Гйгнаг записи 1ре- lut.vp(l6-m Сагчап umpetffmm

гo-зo)

tutHOf внвача о}- feca (-«;

CutHOn вывоча из регистра ItS-ffI

CuiHOt/i anpotae,

futmn ynpaSaefyn внхввнм Mfoveu (ZS-35)

Cut нал (S3-Xl

Cuttat вивоча aff- peca{l6-33f

CatHofi чтения

a-3ei

Сигнал jfnpoiasHe

CatMOf ianufg t Bt- futnv Пв-ЗЧ)

HUM чтений HOHHut u) XuiH ui внгшнеп ycmpoucmfa S 34

Фи9.в

Cfftut регистра #/w; рого огеранЗь (if-Л)

jHtJveme разеяба (

Сигнал CflOKtHvK

ге-зг

Уапись (регистр резутгпо гю )

Запись S регистр vacniuvMia резул- гттз (ze-ZSI

а fat регистра

fjimuvmio рездт- пато (26-28)

(Jjfitatatmt ,f t cmiyttif«t

f/ c(fSiri( ,0( cmtytufH pajpt

CiSui регистра 6t раго anepanSa

Значение сб1инуток разряд 21-26)

fdSuz оегистро частичного результата №-№t

Фиг II

Составитель А.Чекалов Редактор Н.Рогулич Техред Л.Олейник

2771/50

Тираж 671- Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Рйушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор Е.Рошко

| Вычислительная система для решения дифференциальных уравнений | 1975 |

|

SU620980A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Резервированное устройство с управляемой структурой | 1975 |

|

SU565298A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| , | |||

Авторы

Даты

1986-05-23—Публикация

1983-12-19—Подача