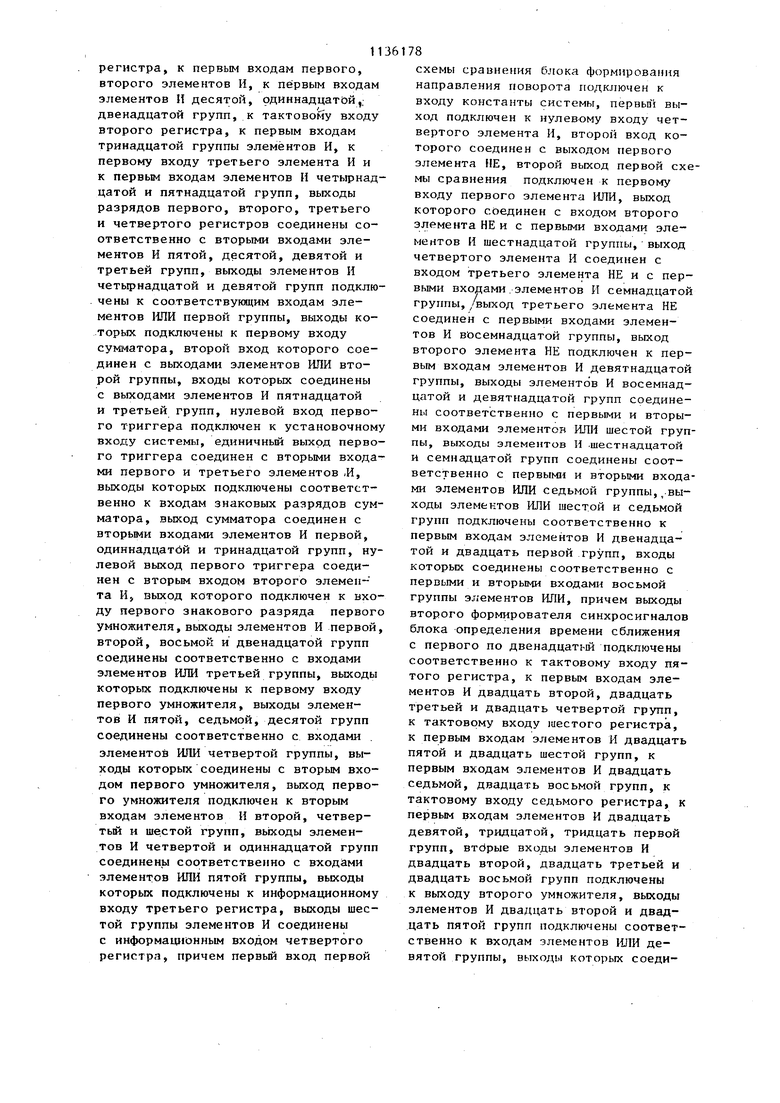

регистра, к первым входам первого, второго элементов И, к первым входам элементов П десятой, одиннадцатой,, двенадцатой групп, к тактовому входу второго регистра, к первым входам тринадцатой группы элементов И, к первому входу третьего элемента И и к первым входам элементов И четырнадцатой и пятнадцатой групп, выходы разрядов первого, второго, третьего и четвертого регистров соединены соответственно с вторыми входами элементов И пятой, десятой, девятой и третьей групп, выходы элементов И четырнадцатой и девятой групп подключены к соответствующим входам элементов ИЛИ первой группы, выходы которых подключены к первому входу сумматора, второй вход которого соединен с выходами элементов Р1ЛИ второй группы, входы которых соединены с выходами элементов И пятнадцатой и третьей групп, нулевой вход первого триггера подключен к установочному входу системы, единичный выход первого триггера соединен с вторыми входами первого и третьего элементов /И, выходы которых подключены соответственно к входам знаковых разрядов сумматора, выход сумматора соединен с вторыми входами элементов И первой, одиннадцатой и тринадцатой групп, нулевой выход первого триггера соединен с вторым входом второго элемепта И, выход которого подключен к входу первого знакового разряда первого умножителя, выходы элементов И первой второй, восьмой и двенадцатой групп соединены соответственно с входами элементов ИЛИ третьей группы, выходы которых подключены к первому входу первого умножителя, выходы элементов И пятой, седьмой, десятой групп соединены соответственно с входами . элементов ИЛИ четвертой группы, выходы которых соединены с вторым входом первого умножителя, выход первого умножителя подключен к вторым входам элементов И второй, четвертый и ше.стой групп, элементов И четвертой и одиннадцатой групп соединены соответственно с входами элементов ИЛИ пятой группы, выходы которых подключены к информационному входу третьего регистра, выходы шестой группы элементов И соединены с информационным входом четвертого регистра, причем первый вход первой

схемы сравнения блока формирования направления поворота подключен к входу константы системы, перньп выход подключен к нулевому входу четвертого элемента И, второй вход которого соединен с выходом первого элемента НЕ, BTOpofi выход первой схемы сравнения подключен к первому входу первого элемента ИЛИ, выход которого соединен с входом второго элемента НЕ и с первыми входами элементов И шестнадцатой группы, выход четвертого элемента И соединен с входом третьего элемента НЕ и с первыми входами.элементов И семнадцатой группы, /выход третьего элемента НЕ соединен с первыми входами элементов И восемнадцатой группы, выход второго элемента НЕ подключен к первым входам элементов И девятнадцатой группы, выходы элементов И восемнадцатой и девятнадцатой групп соединены соответственно с первыми и вторыми входами элементов ИЛИ шестой группы, выходы элементов И .шестнадцатой и семнадцатой групп соединены соответственно с первыми и вторыми входами элементов ИЛИ седьмой группы,.выходы элементов ИЛИ шестой и седьмой групп подключены соответственно к первым входам элементов И двенадцатой и двадцать первой групп, входы которых соединены соответственно с первыми и вторыми входами восьмой группы э 1ементов ИЛИ, причем выходы второго формирователя синхросигналов блока определения времени сближения с первого по двенадцатый подключены соответственно к тактовому входу пятого регистра, к первым входам элементов И двадцать второй, двадцать третьей и двадцать четвертой групп, к тактовому входу luecToro регистра, к первым входам элементов И двадцать пятой и двадцать шестой групп, к первым входам элементов И двадцать седьмой, двадцать восьмой групп, к тактовому входу седьмого регистра, к первым входам элементов И двадцать девятой, тридцатой, тридцать первой групп, втбрые входы элементов И двадцать второй, двадцать третьей и двадцать восьмой групп подключены к выходу второго умножителя, выходы элементов И двадцать второй и двадцать пятой групп подключены соответственно к входам элементов Ш1И девятой группы, выходы которых соедиены с входом уменьшаемого первого ычитателя, вход вычитаемого котороо подключен к выходам элементов ИЛИ есятой группы, первые входы которых соединены с выходами элементов И вадцать третьей группы, выходы элементов И двадцать шестой группы подлючены к вторым входам элементов ИЛИ есятой группы .и к первым входам одиннадцатой группы элементов ИЛИ, вторые входы элементов И двадцать шестой группы подключены к выходам разрядов пятого регистра, первьш и второй входы второго умножителя подключены соответственно к выходам элементов ИЛИ одиннадцатой группы и к выходам элементов И двадцать девятои группы, выходы тридцать первой группы элементов И подключены к вторым входам элементов ИЛИ одиннадцатой группы,.выход первого вычитателя подключен к вторым входам элементов И тринадцатой группы, выходы которой соединены с первым входом узла деления, второй вход которого подключен к выходам элементов ИЛИ двенадцатой группы, первые и вторые входы которой подключены к: выходам элементов И двадцать восьмой и двадцать четвертой групп соответственно, выход узла деле ния соединен с информационными входами шестого и седьмого регистров, выходы разрядов шестого регистра подключены к вторым входам элементов И вадцать седьмой группы, выходы которой соединены с первыми входами тринадцатой группы элементов ИЛИ, вторые входы которой соединены с выходами разрядов седьмого регистра, выходы элементов ИЛИ с второго по шестой подключены соответственно к входу управления.считыванием первого оперативного запоминающего устройства блока памяти исходных данных, к информационному входу первого ревер-. сивного счетчика, к входу вычитания второго реверсивного счетчика, к входу управления записью первого оперативного запоминакхцего устройства, к входу суммирования первого реверсивного счетчика, выходы разрядов первого и второго реверсивных счетчиков подключены cooTBeTCTBeHHOj к входам первого и второго дешифраторов, выходы которых соединены соответственно с младшей и старшей группами адресных разрядов первого оперативного запоминающего устройства, выходы

разрядов второго реверсивного счетчика подключены к входу третьего дешифратора, выходы которого соединены с входами седьмого элемента ШШ, информационный вход второго реверсивного счетчика подключен к выходам элементов И тридцать второй группы, первые входы которой соединены с выходами разрядов восьмого регистра, выходы элементов ИЛИ четырнадцатой группы соединены с информационным входом первого оперативного запоминающего устройства, причем первый и второй тактовые входы с первого по шестой узлов дешифрации команд блока управления подключены соответственно к первому и второму выходам генератора тактовых импульсов, входы пуска с второго по питый уэлов дешифрации команд подключены соответственно к выходам первого, второго, третьего и четвертого элементов И-НЕ, вход пуска первого узла дешифрации команд и единичный вход первого триггера соединены с входом пуска системы, установочные входы с первого по шестой узлов дешифрации команд соединены с установочным входом системы, первые выходы узлов дешифра1щи команд соединены с установочным входом системы, первые выходы узлов дешифрации команд с первого по пятьй подключены соответственно к входам восьмого элемента ИЛИ, первые выходы узлов дешифрации-команд с второго по пятый подключены соответственно к входам установки исходного состояния узлов дешифрации команд с первого по четвертый, первые выходы узлов дешифрации команд с третьего по пятый соединены соответственно с входами девятого элемента ИЛИ, вторые выходы узлов дешифрации Команд с. первого по четвертый подключены к первым входам элементов И-НЕ с первого по четвертьм соответственно, вторые выходы четвертого и пятого узлов дешифрации команд подключены соответственно к первому и второму входам десятого элемента ИЛИ, второй выход пятого узда дешифрации кбманд подключен к первому входу пятого элемента И, причем выходы с первого по восьмой первого распределителя импульсов блока тригонометрических преобразований подключены соответственно к первым входам одиннадцатого элемента ШШ и первым входам влементов И тридцать

третьей группы, к первым входам элементов И тридцать четвертой группы, к первым входам шестого и седьмого элементов И и к тактовому входу девятого регистра, к первому входу восьмого элемента И и к первому тактовому входу десятого регистра, к первым входам элементов И тридцать пятой группы и к первым входам девятого и десятого элементов И, к первы входам элементов И тридцать щестой группы, к первому входу одиннадцатого элемента И, к входу считывания второго оперативного запоминающего устройства, к второму тактовому вход десятого регистра, к первым входам двенадцатого и тринадцатого элементов И и к входу элемента задержки, выход которого соединен с первым входом первого элемента ИЛИ-НЕ, второй вход которого соединен с установочным входом системы, а выход под ключен к нулевым входам второго и третьего триггеров, единичньй выход второго триггера подключен к вторым входам девятого, одиннадцатого и двенадцатого элементов И и к первому входу двенадцатого элемента ИЛИ, единичный выход третьего триггера подключен к вторым входам восьмого, девятого и тринадцатого элементов И и двенадцатого элемента ИЛИ, выход девятого элемента И соединен с вторым входом одиннадцатого элемента ИЛИ, третий вход которого соединен с выходом седьмого элемента И, а выход с первьми входами элементов И Тридцать группы, выходы которой сое; инены с первыми входами элементов ИЖ пятнадцатой группы, вторые и третьи входы которой подключены соответственно к выходам элементов И тридцать восьмой и тридцать девятой групп, выходы элементов ИЛИ пятнадцатой груцпы подключены к входу вычитаемого второго вьгчитателя, вход уменьшаемого которого соединен с выходаьм элементов ИЛИ шестнадцатой группы, входы которой подключены к выходам элементов И тридцать третьей тридцать четвертой, тридцать пятой групп соответственно, вторые входы элементов И тридцать третьей и тридцать пятой групп соединены с выходами разрядов одиннадцатого и двенадцатого регистров соответственно, вторые входы элементов И тридцать четвертой и тридцать седьмой групп подключены к выходу группы разрядов модуля числа тринадцатого регистра, выход модуля результата второго вычитателя подключен к вторым входам элементов.И тридцать шестой группы и к информационному входу девятого регистра, знаковый выход результата второго вычитателя соединен с первъат входами четырнадцатого и пятнадцатого элементов И, с вторым входом шестого элемента И и с входом четвертого элемента НЕ, выход которого подклю- . чен к второму входу седьмого элемента И, выходы одиннадцатого, восьмого и десятого элементов И подключены соответственно к вторым входам четырнадцатого и .пятнадцатого элементов И и к первым входам элементов И тридцать восьмой группы, вторые входы которой соединены с выходамк разрядов девятого регистра, выходы четырнадцатого и пятнадцатого элементов И соединены с первым и вторым входами тринадцатого элемента ИЛИ соответственно, .а выход подключён к входу знакового разряда десятого регистра, информационный вход которого соединен с выходом второго оперативного запоминающего устройства, адресньга вход которого соединен с выходом элементов И тридцать шестой группы, выход двенадцатого элемента ИЛИ подключен к входу начальной установки десятого регистра, и к входу,сброса первого распределителя импульсов, выход шестого элейента И соединен с первыми входами элементов И тридцать девятой группы, вторые входы которой соединены с выходами разрядов четырнадцатого регистра, причем первьй и второй входы второй схемы сравнения блока определения маневра подключены соответственно к выходам разрядов пятнадцатого и шестнадцатого регистрой, выходы разрядов шестнадцатого регистра соединены с информационными входами семнадцатого и восемнадцатого регистров, тактовые входы пятнадцатого и шестнадцатого-регистров подключены к выходам четырнадцатого элемента ИЛИ и шестнадцатого элемента И соответственно, .первьй выход Jвтopoй схемы сравнения подключен к . первому входу семнадцатого элемента И, выход которого соединен с первым входом четырнадцатого элемента ИЛИ, второй выход схемы сравнения подключен к первому входу шестнадца.1

того элемента И, причем тактовые входыдевятнадцатого и двадцатого регистров блока классификации целей подключены к выходам пятнадцатого элемента ИЛИ и восемнадцатого элемента И соответственно, выходы разрядов соединенысоответственно с первым и вторым входами третьей схемы сравнения, выходы разрядов двадцатого регистра подключены к информационному входу двадцать первого регистра, первый выход третьей схемы сравнения подключен кпервому входу девятнадцатого элемента И, выход которого соединен с первым входом пятнадцатого элемента- ИЛИ, второй выход третьей схемы сравнения подключен к первому входу восемнадцатого элемента И, причем первьй и второй выходы второго распределителя импульсов блока анализа подключены соответственно к управлякяцему входу сдвигового регистра и к первът входам двадцатого и двадцать первого элементов И, вход запуска второго распределителя импульсов подключен к выходу.шестнадцатого элемента ИЛИ, первьй и второй входы которого соединены с выходами, двадцать второго и двадцать третьего элементов И соответственно, первый и второй входы двадцать третьего элемента И подключены к выходу двадцать первого элемента И и пятого элемента НЕ соответственно, информационный вход сдвигового регистра подключен к Bbtx од аи сороковой группы элементов И, ныяад( старшего разряда сдвигового регистра соединен с вторым входом двадцатого элемента И и с входом пятого элемента НЕ, выход двадцатого элемента И подключен к первым входам двадцать четвертого и двадцать пятого элементов И, причем выходы с первого по четвертый третьего распределителя импульсов блока индикации опасных судов подключены соответственно к нулевому входу четвертого регистра, к первым входам двадцать шестого элемента И, двадцать седьмого элемента и к первому входу запуска третьего распределителя импульсов, выход первого элемента И подключен к единичному входу четвертого триггера, единичный выход которого соединен с вторьм входом двадцать седьмого элемента. И, выход которого соединен с первым входом двадцать восьмого эле8

мента И, второй вход которого подключен к выходу четвертой схемы сравнения, а выход - к первым входам сорок первой группы элементов И, вторые входы которых соединены с соответствующими выходами четвертого дешифратора, выходы элементов И сорок первой группы подключены к информационному входу двадцать второго регистра, выходы с тринадцатого по девятнадцатьй второго формирователя синхросигналов подключены соответственно к первому входу четвертого элемента ИЛИ, к второму входу пятнадцатого элемента ИЛИ, к первому входу пятого элемента ИЛИ, к первому входу третьего элемента ИЛИ, к первому входу шестого элемента ИЛИ, к первому входу второго элемента ИЛИ, к вторым входам восемнадцатого и девятнадцатого элементов И, вькоды разрядов седьмого регистра подключены соответственно к входам разрядов девятнадцатого и

двадцатого регистров, выходы элементов ИЛИ тринадцатой группы подключены к первым входам элементов НПИ четырнадцатой группы, информационный выход первого оперативного запоминающего устройства подключен к вторым входам элементов И двадцать пятой, двадцать девятой и тридцать первой групп, к информационному входу пятого регистра, к первому входу четвертой схемы сравнения, к вторым-входам элементов И седьмой, двенадцатой, четырнадцатой и пятнадцатой групп, к информационным входам первого и второго регистров, выход переноса второго реверсивного счетчика соединен с вторыми- входами первого, второго, третьего и четвертого элементов И-НЕ,

выход седьмого элемента ИЛИ подключен

c вторым входам двадцать первого и двадцать второго элементов И, выходы разрядов второго реверсивного счетчика подключ-ены соответственно к входам четвертого дешифратора, первьй выход первого -узла дешифрации команд соединен с установочным входом седьмого регистра и с входом запуска второго

ормирователя синхросигналов, второй выход подключен к установочному входу второго формирователя синхросигналов, второй выход второго узла дещифрации команд соединен с вторым входом двад- . цать шестого элемента И и с установочным входом третьего распределителя импульсов,второй вход запуска которого и вход начальной установки двадцать второго регистра соединены с первым выходом второго узла дешифрации комзвд, выход первого элемента И-НЕ подключен к тактовому входу двадцать первого регистра, второ1й выход третьего узла дешифрации команд подключен к второму входу двадцать пятого элемента И, выход десятого элемента ИЛИ соединен с вторым входом двадцать четвертого элемента И,/йыход пятого элемента И подключён к тактовому входу восемнадцатого регистра, тактовый вход семнадцатого регистра и вычитающий вход первого реверсивного счетчика соединены с выходом четвертого элемента И-НЁ, выход шест-ого узла дешифрации команд соединен с входом запуска первого распределителя импульсов, выход восьмого элемента ШШ соединен с вторь&ш входами элементов И тридцать второй группы, выход девятого элемента ИЛИ подключен к первым входам сороковой группы и к третьему входу шестнадцатого элемента ИЛИ,

выход пятого триггера соединен с установочными входами второго распределителя импульсов и первого формирователя синхросигналов, нулевой вход пятого триггера подключен к входу пуска системы, второй выход генератора тактовых импульсов соединен с тактовыми входами первого и второго формирователей синхросигналов, первого, второго и третьего распределителей импульсов, восьмой выход первого распределителя импульсов подключен к входу установки исходного состояния шестого узла дешифрации команд, выходы разрядов десятого регистра соединены с вторым входом восьйой группы элементов И, выходы разрядов тринадцатого регистра подключены к второму входу первой схемы сравнения, к второму входу первого элемента ИЛИ и к входу первого элемента НЕ, вюсод двенадцатого элемента И соединен с первым входом первого формирователя синхросигналов, второй вход которого соединен с выходом тринадцатого элемента И, выходы разрядов семнадцатого и восемнадцатого регистров соединены соответственно с входами

блока индикации, выходы разрядов двадцать первого регистра соединены с вторым входом четвертой схемы сравнения, выходы разрядов двадцать второго регистра соединены с вторыми входами элементов И сороковой группы, первый выход третьего распределителя импульсов подключен к второму входу четвертого элемента ИЛИ, выход двадцать шестого элемента И соединен с вторым входом второго элемента ИЛИ, выходы двадцать четвертого и двадцать пятого элементов И соединены соответст;венно с третьим и четвертым входами первого формирователя синхросигналов, первый выход второго распределителя импульсов подключен к третьему входу четвертого эле- мента ИЛИ, выходы элементов И тринадцатой группы соединены с информационным входом тринадцатого регистра, выходы разрядов первого регистра подключены соответственно к входам разрядов пятнадцатого и шестнадцатого регистров, выходы разрядов четвертого регистра соединены с вторыми входами элементов И шестнадцатой и девятнадцатой групп, выходы разрядов третьего регистра соединены с вторыми входами элементов И семнадцатой и восемнадцатой групп, выходы первого формщ)ователя синхросигналов с двадцать второго по тридцать второй соединены соответственно с единичными входами второго и третьего триггеров, с первьм входом семнадцатого элемента ИЛИ, выход которого подключен к первому входу двадцать второго элемента И, к второму входу пятого элемента ИЛИ, к третьему входу второго элемента ИЛИ, к второму входушестого элемента ИЛИ, к второму входу четырнадцатого элемента ИЛИ,, к вторым входам шестнадцатого, семнадцатого элементов И и к второму входу семнадцатого элемента ИЛИ, к входу пуска шестого узла дешифрации команд к BTopbw входам элементов И двадцать первой группы и к вторым входам элементов И двадцатой. группы, выходы восьмой группы элементов ИЛИ соединены с вторыми входами элементов ШШ четырнадцатой группы.

Изобретение относится к вычислительной технике и может использойаться для автоматизированного управления судами с применением систем предупреждения столкновения судов,

Известна система предупреждения столкновений судов, содержащая датчики скорости собственного судна, его курса, относительной дальности и пеленга, электронную вычислительную ма шину (ЭВМ) и блок индикации, причем выходы датчиков скорости собственного судна,-его курса, относительной дальности и педенга подключены к соответствующим входам электронной вычислительной машины, выход которой подключен к входу блока индикации 1J

Недостатками этой системы являются сложность, так как реализация требует включения, электронной вычислительной машины, низкая точность и надежность оценки, безопасности плавания в случае маневрирования встречного судяа, невозможность автоматизации процесса управления расхождением судов, высокий уровень напряженности работы судоводителя, требование точного определения курса встречного судна, что затруднительно в случае его маневрирования.

Известно устройство предупреждения столкновений судов. Которое повышает точность оценки безопасности плавания при маневрировании собственного судна, содержащее датчики скорости собственного судна, его курса, относительной дальности и пеленга, электронную вычислительную машину и блок индикации, причем выходы датчиков скорости собственного судла, его курса, относительной дальности и пеленга подключены к соответствующим входам электронной вычислительно и машины, выход которой подключен к входу блока индикации C2l

Недостаткаш этого устройства являк1тся сложность, низкая точность и надежность оценки безопасности плавания в случае маневр ирования встречного судна, невозможность автоматизации процесса управления расхождением судов, высокий уровень напряженности работы судоводителя, требование точного огфеделения курса встречного судна, что затруднительно в случае его наиеврирования.

Наиболее близкой по технической :сущности к изобретению является система, предназначенная для расчета ближайшей точки подхода к координатам цели и собственного положения судна. Она содержит панель набора параметров, связанную с блоком кодирования, который соединен с запоминающим устройством, устройство кодирования адреса данных, счетчик адреса, счетчик программы, подключенный к постоянному запоминающему устройству программ и процессор СзД.

Недостатками известной системы являются отсутствие возможности предварительной селекции встречных судов по степени опасности, а также неработоспособность устройства при наличии нескольких опасных судов.

Целью изобретения является расширение функциональных возможностей путем обеспечения предварительной селекции судов по степени опаснбсти и обеспечения безопасности плавания при наличии нескольких опасных судов

Поставленная цель достигается тем что в вычислительную систему, содержащую блок формирования угловых скоростей, блок формирования направления поворота, блок индикации и блок памяти исходных данных, введены блок определения времени сближения, блок управления, блок тригонометрических преобразований, блок определения маневра, блок классификации целей, блок анализа и блок индикации jonacных судов, причем блок формирования угловых скоростей содержит группы элементов И, ИЛИ, элементы И, регистры, сумматор, умножитель и первый формирователь синхросигналов,блок формирования направления поворота содержит группы элементов И, ИЛИ,элементы И, ИЛИ, НЕ и схему сравнения, блок определения времени сближения содержит вычитатель, делитель, регис тры, умножитель, группы элементов И, ИЛИ и второй формирователь синхросигналов, блок памяти исходных данньк с.одержит. регистр, группу элементов И, ИЛИ, дешифраторы, реверсивные счетчики, элементы ИЛИ и оперативное запоминающее устройство, блок управления

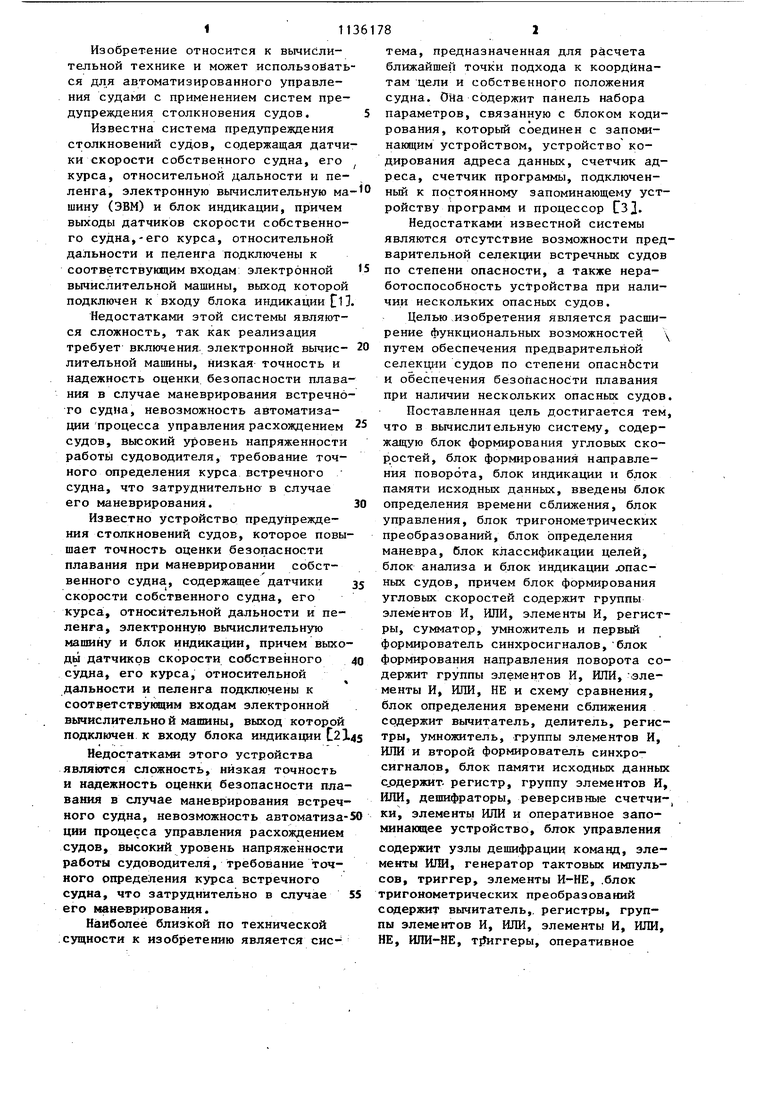

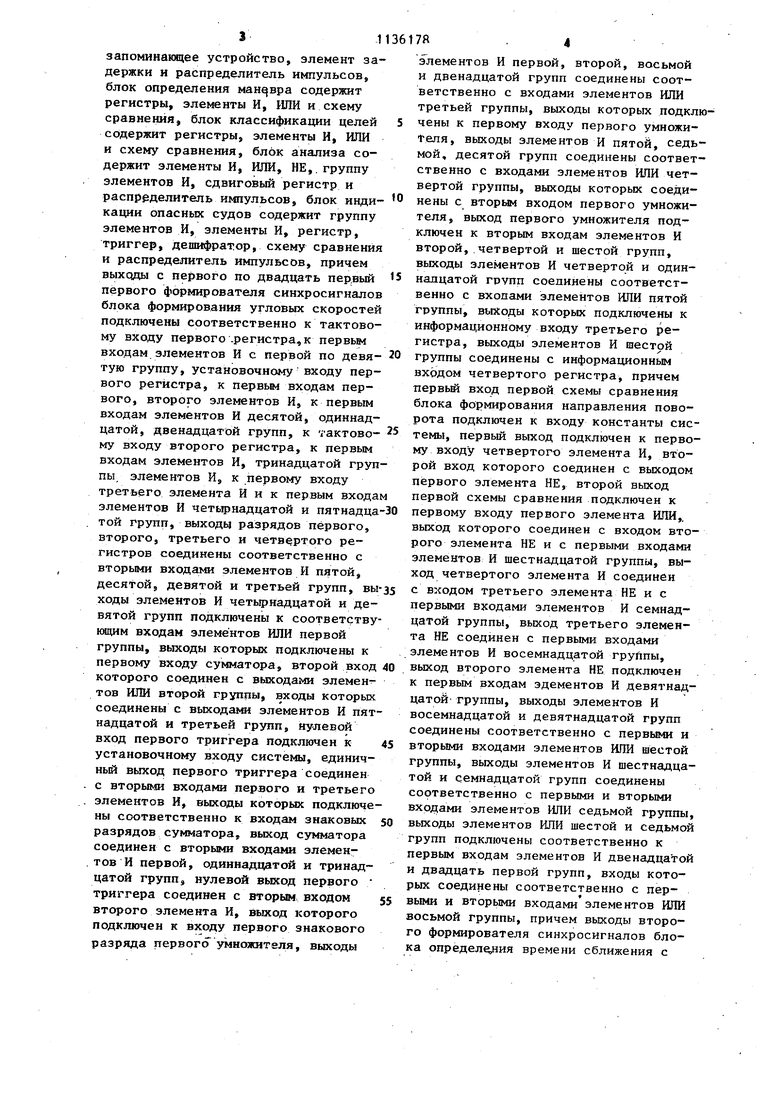

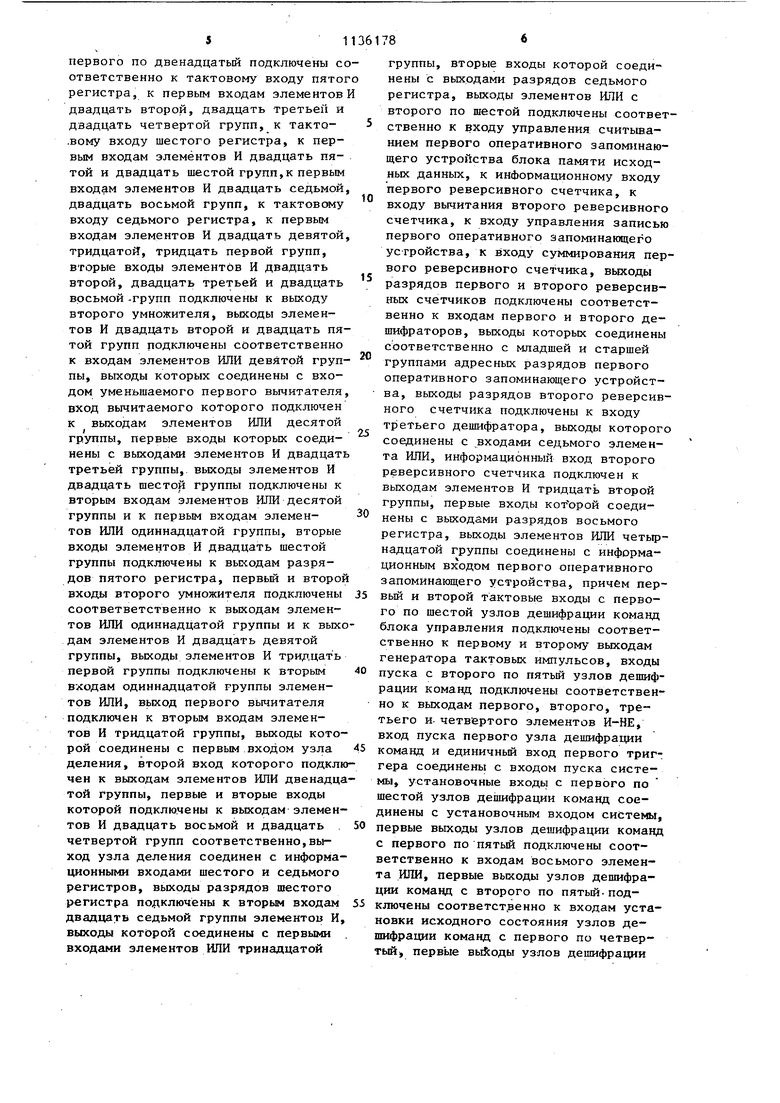

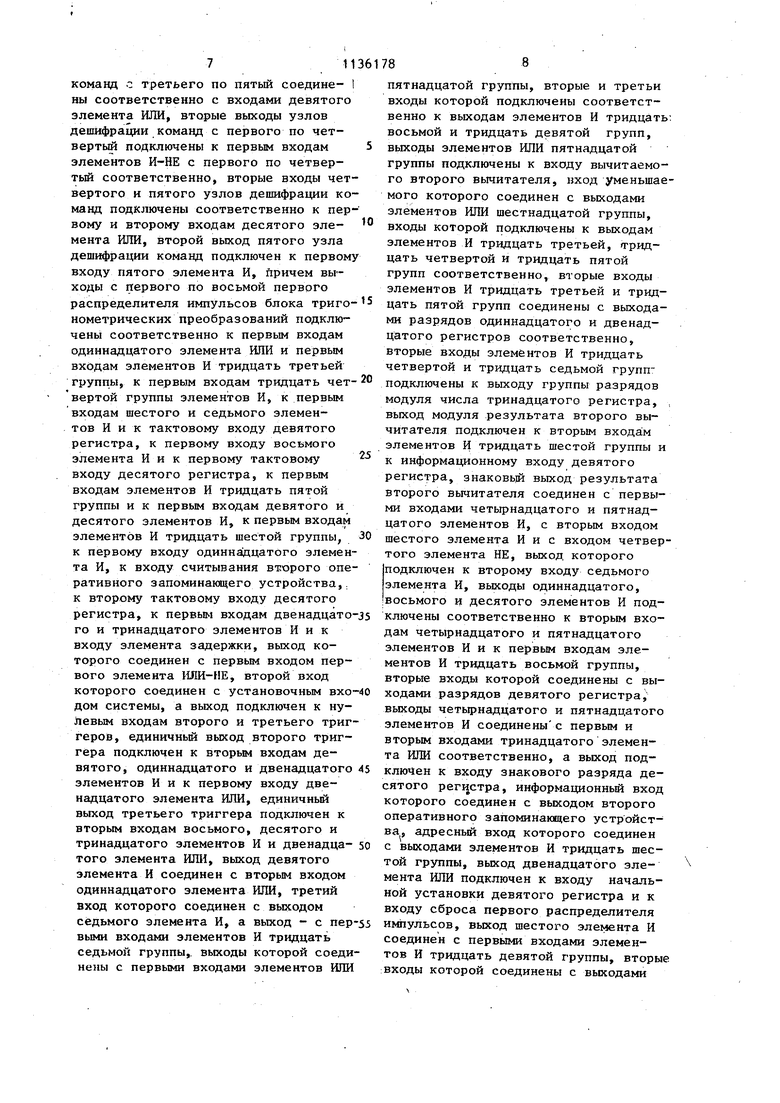

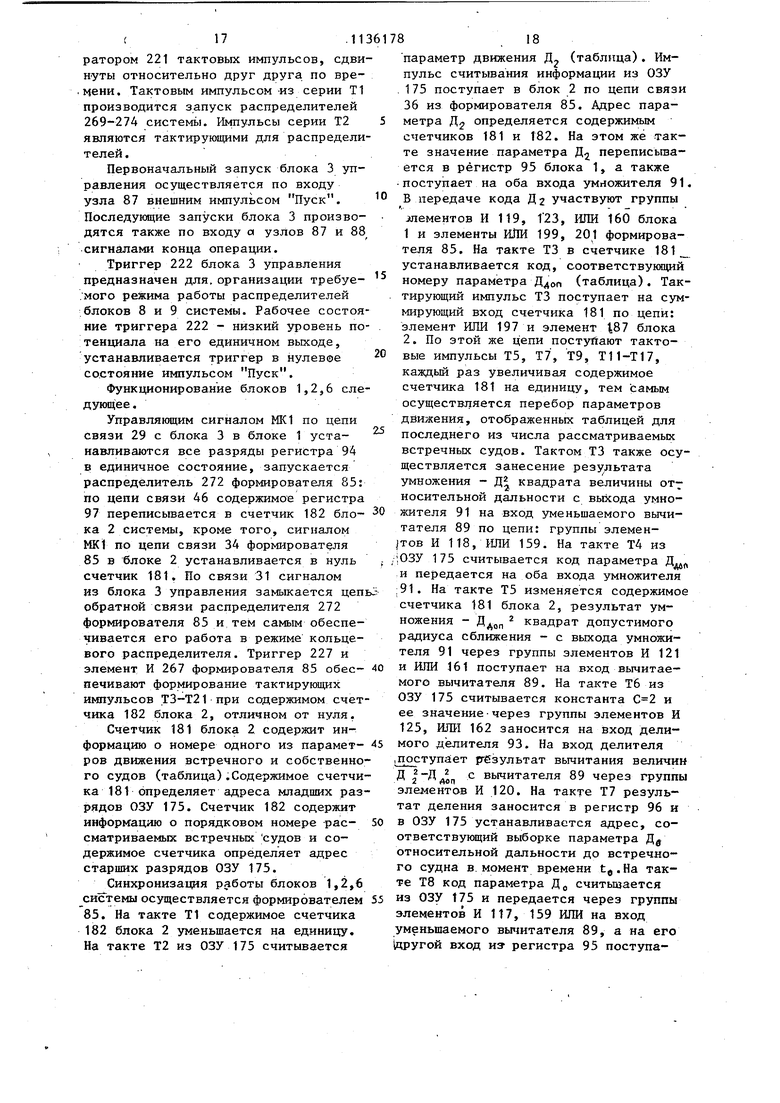

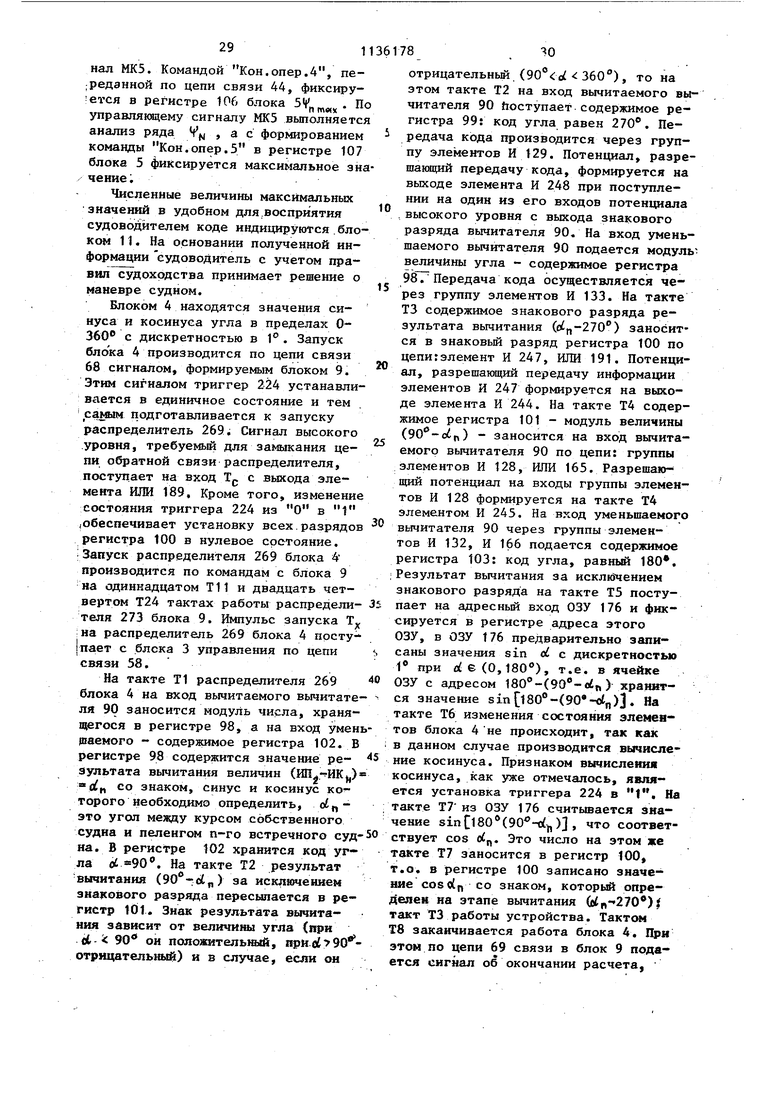

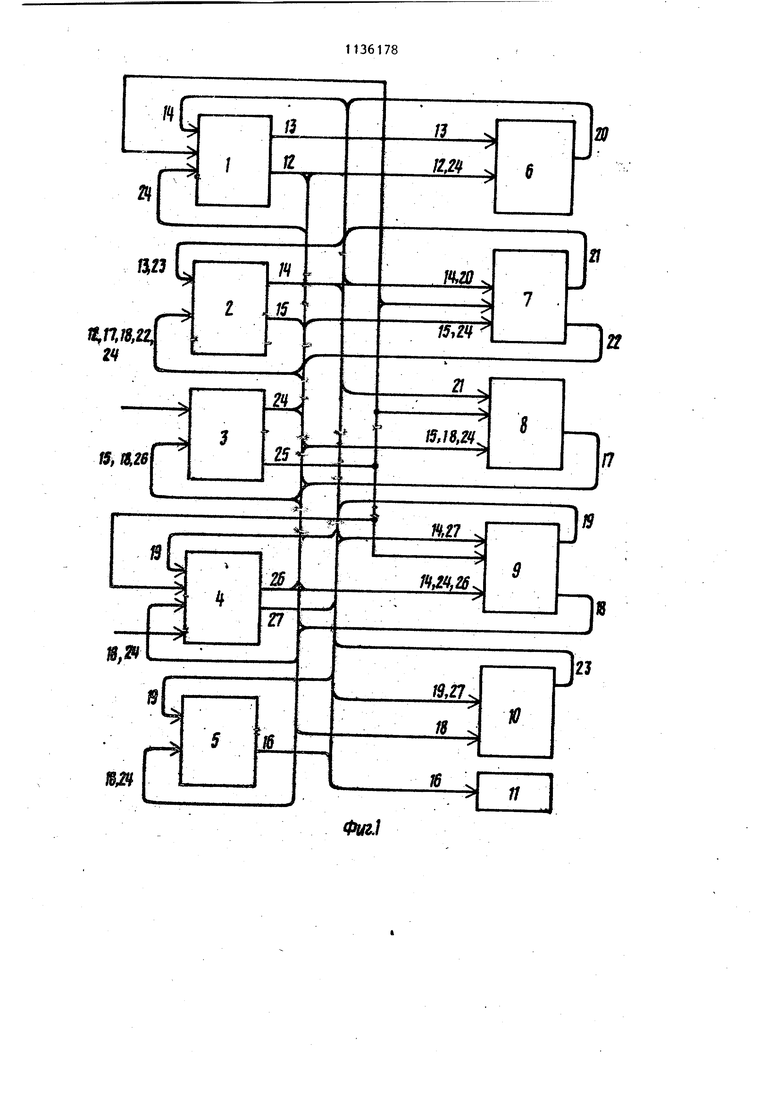

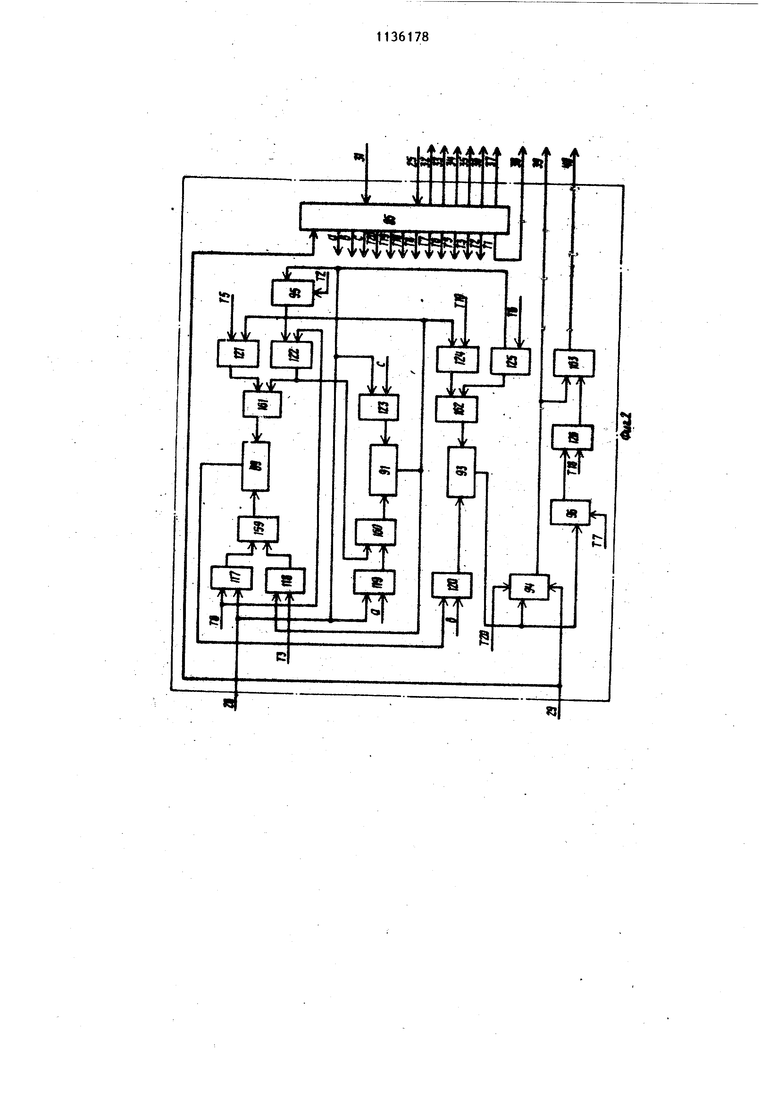

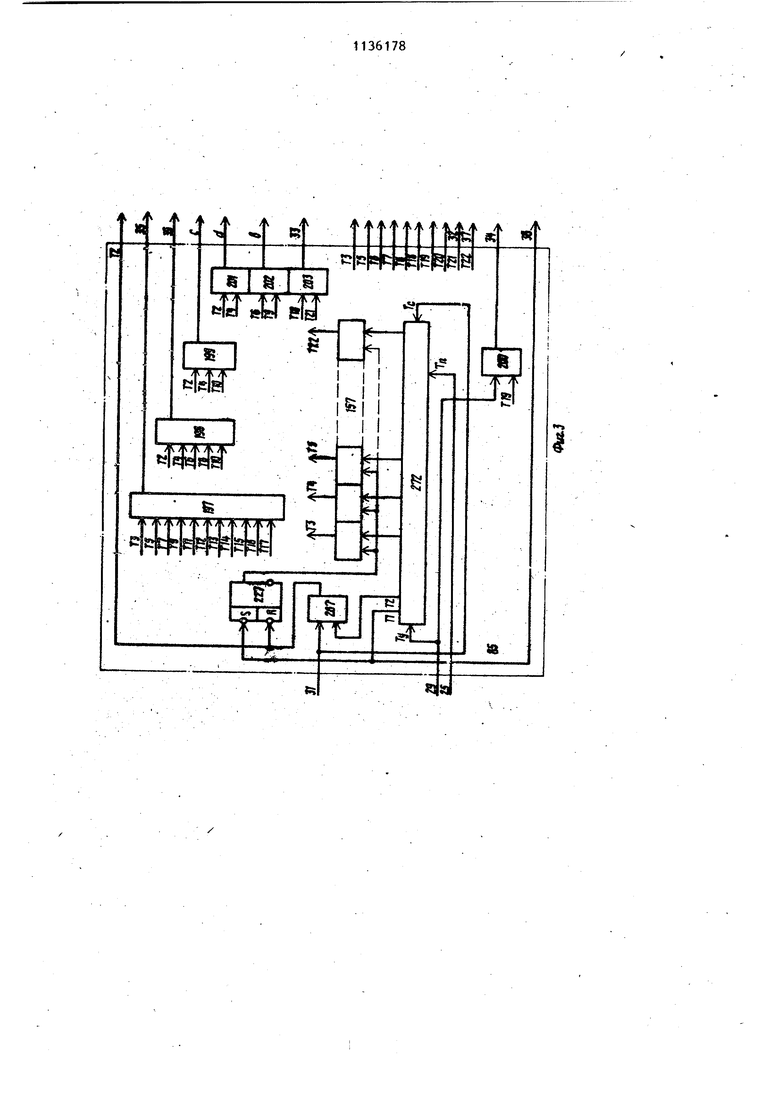

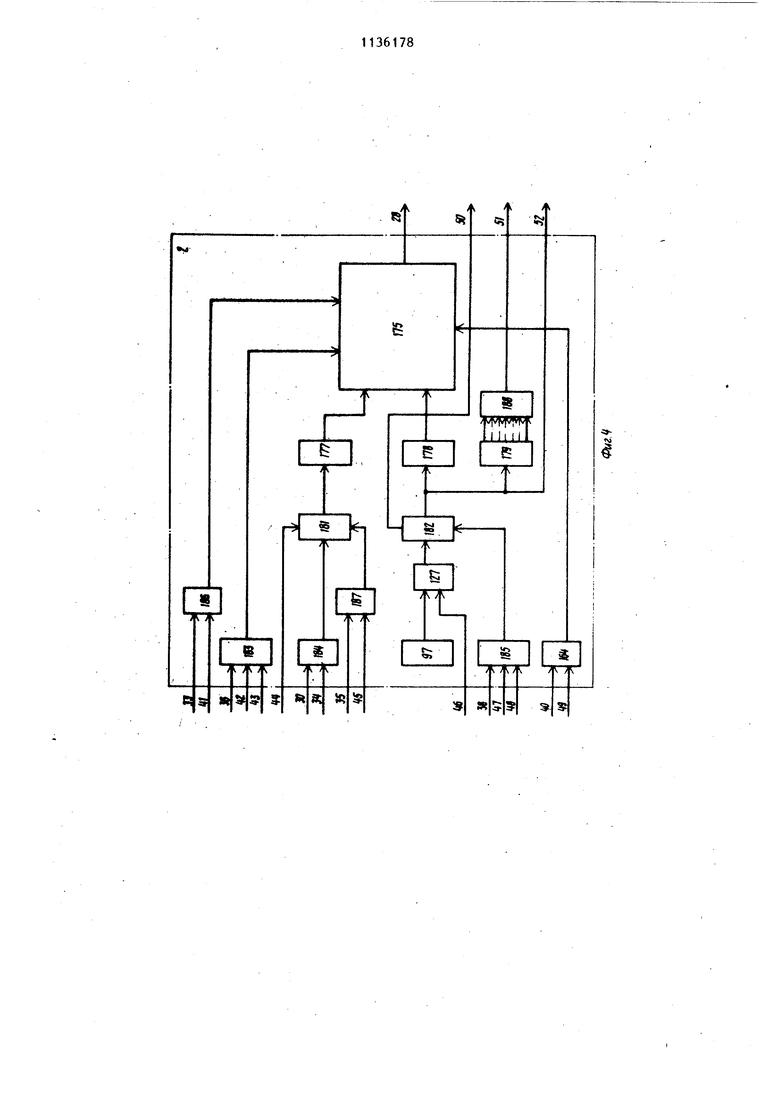

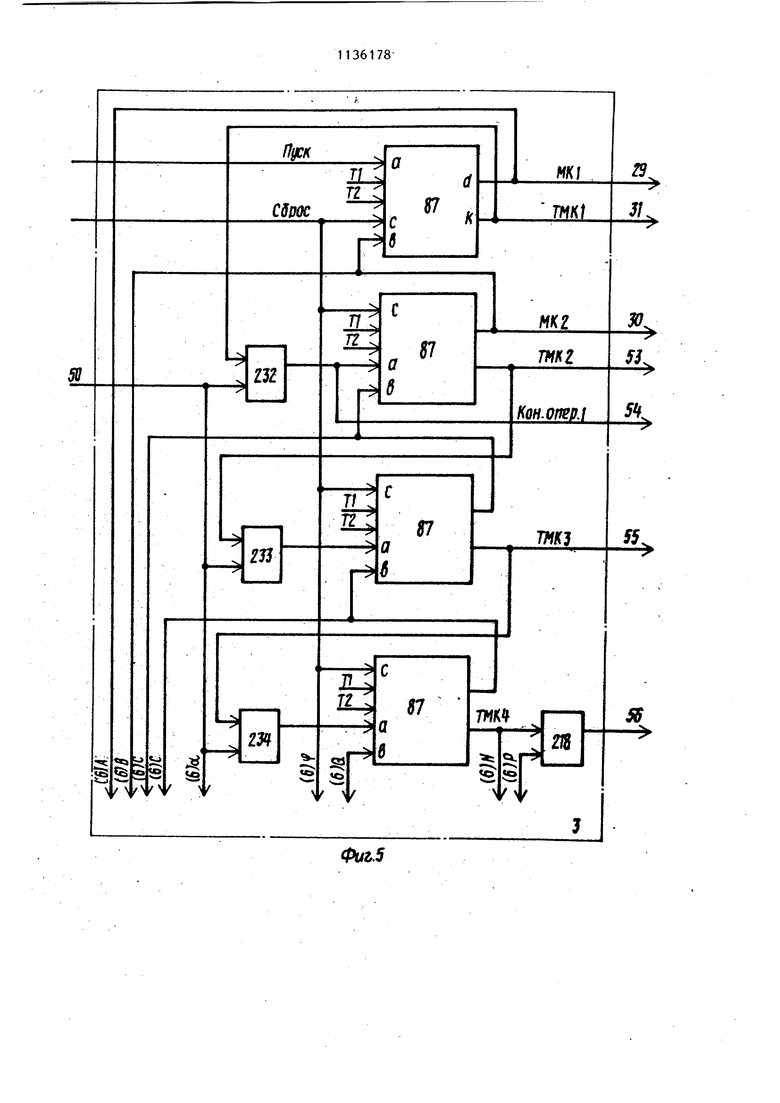

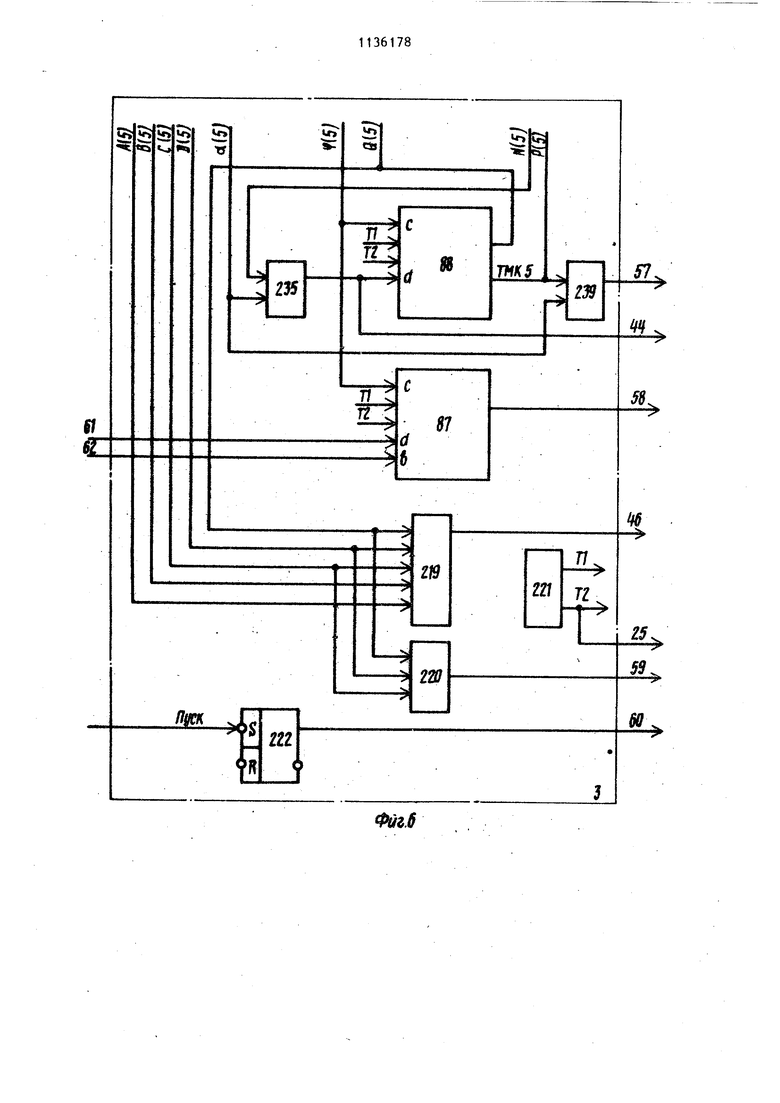

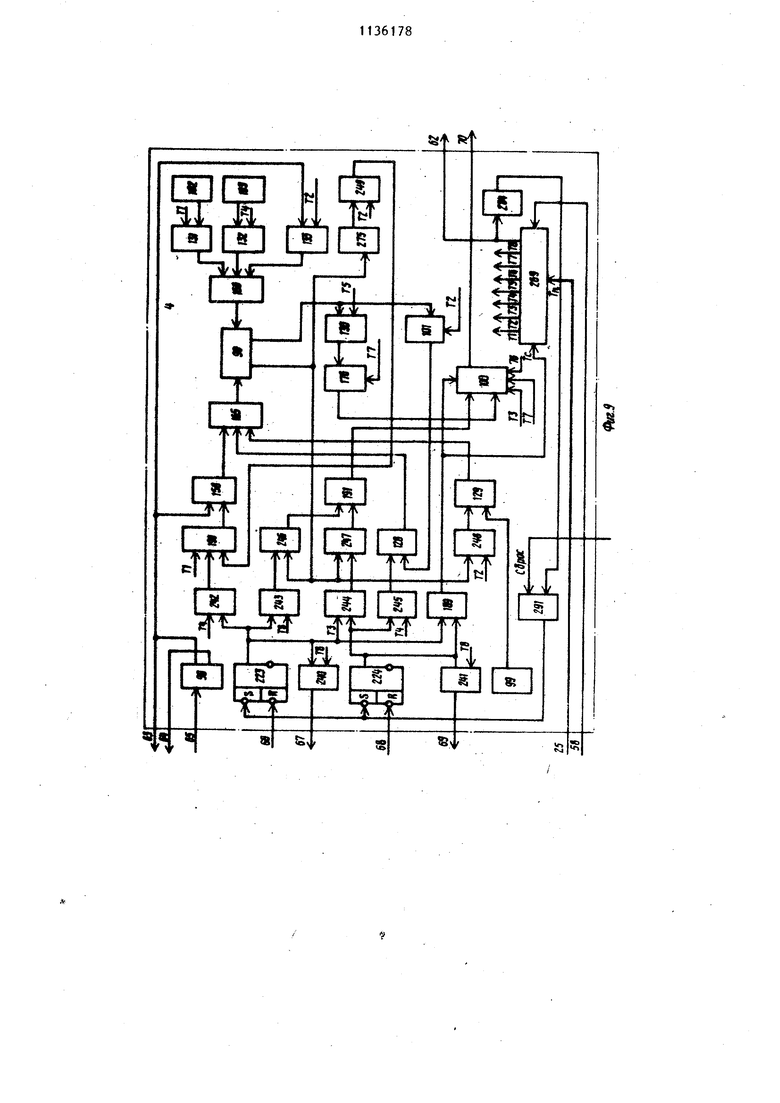

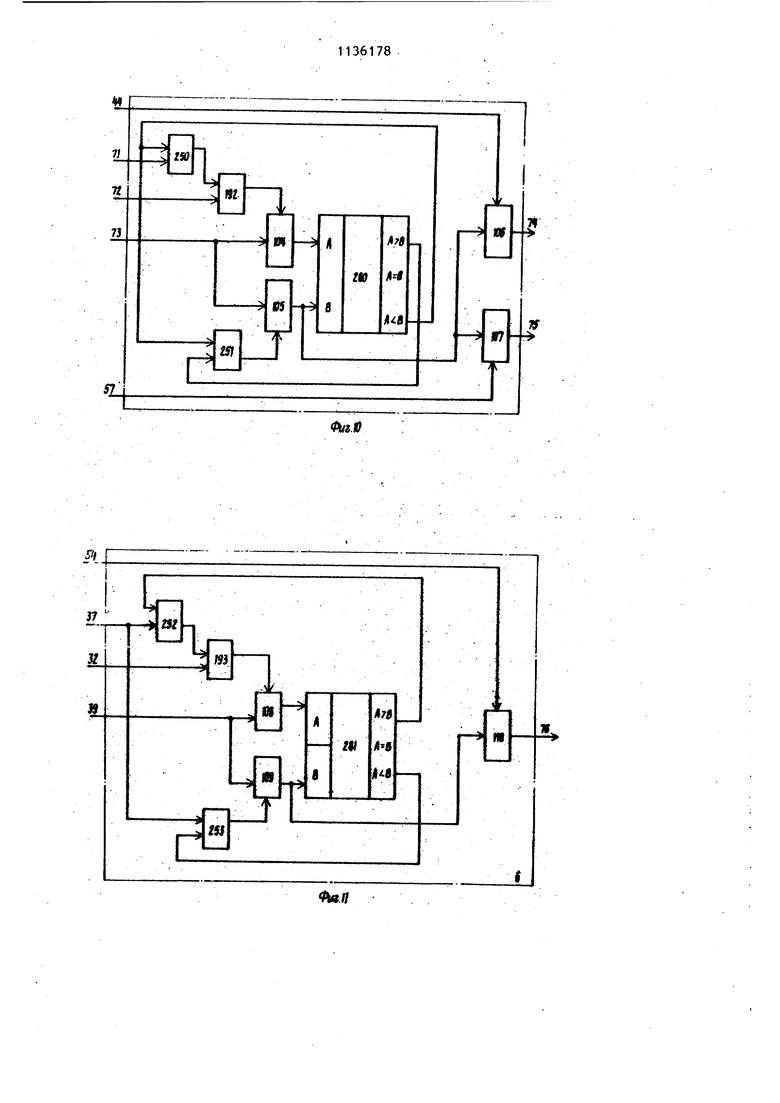

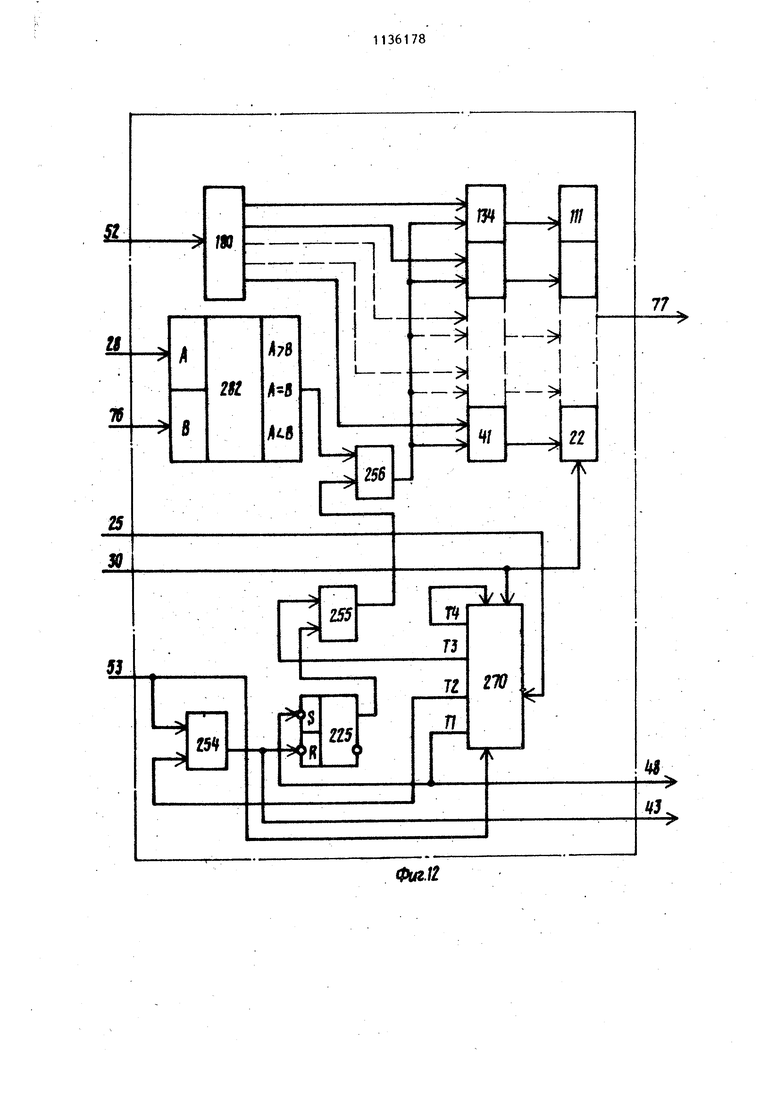

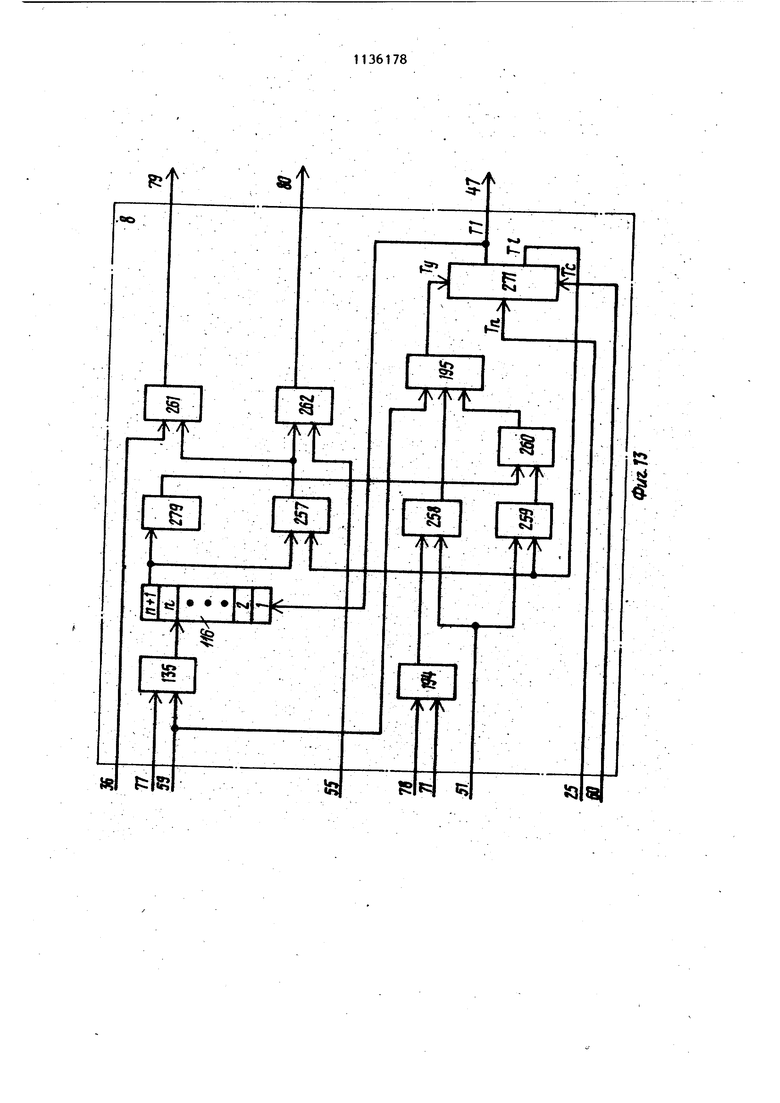

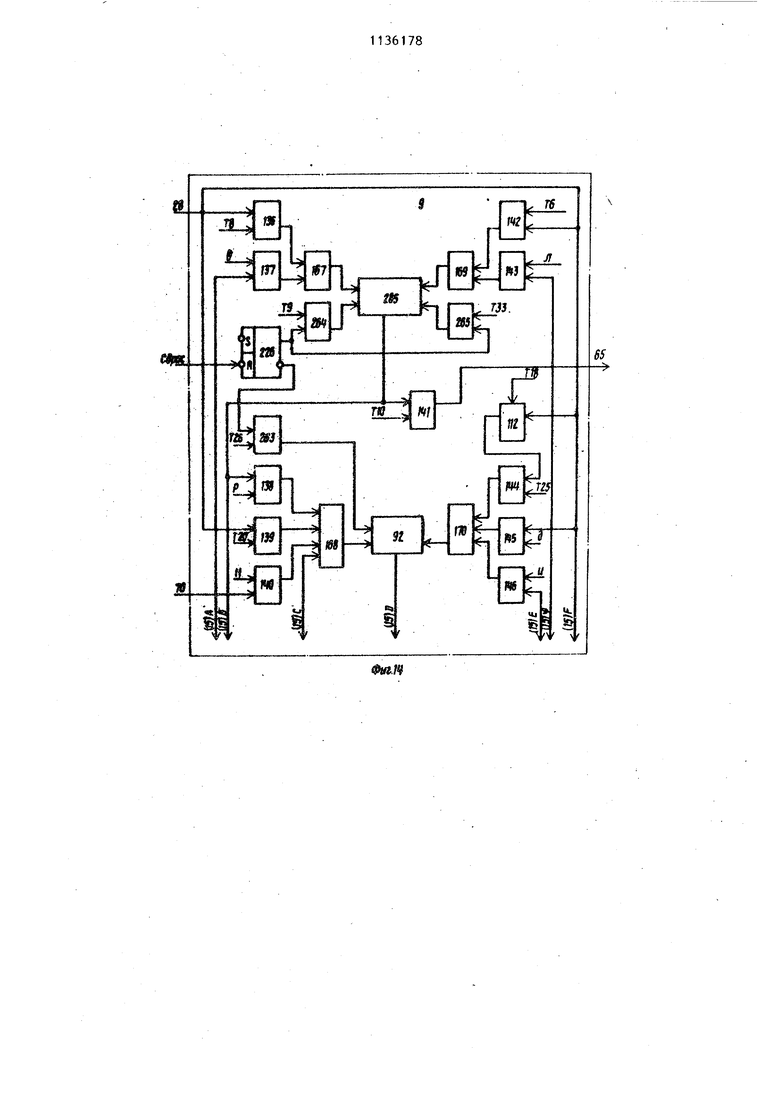

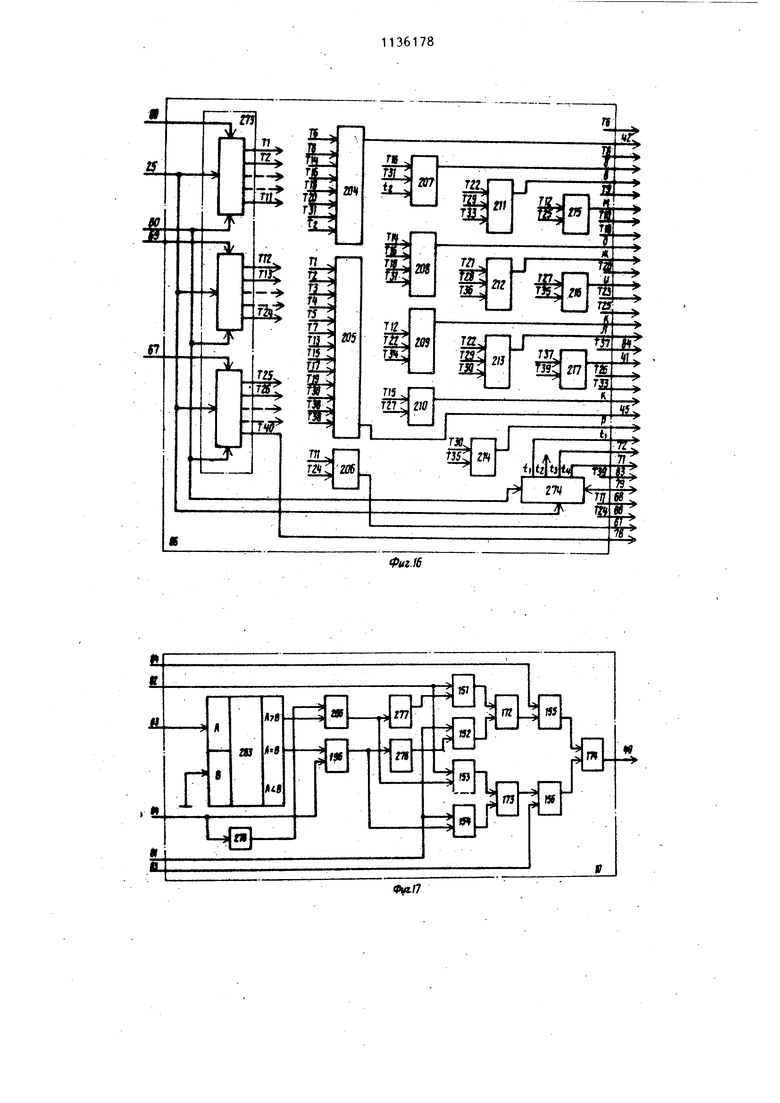

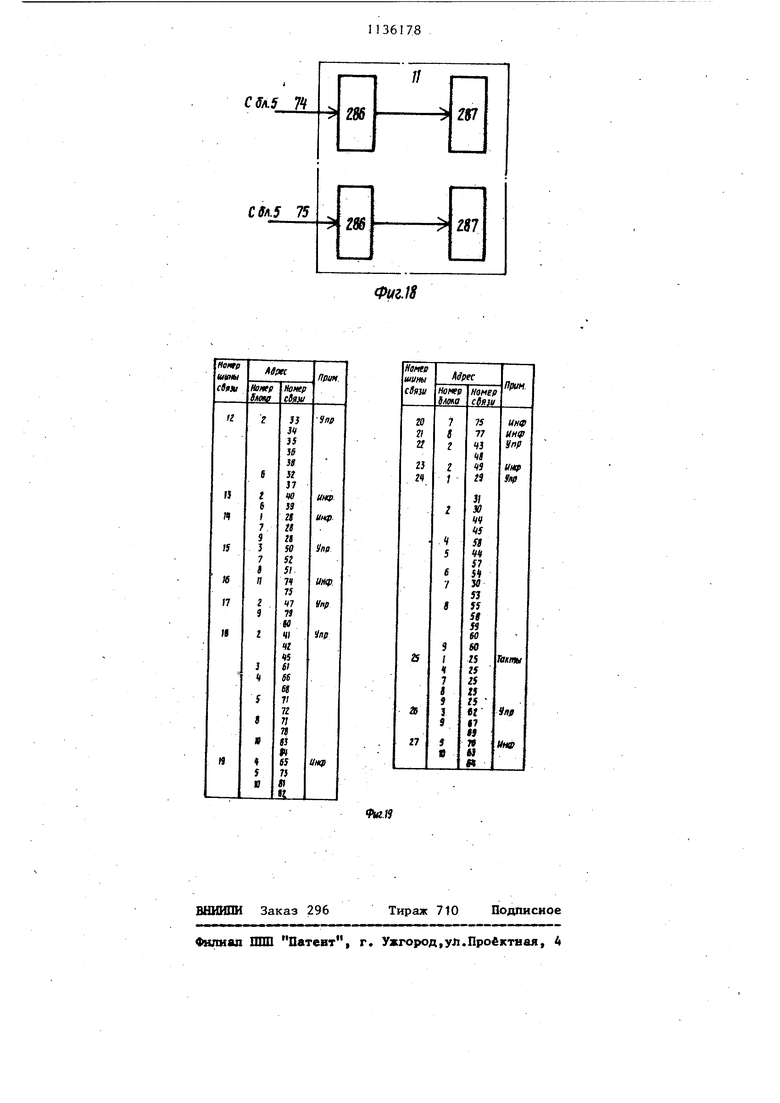

содержит узлы дешифрации команд, элементы ИЛИ, генератор тактовых импульсов, триггер, элементы И-НЕ, .блок тригонометрических преобразований содержит вычитатель,, регистры, группы элементов И, ИЛИ, элементы И, ИЛИ, НЕ, ИЛИ-НЕ, Т1 иггеры, оперативное запоминающее устройство, элемент задержки и распределитель импульсов, блок определения маневра содержит регистры, элементы И, ИЛИ и схему сравнения, блок классификации целей содержит регистры, элементы И, ИЛИ и схему сравнения, блок анализа содержит элементы И, ИЛИ, НЕ,, группу элементов И, сдвиговый регистр и распределитель импульсов, блок индикации опасных судов содержит группу элементов И, элементы И, регистр, триггер, дешифратор, схему сравнения и распределитель импульсов, причем выходы с первого по двадцать пер.вый первого формирователя синхросигналов блока формирования угловых скоростей подключены соответственно к тактовому входу первого .регистра,к первым входам элементов И с первой по девятую группу, установочному входу первого регистра, к первым входам первого, второго элементов И, к первым входам элементов И десятой, одиннадцатой, двенадцатой групп, к тактовому входу второго регистра, к первым входам элементов И, тринадцатой груп пы элементов И, к первому входу третьего элемента Инк первым входа элементов И четьфнадцатой и пятнадца той групп, выходы разрядов первого, второго, третьего и четвертого регистров соединены соответственно с вторьми входами элементов И пятой, десятой, девятой и третьей групп, вы ходы элементов И четырнадцатой и девятой групп подключены к соответству няцим входам элементов ИЛИ первой группы, выходы которых подключены к первому входу сумматора, второй вход которого соединен с выходами элементов ИЛИ второй группы, входы которых соединены с выходами элементов И пят надцатой и третьей групп, нулевой вход первого триггера подключен к установочному входу системы, единичный выход первого триггера соединен . с вторыми входами первого и третьего . элементов И, выходы которых подключе ны соответственно к входам знаковых разрядов сумматора, выход сумматора соединен с вторьп и входами элемен. тов И первой, одиннадцатой и тринадцатой групп, нулевой выход первого триггера соединен с вторым входом второго элемента И, выход которого подключен к входу первого знакового разряда первого умножителя, выходы э лементов И первой, второй, восьмой и двенадцатой групп соединены соответственно с входами элементов ИЛИ третьей группы, выходы которых подключены к первому входу первого умножителя, выходы элементов И пятой, седьмой, десятой групп соединены соответственно с входами элементов ИЛИ четвертой группы, выходы которых соединены с вторым входом первого умножителя, выход первого умножителя подключен к вторым входам элементов И второй, четвертой и шестой групп, выходы элементов И четвертой и одиннадцатой групп соединены соответственно с входами элементов ИЛИ пятой группы, выходы которых подключены к информационному входу третьего регистра, выходы элементов И шестой группы соединены с информационным входом четвертого регистра, причем первый вход первой схемы сравнения блока формирования направления поворота подключен к входу константы системы, первый выход подключен к первому входу четвертого элемента И, второй вход которого соединен с выходом первого элемента НЕ, второй выход первой схемы сравнения подключен к первому входу первого элемента ИЛИ,, выход которого соединен с входом второго элемента НЕ и с первыми входами элементов И шестнадцатой группы, выход четвертого элемента И соединен с входом третьего элемента НЕ и с первыми входами элементов И семнадцатой группы, выход третьего элемента НЕ соединен с первыми входами элементов И восемнадцатой груйпы, выход второго элемента НЕ подключен к первым входам эдементов И девятнадцатой- группы, выходы элементов И восемнадцатой и девятнадцатой групп соединены соответственно с первыми и вторыми входами элементов ИГШ шестой группы, выходы элементов И шестнадцатой и семнадцатой групп соединены соответственно с первыми и вторьп№ входами элементов ИЛИ седьмой группы, выходы элементов ИЛИ шестой и седьмой групп подключены соответственно к первым входам элементов И двенадцатой и двадцать первой групп, входы которых соединены соответственно с первыми и вторыми входамиэлементов ИЛИ восьмой группы, причем выходы второго формирователя синхросигналов блока определ€у1ия времени сближения с первого по двенадцатьм подключены со ответственно к тактовому входу пятог регистра, к первым входам элементов двадцать второй, двадцать третьей и двадцать четвертой групп, к такто.вому входу шестого регистра, к первым входам элементов И двадцать пятой и двадцать шестой групп,к первым входам элементов И двадцать седьмой двадцать восьмой групп, к тактовому входу седьмого регистра, к первым входам элементов И двадцать девятой тридцатой, тридцать первой групп, вторые входы элементов И двадцать второй, двадцать третьей и двадцать восьмой -групп подключены к выходу второго умножителя, выходы элементов И двадцать второй и двадцать пятой групп подключены соответственно к входам элементов ИЛИ девятой группы, выходы которых соединены с входом уменьшаемого первого вьгчитателя вход вычитаемого которого подключен к выходам элементов ИЛИ десятой группы, первые входы которых соединены с выходами элементов И двадцать третьей группы,, выходы элементов И двадцать mecToji группы подключены к вторым входам элементов ИЛИ десятой группы и к первым входам элементов или одиннадцатой группы, вторые входы элементов И двадцать шестой группы подключены к выходам разрядов пятого регистра, первый и второй входы второго умножителя подключены соответветственно к выходам элементов ИЛИ одиннадцатой группы и к выхо дам элементов И двадцать девятой группы, выходы элементов И тридцать первой группы подключены к вторым входам одиннадцатой группы элементов ИЛИ, вькод первого вычитателя подключен к вторым входам элементов И тридцатой группы, выходы которой соединены с первым входом узла деления, второй вход которого подклю чен к выходам элементов ИЛИ двенадца той группы, первые и вторые входы которой подключены к выходам-элементов И двадцать восьмой и двадцать четвертой групп соответственно,выход узла деления соединен с информационными входами шестого и седьмого регистров, выходы разрядов шестого регистра подключены к вторым входам двадцать седьмой группы элементов И, выходы которой соединены с первыми входами элементов ИЛИ тринадцатой группы, вторые входы которой соединены с выходами разрядов седьмого регистра, выходы элементов ИЛИ с второго по шестой подключены соответственно к входу управления считьшанием первого оперативного запоминающего устройства блока памяти исходных данных, к информационному входу первого реверсивного счетчика, к входу вычитания второго реверсивного счетчика, к входу управления записью первого оперативного запоминающего устройства, к входу суммирования первого реверсивного счетчика, выходы разрядов первого и второго реверсивных счетчиков подключены соответственно к входам первого и второго дешифраторов, выходы которых соединены соответственно с младшей и старшей группами адресных разрядов первого оперативного запоминающего устройства, выходы разрядов второго реверсивного счетчика подключены к входу третьего дешифратора, выходы которого соединены с ,входами седьмого элемента ИЛИ, информационный вход второго реверсивного счетчика подключен к выходам элементов И тридцать второй группы, первые входы котЪрой соединены с выходами разрядов восьмого регистра, выходы элементов ИЛИ четырнадцатой группы соединены с информационным входом первого оперативного запоминающего устройства, причем первый и второй тактовые входы с первого по шестой узлов дешифрации команд блока управления подключены соответственно к первому и второму выходам генератора тактовых импульсов, входы пуска с второго по пятый узлов дешифрации комавд подключены соответственно к выходам первого, второго, третьего и- четвертого элементов И-НЕ, вход пуска первого узла дешифрации команд и единичный вход первого триггера соединены с входом пуска системы, установочные входы с первого по шестой узлов дешифрации команд соединены с установочным входом системы, первые выходы узлов дешифрации команд с первого по пятьм подключены соответственно к входам восьмого элемена ИЛИ, первые выходы узлов дешифраии команд с второго по пятый- подлючены соответстренно к входам установки исходного состояния узлов деифрации команд с первого по четверьй, первые вьЛоды узлов дешифрации 71 команд с третьего по пятьй соединены соответственно с входами девятого элемента ИЛИ, вторые выходы узлов дешифрации команд с первого по четвертый подключены к первым входам элементов И-НЕ с первого по четвертый соответственно, вторые входы чет вертого и пятого узлов дешифрации ко манд подключены соответственно к пер вому и второму входам десятого эле- мента ИЛИ, второй выход пятого узла дешифрации команд подключен к первом входу пятого элемента И, йричем выходы с первого по восьмой первого распределителя импульсов блока триго нометрических преобразований подключены соответственно к первым входам одиннадцатого элемента ИЛИ и первым входам элементов И тридцать третьей группы, к первым входам тридцать чет вертой группы элементов И, к первым входам шестого и седьмого элементов И и к тактовому входу девятого регистра, к первому входу восьмого элемента Инк первому тактовому входу десятого регистра, к первым входам элементов И тридцать пятой группы и к первым входам девятого и десятого элементов И, к первым входам элементов И тридцать шестой группы, к первому входу одиннадцатого элемен та И, к входу считывания второго опе ративного запоминающего устройства,, к второму тактовому входу десятого регистра, к первым входам двенадцато го и тринадцатого элементов И и к входу элемента задержки, выход которого соединен с первым входом первого элемента ИЛИ-НЕ, второй вход которого соединен с установочным вхо дом системы, а выход подключен к нулевым входам второго и третьего триг геров, единичньй выход второго триггера подключен к вторым входам девятого, одиннадцатого и двенадцатого элементов Ник первому входу двенадцатого элемента ИЛИ, единичньй выход третьего триггера подключен к вторым входам восьмого, десятого и тринадцатого элементов И и двенадца того элемента ИЛИ, выход девятого элемента И соединен с вторым входом одиннадцатого элемента ИЛИ, третий вход которого соединен с выходом седьмого элемента И, а выход - с пе выми входами элементов И тридцать седьмой группы, выходы которой соед нены с первыми входами элементов ИЛ пятнадцатой группы, вторые и третьи входы которой подключены соответственно к выходам элементов И тридцать: восьмой и тридцать девятой групп, выходы элементов ИЛИ пятнадцатой группы подключены к входу вычитаемого второго вычитателя, «ход уменьшаемого которого соединен с выходами элементов ИЛИ шестнадцатой группы, входы которой подключены к выходам элементов И тридцать третьей, тридцать четвертой и тридцать пятой групп соответственно, вторые входы элементов И тридцать третьей и тридцать пятой групп соединены с выходами разрядов одиннадцатого и двенадцатого регистров соответственно, вторые входы элементов И тридцать четвертой и тридцать седьмой группподключены к выходу группы разрядов модуля числа тринадцатого регистра, , вькод модуля результата второго вычитателя подключен к вторым входа:м элементов И тридцать шестой группы и к информационному входу девятого регистра, знаковьй выход результата второго вычитателя соединен с первыми входами четырнадцатого и пятнадцатого элементов И, с вторым входом шестого элемента И и с входом четвертого элемента НЕ, выход, которого подключен к второму входу седьмого элемента И, выходы одиннадцатого, восьмого и десятого элементов И подключены соответственно к вторым входам четырнадцатого и пятнадцатого элементов И и к первым входам элементов И тридцать восьмой группы, вторые входы которой соединены с выходами разрядов девятого регистра выходы четырнадцатого и пятнадцатого элементов И соединеныс первым и вторым входами тринадцатого элемента ИЛИ соответственно, а выход подключен к входу знакового разряда десятого регистра, информационньй вход которого соединен с выходом второго оперативного запоминающего устройства, адресньй вход которого соединен с выходами элементов И тридцать шестой группы, выход двенадцатого элемента ИЛИ подключен к входу начальной установки девятого регистра и к входу сброса первого распределителя импульсов, выход шестого элемента И соединен с первыми входами элементов И тридцать девятой группы, вторые :входы которой соединены с выходами разрядов четырнадцатого регистра, причем первьй и второй входы второй cxehn сравнения блока определения маневра подключены соответственно к выходам разрядов пятнадцатого и шестнадцатого регистров, вьпсоды раз рядов шестнадцатого регистра соединены с информационными входами семнадцатого и восемнадцатого регистров тактовые входы пятнадца того и шестнадцатого регистров подключены к вы ходам четырнадцатого элемента ИЛИ и шестнадиатого элемента И соответственно, первый выход второй схемы сравнения подключен к первому входу семнадцатого элеме-нта И, выход которого соединен с первым входом четырнадцатого элемента ИЛИ, второй выход схемы сравнения подключен к первому входу шестнадцатого элемен4та И, причем тактовые входы девятнадцатого и двадцатого регистров бл ка классификации целей подключены к выходам пятнадцатого элемента ИЛИ и восемнадцатого элемента И соответст венно, выходы разрядов соединены со ответственно с первым и вторым вход ми третьей схемы сравнения, выходы разрядов двадцатого регистра подклю чены к информационному входу двадца первого регистра, первьм выход третьей схемы сравнения подключен к пе вому входу девятнадцатого элемента выход которого соединен с первым входом пятнадцатого элемента ИЛИ, второй выход третьей схемы сравнени подключен к первому входу восемнадцатого элемента И, причем первьш и второй выходы второго распределител импульсов блока анализа подключены соответственно к управляющему входу сдвигового регистра и к первым входам двадцатого и двадцать первого элементов И, вход запуска второго распределителя импульсов подключен выходу.шестнадцатого элемента ИЛИ, первьш и второй входы которого соединены с выходами двадцать второго двадцать третьего элементов И соот;ветственно, первый и второй входы двадцать третьего элемента И подключены к выходу двадцать первого элемента И и пятого элемента НЕ соответственно, информадионный вход сдви гового регистра подключен к выходам Элементов li сороковой группы, выход, старшего разряда сдвигового регистр соединен с вторым входом двадцатого элемента И и с входом пятого элемента НЕ, выход двадцатого элемента И подключен к первым входам двад цать четвертого и двадцать пятого элементов И, причем выходы с первого по четвертьй третьего распределителя импульсов блока индикации опасных судов подключены соответственно к нулевому входу четвертого регистра, к первым входам двадцать шестого элемента И, двадцать седьмого элемента И и к первому входу запуска третьего распределителя импульсов, выход первого элемента И подключен к единичному входу четвертого тр иггера, единичный выход которого соединен с вторым входом двадцать седьмого элемента И, выход которого соединен с первым входом двадцать восьмого элемента И, второй вход которого подключен к выходу четвертой схемы сравнения, а выход - к первым входам элементов И сорок первой группы, вторые входы которых соединены с соответствующими выходами четвертого дешифратора, выходы элементов И сорок первой- группы подключены к информационному входу двадцать второго регистра, выходы с тринадцатого по девятнадцатый второго формирователя синхросигналов подключены соответственно к первому входу четвертого элемента ИЛИ, к второму входу пятнадцатого элемента ИЛИ, к первому входу пятого элемента ИЛИ, к первому входу третьего элемента ИЛИ, к первому входу шестого элемента ИЛИ, к первому входу второго элемента ИЛИ, к вторым входам восемнадцатого и девятнадцатого элементов И, выходы разрядов седьмого регистра подключены соответственно к входам разрядов девятнадцатого и двадцатого регистров, выходы элементов ИЛИ тринадцатой группы подключены к первым входам элементрв ИЛИ четырнадцатой группы, информационный выход первого оперативного запоминакяцего устройства подключен к вторым входам элементов И, двадцать пятой, двадцать девятой и тридцать первой групп, к информационному входу пятого регистра, к первому входу четвертой схемы сравнения, к вторым входам элементов И седьмой, двенадцатой, четырнадцатой и пятнадцатой групп, к информационным входам первого и второго регистров, выход переноса второго реверсивного счетчика соединен с §торыми входами первого, второго, третьего и четвертого элементов И-НЕ, выход седьмого элемента ИЛИ подключен к вторым входам двадцать первого и двадцать второго элементов И, выходы разрядов второго реверсивного счетчика подключены соответственно к входам четвертого дешифратора, первый выход первого узла дешифратора команд соединен с установочным входом ti bMorq,.регистра и с входом запуска второго фop в poвaтeля синхросигналов, второй выход подключен к установочному входу второго формирователя синхросигналов, второй выход второго узла дешифрации команд соединен с вторьм входом двадцать шестого элемента И и с установочным входом третьего распределителя импульсов, второй вход запуска которого и вход начальной установки двадцать второго регистра соединены с первьм выходом второго узла дешифрации команд, выход первого элемента И-НЕ подклю ён к тактовому входу двадцать первого регистра, второй выход третьего узла дешифрации команд подключен к второму входу двадцать пятого элемента И, выход десятого элемента ИЛИ соединен с вторым входом двадцать четвертого элемента И, выход пятого элемента И подключен к тактовому входу восемнадцатого регистра, тактовый вход семнадцатого регистра и вычитающий вход первого реверсивного счетчика соединены с выходом четвертого элемента И-НЕ, выход шестого узла дешифрации команд соединен с входом запуска первого распределителя импульсов, выход восьмого элемента ИЛИ Соединен с вторыми входами элементов И тридцать второй группы, выход девятого элемента ШШ подключен к первым входам элементов И соро ковой группы и к третьему входу шест надцатого элемента ИЛИ, выход пятого Т1 иггера соединен с установочными входамивторого распределителя импульсов и первого формирователя, синх росигналов, нулевой вход пятого триггера подключен к входу пуска системы, второй выход генератора так товых импульсов соединен с тактовыми входами первого и второго формирователей синхросигналов, первого, второ го и третьего распределителей импуль сов, восьмой ВьЬсод первого распреде лителя импульсов подключен к входу лустановки исходного состояния шестого узла дешифрации команд, выходы разрядов десятого регистра соединены с вторым входом восьмой группы элементов И, выходы разрядов тринадцатого регистра подключены к второму входу первой схемы сравнения, к второму входу первого элемента ИЛИ и к входу первого элемента НЕ, выход двенадцатого элемента И соединен с первьм входом первого формирователя синхросигналов, второй вход которого соединен с выходом тринадцатого элемента И, выходы разрядов семнадцатого и восемнадцатого регистров соединены соответственно .с входами блока индикации, выходы разрядов двадцать первого регистра соединены с вторым входом четвертой схемы сравнения, выхо-: ды разрядов двадцать второго регистра соединены с вторыми входами элементов И сороковой группы, первый выход третьего распределителя импульсов подключен к второму входу четвертого элемента ИЛИ, выход двадцать шестогю элемента И соедине«с вторым входом второго элемента ИЛИ, выходы двадцать четвертого и двадцать пятого элементов И соединены соответственно с третьим и четвертым входами первого формирователя синхросигналов, первьй выход второго распределителя импульсов подключен к третьему входу четвертого элемента ИЖ, выходы элементов И тринадцатой группы соединены с информационным входом тринадцатого регистра, выходы разрядов первого регистра подключены соответственно к входам разрядов пятнадцатого и шестнадцатого регистров,выходы разрядов четвертого регистра соединены с вторыми входами элементов И шестнадцатой и девятнадцатой групп, выходы разрядов третьего регистра соединены с вторьми входами элементов И, семнадцатой и восемнадцатой групп, выходы первого формирователя синхросигналов.с двадцать второго по тридцать второй соединены соответственно с единичньми входами второго третьего триггеров, с первым вхоом семнадцатого элемента ИЛИ, выход оторого подключен к первому входу вадцать второго элемента И, к втоому входу пятого элемента ИЛИ, к ретьему входу второго элемента ИЛИ, к второму входу шестого элемента ИЛИ, к второму входу четьф надцатого эле1311мента ИЛИ, к вторым входам шестнадца того, семнадцатого элементов Ник второму входу семнадцатого элемента ИЛИ, к входу пуска шестого узла дешифрации команд, к вторым входам элементов И двадцать первой группы и к вторым входам элементов И двадца той группы, выходы элементов ИЛИ восьмой группы соединены с вторыми входами элементов ИЛИ четырнадцатой группы. На фиг.1 представлена блок-схема системы на фиг,2 - схема блока опре деления времени сближения; на фиг.З схема устройства формирования синхро сигналов; на фиг.4 - схема блока памяти исходных данных; на фиг.З и 6 схема блока управления; на фиг.7 и 8 - схемы узлов дешифрации команду на фиг.9 - схема блока тригонометрических преобразований; на фиг.10 схема блока определения маневра; на фиг.11 - схема блока классификации целей; на фиг.12 - схема блока индинации опасных судов; на фиг.13-- схе ма блока анализа; на фиг.14 и 15 схема блока формирования угловых ско ростей; на фиг.16 - схема устройства формирования синхросигналов блокад формирования угловых скоростей; на фиг.17 - схема блока формирования направления поворота-, на фиг. 18схема блока индикации; на фиг.19 таблица межблочных связей системы. Вычислительная система содержит блок 1 определения времени сближе.ния, блок 2 памяти исходных данных, блок 3 управления, блок- 4 тригонометрических преобразований, блок 5 определения маневра, блок 6 классифи кации целей, блок 7 индикации опасных судов, блок 8 анализа, блок 9 формирования угловых скоростей, блок 10 формирования направления поворота блок 11 индикации, шины 12-27 связи, цепи 28-84 связи, первый и второй 85 и 86 формирователи синхросигналов, узлы 87 и 88 дешифрации команд, выг читатели 89 и 90, умножитель 91 и 92, узел 93 деления, регистры 94 и 95, элемент ШШ 96, регистры 97-115, сдвиговьй регистр 116, группы элементов И 117-158, группы элементов ИЛИ .159-174, оперативные 9апоьшнакхциё устройства (ОЗУ) 175 и 176, дешифраторы 1-77-180, реверсивные ;счетчики 181 и 182, элементы ИЛИ 183220, генератор 221 тактовых импульсов, триггеры 222-231,. элементы И-НЕ 232-237, элементы И 238-268, распределители 269-274 импульсов, элементы НЕ 275-279, схемы 280-283 сравнения, элемент.284 задержки, сумматор 285, группа дешифраторов 286, индикатор 287,элементы ШШ НЕ 288-291 . Распределители 269-274 выполнены на однотактных кольцевых регистрах. Запуск распределителя осуществляется путем установки его старшего разряда в единицу установочным импульсом . На выходах последовательно формируются импульсы, длительность которых равна длительности тактового импульса Т. Адресный вызов канала распределителя в схеме не используется. Сброс распределителя в исходное состояние осуществляется сигналом сброса . До начала работы системы в ОЗУ 175 блока 2 записывается информация о параметрах собственного судна таких, как У„ и ИК - скорость и курс; служебная информация: Ддоп допустимый радиус безопасност и константа 2, ut - интервал времени наблюдения за встречными судами , а также информация о встречных судах; Доп и Д дотHocyiTельные дальности до п-го встречного судна в первый момент наблюдения и через интервал времени dt соответственно, ИПо - пеленг встречного судна через интервал времени dt, Уц - скорость встречного судна. Адресация ОЗУ по параметрам приведена в таблице. Д - относительная дальность до встреч ного судна через интервал времени (,2, . ..N) Д. допустимьй радиус безопаснос ти Константа 2 Я - относительна дальность до встречного судна в момент времени .at - интервал вре мени наблюдения з устр.ечными суднан ИП - пеленг встр ного судна через интервал времени ИК - курс собственного судна V - скорость встречного судна Дл - (см.нулевой адрес параметра) V - скорость соб ственного судна Д - (см. первы адрес параметра) Кроме того, в регистр 97 заноси ся количество встречных судов. N+1; в регистры 99, 102, 103 - числа 27 90, 180 соответственно, все разряд регистров 104 и 105 устанавливаютс в нулевое, а регистров 108 и 109 единичное состояние. Работа системы начинается с приходом сигнала Сброс, которым устанавливаются в нулевое состояние триггеры 228 и 229 узла 87, 230, 231i узла 88, 223, 224 блока 4 и в единичное - триггер 226 блока 9„ Последовательность работы блоков системы определяется блоком 3 управления, С приходом импульса Пуск блоком 3 формируется управлякящий сигнал МК1, которым запускается блок 1 определения времени сближения Блоком 1 в совокупности с блоками 2 и 6 .Системы рассчитывается время сближения собственного судна с каждым из встречных судов и определяется минимальное его значение. По окончании этой операции на блок 3 управления по цепи связи 50 поступает ответный импульс, по которому формируется комацца конца первой операции Кон. опёр.1. Этой командой в блоке 3 форьвфуется управляняций сигнал МК2 на блоки 2 и 7 системь. Признаком окончания работы этих блоков служит команда Кон.опер.2 на выходе элемента И-НЕ 233 блока 3, Аналогичным образом синхронизируется работа остальных блоков системы Первая группа управляющих сигналов МК1-Ж5 формируется узлами 87 и 88. РЫпульсом сброса по входу С триггеры 228-231 устанавливаются в иулевое состояние (фиг.7 и 8). Импульсом по входу « триггеры 22В к 230 - в.единичное состояние. На такте Т 1 серии тактовых импульсов, задаваемых генератором 221 тактовых импульсов, вырабатываются сигналы ЬВ(1-МК5 ,(выход 0 узлов 87, 88). На этом же такте триггеры 268 и 231 устанавливаются в единичное состояние. Этим вьфабатывается вторая, группа управляющх сигналов ТМК1-ТЖЗ (выход Л ) узлов 87 и 88. На такте Т2 триггеры 228 и 230 возвршцаются в исходное состояние. Отличие между узлами 87 и 88 в том, что,в первом из них (фиг.7) управляющими сигналами МК2-МК5 по входу Ъ триггер 229 устанавливается в исходное нулевое состояние. В узле 88 триггер 231 остается в единичном состоянии в течение всего времени работы системы, т.е. до прихода следующего импульса Сброс. Последовательности тактовых импульсов Т1, Т2, вырабатываемые гене( 17.11 ратором 221 тактовых импульсов, сдви нуты относительно друг друга по времени. Тактовым импульсом -из серии Т1 производится запуск распределителей 269-274 системь. Импульсы серии Т2 являются тактирующими для распредели телей . Первоначальный запуск блока 3 управления осуществляется по входу узла 87 внешним импульсом Пуск, Последующие запуски блока 3 производятся также по входу а узЛов 87 и 88 сигналами конца операции. Триггер 222 блока 3 управления предназначен для. организации требуе.мого режима работы распределителей .блоков 8 и 9 системы. Рабочее состоя ние триггера 222 - низкий уровень по тенциала на его единичном выходе, устанавливается триггер в нулевое состояние импульсом Пуск. Функционирование блоков 1,2,6 сле дующее. Управляющим сигналом МК1 по цепи связи 29 с блока 3 в блоке 1 устанавливаются все разряды регистра 94 в единичное состояние, запускается распределитель 272 формирователя 85: по цепи связи 46 содержимое регистра 97 переписывается в счетчик 182 блока 2 системы, кроме того, сигналом МК1 по цепи связи 34 формироват я 85 в блоке 2 устанавливается в нуль счетчик 181. По связи 31 сигналом из блока 3 управления замыкается цеп обратной связи распределителя 272 формирователя 85 и тем самым обеспечивается его работа в режиме кольцевого распределителя. Триггер 227 и элемент И 267 формирователя 85 обес- иечивают формирование тактирующих импульсов ТЗ-Т21 при содержимом счет чика 182 блока 2, отличном от нуля. Счетчик 181 блока 2 содержит информацию о номере одного из параметров движения встречного и собственно го судов (таблица) .Содерлсимое счетчи ка 181 определяет адреса младпшх раз рядов ОЗУ 175. Счетчик 182 содержит информацию о порядковом номере рассматриваемых встречных судов и содержимое счетчика определяет адрес старших разрядов ОЗУ 175. Синхронизация работы блоков 1,2,6 системы осуществляется формирователем 85. На такте Т1 содержимое счетчика 182 блока 2 уменьшается на единицу. На такте Т2 из ОЗУ 175 считывается 818 параметр движения Д- (таблица). Импульс считывания информации из ОЗУ .175 поступает в блок 2 по цепи связи 36 из формирователя 85. Адрес параметра Д определяется содержимым счетчиков 181 и 182. На этом же такте значение параметра Д переписьгаается в регистр 95 блока 1, а также поступает на оба входа умножителя 91. В передаче кода Дг участвуют группы элементов И 119, 123, ИЛИ 160 блока 1 и элементы ИЛИ 199, 201 формирователя 85. На такте ТЗ в счетчике 181 устанавливается код, соответствукщий номеру параметра (таблица). Тактирующий импульс ТЗ поступает на суммирующий вход счетчика 181 по цепи: элемент ИЛИ 197 и элемент 1.87 блока 2. По этой же цепи поступают тактовые импульсы Т5, Т7, Т9, Т11-Т17, каждый раз увеличивая содержимое счетчика 181 на единицу, тем самым осуществляется перебор параметров движения, отображенных таблицей для последнего из числа рассматриваемых встречных судов. Тактом ТЗ также осуществляется занесение результата умножения - Д квадрата величины ОТ7 носительной дальности с выхода умножителя 91 на вход уменьшаемого вычитателя 89 по цепи: группы элементов И 118, ИЛИ 159. На такте Т4 из ;ОЗУ 175 считывается код параметра Д и передается на оба входа умножителя :91. На такте Т5 изменяется содержимое счетчика 181 блока 2, результат умножения - Ддд 2 квадрат допустимого радиуса сближения - с выхода умножителя 91 через группы элементов И 121 и ИЛИ 161 поступает на вход вычитаемого вычитателя 89. На такте Тб из ОЗУ 175 считывается константа и ее значение-через группы элементов И 125, ИЛИ 162 заносится на вход делимого делителя 93. На вход делителя поступает результат вычитания величин Д вычитателя 89 через группы элементов И 120. На такте Т7 результат деления заносится в регистр 96 и в ОЗУ 175 устанавливается адрес, соответствукщий выборке параметра Д относительной дгшьности до встречного судна в момент времени t,.На такте Т8 код параметра Д считьщается из ОЗУ 175 и передается через группы элементов И 117, 159 ИЛИ на вход уменьшаемого вьпштателя 89, а на его ругой вход и регистра 95 поступает код параметра Д,. Результат вычитания . на такте Т9 передается на вход делителя 93. Этим же тактом измеияется содержимое счетчика 181 на единицу и в ием фиксируется код, соответствующий адресу параметра ut интервалу. наблкщения за встречньАш судами. Тактом Т10 код па paMerpa t считывается из ОЗУ 175 и через группы элементов И 123 постуиа ет на уинсяштель 91. НА тактах Т11-Т17. происходит толь ко изменения адреса ОЗУ 175 за счет увеличения содержимого счетчика 181. Тактом содержимое регистра 96 заносится в ОЗУ 175 по адресу, установленнсму на предьщущем такте. Пере дача кода из регистра 96 происходит йо цепи; группа элементов И 126, НТО 163 и группа элементов ИЛИ 164 блока 2. Разрешение на запись информации в ОЗУ 175 поступает с элемента ИЛИ 186 блока 2. Результат умножения значений пара метров Д , At на такте Т19 передает ся на вход делителя 93 по цепи из группы элементов И .124 и ШШ 162. На этан же такте счетчик 181 импульсом через элемент ШШ 200 и ИЛИ 184 уста навливается в нулевое полшсение. На такте Т20 результат деления - рассчи танное ( 1 время сближения (( с последним из рассматриваеьО|Вс встречных судов - передается в регистр 94, а на тдкте Т21 переписывается в ОЗУ t75 на прежнее место параметра Д относительной дальности до встречного сукна (таблица). Кроме того, на такте Т21 содержимое регистра 94 переписывается в регистр 108 блока 6. Передача информации производится по цепи связи ,39, а импульс, тактиРУ10НР1Й запись, - по цепи связи 32. Яа этом же такте Т21 начинает фун кционировать блок 6 системы, которым определяется минимальное время сближения собственного судна с N встречными супами. Поскольку все разряды регистра 109 блока 6 предварительно были установлены в 1, то на соответствунцем выходе схемы 281 сравнения будет потенциал высокого уровня. Это приведет к тому, что на такте Т2 импульсом по связи 37 через элемент И 253 в регистр 109 будет пе решгсано содержимое регистра 94. В последующем при сравнении между собой времени сближения 1 с другими 11 20 встречными судами возможны варианты, когда , 7 . В ЭТОМ случае высокий потенциал формируется на другом выходе схемы 281 сравнения. При этом на такте Т22 при работе системы с п-м встречным судном в регистре 109 останется прежнее значение как минимальное с Тактом Т22 распределитель 272 формирователя 85 блока 1 запускается вновь и процесс расчета времени сбли жения собственного судна с оставшшда ся встречньо 1И судами повторяется до тех пор, пока счетчик 182 не обнулится. В этом случае по сигналу со счет11ика 182 (цепь связи 50) на блок 3 управления последним формируется комавда конца первой операции (Кои. опер.1). Этой командой (цепь связи 54) в регистре 110 блока 6 фиксируется минимальное время сближения среди всех рассчитанных значений для встречных судов. Управляющим сигнйлом МК2, формируемым после прихода импульса Кон.опер.1, прекращается действие упрйвлянидего сигнала ТЖ1 на выходе узла 87 блока 3 управления, что приводит к останову распределителя 272. Таким образом, произведена классификация встречных судов по степени опасности. Критерием опасности выбрано минимальное время сближения судов. В соответствии с выбранным критерием опасности -. блоками 2 и 7 систеьвы производится индикация опасных судов из всей рассматриваемой совокупности встречных судов. Управляющим сигналом МК2 с блока 3 управления все разряды регистра tit блока 7 устанавливается в нулевое положение, счетчик 181 блока 2 устанавливается в нуль, в счетчик 182 параллельным кодом заносится информация с регистра 97 и производится запуск распределителя 270 блока 7. На такте Т1 этого распределителя в счетчике 182 блока 2 устанавливается код, соответствунмций числу рассматриваемых :встречных судов. Сигналом ТЖ2, формируемым блоком 3, устанавливается требуемый режим работы распределителя 270. Последним синхронизируется работа блоков 2 и 7 всей системы. Принцип работы блока 7 основан на том, что сопоставляется рассчитанное время сближения каждого из встречных судов с минимальным значением и в случае совпадения этих значений осуществляется маркировка встречного судна как опасного. Производится это следующим образом. На вход схемы 282 сравнения блока 7 поступают поочередно коды „ для. каждого из встречных судов, считываемые из ОЗУ 175 блока 2. На другом входе схемы 282 сравнения установлен код минимальногозначения . Де- (Шифратором 180 блока 7 дешифрируются номера встречных судов. Информация на вход дешифратора 180 поступает по цепи 52 связи со счетчика 182 блока 2. Таким образом, при производится запись 1 в тот разряд регистра 111, которьй соответствует номеру встречного судна. При этом на такте Т1 триггер 225 сбрасывается в нулевое состояние; на такте Т2 считывается код из ОЗУ 175 и поступает на схему сравнения 282, а также устанавливается триггер 225 в единицу. Импульс установки триггера 225 в единицу поступает с выхода элемента И 254. На такте ТЗ формируется высокий потенциал на входе элемента И 256, разрешающий запись 1 в соответствующий разряд регистра 111. Группа элементов И 134 служит маской для p.pгистра 111. Тактом Т4 распределитель 270 запускается вновь. Тем самым продолжается анализ информации об остальных встречных судах и осуществляется маркирование тех судов, которые представляют опасность для собственного судна по времени сбл шеиия с последними. Процесс продолжается до iтех пор, пока счетчик 182 блока 2 не обнулится. В этом случае блоком 3 управления формируется команда МКЗ,которой прекращается действие сигнала ТМК2, что приводит к прерыванию заданного режима работы распределителя 270 блока 7. При этом в регистре 111 содержится информация о номерах встречных судов, представляклдих равную опасность для собственного судна Управлякйцим сигналом МКЗ с блока 3 по цепи связи 59 производится перепись информации о номерах опасных встречных судов с регистра lit блока 7 в регистр 116 блока 8 и осуществляется запуск распределителя 27Т. Епоками 8 и 9 системы производится расчет угловых скоростей собственного судна при его маневрировании с целью расхождения с каждым из опасных встречных супов. В блоке 8 на такте Т1 осуществляется .сдвиг содержимого регистра 116 в сторону старшего разряда на один разряд, тем самым в старшем разряде регистра содержится информация, соответствующая номеру п-го встречного судна. Этот же код на такте Т1. устанавливается в счетчике 182 блока 2, тактовьй импульс на вычитакнций вход счетчика 182 поступает по цепи связи 47. Если п-ом разряде регистра 116 блока 8 записа- :на 1 (для п-го встречного судна fp ) то на такте 12 производится запуск блока 9 по цепи; элементы И257, И 262, цепьсвязи 80. Блоком 9 производится расчет значений угловых скоростей для встречного судна. По окончании работы блока 9 последним вырабатывается импульс окончания расчета, которьй по цепи 78 связи, элементы ИЛИ 194, И 258, ИЛИ 195 вновь запускает распределитель 271. Продолжается процесс анализа содержимого регистра 116 и расчета значений угловых скоростей отворота собственного судна по отношению к тем встречным судам, для которых время сближения минимально. Если в п-ом разряде регистра 116 записан нуль, то запуск блока 9 не производится, а запускается распределитель 2.71 по цепи: элементы И 259, И 260, ИЛИ 195.Содержимое регистра 116 ана.лизируется до момента обнуления счетчика 182 блока 2. В этом случае по цепи связи 51 с блока 2 поступает сигнал запуска на повторньм запуск распределителя 271 и тем самым завершается работа блока 8. Блок 9 функционирует следующим образом. Синхронизация работы блока осуществляется формирователем 86 синхросигналов, первоначальный импульс запуска на которьп поступает с блока 8 (цепь связи 80). При этом начинает работать распределитель 273, На тактах Т1-Т5 содержимое счетчика 181 блока 2 (цепь связи 45) увеличиЧ вается на пять, что приводит к установке кода адреса параметра ИП2 - пеенга на встречное судно с порядковым номером для рассмотренного слуая равным п. По цепи связи 45 в лок 2 с распределителя 273 постуают тактовые импульсы Т7, Т13, Т15, 17, Т19, Т36, Т38, каждьй из котоых увеличивает содержимое счетчика 181 на единицу. Этим осуществляете последовательньй перебор кодов адресов параметров.движения, отображенных в таблице. На такте Т6 из ОЗУ 175 блока 2 считывается код значения пар. - метра Ш1д и передается на вход сумматора 285 блока 9 через группы элементов И 142, ИЛИ 169. На такте Т7 устанавливается адрес параметра ИКц(курс собственного судна), а на такте Т8 из ОЗУ 175 считывается код значения этого параметра и передается на другой вход сумматора 285 через группы элементов И 136, ИЛИ 167.На такте Т9 содержикое триггера 226 блока 9 переписывается в знаковьй разряд слагаемого по входу сумматора 285. Результат сложения на такте Т10 передается на вход блока 4 тригонометрических преобразований (цепь связи 65). Сигналом, передаваемым из блока 9 по цепи связи 68 в блок 4 иа такте Т11, обеспечивается подготовка блока 4 к работе и устанавливается в нем признак вычисления созСИП -ИК,,). Конец этой операции характеризуется поступлением по цепи 69 связи импульса разрешения на запуск второй части распределителя 273. Кодированное значение cos (ИП2-Ж„) поступает на блок 9 из блока 4 по цепи 70 связи. Это число на такте Т12 через группы элементов И 140, ИЛИ 168 передается на вход умножителя 92. Тактовый импульс на входы группы элементов И 140 поступает из формирователя 86 с выхода элемента ИЛИ 215. На та.кте .Т 13 изменяет ся содержимое счётчика 181 блока 2 и устанавливается адрес параметра V (скорость встречного судна), а тактом Т14 считывается из ОЗУ 175 собст «. . . венно значение параметра Уц и переда ется на вход умножителя 92 блока 9 через группы элементов И 145, ИЛИ 170. 1ак товЫй импульс на входы группы элементов И 145 поступает с выхода элемента ИЛИ 208 формирователя 86. Результат умножения на такте Т15 через группу элементов И t47, ИЛИ 168 внов передается на вход умножителя. На этом же такте Т15 за счет изменения содержимого счетчика 181 блока 2 устанавливается код адреса параметра Д (относительная дальность до встречного судна через интервал времени At). На такте Т16 из ОЗУ 175 блока 2 считьшается код значения параметра Д и передается на вход ум ножителя 9, производится запись этого числа в регистр 115 блока 9с Тактирующий импульс записи числа в регистр 115 поступает на последний с выхода элемента ИЛИ 207. Результат умножения на такте Т17 передается в регистр 113 по цепи: группы элементов И 148, ИЛИ 171. На этом же такте Т17 в ОЗУ 175 блока 2 устанавливается адрес параметра V, (скорость собственного судна), а на такте Т18 значение этого параметра считывается из ОЗУ и поступается на вход умножителя 92 и, кроме того, зап гсывается в регистр 112 блока 9. Тактом Т19 на адресном входе ОЗУ 175 блока 2 формируется адрес параметра Ддоп (допустимый радиус безопасности), На такте Т20 код значения параметра считыва- ется из ОЗУ 175 и через группы элементов И 139, ИЛИ 168 блока 9 поступают на умножитель 92. Результат умножения на такте Т21 заносится в регистр 114. Тактовьй икшульс записи числа в регистр поступает на вторые входы группы элементов И 150с выхода элемента ИЛИ 119 формирователя 86. На такте Т22 содержимое регистров 113 и 114 передается на оба входа суьФ атора 285 по цепи: группыэле- ментов И 137, ИЛИ 167 и И 143,ИШ 169 соответственно, тактовый импульс формируется элементами ИЛИ 211, 213 формирователя 86. Результат сложения на такте Т23 через группы элементов И 149, ИЛИ 171 передается в регистр 113. На такте Т24 сигнал по цепи связи 66 в блок 4 служит признаком вычисления sin (ИП2-ИК). Окончанием расчета в блоке 4 приведенного выражения служит сигнал, поступакщий По цепи связи 67 на запуск третьей части распределителя 273. Вычисленное значение на такте Т25 из блока 4 по цепи 70 связи передается на вход умножителя 92 блока 9. Тактовьй импульс, разрешающий передачу информации на вход умножителя, формируется элементом ИЛИ 215 формирователя 86 и поступает на вторые входы группы элементов И 140. Так как в вычислениях принимается в расчет лишь модуль этого сомножителя, то в знаковьй разряд множителя записываетсякод нуля. Эта операция осуществляется на такте Т26 путем переписывания О с нулевого выхода триггера 226. Кроме того, на такте Т25 через группу элементов И 144, ИЛИ 170 на вход умножителя 92 передано содержимое регист ра 112. Результат умножения V../sin (ИП2-ИКц) и содержимое регистра 115 на такте Т27 поступают на входы умножителя 92 соответственно по цепи: И 147, ИЛИ 168 и И 146, ИЛИ 170. Так тирующие импульсы формируются элемен тами ИЛИ 210, 216 формирователя 86. Результат умножения (ИП2-ИК„). Ц,2 передаётся в регистр 114. Импульс разрешающий запись в регистр, формируется элементом 1ШИ 212 на такте Т28. На такте Т29 содержимое регистров 113, 114 передается на входы сум матора 285, а результат сложения на Такте. ТЗО через группы элементов И 13 ИЛИ 168 поступает на вход умножителя 92;. Импульс, разрешающий передачу ин формации, формируется элементом ШШ 214. Наэтом же такте ТЗО на адресно входе ОЗУ 175 блока 2 устанавливаетс КОД адреса, рассчитанного ранее блоком 1 и записанного в ОЗУ коэффици2Значение этого коэфента -5 2 Аоп фициента на такте Т31 поступает на вход умножителя 92 и записывается в регистр 115. На такте Т32 содержимое регистра 114 передается в сумматор 285. На такте ТЗЗ знаковьм разряд этого слагаемого устанавливается при нудительно, вне зависимости от ранее полученного результата.. Осуществляет ся это путем считывания потенциала с единичного выхода триггера 226 и его передачи через элемент И 265 на знаковьй разряд входа сумматора 285. На такте ТЗЗ осуществляется передача содержимого регистра 113 на другой вход сумматора. На такте Т34 результат умножения пг:п (ип2-ик„)д,,-иу„д „+у„ / Mj ДАОП /81п(И11г-ИКц)/В.г переписывается в регистр 113. На так те Т35 результат сложения Уцсоз (ИП2-ИК„.)В J,+VH /Sin(ИП.2-ИК„)7Д, передается на один из входов умножителя 92, а на его другой вход пасту . пает содержимое регистр 115 2. ДРД . . На такте Т36 результат умножения передается в регистр 114, кроме того, на этом такте увеличивается содержимое счетчика 181 блока 2 на единицу, что приводит к установке кода адреса свободной ячейки ОЗЦ 175. Следующим тактом Т37 запускается блок 10 формирования направления поворота. Направление поворота собственного судна от встречного определяется знаком и попаданием модуля величины () в определенные интервалы значений. По цепи 63 связи на вход схемы 283 сравнения блока 10 придается значение модуля выражения ИП2-ИКц, а по цепи 64 связи - его знак. По цепям 81 и 82 связи с блока 9 передается содержимое регистра 113 дГ1дГ- (ИП,-ИК„ ),Д,„н 2 АОП +У„/з1п (ИП2-ИК„)/Д2 и регистра 114 4 дГ1ДГ-- соз(ИП,-ИК„)Д2-ьУ„Д,,-Ун/31п(1Ш2-ИКн)/Д2. Схемой 283 сравнения осуществляется сравнение модуля () с нулем-, если результат больше нуля, то на одном выходе схемы 283 сравнения .() будет 1, а на другом выходе () . При таких потенциалах на выходах схемы сравнения на такте Т37 код числа Ч через группы элементов И 152, ИЛИ 172, И.155, ИЛИ 174 поступает в блок 2 по цепи 49 связи и заносится в ОЗУ 175 по адресу, установленному на такте Т36. Разрешение на .прохождение информации по цепи связи формируется элементами ИЛИ 196, НЕ 278. На такте Т38 код адреса ОЗУ 175 увеличивается на единицу и на такте Т39 по этому адресу заносится в ОЗУ 175 код числа V. В передаче информации ; участвуют группы элементов И 153, ИЛИ 173, и 156 и ИЛИ 174. если модул (ИП2-ИК)0, то на выходе () схемы сравнения 283 установится 1, а на выходе ) будет О. В этом случае на такте Т37 в ячейку ОЗУ 175 с первым адресом, установленным на такте Т36, будет записано число V . Код числа передается по цепи: группы элеменгов И 151, ШШ 172, И 155, ШШ 174. Разрешение формируется элементами И 266, НЕ 277. По второму адресу, установленному на такте Т38, будет записаночисло V . Код числа передается по цепи; группы элементов И 154, ИЛИ 173, И 156, ИЛИ 174. Если значение выражения ИП2-ИК меньше нуля, то сигнал, поступакидий ра блок 10 по цепи связи 64, будет высокого уровня - 1. При этих условиях на выходе (А7В) схемы сравнения 283 будет 1, а на выходе () . Тогда тактом Т37 V заносится в ОЗУ 175 по первому адресу, а по второму адресу на такте Т39. Коды чисел V и Ч передаются соответственно jio цепям: группы элементов И 15 ИЛИ 172, И 155, И 154, ИЛИ 173, И 156. Таким образом, в ячейке ОЗУ 175 по первому адресу хранится значение величины поворота собственного судна влево (Уд), а в ячейке по второму адресу - вправо (V ). Тактом Т40 заканчивается процесс расчета и записи в ОЗУ 175 величин поворота собственного судна в приемлемых для него нап равлениях по отношению к курсу п-го встречного судна. Этот процесс повто ряется для тех из оставшихся встречных судов, для которых время сближения минимально. G этой целью блок 8 по цепи связи 78 с блока 9 периодически запускается тактом Т40. По окончанию всего цикла расчетов блоке 3 управления вырабатывается импульс конца третьей операции (Кон. опер.3% который прерьгоает действие Заправляющего сигнала ТМКЗ. Этим достигается останов распределителя 273 блока 9 И формируется управляющий сигнал МК4. Последним запускаются блоки 5, 8 и 11 системы. Помимо этог блоком 3 формируется управляищий сиг нал ТМК4, которым дается разрешение на продолжение работы блока 9. Для принятия правильного решения на маневр судна совокупностью блоков 3,8,9 системы выполняется анализ все го ряда полученных значений параметров V. I V.x (K4N) и производится выббр максимальных значений среди них. Так, сигналом МК4 в блоке В запускается распределитель 271 (цепь связи 59), содержимое регистра 111 блока 7 переносится в регистр 116 блока 8 и содержимое регистра 97 блока 2 - в счетчик 182 того же блока. На такте Т1 распределителя 271 блока 8 производится сдвиг регистра 116 на один разряд и уменьшение содержимого счет чика 182 блока 2 на единицу. Если рассматриваемое встречное судно представляет опасность, то в старшем разряде регистра 116 будет записана IV Этим формируется разрешающий управляющий потенциал на элемент И 257 и тогда на такте Т2 по цепи 79 связи производится запуск распределителя 274 формирователя блока 9. На первом такте распределителя 274 устанавливаются в нулевое состояние все разряды регистра 115 блока 9. На втором такте из ОЗУ 175 блока 2 считьшается начение Vj, для п-го встречного судна и заносится в регистр 11.5 блока 9. На третьем такте содержимое регистра 115 блока 9 по цепи связи 73 переписывается в регистр 104 блока 5. Тактирукщий импульс записи поступает из блока 9 по цепи связи 72 в блок 5 на вход элемента ИЛИ 192. Поскольку до начала работы системы регистр 105 установлен в нулевое состояние, то на выходе (А В) схемы 280 сравнения блока 5 будет высокий уровень сигнала 1. Поэтому на четвертом такте содержимое регистра 115 блока 9 будет переписано в регистр 103 блока 5. Разрешение на запись информации в регистр 105 формируется элементом И 251 блока 5,. Если же встречное судно с данным порядковом номером не опасно, то в старшем разряде регистра 116 блока 8 будет записан нуль. Тогда тактом 12 распределителя 271 не производится запуск распределителя 274 формирова-. теля 86 и вновь запускается распределитель 271. Анализ оставшихся членов ряда Vj, производится в такой последовательности, что очередной параметр первоначально всегда заносится в регистр 104 блока 5 и сравнивается со значением предьиущего параметра, хранящимся в регистре 105. В случае, если очередной параметр больше предьщущего, то содержимое регистров 104 и 105 уравнивается за счет перезаписи информации из регистра 115 блока 9 в регистр 105 блока 5 на четвертом такте распределителя 274, Таким образом, по окончании анализа ряда в регистре 105 блока 5 всегда будет записано максимальное значение из всей последовательности. Признакомконца анализа ряда служит обнуление счетчика 182 блока 2, по которому последним формируется в блоке 3 команда Кон.опер.4 и управляклций сигнал МК5. Командой Кон.опер.4, пе;реданной по цепи связи 44, фиксиру ется в регистра 106 блока 5V, управлякидему сигналу МК5 выполняется анализ ряда V,j , а с формированием команды Кон.опер.5 в регистре 107 блока 5 фиксируется максимальное зна чение; Численные величимы максймальньк значений в удобном для .восприятия судоводителем коде индицируются . блоком Г1. На основании полученной информации судоводитель с учетом праВИЛ судоходства принимает решение маневре судном. Блоком 4 находятся значения синуса и косинуса угла в пределах 0360® с дискретностью в 1°. Запуск блока 4 производится по цепи связи 68 сигналом, формируемым блоком 9. Этим сигналом триггер 224 устанавливается в единичное состояние и тем самым подготавливается к запуску распределитель 269. Сигнал высокого уровня, требуемый для замыкания цепи обратной связи распределителя, поступает на вход Тр с выхода элемента ИЛИ 189, Кроме того, изменение состояния триггера 224 из О в 1 (Обеспечивает установку всех.разрядов регистра 100 в нулевое состояние. ; Запуск распределителя 269 блока 4 производится по командам с блока 9 на одиннадцатом Т11 и двадцать четвертом Т24 тактах работы распределителя 273 блока 9. Импульс запуска Т :на распределитель 269 блока 4 посту|пает с блока 3 управления по цепи связи 58. На такте Т1 распределителя 269 блока 4 на вход вычитаемого вычитате ля 90 заносится модуль числа, хранящегося в регистре 98, а на вход умен шаемого - содерлсимое регистра 102. В регистре 98 содержится значение резупьтата вычитания величин ( ,) со знаком, синус и косинус которого необходимо определить, это угол между курсом собственного судна и пеленгом п-го встречного суд на. В регистре 102 хранится код угла oi «90. На такте Т2 результат вычитания (90го „) за исключением знакового разряда пересыпается в регистр 101. Знак результата вычитания зависит от величины угла (при .flt-ic 90 он положительш, npRfli 90 отряцательный) и в случае, если он 1 8. отрицательный ( : 360°) , то на этом такте Т2 на вход вычитаемого вычитателя 90 йоступает содержимое регистра 99; код угла равен 270. Передача кода производится через группу элементов И 129. Потенциал, разрешающий передачу кода, формируется на выходе элемента И 248 при поступлении на один из его входов потенциала , высокого уровня с выхода знакового разряда вычитателя 90, На вход уменьшаемого вычитателя 90 подается модуль величины угла - содержимое регистра 9 Передача кода осуществляется через группу элементов И 133. На такте ТЗ содержимое знакового разряда результата вычитания (о „-270°) заносится в знаковый разряд регистра 100 по цепигэлемент И 247, ИЛИ 191. Потенциал, разрешающий передачу информации элементов И 247 формируется на выходе элемента И 244. На такте Т4 содержимое регистра 101 - модуль величины (90-cir,) - заносится на вход вычитаемого вычитателя 90 по цепи: группы элементов И 128, ИЛИ 165. Разрешающий потенциал на входы группы элементов И 128 формируется на такте Т4 элементом И 245. На вход уменьшаемого вычитателя 90 через группы элементов И 132, И 166 подается содержимое регистра 103: код угла, равньй 180. Результат вычитания за исключением знакового разряда на такте Т5 поступает на адресный вход ОЗУ 176 и фиксируется в регистре адреса этого ОЗУ, в ОЗУ 176 предварительно записаны значения sin о с дискретностью 1 при 6(0,180), т.е. в ячейке ОЗУ с адресом 180-(90-о п) хранится значение sin ()3 . На такте Т6 изменения состояния элементов блока 4 не происходит, так как в данном случае производится вычисление косинуса. Признаком вычисления косинуса, как уже отмечалось, явля 1. На ется установка триггера 224 в такте Т7 из ОЗУ 176 считывается значение (( ) , что соответствует cos Ып ° число на этом же такте Т7 заносится в регистр 100 т.о. в регистре 100 записано значение cosc(r, со знаком, который определен на этапе вычитания (270) такт ТЗ работы устройства. Тактом Т8 заканчивается работа блока 4. При этом по цепи 69 связи в блок 9 подается сигнал об окончании расчета,

3111

через элемент 284 задержки триггеры 223, 224 блока 4 устанавливаются в исходное нулевое состояние, узел 87 блока 3 (цепь 62 связи) - в исходное состояние,

Рассмотрим работу блоки 4 для случая, когда знак результата вычитания (,) положительный о6„ 90. На такте Т2 результат вычитания за искпктением знакового разряда пересылается в регистр 101, а на такте ТЗ содержимое знакового разряда вычитателя 90 заносится в знаковый разряд регистра 100. Для того, чтобы содержимое знакового разряда вычитателя 90 не изменялось до начала действия такта ТЗ на такте Т2 на оба входа вычитателя заносится одно и тоже число (oCj,), хранящееся в регистре 98. Дальнейшая работа блока 4 по вычислению coset, при Ыд . 90 аналогична описанной. Таким образом, на тактах Т1, Т2 работы блока 4 прризводится определение знака .