сл

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1985 |

|

SU1352624A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1587515A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1451781A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

| Многоканальный сигнатурный анализатор | 1987 |

|

SU1529221A1 |

| Сигнатурный анализатор для контроля устройств памяти | 1987 |

|

SU1506449A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах технического диагностирования дискретных объектов. Цель изобретения - повышение быстродействия. Устройство содержит блок памяти, счетчик адреса, дешифратор, три регистра, формирователь испытательных последовательностей, распределитель импульсов, блок коммутации, генератор импульсов, сигнатурный анализатор, блок индикации, генератор псевдослучайных чисел, формирователь синхросигналов. Устройство позволяет формировать на входах проверяемого объекта три вида сигналов - псевдоциклический код, псевдослучайные сигналы и сдвинутые син- хросерии. Эффективность устройства повышается при проверке схем, проектирование которых выполнено с учетом контролепригодности. 1 з.п, ф-лы, 5 ил.

Изобретение относится к вычислительной технике и может быть использовано в системах тестового диагностирования.

Цель изобретения - повышение быстродействия устройства.

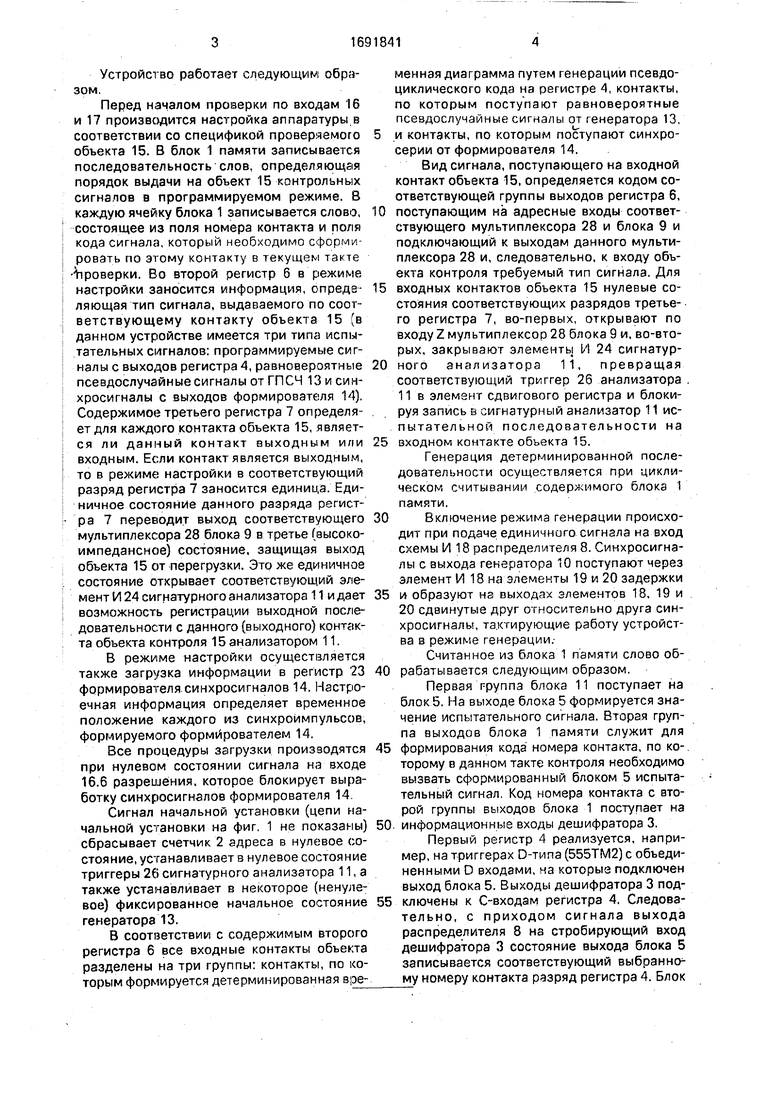

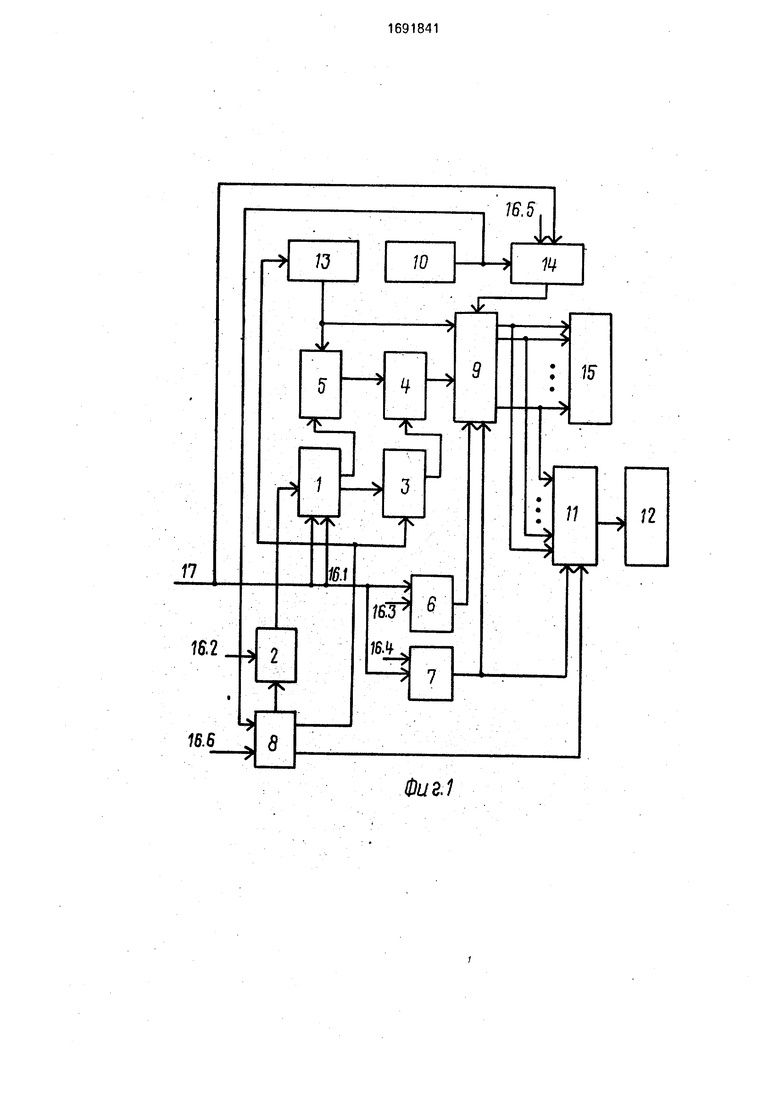

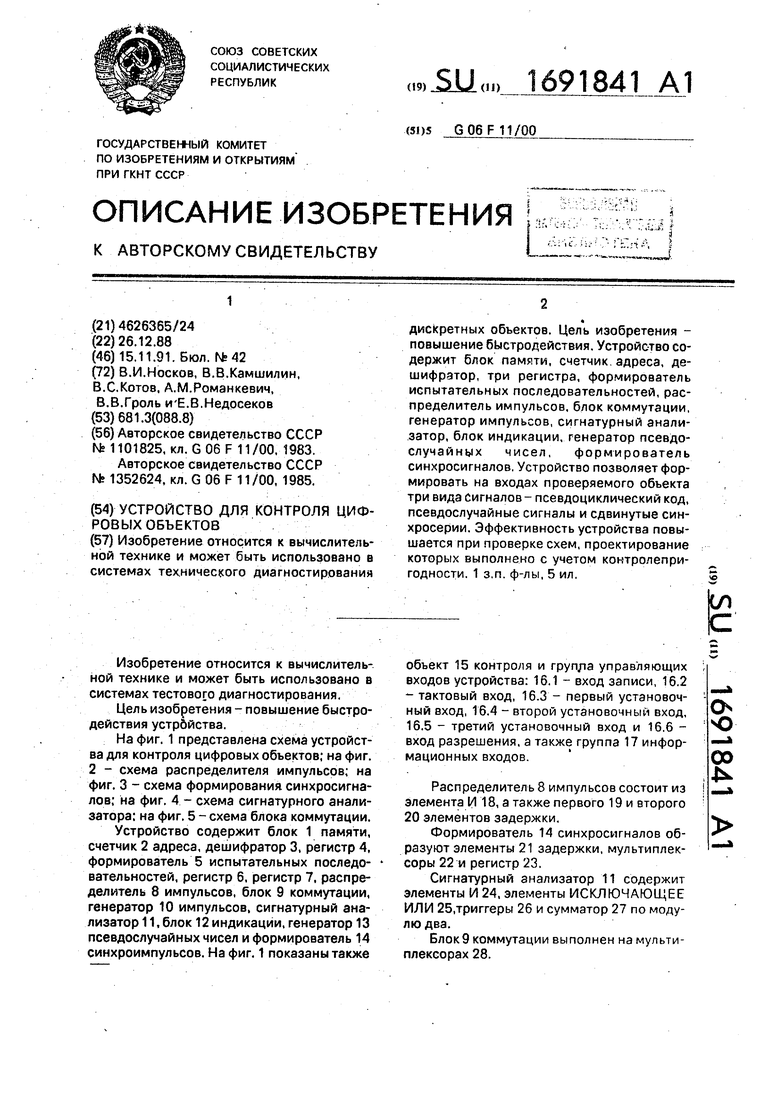

На фиг. 1 представлена схема устройства для контроля цифровых объектов; на фиг. 2 - схема распределителя импульсов; на фиг. 3 - схема формирования синхросигналов; на фиг. 4 - схема сигнатурного анализатора; на фиг. 5 - схема блока коммутации.

Устройство содержит блок 1 памяти, счетчик 2 адреса, дешифратор 3, регистр 4, формирователь 5 испытательных последовательностей, регистр 6, регистр 7, распределитель 8 импульсов, блок 9 коммутации, генератор 10 импульсов, сигнатурный анализатор 11, блок 12 индикации, генератор 13 псевдослучайных чисел и формирователь 14 синхроимпульсов. На фиг. 1 показаны также

объект 15 контроля и rpynjia управляющих входов устройства: 16.1 - вход записи, 16.2 - тактовый вход, 16.3 - первый установочный вход, 16.4 - второй установочный вход, 16.5 - третий установочный вход и 16.6 - вход разрешения, а также группа 17 информационных входов.

Распределитель 8 импульсов состоит из элемента И 18, а также первого 19 и второго 20 элементов задержки.

Формирователь 14 синхросигналов образуют элементы 21 задержки, мультиплексоры 22 и регистр 23.

Сигнатурный анализатор 11 содержит элементы И 24, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 25,триггеры 26 и сумматор 27 по модулю два.

БлокЭ коммутации выполнен на мультиплексорах 28.

сь ю

со

Јь

Устройство работает следующим образом.

Перед началом проверки по входам 16 и 17 производится настройка аппаратуры в соответствии со спецификой проверяемого объекта 15. В блок 1 памяти записывается последовательность слов, определяющая порядок выдачи на объект 15 контрольных сигналов в программируемом режиме. В каждую ячейку блока 1 записывается слово, состоящее из поля номера контакта и поля кода сигнала, который необходимо сформировать по этому контакту в текущем такте проверки. Во второй регистр б в режиме настройки заносится информация, определяющая тип сигнала, выдаваемого по соответствующему контакту объекта 15 (в данном устройстве имеется три типа испытательных сигналов: программируемые сигналы с выходов регистра 4, равновероятные псевдослучайные сигналы от ГПСЧ 13 и синхросигналы с выходов формирователя 14). Содержимое третьего регистра 7 определяет для каждого контакта объекта 15, является ли данный контакт выходным или входным. Если контакт является выходным, то в режиме настройки в соответствующий разряд регистра 7 заносится единица. Единичное состояние данного разряда регистра 7 переводит выход соответствующего мультиплексора 28 блока 9 в третье (высоко- импедансное) состояние, защищая выход объекта 15 от перегрузки. Это же единичное состояние открывает соответствующий элемент И 24 сигнатурного анализатора 11 идает возможность регистрации выходной последовательности с данного (выходного) контакта объекта контроля 15 анализатором 11.

В режиме настройки осуществляется также загрузка информации в регистр 23 формирователя синхросигналов 14. Настроечная информация определяет временное положение каждого из синхроимпульсов, формируемого формирователем 14.

Все процедуры загрузки производятся при нулевом состоянии сигнала на входе 16.6 разрешения, которое блокирует выработку синхросигналов формирователя 14.

Сигнал начальной установки (цепи начальной установки на фиг. 1 не показаны) сбрасывает счетчик 2 адреса в нулевое состояние, устанавливает в нулевое состояние триггеры 26 сигнатурного анализатора 11, а также устанавливает в некоторое (ненулевое) фиксированное начальное состояние генератора 13.

В соответствии с содержимым второго регистра 6 все входные контакты объекта разделены на три группы: контакты, по которым формируется детерминированная временная диаграмма путем генерации псевдоциклического кода на регистре 4, контакты, по которым поступают равновероятные псевдослучайные сигналы от генератора 13,

и контакты, по которым поступают синхро- серии от формирователя 14.

Вид сигнала, поступающего на входной контакт объекта 15, определяется кодом соответствующей группы выходов регистра 6,

0 поступающим на адресные входы соответствующего мультиплексора 28 и блока 9 и подключающий к выходам данного мультиплексора 28 и, следовательно, к входу объекта контроля требуемый тип сигнала. Для

5 входных контактов объекта 15 нулевые состояния соответствующих разрядов третьего регистра 7, во-первых, открывают по входу мультиплексор28 блока9 и, во-вторых, закрывают элементы И 24 сигнатур0 ного анализатора 11, превращая соответствующий триггер 26 анализатора 11 в элемент сдвигового регистра и блокируя запись в сигнатурный анализатор 11 ис- пытательной последовательности на

5 входном контакте объекта 15.

Генерация детерминированной последовательности осуществляется при циклическом считывании содержимого блока 1 памяти.

0 Включение режима генерации происходит при подаче единичного сигнала на вход схемы И 18 распределителя 8. Синхросигналы с выхода генератора 10 поступают через элемент И 18 на элементы 19 и 20 задержки

5 и образуют на выходах элементов 18, 19 и 20 сдвинутые друг относительно друга синхросигналы, тактирующие работу устройства в режиме генерации,Считанное из блока 1 памяти слово об0 рабатывается следующим образом.

Первая группа блока 11 поступает на блок 5. На выходе блока 5 формируется значение испытательного сигнала. Вторая группа выходов блока 1 памяти служит для

5 формирования кода номера контакта, по которому в данном такте контроля необходимо вызвать сформированный блоком 5 испытательный сигнал. Код номера контакта с второй группы выходов блока 1 поступает на

0 информационные входы дешифратора 3.

Первый регистр 4 реализуется, например, на триггерах D-типа (555ТМ2) с объединенными D входами, на которые подключен выход блока 5. Выходы дешифратора 3 под5 ключены к С-входам регистра 4. Следовательно, с приходом сигнала выхода распределителя 8 на стробирующий вход дешифратора 3 состояние выхода блока 5 записывается соответствующий выбранному номеру контакта разряд регистра 4. Блок

5 может формировать единичные и нулевые сигналы различной вероятности.

Сигнал с первого выхода распределителя 8 поступает также на синхровход генератора 13, формируя в каждом такте контроля новый псевдослучайный набор, разряды которого используются для подачи в объект через соответствующие мультиплексоры 28 блока 9 коммутации равновероятных испытательных сигналов в непрерывном режиме (т.е. в каждом такте контроля, так как содержимое второго регистра б в течение всего периода проверки остается неизменным).

Третий вид сигналов - программируемые синхроимпульсы, вырабатываются формирователем 14 (фиг. 3). Количество мультиплексоров 22 формирователя 14 равно наибольшему числу синхросерий для множества проверяемых объектов. Таким образом, задавая различные коды в регистре 23 формирователя 14 можно на каждом из выходов этого блока получить различные синхросерий, произвольным образом смещенные друг относительно друга (смещение определяется величиной задержек элементов 21, а все синхросигналы на выходах формирователя 14 находятся в пределах периода следования импульсов задающего генератора 10).

1 Таким образом, все три вида сигналов (псевдоциклический код регистра 4, псевдослучайные сигналы генератора 13 и синхросерий формирователя 14) одновременно (в пределах такта проверки) поступают через открытые мультиплексоры 28 блока 9 на входы объекта. После окончания переходного процесса на выходных контактах объекта устанавливаются выходные (ответные) сигналы, которые по синхросигналу на втором выходе распределителя 8 отрабатываются в анализаторе 11.

После записи новой информации в сигнатурный анализатор 11 распределитель 8 вырабатывает импульс по третьему выходу, модифицирующий содержимое счетчика адреса 2, переходя к следующему такту контроля. Величина задержки элемента 19 распределителя 8 соответствует времени распространения сигнала через дешифратор 3, регистр 4, блок 9 коммутации, объект контроля 15, элемента И 24, элементы.25 сигнатурного анализатора 11. Величина задержки элемента 20 распределителя 8 определяется временем устойчивого сохранения сигналов на выходах объекта, в течение которого осуществляется надежная запись информации в сигнатурный анализатор 11. Интервал от импульса на выходе элемента задержки 20 распределителя 8 до очередного (ближайшего) импульса на выходе генератора 10 (т.е. входе элемента 19) должен быть не менее суммарного времени переключения счетчика 2 адреса и времени формирования очередного испытательного сигнала на выходе блока 5.

После формирования устройством требуемого числа тактов проверки сигнал 16.6 устанавливается в нулевое состояние, бло0 кируя дальнейшую выработку синхросигналов на выходах распределителя 8 и фиксируя последнее состояние сигнатурного анализатора 11, которое индицируется блоком 12 индикации. Предлагаемое устрой5 ство по сравнению с прототипом позволяет в единицу времени подавать существенно большее разнообразие проверяемых наборов на входы объекта 15, что сопровождается уменьшением вероятности наличия необна0 руживаемых неисправностей,

Эффективность предлагаемого устройства по сравнению с прототипом значительно выше при проверке схем, проектирование которых было выполнено с

5 учетом требований контролепригодности, в частности, на основе метода сквозного сдвигового регистра, когда результирующая схема в режиме контроля требует только небольшого числа, детерминированных од0 поразрядных последовательностей, для которых необходимо обеспечить жесткие временные ограничения, т.е. реализовать фиксированную временную диаграмму. Основное число входных контактов в таких схе5 мах допускает подачу равновероятных псевдоспучайных сигналов и сигналов программируемых синхросерий одновременно, на каждом такте проверки.

Формула изобретения

объектов, содержащее два регистра, генератор псевдослучайных чисел, формирователь испытательных последовательностей, счетчик адреса, распределитель импульсов, сиг5 натурный анализатор, блок индикации, блок памяти, генератор импульсов, выход которого соединен с тактовым входом распределителя импульсов, первый выход которого соединен с тактовым входом сигнатурного

0 анализатора, группа входов разрешения которого подключена к группе разрядных выходов первого регистра, группа выходов .блока коммутации подключена к группе информационных входов сигнатурного анали5 затора и образует группу информационных выходов устройства для подключения к выводам проверяемого объекта, второй выход распределителя импульсов соединен с входом разрешения дешифратора, группа выходов которого соединена с группой

тактовых входов второго регистра, группа информационных входов которого подключена к группе выходов формирователя испытательных последовательностей, группа разрядных выходов второго регистра соединена с первой группой информационных входов блока коммутации, первая и вторая группы выходов блока памяти соединены соответственно с первой и второй группой входов формирователя испытательных последовательностей, третья группа входов которого подключена к группе выходов генератора псевдослучайных чисел, группа разрядных выходов счетчика адреса соединен с группой адресных входов блока памяти, отличающееся тем, что, с целью повышения быстродействия, оно содержит третий регистр и формирователь синхросигналов, причем третий выход распределителя импульсов соединен с первым тактовым входом счетчика адреса, тактовый вход генератора псевдослучайных чисел подключен к второму выходу распределителя импульсов, третья группа выходов блока памяти соединена с группой входов дешифратора, группа входов запрета блока коммутации подключена к группе разрядных выходов первого регистра, группа разрядных выходов третьего регистра соединена с группой адресных входов блока коммутации, вторая группа информационных входов блока коммутации подключена к группе выходов генератора псевдослучайных чисел, третья группа информационных входов блока коммутации подключена к

группе выходов формирователя синхросигналов, тактовый вход которого подключен к выходу генератора импульсов, группа управляющих входов формирователя синхросигналов группы информационных входов блока памяти, первого и третьего регистра поразрядно объединены и образуют группу информационных входов устройства, второй тактовый вход счетчика адреса образует

тактовый вход устройства, вход записи блока памяти образует одноименный вход устройства, тактовые входы первого и третьего регистра, установочный вход формирователя синхросигналов образуют соответственно первый, второй и третий установочные входы устройства, вход разрешения распределителя импульсов образует одноименный вход устройства,

выходам регистра.

Фиг.1

| Устройство для контроля логических блоков | 1983 |

|

SU1101825A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1352624A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-11-15—Публикация

1988-12-26—Подача