113

. Изобретение относится к вычислительной технике и может быть использовано при построении специализированных машин для моделирования сетевых графиков и сопряжения их с объектом в реальном масштабе времени.

Цель изобретения - повышение быстродействия.

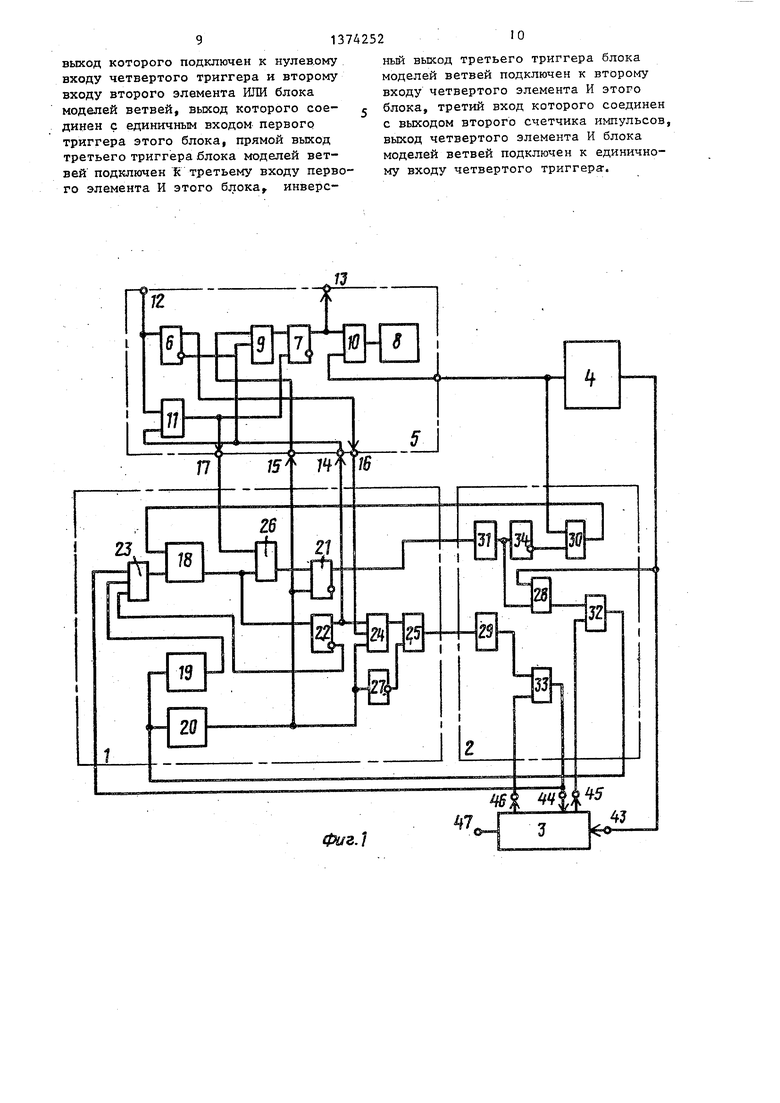

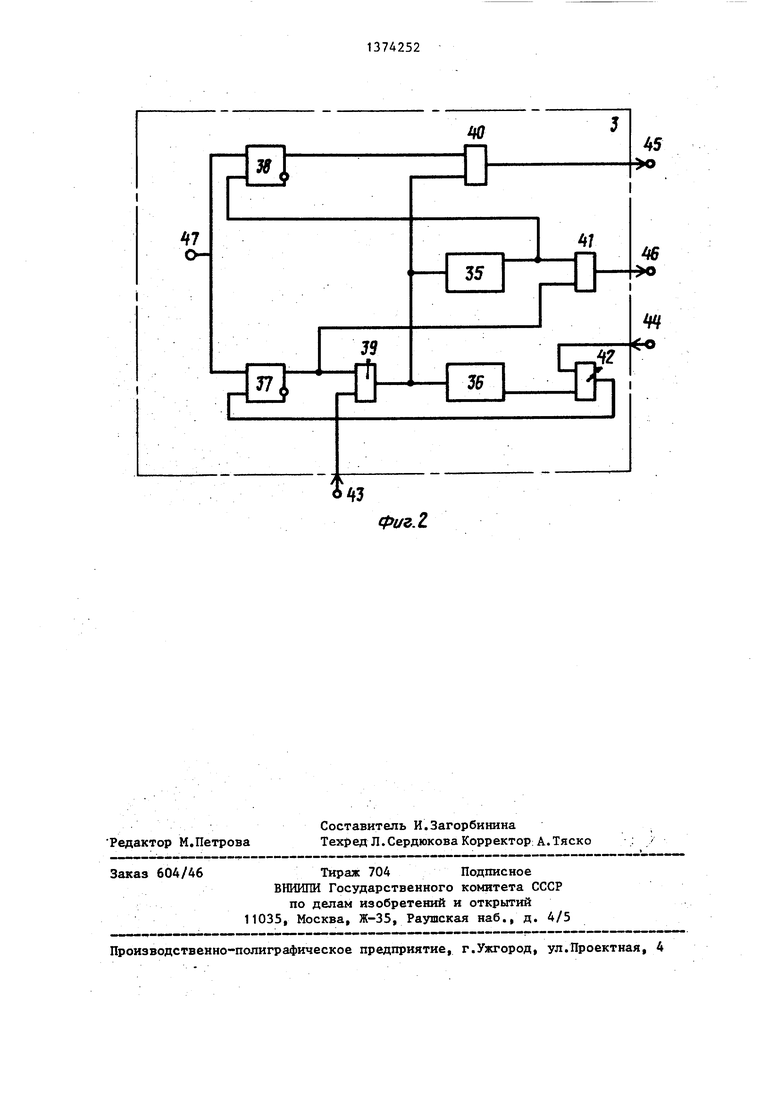

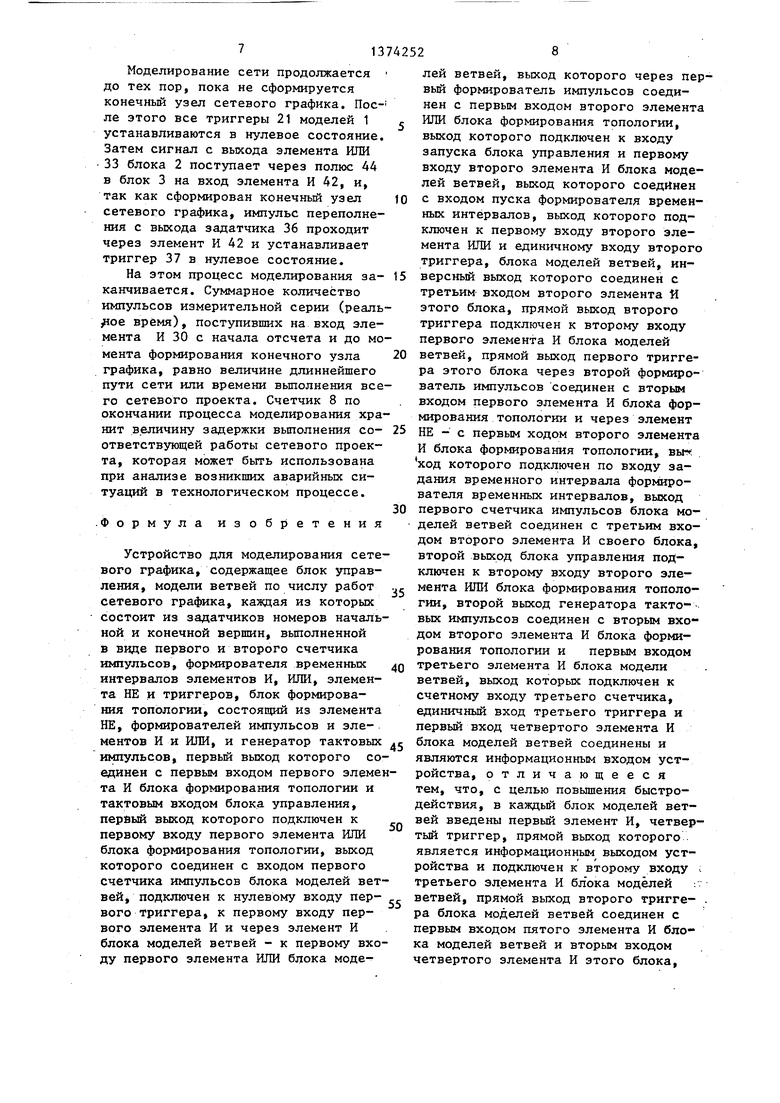

На фиг. 1 приведена блок-схема устройства; на фиг. 2 - схема блока управления.

Устройство содержит модели 1 ветвей по числу работ сетевого графика

2формирования топологии, блок 3 управления, генератор 4 импульсов, узел 5 сопряжения, содержатций триггеры б и 7, счетчик 8 и элементы

И 9 - 11.

Вход 12 и выход 13 устройства предназначены для организации связи с реальным объектом. Полюса 14-17 предназначены для организации взаимосвязи элементов устройства с соответствующей моделью 1 ветви.

Каждая из моделей 1 ветвей содержит формирователь 18 временных ин- тервалбв, задатчики начального 19 и конечного 20 адресов, выполненные в виде счетчиков импульсов, триггеры 21 и 22, элементы И 23 и 24, элементы ИЛИ 25 и 26 и элемент НЕ 27. Модель зетви предназначена для моделирования одной работы исследуемого сетевого объекта.

Блок 2 формирования топологии содержит элементы И 28-30, элементы ИЛИ 31-33 и элемент НЕ 34. Блок 2, соединенный с блоком моделей 1 ветвей сетевой модели, предназначен для обеспечения взаимосвязи моделей .1 вевей по временнному принцгату на основании адресов начального и конечного событий в задатчиках 19 и 20 адресов

Блок 3 .управления может быть выполнен различным образом,как управляющий автомат с. жесткой логикой и состоит из задатчиков 35 и 36 начального и конечного узлов сетевого графика соответственно, выполненных анало гично-задатчикам 19 и 20 блока моделей ветвей, триггеров 37 и 38, элементов И 39-42. Входы 43 и 44 блока

3управления соединены соответственн

с генератором 4 импульсов и выходом элемента ИЛИ 33 блока 2 формирования топологии, а выходы 45 и 46 блока управления подключены соответственно к входам элементов ИЛИ 32 и 33 блока

0

5

0

5

Q

5

0

формирования топологии. Позицией 47 обозначен вход пуска устройства. Блок 3 управления предназначен для осуществеления первоначального запуска сетевой модели.

Генератор 4 импульсов предназначен для выработки на своих выходах двух серий импульсов: измерительной И топологической, которые соответст- :венно соединены с элементами И 30 jK 28 блока 2, а выход измерительной серии соединен также с элементом И 10. Измерительная серия соответствует реальному масштабу времени и предназначена для обеспечения функционирования модели сети в полном соответствии с реальоным объектом. Топологическая серия предназначена для обеспечения ускоренного моделирования топологии.

Рассмотрим работу устройства при обеспечении обмена информацией между объектом и сетевой моделью в реальном масштабе времени для оперативного контроля вьшолнения работ по сетевому проекту.

В сетевой модели в задатчики 19 и 20 адресов всех моделей ветвей предварительно заносятся количества импульсов, дополняющие номера соответственно начальных и конечных узлов ветвей сетевого графика до полной емкости счетчиков. В формирова- 5 тель 18 временных интервалов каждой модели 1 ветви заносится количество импульсов соответствующее длительности моделируемой ветви, а триггеры 21 и 22 устанавливаются в нулевое состояние.

В блоке 3 управления предварительно в задатчики 35 и 36 заносятся соответственно дополнительньй код адре са начального и конечного узлов контролируемого сетевого графика, триггеры 37 и 38 устанавливаются в нулевое состояние.

Триггеры 6 и 7 и счетчик 8 предварительно устанавливаются в нулевое состояние.

Для включения модели сети синхронно с работой объекта сигнал Пуск подается на полюс 47 блока 3 в момент, соответствующий планируемому времени начала выполнения контролируемого проекта. Сигнал Пуск в блоке 3 управления поступает на входы триггеров 37 и 38 и устанавливает их в единичное состояние. Единичное состо0

5

яние триггера 37 выдает разрешение на вход элемента И 39, а импульсы с выхода генератора 4 через входной полюс 43 и элемент И 39 проходят на входы задатчиков 35 и 36.

Кроме того,импульсы с выхода элемента И 39 проходят через элемент И 40, и на втором входе которого присутствует разрешение с выхода триггера 38, на выходной полюс 45. Далее они через (полюс 45 на фиг.1) элемент ИЛИ 32 блока 2 формирования топологии поступают на входы задатчиков 19 и 20 адресов блока моделей ветвей. Эти импульсы поступают до тех пор, пока на выходах задатчиков 19, в которых записан адрес начального узла сетевого графика, не появится сигнал переполнения. В этот же мо мент времени на выходе задатчика 35 начального узла сетевого графика в блоке 3 появляется сигнал перепол

нения, которьй проходит через элемент

И 41, так.как на втором входе элемента присутствует разрешение с выхода триггера 37, на выходной полюс 46 и далее поступает на вход элемента ИЛИ 33 блока 2 формирования топологии.

Сигнал переполнения с выхода задачика 35 поступает также на вход триггера 38 и устанавливает его в нулевое состояние. В результате прекращается подача импульсов на вход элемента ИЛИ 32 блока 2.

Сигнал с выхода элемента ИЛИ 33 блока 2 формирования топологии поступает на входы элементов И 23 всех моделей 1 ветвей. Разрешающий сигнал появляется на выходе тех элементов И 23, на остальных входах которого присутствует разрешение с нулевого выхода триггера 22 и задатчика 19. Сигнал с выхода элемента И 23 проходит на вход формирователя 18 времен- Hbix интервалов соответствующей модели ветви и подготавливает его к от- (Счету импульсов измерительной серии (ГИ1), поступающей из блока 2 формирования топологии. Таким образом, в модели сети подготавливаются для моделирования длительностей те модели ветвей, которые выходят из начального узла сети.

После этого осуществляется моделирование длительностей в моделях ветвей, имеющих включенные формирователи 18 временных интервалов. В этом

0

0

5

5

случае все триггеры 21 моделей вет- , вей 1 находятся в нулевом состоянии, так как ни один формирователь не выработал сигнал переполнения. Элемент ИЛИ 31 блока 2, объединяющий единичные выходы триггеров 21, вырабатьгоа ет запрещакщий сигнал на прохождение топологической серии (ГИ2) генератора 4 через элемент И 28 и через элемент НЕ 34 разрешающий сигнал на вход элемента И 30, Как результат импульсы измерительной серии (ГИ1) генератора 4 проходят на входы формирователей 18 временных интервалов всех моделей 1 ветвей, но отсчитывают измерительную серию только формирователи, подготовленные сигналом с выхода элемента И 23.

Формирователи 18 временных интервалов моделей 1 ветвей отсчитьшают измерительную серию ГИ1, соответствующую длительности данной ветви до тех пор, пока хотя бы один из них не выработает сигнал, которьй установит в единичное состояние триггеры 21 и 22 своей модели ветви. С единичного выхода триггера 21 сигнал поступает в блок 2 формирования топологии на один из входов элемента ИЛИ 31, к остальным входам которого подключены одноименные входы остальных моделей 1 ветвей. Пройдя через элемент ИЛИ 31, сигнал поступает на вход элемента НЕ 34, которьй вьфа- батывает запрет на одном из входов элемента И 30. В результате запрещается поступление импульсов (ГИ1) . измерительной серии на входы всех моделей 1 ветвей, хотя это не обязательно для предлагаемого устройства сопряжения с сетевой моделью, так как топологическая серия подается в ускоренном масштабе времени и ком5 мутация моделей ветвей выполняется до прихода следующего импульса измерительной серии. Сигнал с выхода элемента ИЛИ 31 также поступает на вход элемента И 28 и разрешает проп хождение импульсов серии ГИ2(топологической серии) с выхода генератора 4. Импульсы ГИ2 проходят через элемент И 28, ИЛИ 32 и поступают на входы задатчиков 19 и 20 адресов всех моделей 1 ветвей. Задатчики 19 и 20 начальных и конечных узлов отсчитьшают импульсы до тех пор, по- ка задатчик 20 модели 1 ветви, где сформирован временной интервал фор- ,

0

5

0

5

NiHpoBaTeneM 18, не вырабатьшает сигнал переполнения.

Сигнал с выхода задатчика 20 адресов (в котором записан адрес конечно- го узла ветви) в своей модели ветви устанавливает в нулевое состояние триггер 21 и поступает на первый вход элемента И 24 и на вход элемента НЕ 27. Кроме того, сигнал с вько- да задатчика 20 через полюс 15 проходит на вход элемента И 9.

В определенньй момент времени из объекта по каналу связи на полюс 12 в устройство проходит сигнал Конец выполнения работы. Появление этого сигнала в момент планируемого окончания соответствующей работы, который определяется на модели сети, подтверждает правильность вьшолнения операций в объекте. Сигнал конца работы с полюса 12 в устройстве устанавливает триггер 6 в единичное состояние. Во втором случае в технологическом процессе при возникновении каких-то неполадок происходит срьт конца вьшолнения определенной работы Сигнал конца выполнения этой работы не приходит в планируемый момент времени в устройство и триггер 6 остает ся в нулевом состоянии.

Для случая аварийного протекания технологического процесса триггер 6 находится в нулевом состоянии л вырабатьшает разрешающий сигнал на вход элемента И 9 и запрещающий сигнал через полюс 16 на вход элемента и 24 соответствующей модели ветви. ;В планируемый момент времени сигнал с выхода задатчика 20 адресов в этой ситуации проходит в устройстве через элемент И 9, так как на другом его входе присутствует разрешение с единичного выхода триггера 22 соответствующей модели ветви. Сигнал с вы- хода элемента И 9 поступает на единичный вход триггера 7 и устанавливает его в единичное состояние, которое определяет задержку выполнения соответствующей работы в объекте. Для этой работы сигнал Задержка с единичного выхода триггера 7 передается через полюс 13 на место выполнения соответствующей работы.

Если все ветви, входящие в рас- сматриваемый узел, сформировали временной интервал и имеется информация об окончании соответствующих работ, на выходе элемента И 29 блока 2 появляется разрешающий сигнал, который поступает через элемент ИЛИ 33 на полюсы моделей ветвей. Разреша- каций сигнал в каждой модели 1 ветви поступает на вход элемента И 23 и проходит через него в тех моделях ветвей, которые выходят из сформиро- ванного узла, т.е. при наличии разрешения с задатчика 19 адресов и нулевого вьосода тоиггет5а 22.

Импульсы с генератора. 4 поступают на входы задатчиков 19 и 20 до тёзГ. пор, пока хотя бы на одном из входов блока 2 присутствует сигнал с выхода триггера 21 какой либо модели 1. После того, как все триггеры 21 установлены в нулевое состояние выходными сигналами соответствующих задатчиков 20 адресов, блок 2 запрещает прохождение импульсов серии на входы задатчиков адресов. В блоке 2 разрешается беспрепятственное поступление импульсов измерительной серии на входы формирователей 18 BpeMeHiaix интервалов .

Импульсы измерительной серии поступают также через полюс 13 на входы элементов И 10. Если триггер 7 находился в единичном состоянии, что соответствует задержке выполнения работы, то счетчик 8 накапливает величину временной задержки работы (до прихода сигнала конца работы с места выполнения соответствукщей операции) .

В этом случае сигнал с полюса 12 проходит через элемент И 11, на втором входе которого присутствует разрешение с единичного выхода триггера 22 (полюс 14). С выхода элемента И 11 сигнал поступает на нулевой вход триггера 7 и устанавливает его в нулевое состояние, которое запрещает прохождение импульсов измерительной серии на вход счетчика 8. Этот же сигнал проходит через полюс 17 на вход элемента ИЛИ 26 соответ- ствуеющей модели 1 ветви. Сигнал с выхода, элемента ИЛИ 26 устанавливает триггер 21 в единичное состояние, которое вызывает прерьшание измери- тельной серии импульсов. Вьфабатывае- мая топологическая серия с выхода элемента И 28 блока 2 в ускоренном , масштабе времени осуществляет опрос задатчиков 19 и 20 адресов и формирует топологию моделируемой сети для текущего момента времени.

Моделирование сети продолжается до тех пор, пока не сформируется конечньй узел сетевого графика. После этого все триггеры 21 моделей 1 устанавливаются в нулевое состояние. Затем сигнал с выхода элемента ИЛИ 33 блока 2 поступает через полюс 44 в блок 3 на вход элемента И 42, и, так как сформирован конечный узел сетевого графика, импульс переполнения с выхода задатчика 36 проходит через элемент И 42 и устанавливает триггер 37 в нулевое состояние.

На этом процесс моделирования за- канчивается. Суммарное количество импульсов измерительной серии (реаль fioe время), поступивших на вход элемента И 30 с начала отсчета и до момента формирования конечного узла графика, равно величине длиннейшего пути сети или времени выполнения всего сетевого проекта. Счетчик 8 по окончании процесса моделирования хранит в.еличину задержки выполнения со- ответствующей работы сетевого проекта, которая может быть использована при анализе возникших аварийных ситуаций в технологическом процессе.

.Формула изобретения

Устройство для моделирования сетевого графика, содержащее блок управления, модели ветвей по числу работ сетевого графика, каждая из которых состоит из задатчиков номеров начальной и конечной вершин, выполненной в виде первого и второго счетчика импульсов, формирователя временных интервалов элементов И, ИЛИ, элемента НЕ и триггеров, блок формирования топологии, состоящий из элемента НЕ, формирователей импульсов и элементов И и ИЛИ, и генератор тактовых ньшульсов, первый выход которого соединен с первым входом первого элемета И блока формирования топологии и тактовым входом блока управления, первый выход которого подключен к первому входу первого элемента ИЛИ блока формирования топологии, выход которого соединен с входом первого счетчика импульсов блока моделей ветвей, подключен к нулевому входу пер- вого триггера, к первому входу первого элемента И и через элемент И блока моделей ветвей - к первому входу первого элемента ИЛИ блока моделей ветвей, выход которого через первый формирователь импульсов соединен с первым входом второго элемента ИЛИ блока формирования топологии, выход которого подключен к входу запуска блока управления и первому входу второго элемента И блока моделей ветвей, выход которого соединен с входом пуска формирователя временных интервалов, выход которого подключен к первому входу второго элемента ИЛИ и единичному входу второго триггера, блока моделей ветвей, инверсный выход которого соединен с третьим входом второго элемента Я этого блока, прямой выход второго триггера подключен к второму входу первого элемента И блока моделей ветвей, прямой выход первого триггера этого блока через второй формирователь импульсов соединен с вторым входом первого элемента И блока формирования топологии и через элемент НЕ - с первым ходом второго элемента И блока формирования топологии, ход которого подключен по входу задания временного интервала формирователя временных интервалов, выход первого счетчика импульсов блока моделей ветвей соединен с третьим входом второго элемента И своего блока, второй выход блока управления подключен к второму входу второго элемента ИЛИ блока формирования топологии, второй выход генератора тактовых импульсов соединен с вторым входом второго элемента И блока формирования топологии и первым входом третьего элемента И блока модели ветвей, выход которых подключен к счетному входу третьего счетчика, единичный вход третьего триггера и первый вход четвертого элемента И блока моделей ветвей соединены и являются информационным входом устройства, отличающееся тем, что, с целью повышения быстродействия, в каждый блок моделей ветвей введены первый элемент И, четвертый триггер, прямой выход которого является информационным выходом устройства и подключен к второму входу третьего элемента И бл ока моделей ветвей, прямой выход второго тригге- ра блока моделей ветвей соединен с первым входом пятого элемента И блока моделей ветвей и вторым входом четвертого элемента И этого блока.

выход которого подключен к нулев.ому входу четвертого триггера и второму входу второго элемента ИЛИ блока моделей ветвей, выход которого соединен с единичным входом первого триггера этого блока, прямой выход третьего триггера блока моделей ветвей подключен R третьему входу первого элемента И этого блока,, инверсньй выход третьего триггера блока моделей ветвей подключен к второму входу четвертого элемента И этого блока, третий вход которого соединен с выходом второго счетчика импульсов, выход четвертого элемента И блока моделей ветвей подключен к единичному входу четвертого триггера-.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования сетевых графиков | 1985 |

|

SU1300481A2 |

| Вычислительное устройство для решения задач сетевого планирования | 1978 |

|

SU750503A1 |

| Устройство для моделированияСЕТЕВОгО гРАфиКА | 1980 |

|

SU849232A2 |

| Устройство для моделирования сетевого графика | 1975 |

|

SU608169A1 |

| Устройство для моделирования сетевых графиков | 1983 |

|

SU1128272A2 |

| Устройство для моделирования сетевых графиков | 1983 |

|

SU1119024A1 |

| Устройство для расчета сетевыхгРАфиКОВ | 1979 |

|

SU851417A1 |

| Устройство для моделирования сетевых графиков | 1977 |

|

SU636635A2 |

| Устройство для моделирования сетевого графика | 1981 |

|

SU1012267A1 |

| Устройство для моделирования сетевых графиков | 1976 |

|

SU556460A2 |

Изобретение относится к области вычислительной техники и может быть использовано при построении специализированных машин для моделирования сетевых графиков и сопряжения их с объектом в реальном масштабе времени. Цель изобретения - повышение быстродействия. Цель достигается введением в каждый блок моделей ветвей элемента и триггера. Устройство позволяет уменьшить время выполнения исследуемых технологических процессов примерно в четыре раза за счет введения контроля текущего состояния сети в реальном масштабе времени. 2 ил.

Фиъ.

ф1/г2

| Авторское свидетельство СССР № , кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для моделирования сетевых графиков | 1985 |

|

SU1300481A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-02-15—Публикация

1985-04-24—Подача