;kHT сумматор no модулю 2, входы которого соединены с одним и другим входами определителя квадрантов, а выход через элемент НЕ определителя квадрантов подключен к одному выходу определителя квадрантов, другой выход которого соединен с другим входом определителя квадраитов.

4. Преобразователь по п. 1, отличаюищйся ем, что формирователь уровня содержит регистр формирователя, первый и второй элементы НЕ формирователя и селектормультиплексор, первый вход формирователя подключен к первому и через первый элемент НЕ формирователя к второму ииформациониым входам селектора-мультиллек- сора, второй и третий входы формирователя подключены к входам регистра формирователя, выходы которого подключены к управляющим входам селектора-мультиплексора,

третий вход формирователя подключен к третьему и через второй элемент НЕ -к четвертому информационным входам сеЛектора-мультиплексора, выход которого подключен к выходу формирователя, управляющий вход формирователя уровня подключен к управляющему входу регистра формирователя.

5. Преобразователь по. п. I, отлинающийся тем, что блок управления содержит нульорган, элемент ИЛИ и элемент И блсжа управления первый и второй входы блока управления подключены через элемент ИЛИ к второму выходу блока, третий вход блока через нуль-орган подключен к одному входу апемента И блока, другой вход которого соединен с первым входом блока, а выход элемента И блока подключен к первому выходу блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угла поворота вала в код | 1981 |

|

SU972541A1 |

| Радиопеленгатор ближних гроз | 1984 |

|

SU1233064A1 |

| Следящий преобразователь угла поворота вала в код | 1983 |

|

SU1116446A1 |

| Преобразователь сигналов с импульсно-кодовой модуляцией в сигналы с адаптивной дельта-модуляцией со слоговым компандированием | 1990 |

|

SU1709537A1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

| Двухотсчетный преобразователь угла поворота вала в код | 1985 |

|

SU1269265A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1280698A1 |

| Кольцевая система громкоговорящей связи с временным разделением каналов | 1990 |

|

SU1699359A3 |

| Преобразователь кода в угловое положение вала | 1985 |

|

SU1305864A1 |

| Устройство аналого-цифрового преобразования узкополосных сигналов | 1984 |

|

SU1225014A1 |

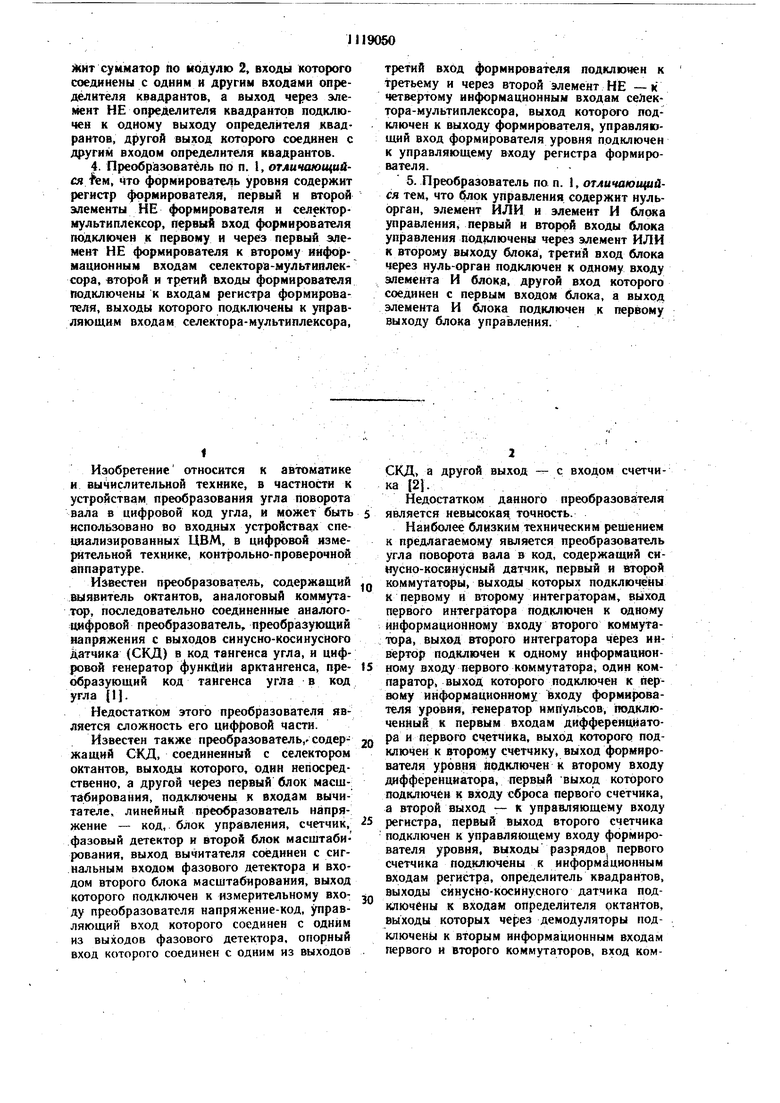

1. ПРЕОБРАЗОВАТЕЛЬ УГЛА ГЮВОРОТА ВАЛА В КОД, содержащий синусно-косинусный датчик, первый и второй коммутаторы, выходы которых подклю,чены к первому и второму интеграторам, выход первого интегратора подключен к од1юму информационному входу второго коммутатора выход второго HHterpatopa через инвертор подключен к одному информаци(жному входу первого коммутатора, один компаратор, выход которого подключен к ПЁрвому информационному входу формирователя уровня, генератор импульсов, подключенный к первым входам дифференциатора и первого счетчика, выход которого . подключен к второму счетчику, выход формирователя уровня подключен к второму входу дифференциатора, первый выход которого подключен к входу сброса nepBoix счетчика, а второй выход :- к управляющему входу регистра, первый вь1ход второго : счефчика подключен к управляющему входу формирователя уровня, выходы разрядов первого счетчика подключены к информационным входам регистра, определитель квадрантов, тем, что, с целью повышения точности преобразователя, в него введены блок управления, блок уставок и другой компаратор, выходы синусно-косинусного датчика подключены к другим входам первого и второго коммутаторов соответствеино, входы одного и другого компараторов подключены к выхода «i второго и первого интеграторов соответственно, а выходы компараторов подключены : к входам определителя квадрантов, выходы которого подключены к йторому и третьему ; информационным входам формирователя уровня и к установочным входам старших разрядов первого счетчика, установочные входы младших разрядов которого соединены с выходами блока уставок, первый выход дифференциатора подключен к входу сброса второго счетчика, выходы которого подключены к первому и второму входам блока управления, третий вход которого соединен с источником опорного напряжения, первый выход блока управления подключен к одиим i управляющим входам первого и второго ком- мутаторов, второй выход подключен к управ(Л ляющим входам интегратора, а первый выход второго счетчика подключен к другим управляющим входам первого и второго коммутаторов, управляющим входам дифференциатора и первого счетчика. 2,Преобразвватель по п. 1, отлинаюu ftucff тем, что дифференциатор содержит D-триггер, первый и второй элементы И дифференциатора и элемент НЕ дифференциатора, первый вход диффереицнатора со о ел подключен к С-входу D-триггера, к одному входу первого элемента И дифференциатора и через элемент НЕ дифференциатора - к одному входу второго элемента И дифференциатора, второй и управляющий i входы дифференциатора подключены соот- : ветственно к D- и R-входам триггера, выхоД триггера подключен к другим входам первого и второго элементов И диффереициатора а выходы второго и первого элементов И дифференциатора подключены к первому и второму выходам дифференциатора,f, 3.Преобразователь по п. 1, отлинаюи йся тем, что определитель квадрантов содер

«

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам преобразования угла поворота вала в цифровой код угла, и может быть использовано во входных устройствах специализированных ЦВМ, в цифровой измерительной технике, контрольно-проверочной аппаратуре.

Известен преобразователь, содержащий выявитель октантов, аналоговый коммутатор, последовательно соединенные аналогоцифровой преобразователь, преобразующий напряжения с выходов синусно-косинусного Датчика (СКД) в код тангенса угла, и цифровой генератор функций арктангенса, преобразующий код тангенса угла в код угла {1J.

Недостатком этого преобразователя является сложность его цифровой части.

Известен также преобразователь,-содержащий СКД, соединенный с селектором октантов, выходы которого, один непосредственно, а другой через первый блок масш-; табировання, подключены к входам вычитателе, линейный преобразователь напряжение - код, блок управления, счетчик, фазовый детектор и второй блок масштабирования, выход вычитателя соединен с снгнальным входом фазового детектора и входом второго блока масштабирования, выход которого подключен к измерительному входу преобразователя напряжение-код, управляющий вход которого соединен с одним из выходов фазового детектора, опорный вход которого соединен с одним из выходов

СКД а другой выход - с входом счетчика (21.

Недостатком данного преобразователя является невысокая, точность.

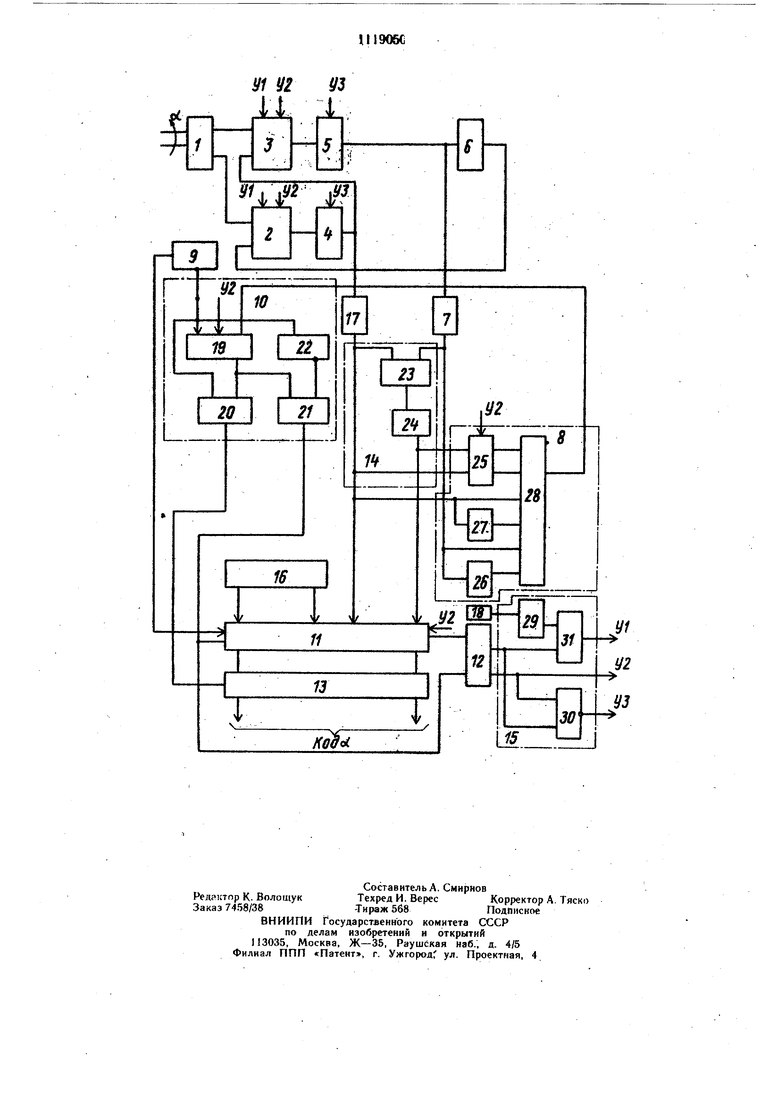

Наиболее близким техническим рещеиием к предлагаемому является преобразователь угла поворота вала в код, содержащий снусно-кос0нусный датчик, первый и второй коммутаторы, выходы которых подключены к первому н второму интеграторам, вь1ход первого интегратора подключен к одному информационному входу второго коммутатора, выход второго интегратора через инвертор подключен к одному информационному входу первого коммутатора, один компаратор, выход которого подключен к первому информационному входу формн{х}вателя уровня, генератор импульсов, подключенный к первым входам дифференциатора и первого счетчика, выход которого подключен к второму счетчику, выход формирователя уровня йрдключеи к второму входу ифференциатора, первый выход которого подключен к входу сброса первого счетчика, а второй выход - к управляющему входу егистра, первый выход второго счетчика подключен к управляющему входу формирователя уровня, выходы разрядов первого счетчика подключены к информационным входам регистра, определитель квадрантов, выходы синусио-косинусного датчика подключены к входам определителя октантов, выходы которых че|зез демодуляторы подключены к вторым информационным входам ервого и второго коммутаторов, вход компаратора соединен с выходом инвертора, а выход формирователя уровня подключен к управляющим входам первого и второго коммутаторов, второй выход второ-о счетчика подключен к управляющим входам интеграторов {З). Недостаток этого устройства - низкая точность. Цель изобретения - повышение точности. .Поставленная цель достигается тем, что в преобразователь угла поворота вала в код, содержащий синусно-косииусный датчик, первый и второй коммутаторы, выходы которых подключены к первому и второму интеграторам, выход первого интегратора подключен к одному информационному входу второго коммутатора, выход второго интегратора через инвертор подключен к одному йиформациоииому входу первого коммутатора, одии компаратор, выход которого ЛоДключен к первому информационному входу формирователя уровия, генератор импульсов, подключенный к первым входам дифференциатора и первого счетчика, выход которого подключен к второму счетчику, эыход формирователя уровня подключён к второму входу дифференциатора, первый которого подключен к входу сброса первого счетчика, а второй выход - к управляющему входу регистра, первый выход второго счетчика подключен к управляющему входу формирователя уровня, выходы разрядов первого счетчика подключены к информационным входам регистра, опредедатель квадр 1итов, введены блок управлетя, блок уставок и другой компаратор, выходы синусно-косинусного датчика подключены к другим входам первого и второго коммутаторов соответственно, .входы одного и другого компараторов подключены к выходам второго и первого интеграторов, соответственно, а выходы компараторов подключены к входам определителя квадрантов, выходы которого подключены к второму и третьему информационным входам формирователя уровия и к установочным входам старших разрядов первого счетчика, установочные входы младших разрядов которого соединены с выходами блока уставок, пфвый выход дифференциатора подключен к входу сброса второго счетчика, выходы которого подключены к первому и второму входам блока управления, третий вход коtoporo соединен с источником опорного напряжения, первый выход блока управления подключеи к одним управляющим входам первого и второго коммутаторов, .второй выход подключен к управляющим .входам интеграторов, а первый выход второго счет чика подключеи к другим управляющим входам первого и второго коммутаторов, управляющим входам дифференциатора и первого счетчика.. Дифференциатор содержит D-триггер, первый и второй элементы И дифференциатора и элемент НЕ дифференциатора, первый вход дифференциатора подключен к С-входу D-триггера, к одному входу первого элемента И дифференциатора и через элемент НЕ дифференциатора - к одному входу второго элемента И дифференциатора, второй и управляющий входы дифференциатора подключены соответственно к D- и R-входам триггера, выход D-трнггера подключен к другим входам первого и второго элементов И дифференциатора, а выходы второго и первого элементов И дифференциа тора подключен к первому и второму выхо дам дифференциатора. Определитель квадрантов содержит сумматор по модулю 2, входы которого Соединены с одним и Другнм входами определителя квадрантов, а выход через элемент НЕ определителя квадрантов подключен к одному выходу определителя квадрантов, другой выход которого соединен с другим входом определителя квадрантов. Формирователь уровня содержит регистр формирователя, первый и второй элементы НЕ формирователя и селектор-мультиплексор, первый вход формирователя подключен к первому и через первый элемент НЕ формирователя к второму информационным входам селектора-мультиплексора, второй и третий входы формирователя подключены к входам регистра формирователя, выходы которого подключены к управляющим входам селектора-мультиплексора, третий вход формирователя подключен к третьему и через второй элемент НЕ формирователя - к четвертому ииформациониым входам селектбра-мультиплексора, выход которого подключеи к выходу формирователя,управляющий вход формирователя уровня подключен к управляющему входу регистра формирователя., Блок управления содержит нуль-орган, элемент ИЛИ и элемент И блока управления, первый и второй входы блока управления подключены через элемент ИЛИ к второму выходу блока, третий вход блока через нуль-орган подключен к одному входу элемента И блока, другой вход которого соединен с первым входом блока, а выхоД элемента И блока подключен к первому выходу блока, упрайления. На чертеже представлена структурная схема преобразователя. Преобразователь УГЛЗ поворота вала в код содержит синусно-косииусный датчик i, первый 2 и второй 3 коммутаторы, выходы которых подключены к первому 4 и второму 5 интеграторам, выход интегратора 4 1юдключен. к одному информационному входу коммутатора 3, выход интегратора 5 через инвертор 6 подключен к одному инфрр макионному входу коммутатора 2, один компаратор 7, выход которого подключен к первому информацнонному входу формирователя 8 уровня, генератор 9 нмпульсов, 1юдключеннмй к первым входам дифференциатора 10 и первого счетчика 11, выход которого подключен к второму счетчику 12, выход формирователя б уровня подключен к второму входу дифференциатора 10, первый выход которого подключен к входу сброса счетчика II, а второй выход - к управляющему входу регистра 13, первый ых(5д счетчика 12 подключен к управляющему входу формирователя 8 уровня, выходы разрядов счетчнка II подключены к информационным входам регистра 13, определитель 14 квадрантов, блокЧ5 управления, блок 16 уставок н другой компаратор 17, выходы синусно-косннусного датчика J подключены к другим входам первого 2 н второго 3 коммутаторов соответственно, входы одного 7 н другого 17 компараторов подключены к выходам второго 5 и первого 4 интеграторов соответственно, а выходы компараторов 7 и 17 подключ ены к входам определителя 14 квадрантов, выходы которого подключены к второму н третьему нн-. формацнонным входам формирователя 8 уровня н к установочным входам старших разрядов счетчнка П, установочные входы младших разрядов которого соединены с выходами бловд 16 уставок, первый выход дифференциатора 10 подключены к входу сброса счетчика 12, выходы которого подключеиы к первому н второму входам блока 15 управл ения, третий вход которого соединен с источником 18 опорного иапряжеНня, первый выход блока 15 управления подключен к одним управляющнм входам .первого 2 н второго 3 коммутаторов, второй выход подключен к управляющнм входам интеграторов 4 и 5, а первый выход счетчнка 12 подключен к другим управляющим входам первого 4 и второго 5 коммутаторов, управляющим входам днфференш атЬра Ш н счетчнка 11..

Днфференциатор Ю содержнт D-трнггер 19, первый 20 и второй 21 элементы И днфференциатора н элемент НЕ 22 днфференцнатора, первый вход днфференциатора 10 подключен к С-входу О-трнггера 19, к одному входу элемента И 20 н через элемент НЕ 22 - к одному входу элемента И 21, второй и управляющий входы дифференцнатора 10 подключены соответственно к D- н R-входам триггера 19, выход D-трнггера 19 подключен к другим входам первого 20 и второго 21 элементов И, а выходы элементов И 20 и 2 подключены к первому н второму выходам днфференцнатора 10.

Определитель 14 квадрантов содержнт сумматор 23 по модулю 2, вхрды которого

соедннены с одним н другим входамн определителя 14 квадрантов, а выход через элемент НЕ 24 определнтеля -квадрантов подключен к одному выходу онределнтеля 14 квадрантов, другой выход которого сое-: дннеН с другим входом определнтеля 14 квадрантов.

Формнрователь 8 уровня содержнт регнстр 25 формнрователя, первый 26 н второй 27 элементы НЕ формнрователя н селектор-мультнплексор 28, первый вход формирователя 8 подключен к первому и через элемент НЕ 26 к второму информационным входам Селектор-мультиплексора 28 второй н третнй входы формнрователя 8 подключены к входам регистра 25, выходы которого подключены к управляющим входам селектор-мультиплексора 28, третий вход формнрователя 8 подключен к третьему и через элемент НЕ 27 - к четвертому информационным входам селектор-мультиплексора 28, выход которого подключен К выходу формирователя 8, управляющий вход формнрователя 8 подключен к управляющему йходу регистра 25.

Блок 15 управления содержит нульорган 29, элемент ИЛИ 30 и элемент И 31 блока управления, первый. н второй входы блока 15 управления подключены через элемент ИЛИ 30 к второму выходу блока 15, третнй вход блока 15 через нуль-орган 29 подключен к Одному входу элемента И 31, другой вход которого соедннен с первым входом блока. 15, а выход элемента И 31 подключен к первому выходу блока 15 управления.

Определитель 10 квадрантов предназначен для формировання кода квадранта, предшествующего квадранту расположення угла (напрнмер, при- расположении ее во втором квадранте формируется код первого квадранта н т.д.). Регнстр 25 предназначен для хранения кода квадранта, необходимого .ОЛЯ выделения нужного фронта сигнала из выходных снгналов компараторов 7 н 17 прн расположении угла оС в любом из четырех квадрантов. Счетчнк 11 имеет входы параллельной запнси во все разряды (например, счетчик может быть сделан нз микросхем 133ИЕ7). Код, хранящийся в йчоке 16 уставок совместно со-сформнрованным кодом квадранта представляет собой код начала квадранта расположения угла 0, уменьшенный на величину коДа, который предназначен для компенсацни задержки Т коммутаторов и компараторов и выбирается равным коду N уставки блока 16 N«f -Т.

Например, если N соответствует нсс расположен во втором квадранте, то на параллельные входы счетчнка II поступает код„ соответствующий 89,7°. Одновременно Налнчне двух стдрщнх разрядов в счетчике

II, куда записывается код квадранта, предохраняет преобразователь от сбоев, выражающихся в переполнении разрядов счетчика II, формирующих код угла внутри квадранта.

Нуль-орган 29 и элемент И 31 предназначены для формирования пачки импульсов У1, получаемой от совпадения положительных полуволн опорного напряжения источника 18 с состоянием «I первого выхода счетчика 12. Количество импульсов в пачке задается временным интервалом с помощью счетчика 12 таким, чтобы напряжение не интеграторах 4 и 5 в конце первого такта доходило до «ужиого для требуемой чувствительности уровня.

Работа преобразователя происходит в три такта.

На первом такте на втором выходе счетчика 12 - «1, на первомвыходе - «О. Имлульсы У1 синхронно с положительными полуволнами опорного напряжения источника 18 поступают на управляющие входы коммутаторов 2 и 3. При наличии импульса У1 напряжения с выходов СКД 1 через коммутаторы 2 и 3 поступают на входы интеграторов 4 и 5 и накапливаются там. В паузах между импульсами У1 на входы интеграторов 4 и 5 ничего не поступает и они выполняют роль аналоговых запоминающих устройств. При поступлении сигнала на счетчик 12 со счетчика 11, который находится в режиме постоянного счета, счетчик Г2 увеличивает свое состояние на единицу, на втором выходе счетчика 12 появляется «О. С помощью коммутаторов 2 и 3 прекращается подача напряжений с выходов СКД 1 на интеграторы 4 и 5. При установке на первом выходе счетчика 12 «1 начинается BTOipofl такт.

По фронту сигнала У2 код квадранта, сформированнь1Й на выходах Компаратора 17 и элемента НЕ 24, записывается в ре,гистр 25 и совместно с кодом блока 16 записывается в счетчик 11. Код с выходов регистра 25 подготавливает мультиплексор 28 к пропусканию положительного фронта

сигнала (при ближайшем переходе через ноль напряжения одного из интеграторов) на D-вход триггера 13, который отсутствием «1 на первом выходе счетчика 12 был установлен в состояние «О. Одновременно при появлении «I на первом выходе счетчика

12 с помощью коммутаторов 2 и 3 интеграторы 4 и 5 и инвертор 6 образуют замкнутую петлю - осциллятор. При ближайщем переходе через ноль напряжения одного из иитеграторов 4 и 5 сигнал на выходе мультиплексора 28 принимает состояние «1 и триггер 19, который ранее поддерживался в состоянии «0, переходит по ближайшему фронту импульса генератора 2 в состояние «I, тем самым разрешая запись в регистр 13 кода изсчетчика 11, который накапли вался там в течение интервала осциллирования. Отрицательный фронт импульса генератора 9, пройдя через элементы НЕ 22 и И 21, устанавливает в «О счетчики II и 12 и тем самым устанавливает в «0 триггер 19 по R-входу.

Начинается третий такт. На третьем гакте на выходе элемента ИЛИ 30 появляется «I, н интеграторы 4 и 5 начинают обнуляться. Третий такт продолжается до тех пор, пока сигнал свыхода счетчика 11 г-ге увеличит на единицу состояние счетчика 12, т.е. начнется снова первый такт.

В результате происходит увеличение точности преобразователя за счет компенсации погрешности, вызванной задержанием аналоговых коммутаторов и компараторов, и устранения возможности сбоя при переполнении счетчика 11 при углах, близких к 90, 180, 270, 360°, вследствие изменения постоянных времени иитеграторов.

Экономический эффект от использования предлагаемого преобразователя определяется его техническим преимуществом.

У1 У2 ИЗ V 4. ,

ч

- 9

Г

У2

10

t

LMJ

UL

О

20

iS

16

f

11

13

Т

1(о9

г

Щ

н%

mf-,

.У2

29

12

У2

oq

УЗ

1

30

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Функциональный преобразователь углового положения вала в код | 1975 |

|

SU550664A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство и принцип действия преобразователей аналог - код | |||

| Устройство для усиления микрофонного тока с применением самоиндукции | 1920 |

|

SU42A1 |

Авторы

Даты

1984-10-15—Публикация

1982-12-10—Подача