рой выход читающему 1120322 которого подключен к вы- выход триггера соединен с управляюиими входу реверсивного счетчика, входами второго и третьего коммутаторов

| название | год | авторы | номер документа |

|---|---|---|---|

| Число-импульсный функциональный преобразователь | 1982 |

|

SU1043645A1 |

| Аппроксимирующий функциональный преобразователь | 1983 |

|

SU1160430A1 |

| Вычислительное устройство | 1983 |

|

SU1083187A1 |

| Функциональный преобразовательчиСлА иМпульСОВ B цифРОВОй КОд | 1979 |

|

SU807285A1 |

| Вычислительное устройство | 1983 |

|

SU1080137A1 |

| Устройство для возведения в степень и извлечения корня | 1983 |

|

SU1084790A1 |

| Частотно-импульсный функциональный преобразователь | 1981 |

|

SU995095A1 |

| Измерительный функциональный преобразователь | 1981 |

|

SU983704A1 |

| Устройство для воспроизведения степенных функций | 1983 |

|

SU1095175A1 |

| Преобразователь фаза-код | 1991 |

|

SU1803882A1 |

ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий m -разрядный счетчик, п -разрядный счетчик, причем пл п , реверсивный счетчик, первый коммутатор, генератор,формирователь импульса, первую и вторую группы элементов И, первый, второй и третий элементы ШШ и триггер, вход установки которого соединен с входом выбора режима преобразователя, выход обнуления реверсивного счетчика подключен к входу сброса триггера, выход которого соединен с управляющим входом первого коммутатора и через формирователь импульса с входами сброса и установки гп - и п-разрядных счетчиков, выходы элементов И первой и второй групп подключены соответственно к входам первого и второго элементов ИЛИ, инверсные входы h-разрядного счетчика соединены с потенциальными входами элементов И первой группы, отли ч ающий ся тем, что, с целью расширения функциональных возможностей путем вычисления дополнительных функций ,ln X и V , в него введены вычитатель, делитель, второй и третий коммутаторы и элемент задержки, причем информационный вход преобразова теля соединен с первым информационным входом первого коммутатора и первым входом третьего элемента ИЛИ, выход первого элемента ИЛИ подключен к первому входу вычитателя и через элемент задержки к второму входу третьего элемента ИЛИ, выход которого соединен с первым информационным входом второго коммутатора, выход которого подключен к счетному входу m-разрядного счетчика, прямые выходы старших (Л разрядов которого соединены с импульсными входами элементов И второй группы, потенциальные входы которых подключены к прямым выходам младших разрядов т-разрядного счетчика, прямой выход (h - i+ I) разряда которого соединен с импульсным входом элементов И первой группы, где i- инверсный выход п -разрядного счетчика ( i , 1,2,... ,п) , выход генератора подключен к входу делителя и к первому информационному входу третьего коммутатора, первый выход которого соединен с суммирующим входом реверсивного счетчика, выход делителя подключен к второму информационному входу второго коммутатора и к второму входу вычитателя, выход которого соединен с вторым информационным входом первого коммутатора, выход которого подключен к счетному входу п -разрядного счетчика, выход второго элемента ИЛИ соединен с вторым информационным входом третьего коммутатора, вто

Изобретение относится к автомати ке, вычислительной технике и может быть использовано в качестве специа лизированного вычислителя, входящего в состав устройств автоматики управления и контроля.

Известно устройство для вычисления логарифмов чисел, содержащее два счетчика, регистор, коммутатор, восемь элементов И-НЕ, триггер, пять элементов И и элемент ИЛИ tl.

Недостатком данного устройства является способность вычислять только логарифмическую функцию.

Наиболее близким к изобретению по технической сущности является вычислительное устройство, содержащее два счетчика, реверсивный счетчик, коммутатор , две групшз элементов И, сумматор-вычитатель, генератор, формирователь, триггер, шесть элементов И и пять элементов ИЛИ 2.

Недостатком известного устройства является неспособность вычислять

л

функции вида p klnxиv jf-kenx

Цель изобретения - расширение функциональных возможностей путем вычисления дополнительных функций ,ln2x , и у),- .

Поставленная цель достигается тем, что в цифровой функциональный преобразователь, содержащий m-разрядный счетчик, п-разряднь й счетчик, причем -п-,г , реверсивный счетчик, первый коммутатор, генератор, формирователь импульса, первую и втрую группы элементов И, первый, второй и третий элементы ИЛИ и триггер вход установки которого соединен с входом выбора режима преобразователя, выход обнуления реверсивного счетчМка подключен к входу сброса триггера, выход которого соединен с управляющим входом первого коммутатора и через формирователь импульса с входами сброса и установки m - и

п-разрядных счетчиков, выхода элементов И первой и второй групп подключены соответственно к входам первого и второго элементов ИЛИ, инверсные

выходы п-разрядного счетчика соединены с потенциальными входами элементов И первой группы, введены вычитатель, делитель, второй и третий коммутаторы и элемент зад.ержки, причем информационный вход преобразователя соединен с первым информационным входом первого коммутатора и первым входом третьего элемента ИЛИ, выход первого элемента ИЛИ подключен

к первому входу вычитателя и через элемент задержки к второму входу третьего элемента ИЛИ, выход которого соединен с первым информационным входом второго коммутатора, выход которого подключен к счетному входу m -разрядного счетчика, прямые выходы старших,разрядов которого соединены с импульсными входами элементов И второй группы, потенциальHJbie входы которых подключены к прямым выходам г-шадших разрядов гп-разряд:ного счетчика, прямой выход (п - i + К I) разряда которого, соединен с импульсным входом элементов И первой группы, где i - инверсный выход п-разрядного счетчика (i 1,2,-. .,,п), выход генератора подключен к входу делителя и к первому информационному входу третьего коммутатора, первый выход которого соединен с суммирующим входом реверсивного счетчика, выход делителя подключен к второму информационному входу второго коммутатора и к

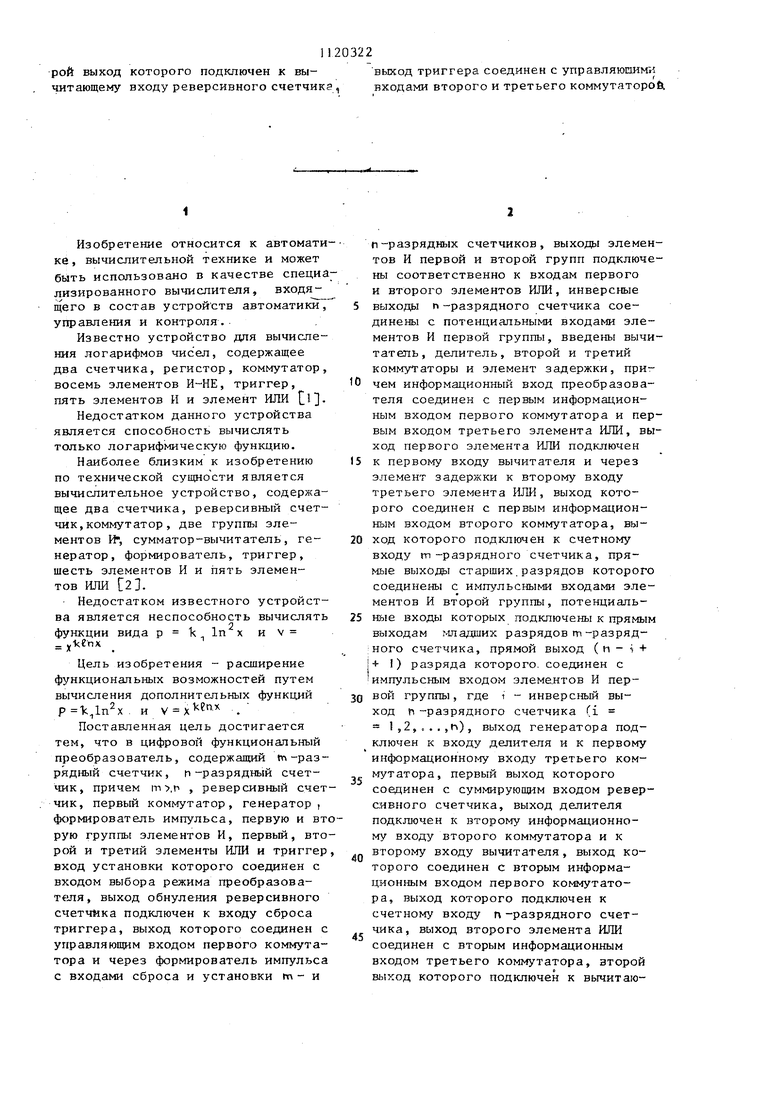

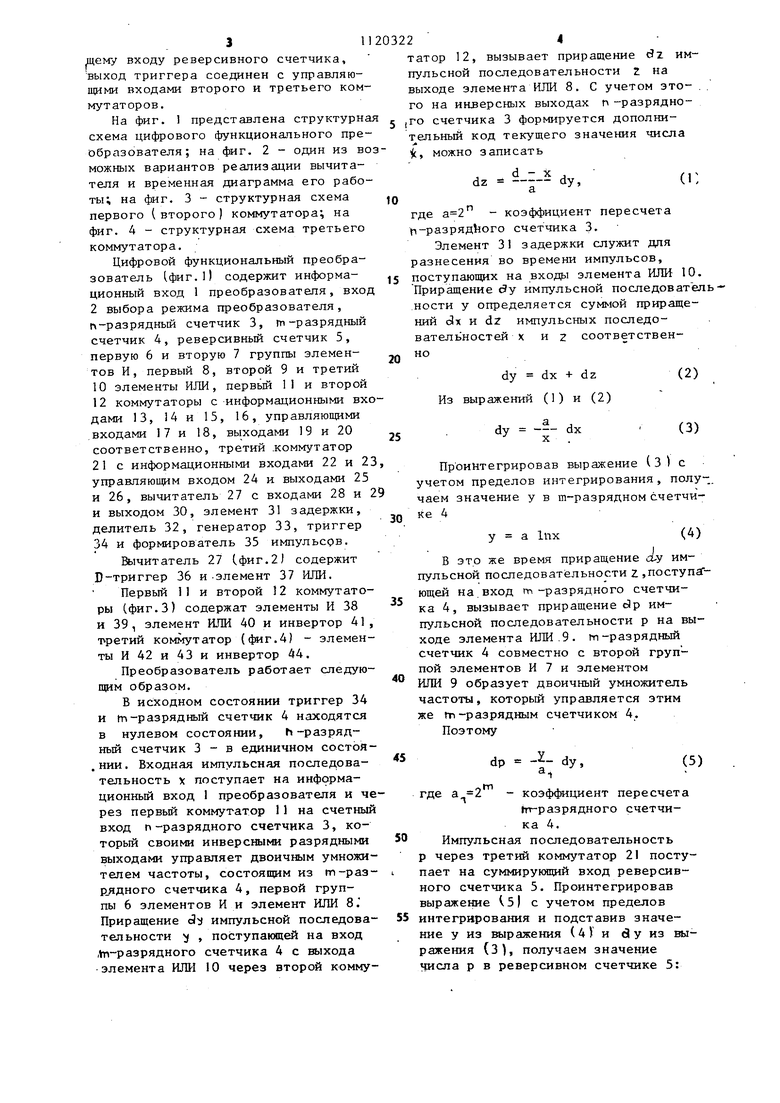

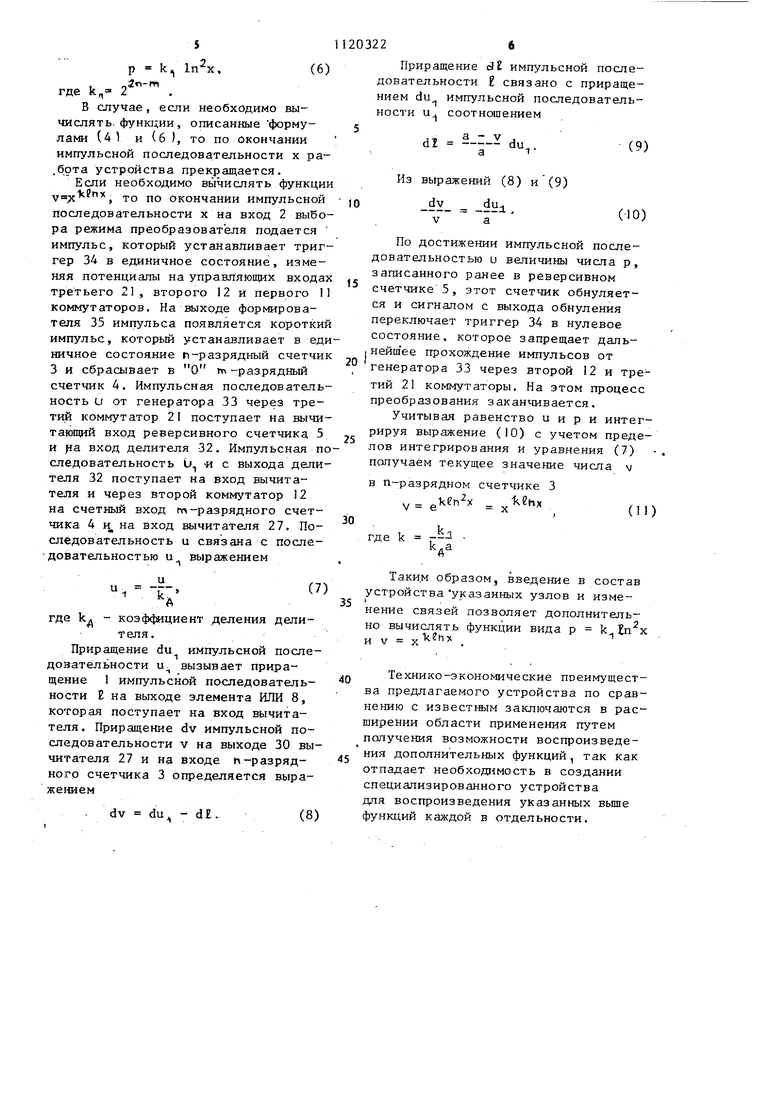

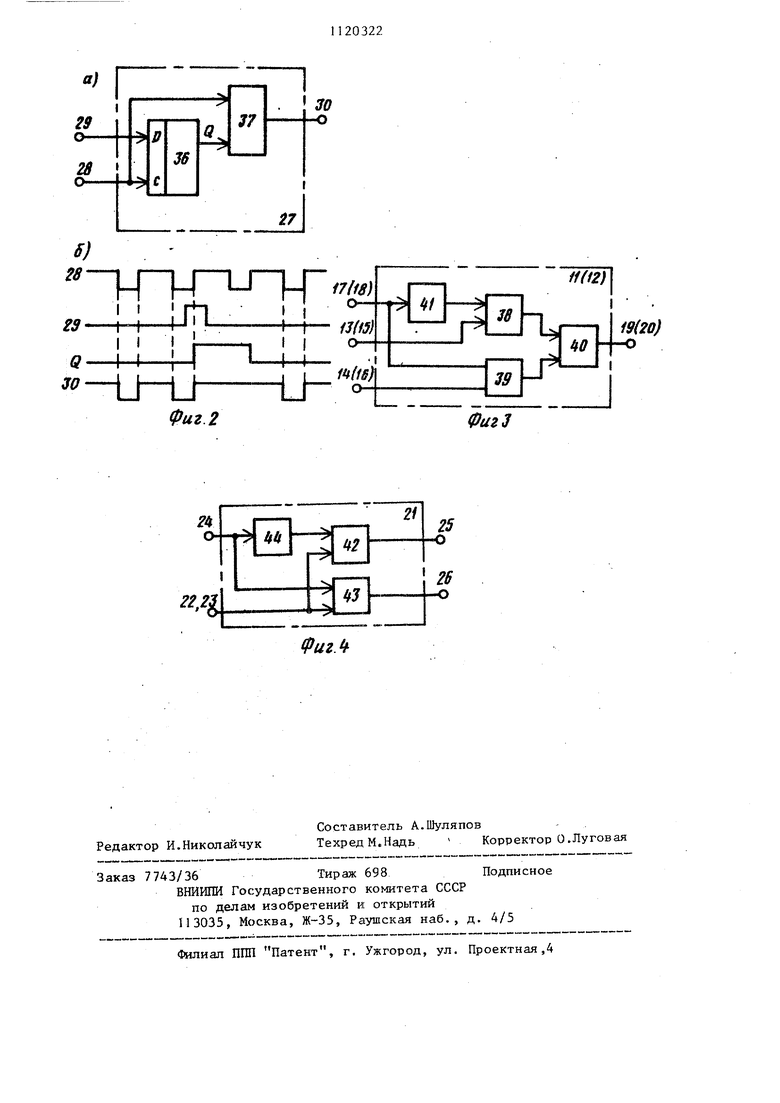

второму входу вычитателя, выход которого соединен с вторым информационным входом первого коммутатора, выход которого подключен к счетному входу rv -разрядного счетчика, выход второго элемента ИЛИ соединен с вторым информационным входом третьего коммутатора, второй которого подключен к вычитаю|1цему входу реверсивного счетчика, выход триггера соединен с управляющими входами второго и третьего коммутаторов. На фиг. 1 представлена структурна схема цифрового функционального преобразователя; на фиг. 2 - один из во можных вариантов реализации вычитателя и временная диаграмма его работы; на фиг. 3 - структурная схема первого (второго) коммутатора, на фиг. 4 - структурная схема третьего коммутатора. Цифровой функциональный преобразователь 1ФИГ.1) содержит информационный вход 1 преобразователя, вход 2 выбора режима преобразователя, г -разрядный счетчик 3, m-разрядный счетчик 4, реверсивный счетчик 5, первую 6 и вторую 7 группы элементов И, первый 8, второй 9 и третий 10 элементы ИЛИ, первый II и второй 12 коммутаторы с информационными вхо дами 13, 14 и 15, 16, управляющими входами 17 и 18, выходами 19 и 20 соответственно, третий .коммутатор 21 с информационными входами 22 и 2 управляющим входом 24 и выходами 25 и 26, вычитатель 27 с входами 28 и и выходом 30, элемент 31 задержки, делитель 32, генератор 33, триггер 34 и формирователь 35 импульсов. Вычитатель 27 Сфиг.2) содержит D-триггер 36 и-элемент 37 ИЛИ. Первый 11 и второй 12 коммутаторы (фиг.З) содержат элементы И 38 и 39, элемент ИЛИ 40 и инвертор 41, peтий коммутатор (фиг.4) - элементы И 42 и 43 и инвертор 44. Преобразователь работает следующим образом. В исходном СОСТОЯНИЙ триггер 34 и m-разрядный счетчик 4 находятся в нулевом состоянии, h-разрядный счетчик 3 - в единичном состоя. НИИ. Входная импульсная последовательность X поступает на информационный вход 1 преобразователя и че рез первый коммутатор 11 на счетный вход п-разрядного счетчика 3, который своими инверсными разряднь:ми выходами управляет двоичным умножителем частоты, состоящим из т-разр.ядного счетчика 4, первой группы 6 элементов И и элемент ИЛИ 8. Приращение dij импульсной последовательности , поступающей на вход ,Уп-разрядного счетчика 4 с выхода элемента ИЛИ 10 через второй комму14 татор 12, вызывает приращение tJz импульсной последовательности 2 на выходе элемента ИЛИ 8. С учетом это- . го на инверсных выходах п-разрядного счетчика 3 формируется дополнительный код текущего значения числа ic, можно записать где - коэффициент пересчета ri-разрядного счетчика 3Элемент 31 задержки служит для разнесения во времени импульсов, поступающих на входы элемента ИЛИ 10. Приращение dy импульсной последователь- ности у определяется суммой приращений 3х и dz импульсных последовательностей х и 2 соответственdy dx + dz выражений (1) и (2) а dy Проинтегрировав выражение (З) с учетом пределов интегрирования, полу-. чаем значение у в т-разрядном счетчике 4 у а Inx(4) В это же время приращение о-у импульсной последовательности Z ,поступагющей на вход m -разрядного счетчика 4, вызывает приращение dp импульсной последовательности р на выходе элемента ИЛИ. 9. tn-разрядный счетчик 4 совместно с второй группой элементов И 7 и элементом ИЛИ 9 образует двоичный умножитель частоты, который управляется этим же m-разрядным счетчиком 4. Поэтому - коэффициент пересчета Нт-разрядного счетчика 4. Импульсная последовательность р через третий коммутатор 21 поступает на суммирующий вход реверсивного счетчика 5. Проинтегрировав выражение {5} с учетом пределов интегрирования и подставив значение у из илражения (4) и в у из выражения (З), получаем значение числа р в реверсивном счетчике 5: р k , где k, В случае, если необходимо вычислять, фунюлии, описанные формулами (4V и (б ), то по окончании импульсной последовательности к ра.бота устройства прекращается. Если необходимо вычислять функци , то по окончании импульсной последовательности к на вход 2 выбо ра режима преобразователя подается импульс, который устанавливает триг гер 34 в единичное состояние, изменяя потенциалы на управляющих входа третьего 21, второго 12 и первого 1 коммутаторов. На выходе формирователя 35 импульса появляется коротки импульс, который устанавливает в ед ничное состояние h-разрядный счетчи 3 и сбрасывает в О пл -разрядньй счетчик 4. Импульсная последователь ность и от генератора 33 через третий коммутатор 21 поступает на вычи тающий вход реверсивного счетчика 5 и а вход делителя 32. Импульсная п следовательность и « с выхода дели теля 32 поступает на вход вычитателя и через второй коммутатор 12 на счетный вход м-разрядного счетчика 4 j|, на вход вычитателя 27. Последовательность U связана с последовательностью и выражением ,- V где kj, - коэф(|ициент деления делителя. Приращение du импульсной последовательности U; вызывает приращение 1 импульсной последовательности на выходе элемента ИЛИ 8, которая поступает на вход вычитателя. Приращение dv импульсной последовательности V на выходе 30 вычитателя 27 и на входе п-разрядного счетчика 3 определяется выражегтаемdv du - d. 226 Приращение dE импульсной последовательности связано с приращением du импульсной последовательности и соотнощением , а - V . dl du а1 Из выражений (8) и(9) dv du.j По достижении импульсной последовательностью и величины числа р, записанного ранее в реверсивном счетчике 5, этот счетчик обнуляется и сигналом с выхода обнуления переключает триггер 34 в нулевое состояние, которое запрещает дальнейшее прохождение импульсов от генератора 33 через второй 2 и третий 21 коммутаторы. На этом процесс преобразования заканчивается. Учитывая равенство и и р и интегрируя выражение (10) с учетом пределов интегрирования и уравнения (7) получаем текущее значение числа v в п-разрядном счетчике 3 V е х где k p-J Таким образом, введение в состав устройствауказанных узлов и изменение связей позволяет дополнительно вычислять функции вида р k и V - . Технико-экономические преимущества предлагаемого устройства по сравнению с известным заключаются в расширении области применения путем получения возможности воспроизведения дополнительных функций, так как отпадает необходимость в создании специализированного устройства для воспроизведения указанных вьппе функций каждой в отдельности.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления логарифмов чисел | 1978 |

|

SU746540A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3545326, кп | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-10-23—Публикация

1983-07-21—Подача