ход старшего разряда первого счетчи ка соединен с импульсным входом 1-го элемента И первой групп л, потенциальный вход которого подключен к инверсному выходу младшего разряда второго счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в степень и извлечения корня | 1983 |

|

SU1084790A1 |

| Вычислительное устройство | 1983 |

|

SU1080137A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1120322A1 |

| Число-импульсный функциональный преобразователь | 1982 |

|

SU1043645A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Линейный аппроксиматор | 1983 |

|

SU1157548A1 |

| Цифровая система регулирования скорости центробежного аппарата | 1983 |

|

SU1176302A1 |

| Цифровой адаптивный линейный интерполятор | 1982 |

|

SU1095189A1 |

| Устройство для регулирования расхода | 1986 |

|

SU1377832A1 |

| Устройство для вычисления функций у=aRcSINx и у=aRccoSx | 1980 |

|

SU935949A1 |

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержскцее первый и второй счетчики, реверсивный счетчик, коммутатор/ первую и вторую группы элементов И, генератор опорной частоты, формирователь импульса, триггер, первый, второй, третий, четвертый, пятый и шестой элементы И, первый, второй, третий и четвертый элементы ИЛИ, причем управляющий вход устройства соединен с входом установки триггера, прямой выход которого через формирователь импульса подключен к управляющим входам первого и второга счетчиков, выходы элементов И первой и второй групп соединены соответственно с входами первого и второго элементов ИЛИ, выход старшего разряда первого счетчика подключен к импульсному входу |-го элемента И второй группы, где i- количество разрядов первого счетчика,потенцисшьный вход которого .соединен с выходом младшего разряда кокмутатора, первый и второй информационные входы которого подключены соответственно к первому и второму информационным входам устройства, выход второго элемента ИЛИ соединен с первыми входами первого и второго элементов И, выходы которых подключены соответственно к входам сложения и вычитания реверсивного счетчика, информационный вход первого счетчика соединен с выходом третьего элемента ИЛИ, первый и второй входы которого подключены соответственно к выходам третьего и четвертого элементов И, инверсный выход триггера соединен с первыми входами третьего и пятого элементов И, информационный вход второго счетчика подключен к выходу четвертого элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами пятого и шестого элементов И, прямой выход триггера подключен к первым входам четвертого и шестого элементов И, третий информационный вход устройства ел соединен с вторым входом пятого элемента И, выход генератрра опорной частоты подключен к второму входу . четвертого элемента И, отличающееся тем, что, с целью расшире ния функциональных возможностей за счет., вычисления функции вида X, в него дополнительно введены сумматор-вычитатель и пятый элемент 00 ИЛИ, первый и второй входы которого 00 соединены соответственно с выходами четвертого и пятого элементов И, а выход пятого элемента ИЛИ подклю00 чен к первому информационному входу сумматора-вычитателя, второй инфор мационный вход которого соединен с выходом первого элемента ИЛИ, выход реверсивного счетчика соединен с входом сброса триггера, инверсный выход которого подключен к второму входу первого элемента И и первому управляющему входу сумматора-вычитателя, прямой выход триггера соединен с управляющим входом коммутатора, с вторым входом второго элемента И и с вторым управляющим входом сумматора-вычитателя, выход которого подключен к вторым входам третьего и шестого-элементов И, ВЬ1

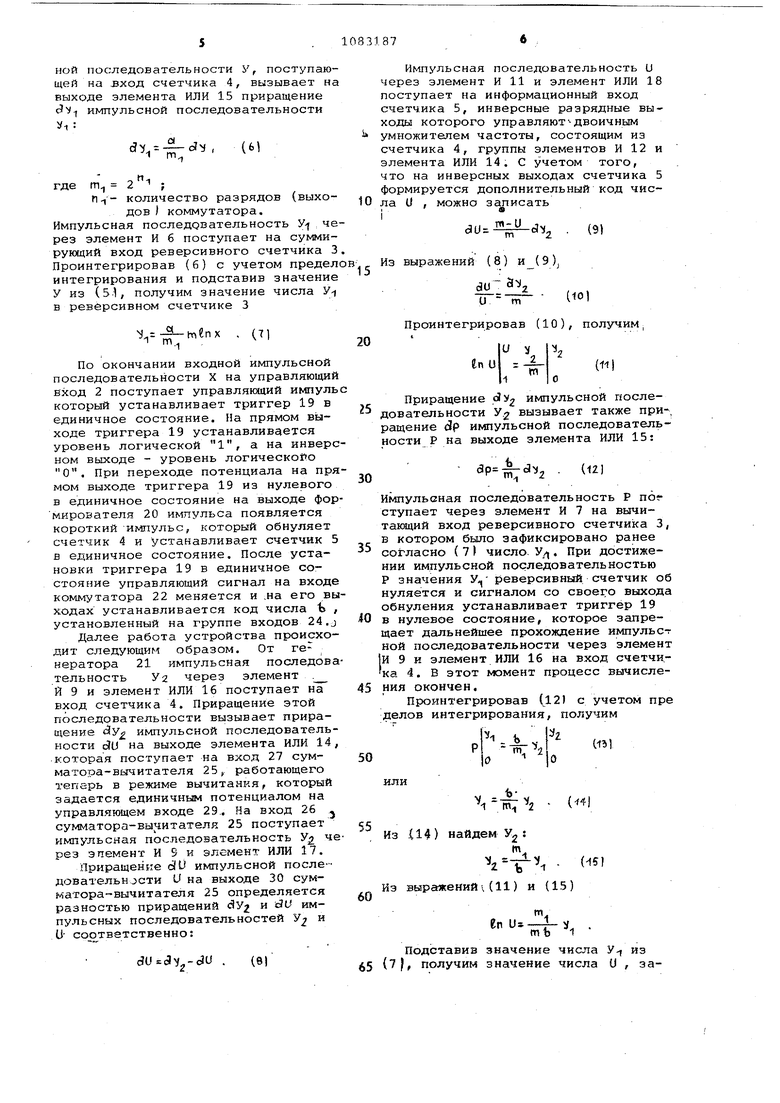

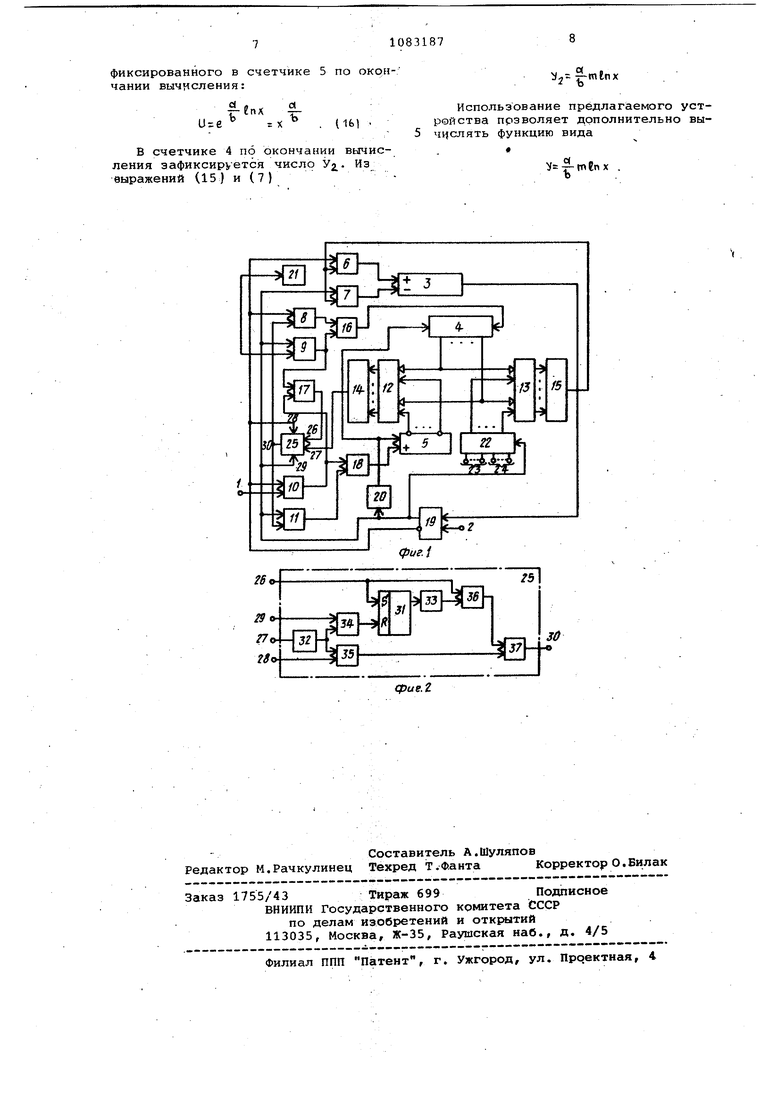

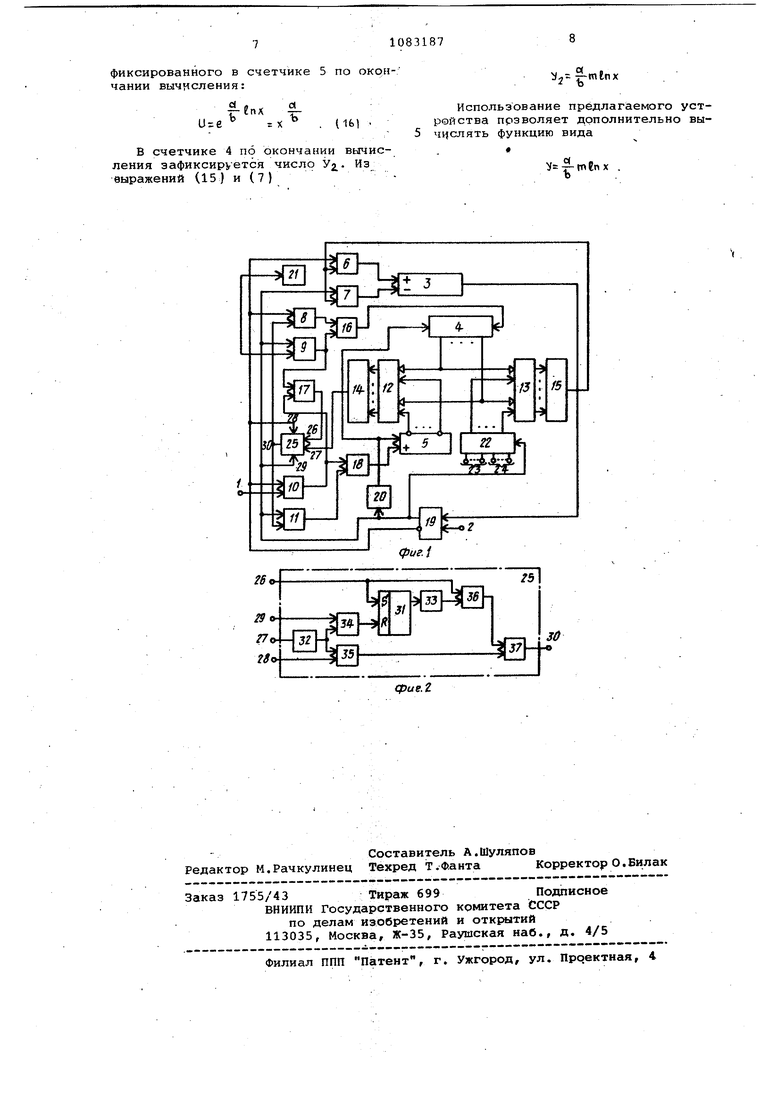

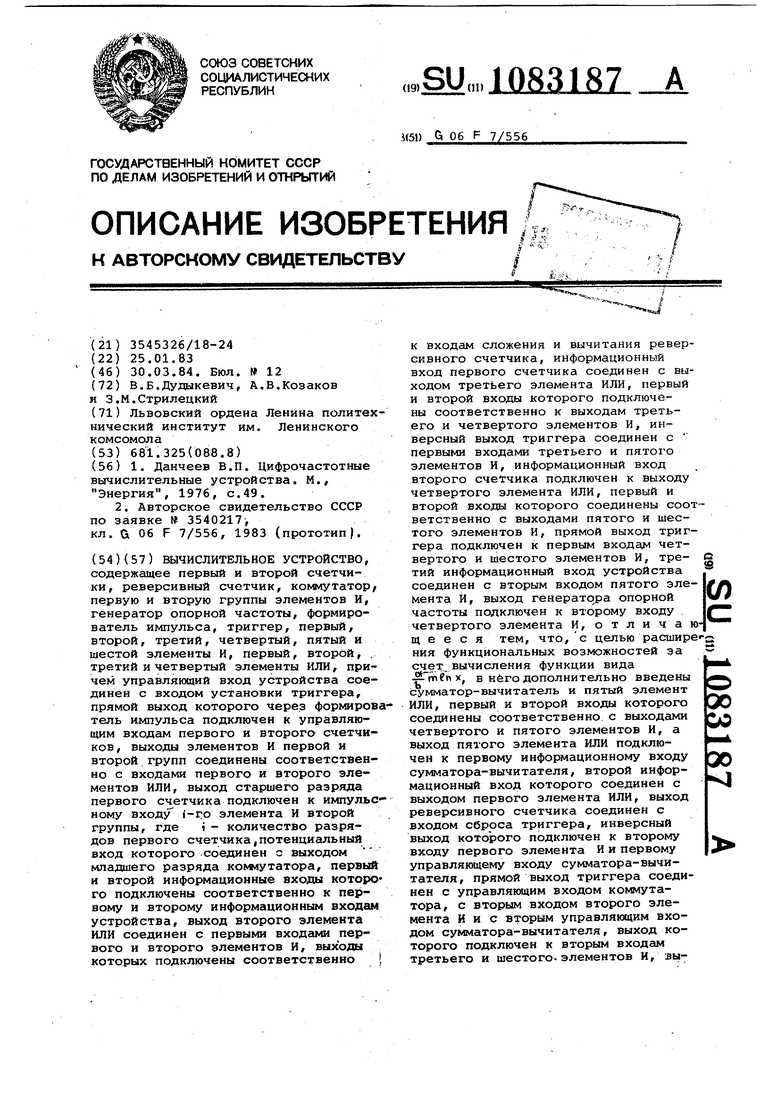

Изобретение относится к автоматике, вычислительной и измерительной технике и может быть использовано в качестве специализированного вычислителя, входящего в состав устройств автоматики, управления и контроля. Известно устройство для воспроизведения степенной зависимости V-Л с цифровым регулируемым показателем, содержащее информационный вход, пять счетчиковj регистр управляющего кода, схему сравнения кодов, две группы элементов И, два элемента ИЛИ и счетчик-делитель Недостатками данного устройства являются невозможность вычисления функций с дробным показателем степени и большие аппаратурные затраты Наиболее близким по технической сущности к предлагаемому является вычислительное устройство, содержащее реверсивный счетчик, два счет чика, коммутатор, генератор опорной частоты, формирователь импульса, дв триггера, две группы элементов И, вы читатель, шесть элементов И и четыре элемента ИЛИ С2. Недостатком известного устройс-рва является невозможность вычисления функции вида ,, Сп х . ,-:-,. - b Цель изобретений - расширение функциональных возможностей за счет - Ы йычисления функции вида- твпх . . Прставленная цель достигается тем, что в вычислительное устройстве содержащее пердый и второй счетчики, реверсивный счетчик, коммутатор первую и вторую г|руппы элементбВ И, reHepaiTop опорной частоты, формирователь импульса, триггер, первый,вто рой, третий, четвертый, пятый и шеетой элементы И, первый, второй, третий и четвертый .ты ИЛИ, причем управляющий вход устройства соединён с входом установки триггера, прямой выход которого через форлмрой тель импульса подключен к упра8Ляю ци входам первого и второго счетчиков, элементов И первой и второй . групп соответственно с вхо дг1ми первого и второго элементов ИЛИ выхсщ Cfai siero разряда первого счетчика- подключен к юшульсному входу i-го элементна И второй группы, где f- количество разрядов первого счетчика, потенциальный вход которого соединен с выходом младшего разряда коммутатора, первый и второй информационные входы которого подключены соответственно к первому и второму ииформёщионным входам устройства, выход второго.элемента ИЛИ соединен с первыми входами первого и второго элементов И, выходы которых подключены соответственно к входам сложения и вычитания реверсивного счетчика, информационный вход первого счетчика соединен с выходом третьего элемента ИЛИ, первый и второй входы которого подключены соответственно к выходам третьего и четвертого элементов И, инверсный выход триггера соединен с первыми входами третьего и пя:тоГо элементов И, информационный вход второго счетчика подключен к выходу четвертого .элемента ИЛИ, первый и второй входы которого соединены соответственно- с выходами пятого и шестого элементов И, прямой выход триггера подключен к первым входам четвертого и шестого элементов И, третий информационный вход устройства соединен с вторым входом пятого элемента И, выход генератора опорной частоты подключен к второму входу четвертого элемента И, дополнительно введены сумматор-вычитатель и пятый элемент ИЛИ, первый и второй входы KOTopor j соединены соответственно с выходами четвертого и пятого элементов И,, а. выход пятого элемента ИЛИ подключен к первому информационному входу сукфлатора-вычитателя, второй информационный вход которого соединен с выходом первого элемента ИЛИ, выход реверсивного счетчика соединен с входом сброса триггера, инверсный выход которого подключен к второму входу первого элемента И и первому управлякнцему входу сумматора-вычитателя, прямой выход триггера соединен с управляющим входом коммутатора, с вторым входом второго элемента И и с вторым управляющим входом сумматора-вычитателя, выход которого подключен к вторым входам третьего и шестого элементов И, выход старшего разряда первого счетчика соединен с импульсным входом 1-го элемента И первой группы, потенцисшьный вход которого подключен к инверсному выходу младшего разряда второго счетчика. На фиг; 1 представлена структурная схема предлагаемого устройства; на фиг, 2 - вариант реализации сумматора-вычитателя. Вычислительное устройство (фиг.1 содержит третий информационный вход 1I управляющий вход.2, реверсивный .счетчик 3, первый и второй счетчики и 5, перйый , второй, третий, четвер пятый и шестой элементы И 6-11 соответственно, первую и вторую группы 12 и 13 элементов И, первый, вто рой, третий, пятый и четвертый эле-менты ИЛИ 14-18 соответственно, триг гер 19, формирователь 20 импульса, генератор 21 опорной частоты, комму татор 22 с группами входов 23 и 24, импульсный сумматор-вычитатель 25 с информационными входами 26 и 27, управляющими входами 28 и 29 и выходом 30. Импульсньй сумматор-вычитатель 2 (фиг.2 I содержит триггер 31, первый и второй элементы 32 и 33 эадержки, первый, второй и третий элементы И 34, 35 и 36 и элемент ИЛИ 37. Сумматор-вычитатель 25 (фиг.2) работает следующим образотл. В исходном положении триггер 31 находится в единичном состоянии или устанавливается в это состояние первым импульсом, поступающим на ин формационный вход 26. В режиме суммирования на управляющий вход 28 поступает единичный потенциал, а на управляющий вход 29 - нулевой потен циал, импульсные последовательнорти с информационных входов 26 и 27 через элвменты И 36 и 35 соответственно поступают на элемент ИЛИ 37 который производит их суммирование. Элемент 32 задержки исключает возможность совпадения импульсов этих импульсных последовательностей и задерживает импульсы, поступающие на информационный вход 27 на вреМя, которое чуть больше длительности импульса на информационном входе 26. В режиме вычитания на управляющем входе 29 присутствует единичный потенциал, а на управлякщем входе 28 - нулевой. Импульсная последовательность с Входа 26 прохо дит через элементы 36 и 37 на выход 30. При поступлении импульса на вход 27 31 устанавливается в нулевое состояние, запрещая прохождение очередного.импульра с входа 26 через элемент И. Этот очередной импульс с входа 26 вновь устанавливает триггер 31 в единичное состояние, которое через неко.торое появляетря на выходе элемента 33 задержки. Этот импульс с входа 2ёне проходит на выход. Из импульсной последовательности, поступающей на вход 26, вычитается один импульс. Элемент 33 задержки служит для того, чтобы импульс с входа 26, который должен быть вычтен, не разрешал себе прохождение через элемент , установив триггер своим передним фронтом в единичное состояние. Вычислительное устройство (фиг.1) работает сУ1едующим образом. В исходном положении триггер 19 и счетчик 4 находятся в нулевом РОстоянии, а счетчик 5 - в единичном. Входная икшульсная последовательность X поступает на информационный вход 1 и через элементы И 10 и ИЛИ 18 на информационный вход счетчика 5. Этот счетчик своими инверсными разрядными выходами управляет двоичным умножителем частоты, состоящим из счетчика4,группы элементов И 12 и элемента ИЛИ 14. Приращение dy импульсной последовательности У, постуг пающей на вход счетчика 4 с выхода 30 импульсного сумматора-вычитателя 25 через элементы И 8 и ИЛИ 16 вызывает на выходе элемента ИЛИ 14 приращение dZ импульсной последователь-. ности Z . С учетом того, что на инверсных выходах счетчика 5 форми- руетря дополнительный код текущего значения числа X, можно записать dz.e. где m - коэффициент пересчета счетчиков 4 и 5. Импульсный сумматор-вы.читатель 25 работает в режиме сум- . мирования, который задается единичным потенциалом на управляющем входе 28 . Приращение импульсной последовательности Определяется суммой приращений dx и dZ соответственно: , + dlZ. (2) Из выражений (1) и (2) Проинтегрировав (3) с учетомпределов интегрирования, получим .текущее значение чирла У в рчетчике 4 у(.е.х|;.. W Окончательно V rotn;c В это же время управляющим сигналом с прямого выхода триггера 19 на вы-. ходы коммутатора 22 передается код числа Q Р группы входов 23. Выходы коммутатора управляют двоичньи умножителем частоты, РОРТОЯВЩМ иэ рчетчика 4, группы элементов И 13 и элемента ИЛИ 15. Приращение А ИАШульрной последовательности У, поступающей на ход счетчика 4, вызывает на выходе элемента ИЛИ 15 приращение импульсной последовательности Vi : m, 2 ; П-,- количество разрядов (выходов) коммутатора. Импульсная последовательность У че рез элемент И б поступает на суммирующий вход реверсивного счетчика 3 Проинтегрировав (б) с учетом предел интегрирования и подставив значение У из (5-1, получим значение числа Ув реверсивном счетчике 3 По окончании входной импульсной последовательности X на управляющи вход 2 поступает управляющий импул который устанавливает триггер 19 в единичное состояние. На прямом выходе триггера 19 устанавливается уровень логической 1, а на инвер ном выходе - уровень логическог о О, При переходе потенциала на пр мом выходе триггера 19 из нулевого в единичное состояние на выходе фор мирозателя 20 импульса появляется короткий импульс, который обнуляет счетчик 4 и устанавливает счетчик 5 в единичное состояние. После установки триггера 19 в единичное состояние управляющий сигнал на входе коммутатора 22 меняется и .на его вы ходах устанавливается код числа Ъ установленный на группе входов 24.j Далее работа устройства происходит следующим образом. От генератора 21 импульсная последова тельность У2 через элемент . И 9 и элемент ИЛИ 16 поступает на вход счетчика 4. Приращение этой последовательности вызывает приращение dy импульсной последовательности dU на выходе элемента ИЛИ 14 которая поступает на вход 27 сумматора-вычитателя 25, работающего теперь в режиме вычитания, который задается единичным потенциалом на управляющем входе 29.. На вход 26 cyм aтopa-вычитaтeля 25 поступает импульсная последовательность У2 че рез элемент И 5 и элемент ИЛИ 17. Приращение dIU импульсной последовательности U на выходе 30 сумматора Вычитателя 25 определяется разностью приращений «Яу и dU импульсных последовательностей У и U соответственно: . (в| Иьтульсная последовательность U через элемент И 11 и элемент ИЛИ 18 поступает на информационный вход счетчика 5, инверсные разрядные выходы которого управляют двоичным умножителем частоты, состоящим из счетчика 4, группы элементов И 12 и элемента ИЛИ 14. С учетом того, что на инверсных выходах счетчика 5 формируется дополнительный код числа и , можно записать m-U Из выражений (8) и аи Проинтегрировав (10), получим, Приращение .oJv импульсной последовательности У.2 вызывает также приращение dp импульсной последовательности Р на выходе элемента ИЛИ 15: Импульсная последовательность Р по;ступает через элемент И 7 на вычитающий вход реверсивного счетчика 3, в котором было зафиксировано ранее согласно ( 7 число У,.. При достижении импульсной последовательностью Р значения реверсивный счетчик об нуляется и сигналом со своего выхода обнуления устанавливает триггер 19 в нулевое состояние, которое запрещает дальнейшее прохождение импульсной последовательности через элемент И 9 и элемент ИЛИ 16 на вход счетчика 4. В этот момент процесс вычисления окончен, Проинтегрировав (12) с учетом пре делов интегрирования, получим 1 . Ъ , р2 О - |о V i m 2 Из (14) найдем m - И5) Из выражений-(11) и (15) en Ui-4 mfe 1 Подставив значение числа У-, из (Т}г получим значение числа U , зафиксированного в счетчике 5 по окончании выч сления:

епх

Ure

X . (ifel

В счетчике 4 по окончании вьлЧисления зафиксируется число У2.выражений (15) и (7)гво

2 -mEnx

Использование предлагаемого устройства позволяет дополнительно выч11слять функцию вида

X

#

. ъ

р

/5

г

фиг.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Данчеев В.П | |||

| Цифрочастотные вычислительные устройства, М., Энергия, 1976, с.49 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке W 3540217, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-03-30—Публикация

1983-01-25—Подача