О

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1983 |

|

SU1107131A1 |

| Число-импульсный функциональный преобразователь | 1982 |

|

SU1043645A1 |

| Аппроксимирующий функциональный преобразователь | 1983 |

|

SU1160430A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Синхронный фильтр | 1983 |

|

SU1131028A1 |

| Функциональный преобразователь кода в частоту | 1975 |

|

SU547772A1 |

| Цифровая система управления электроприводом | 1986 |

|

SU1334102A1 |

| Преобразователь двоичных кодов угла и дальности в двоично-десятичные коды | 1987 |

|

SU1432782A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1246091A1 |

| Цифровой прибор для тензометрических весов | 1980 |

|

SU934233A1 |

Использование: измерительная техника, измерение фазового сдвига в широком диапазоне частот. Сущность изобретения: устройство содержит 2 входных формирователя (1, 2), 1 блок управления (3), 1 генератор тактовых импульсов (4), 2 ключа (5, 14), 1 схема вычитания (6), 1 коммутатор (7), 3 комбинационных элемента И-ИЛИ (8, 9, 12), 1 суммирующий счетчик (10), 1 реверсивный счетчик (11), 1 управляемая схема вычитания

со

С

00

о

со

00

00

Ю

Фие.1

Изобретение относится к цифровой измерительной технике и может быть использовано для точного измерения фазового сдвига в широком диапазоне частот.

Цель изобретения - повышение быстродействия.

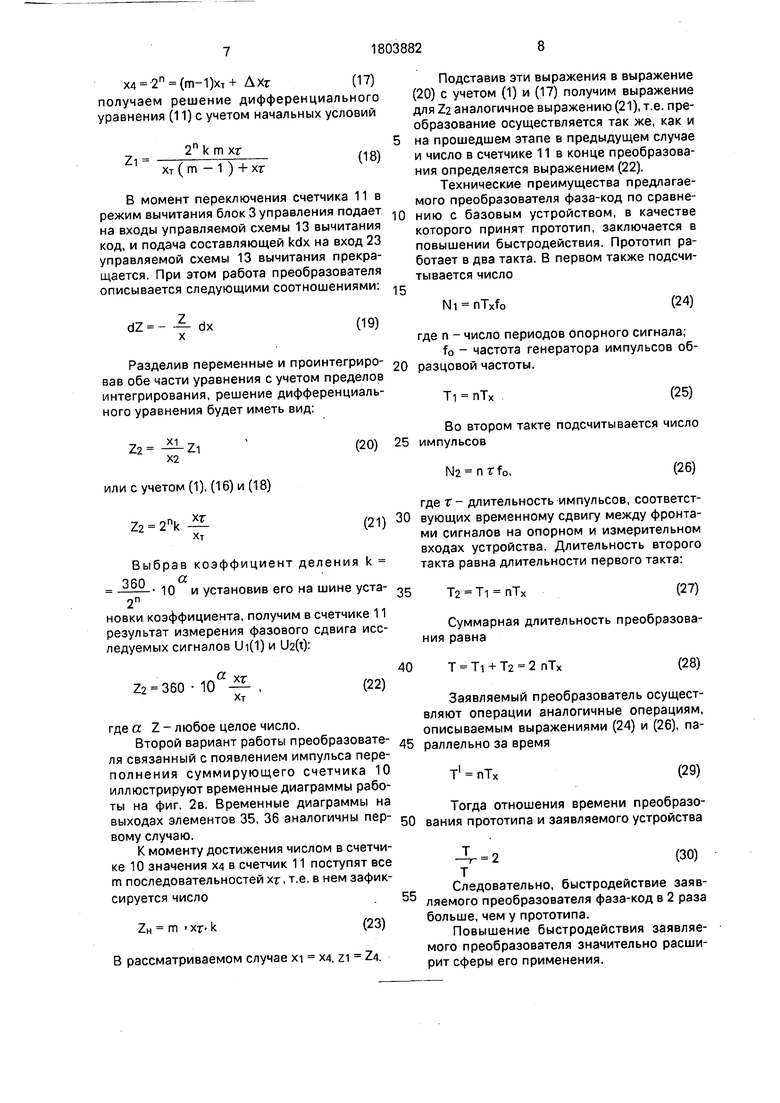

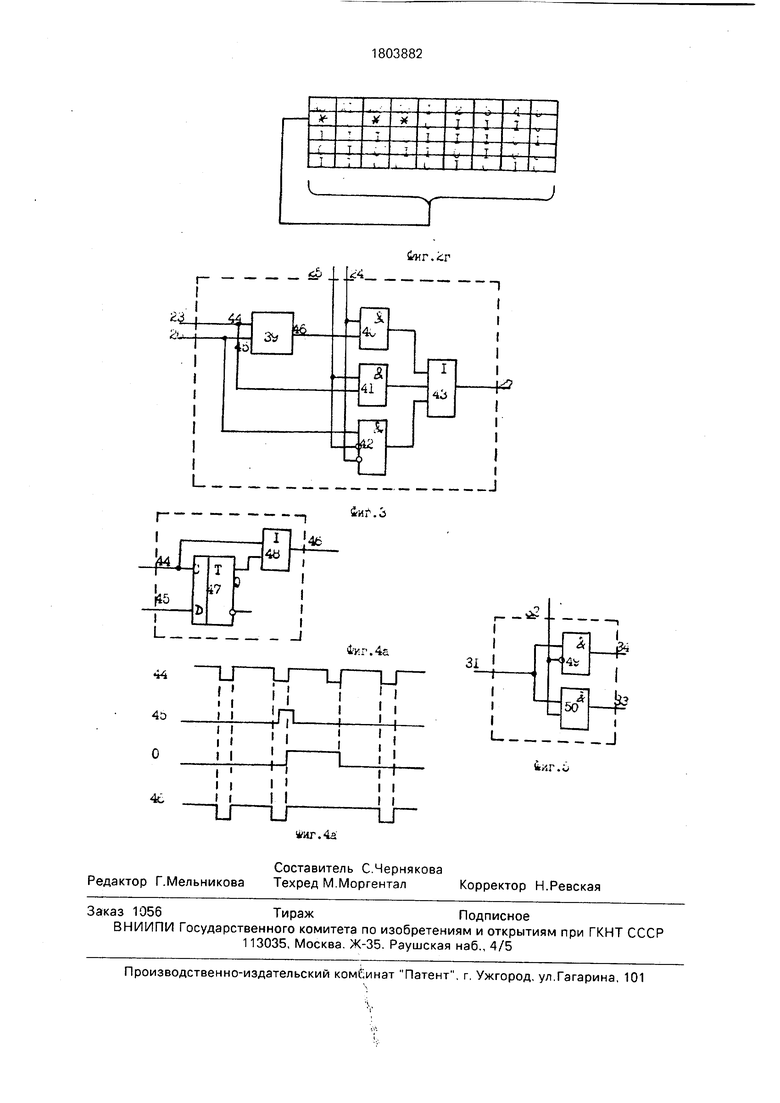

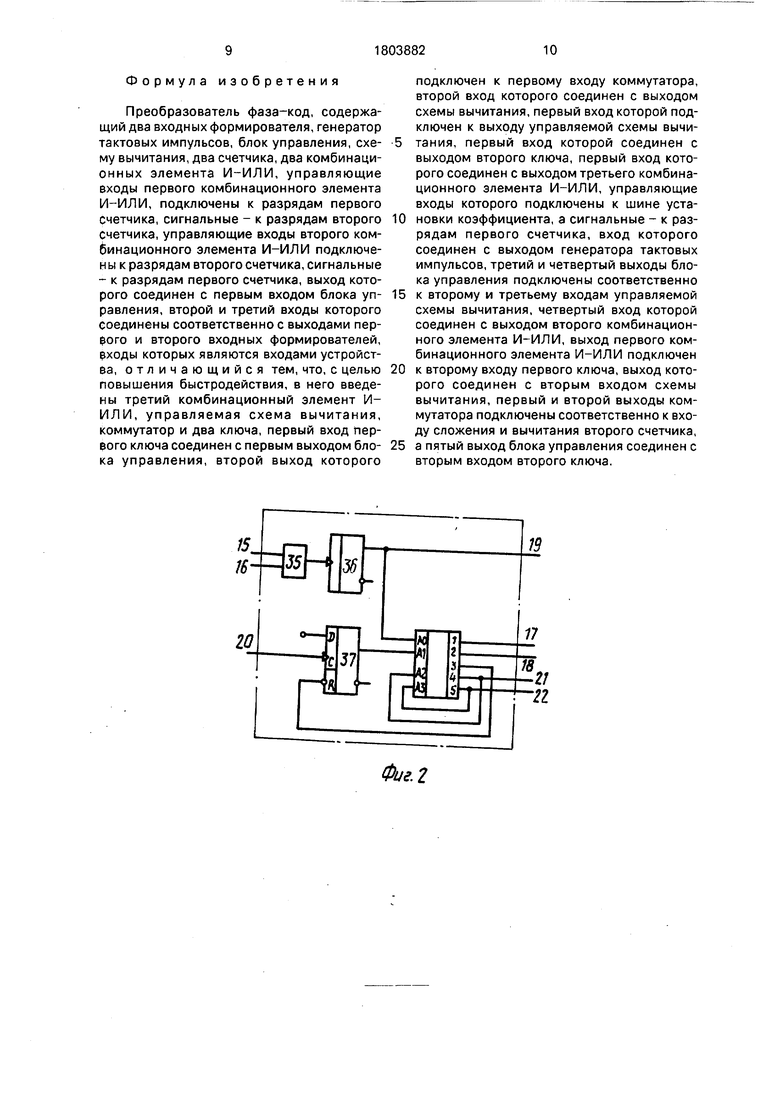

Структурная схема преобразователя фаза-код представлена на фиг. 1. На фиг. 2 а)-г) - одна из возможных реализаций блока управления, временные диаграммы работы и карта прошивки ПЗУ; на фиг. 3 - пример реализации управляемой схемы вычитания; на фиг. 4 а)-б) - реализация и временные диаграммы работы схемы вычитания; на фиг. 5 - пример реализации коммутатора.

Преобразователь фаза-код (фиг. 1) содержит входные формирователи 1 и 2, блок 3 управления, генератор 4 тактовых импульсов, ключ 5, схему 6 вычитания, коммутатор 7, комбинационные элементы 8, 9, 12 И- ИЛИ, суммирующий счетчик 10, реверсивный счетчик 11, управляемая схема 13 вычитания, ключ 14.

Блок 3 управления (фиг. 2а) содержит элемент 35 ИЛИ, счетный триггер 36, D- триггер 37, постоянное запоминающее устройство 38 (ПЗУ).

Управляемая схема 13 вычитателя (фиг. 3) содержит схему 39 вычитания, элементы 40, 41, 42 И, элемент 43 ИЛИ.

Схема 6 вычитания (фиг. 4а) содержит D-триггер 47 и элемент 48 ИЛИ. Схема 39 вычитателя имеет аналогичную структуру.

Коммутатор 7 (фиг. 5) содержит элементы 49,50 И.

В качестве комбинационных элементов 8, 9 и 12 могут быть использованы, например, интегральные микросхемы К155ЛРЗ.

В преобразователя фаза-код управляющие входы первого комбинационного элемента 8 И-ИЛИ подключены к разрядам первого счетчика 10, сигнальные - к разрядам второго счетчика 11, управляющие входы второго комбинационного элемента 12 И-ИЛИ, подключены к разрядам второго счетчика 11, сигнальные - к разрядам первого счетчика 10, выход которого соединен с первым входом блока 3 управления, второй и третий входы которого соединены соответственно с выходами первого и второго входных формирователей 1, 2, входы которых являются входами устройства, первый вход ключа 5 соединен с первым выходом блока 3 управления, второй выход которого подключен к первому входу коммутатора 7, второй вход которого соединен с выходом схемы б вычитания, первый вход которой подключен к выходу управляемой схемы 13 вычитания, первый вход которой соединен с выходом второго ключа 14, первый вход

которого соединен с выходом третьего комбинационного элемента 9 И-ИЛИ, управляющие входы которого подключены к шине установки коэффициента, а сигнальные - к разрядам первого счетчика 10, вход которого соединен с выходом генератора 4 тактовых импульсов, третий и четвертый выходы блока 3 управления подключены соответственно ко второму и третьему входам управляемой схемы 13 вычитания, четвертый вход которой соединен с выходом второго комбинационного элемента 12 И-ИЛИ, выход первого комбинационного элемента 8 И-ИЛИ подключен ко второму входу ключа 5, выход

5 которого соединен со вторым входом схемы 6 вычитания, первый и второй выходы коммутатора 7 подключены соответственно ко входу сложения и вычитания второго счетчика 11, а пятый выход блока 3 управления

0 соединен со вторым входом ключа 14.

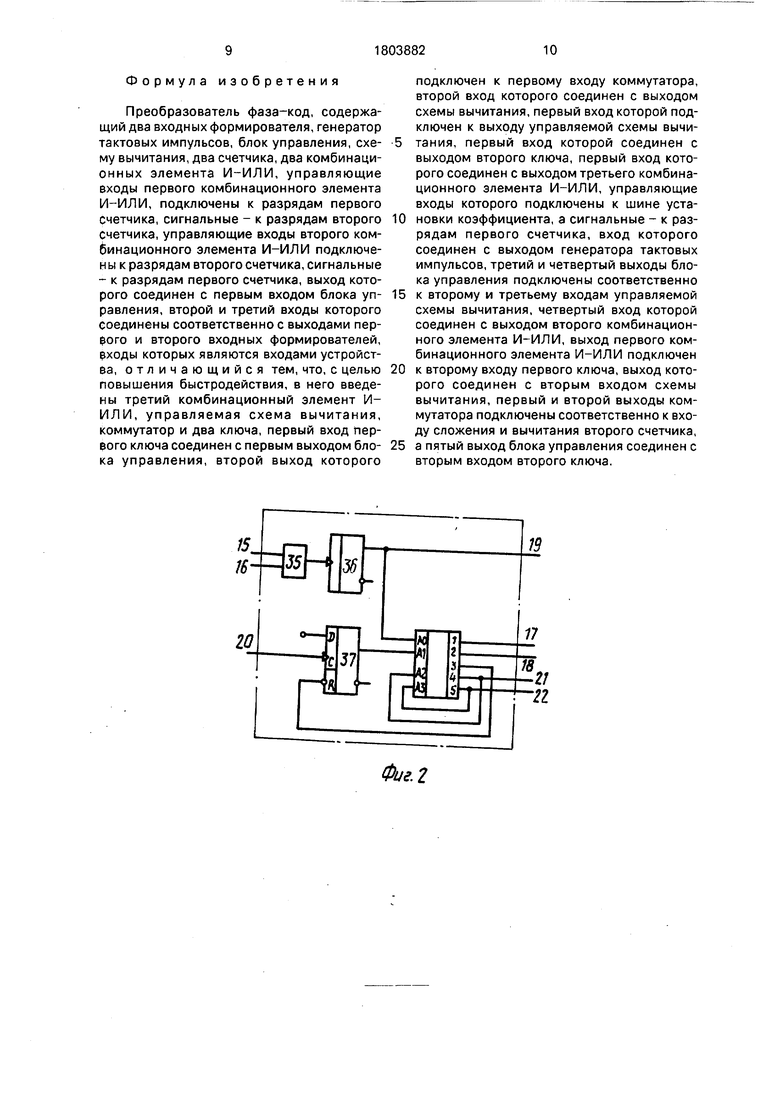

Возможны два варианта работы преобразователя. В первом случае преобразователь работает следующим образом. В исходном состоянии ключи 5, 14 закрыты,

5 счетчики 10 и 11 обнулены, коммутатор 7 коммутирует выход 30 схемы 6 вычитания с суммирующим входом реверсивного счетчика 11. На управляющих входах управляемой схемы 13 вычитания при помощи блока 3

0 управления устанавливается код, при котором импульсная последовательность kdx с выхода комбинационного элемента 9 И-ИЛИ через управляемую схему 13 вычитания подается на вход 28 схемы 6 вычитания.

5 Исследуемые сигналы Ui(t) и L)2(t) фазовый сдвиг между которыми необходимо измерить, подаются на входные формирователи 1, 2 соответственно, и преобразуются в короткие однополярные импульсы. Блок 3 уп0 равления формирует из этих импульсов стробирующие импульсы длительностью т с периодом следования Т, равные измеряемому фазовому сдвигу. Квантующие импульсы генератора 4 тактовых импульсов в течение

5 гп периодов частоты исследуемых сигналов поступают на вход суммирующего счетчика 10. Результат квантования m периодов

50

Х2 тхт,

0)

где хт - результат квантования одного периода.

В момент появления импульса переполнения суммирующего счетчика 10 (фиг. 26) блок 3 управления подает на входы управляемой схемы 13 вычитания управляющий код и на ее выходе появляется приращение импульсной последовательности

dp kdx - dq,

(2)

где XT-приращение импульсной последова- те ьности на выходе комбинационного элемента 12 И-ИЛИ. Открывается ключ 5. На схему 6 вычитания начинает поступать при- раЦение импульсной последовательности dr|c выхода комбинационного элемента 8 И-ИЛИ, По окончанию стробирующего им- nyjjibca на прямом выходе счетного триггера 36 блока 3 управления на выход управляемо схемы 13 вычитания поступает прира- ще|ние импульсной последовательности dq. Коммутатор 7 коммутирует выход 30 схемы 6 цычитания с вычитающим входом реверсивного счетчика 11. По окончании паузы на прямом выходе счетного триггера 36 блока 3 управления триггер 37 блока 3 управления сбрасывается в ноль, ключ 5 закрывается, преобразователь переходит в исходное со- стс|яние и цикл измерения повторяется внбвь.

К моменту достижения частоты в счетчике J10 значения XH 2П на вход счетчика 11 поступило (m-1) импульсных последова- тефностей, каждая из которых содержит хг Импульсов и часть m-й последовательности A XT. В реверсивном счетчике 11 зафиксировано число

ZH k((m-1)xr + А хг

(3)

где: к - коэффициент деления делителя частот, образованного счетчиком 10 и комби- нафюнным элементом 9 И-ИЛИ.

Счетчики 10, 11, комбинационный элемент 12 И-ИЛИ и управляемая схема 13 вычитания образуют число-импульсный умножитель. Приращение импульсной последовательности на его выходе описывается соотношением

dq dx 2n

(4)

где n - разрядность счетчиков.

На выходе 27 управляемой схемы 13 вычитания появляется приращение импульсной последовательности

dp kdx - dq

(5)

Подставив значение (4) в выражение (5) получим

dp

2nkdx-Zdx 2n

(6)

,На выходе 30 схемы 6 вычитания прира- щейие импульсной последовательности описывается выражением

dZ dp - dr(7) Счетчики 10, 11, комбинационный элемент 8 И-ИЛИ и схема 6 вычитания образуют число-импульсный умножитель, работа которого описывается выражением

dr dZ

2n

(8)

где х - текущее значение числа в счетчике 10 после его переполнения.

Подставив в выражение (7) значение dr из выражения (8) получим:

15

2П -1-х

(9)

С учетом количества импульсов хн 2П, по- требовавшегося для переполнения счетчика 10, общее количество импульсов, поступивших на его вход определяется выражением х 2П + х1. Подставив это значение в (9) получаем:

х

dZ

(10)

30

Подставив в выражение (10) значение dp из выражения (6) получим

2n k - 2 dZ d x

(11)

35 Разделяя переменные и интегрируя левую и правую части выражения получаем

-In(2nk-Z) lnx

(12)

40Подставив пределы интегрирования, получим

21х1

-In(2nk-Z)l lnxl

Z4Х4

,n2nk-Z ln- 2nk-ZiХ4

(13)

(14)

50 Отсюда

2nk -Z4 xi 2nk-Zi X4

(15)

где xi хт (m-1) + х т(16) результат квантования (m-1) целых периодов и одного фазового сдвига.

Выразив из выражения (15) переменную Zi при условии

V.

X4 2n (m-1)xT + Ахт(17) получаем решение дифференциального уравнения (11) с учетом начальных условий

Zi

2n k m XT

XT ( m - 1 ) + xr

В момент переключения счетчика 11 в режим вычитания блок 3 управления подает на входы управляемой схемы 13 вычитания код, и подача составляющей kdx на вход 23 управляемой схемы 13 вычитания прекращается. При этом работа преобразователя описывается следующими соотношениями:

dZ - - dx х

Разделив переменные и проинтегрировав обе части уравнения с учетом пределов интегрирования, решение дифференциального уравнения будет иметь вид:

Х2

или с учетом (1), (16) и (18)

Z2 2nk -HL

XT

Выбрав коэффициент деления k

360 а

-10 и установив его на шине уста2п

новки коэффициента, получим в счетчике 11 результат измерения фазового сдвига исследуемых сигналов Ui(1) и LJ2(t):

а хг Z2 360-10 - ,

ХТ

где а Т.- любое целое число.

Второй вариант работы преобразователя связанный с появлением импульса переполнения суммирующего счетчика 10 иллюстрируют временные диаграммы работы на фиг. 2в. Временные диаграммы на выходах элементов 35, 36 аналогичны первому случаю.

К моменту достижения числом в счетчике 10 значения Х4 в счетчик 11 поступят все m последовательностей XT, т.е. в нем зафиксируется число

ZH гл XT- k

В рассматриваемом случае xi Х4, zi Z4.

Подставив эти выражения в выражение (20) с учетом (1) и (17) получим выражение для Z2 аналогичное выражению (21), т.е. преобразование осуществляется так же, как и 5 на прошедшем этапе в предыдущем случае и число в счетчике 11 в конце преобразования определяется выражением (22).

Технические преимущества предлагаемого преобразователя фаза-код по сравне- 10 нию с базовым устройством, в качестве которого принят прототип, заключается в повышении быстродействия. Прототип работает в два такта. В первом также подсчитывается число 15

Ni nTxfo(24)

где п - число периодов опорного сигнала;

fo - частота генератора импульсов об- 20 разцовой частоты.

Ti пТх

(25)

(20)

Во втором такте подсчитывается число 25 импульсов

N2 П rfo,

(26)

где г- длительность импульсов, соответст- 30 вующих временному сдвигу между фронтами сигналов на опорном и измерительном входах устройства. Длительность второго такта равна длительности первого такта:

35 Т2 Ti пТх

(27)

Суммарная длительность преобразования равна

40

Т Ti + Т2 2 пТх

(28)

Заявляемый преобразователь осуществляют операции аналогичные операциям, описываемым выражениями (24) и (26), па- 45 раллельно за время

Т1 пТх

(29)

Тогда отношения времени преобразо- 50 вания прототипа и заявляемого устройства

2

(30)

Следовательно, быстродействие заяв- ляемого преобразователя фаза-код в 2 раза больше, чем у прототипа.

Повышение быстродействия заявляемого преобразователя значительно расширит сферы его применения.

Формула изобретения

Преобразователь фаза-код, содержащий два входных формирователя, генератор тактовых импульсов, блок управления, схему вычитания, два счетчика, два комбинаци- онных элемента И-ИЛИ, управляющие входы первого комбинационного элемента И-ИЛИ подключены к разрядам первого счетчика, сигнальные - к разрядам второго счетчика, управляющие входы второго комбинационного элемента И-ИЛИ подключены к разрядам второго счетчика, сигнальные - к разрядам первого счетчика, выход которого соединен с первым входом блока управления второй и третий входы которого единены соответственно с выходами первого и второго входных формирователей, входы которых являются входами устройства отличаю щийся тем, что, с целью повышения быстродействия, в него введены третий комбинационный элемент И ИЛИ управляемая схема вычитания, коммутатор и два ключа, первый вход пер- Вого ключа соединен с первым выходом бло- ка управления, второй выход которого

25

0

5

20

подключен к первому входу °ммУта™Рам второй вход которого соединен с выходом схемы вычитания, первый вход которой подключен к выходу управляемой схемы вычитания первый вход которой соединен с выходом второго ключа, первый вход которого соединен с выходом третьего комбина- Еионного элемента И-ИЛИ, управляющие входы которого подключены к шине установки коэффициента, а сигнальные - к разрядам первого счетчика, вход которого соединен с выходом генератора тактовых импульсов, третий и четвертый выходы блока управления подключены соответственно к второму и третьему входам управляемой схемы вычитания, четвертый вход которой соединен с выходом второго комбинационного элемента И-ИЛИ, выход первого комбинационного элемента И-ИЛИ подключен к второму входу первого ключа, выход которого соединен с вторым входом схемы вычитания, первый и второй выходы коммутатора подключены соответственно к входу сложения и вычитания второго счетчика, а пятый выход блока управления соединен с вторым входом второго ключа.

I I 288C081

OP

f

.r

Авторы

Даты

1993-03-23—Публикация

1991-04-08—Подача