к раэрядньм выходам первого счетчика причем к импульсному входу i-ro элемента И второй группы подключен выхо ()-го разряда третьего счетчика, к потенциальному вход того же элеме та И второй группы подключен выход ()-ro разряда первого счетчика, выход импульсного вычитателя соедине с первым информационным входом второ го коммутатора, к второму информационному входу которого подключен выхо первого коммутатора, к третьему информационному входу второго коммутат ра подключен выход импульсного вычитателя, выход второго Коммутатора соединен с информационным входом пер вого управляемого делителя частоты, выход которого соединен с счетным входом счетчика результата, первы вход второго импульсного сумматора подключен к выходу третьего элемента ИЛИ и к второму информационному входу первого коммутатора, второй вход второго импульсного сумматора подключен к входу преобразователя, выход второго импульсного сумматора подключен к первому информационному входу третьего коммутатора, второй 1 0 информационный вход которого подключен к выходу первого импульсного сумматора, выход третьего коммутатора соединен с информационным входом второго управляемого делителя частоты, выход которого соединен со счетным входом второго счетчика, разрядные выходы реверсивного счетчика соединены с потенциальными входами импульсно-потенциальных элементов И третьей группы, причем к импульсному входу л-го элемента И третьей группы подключен выход, ()-ro разряда второго счетчика, к потенциальному входу того же элемента И третьей группы подключен выход (n-i)-ro разряда реверсивного счетчика, разрядные выходы третьего счетчика подключены к входам дешифратора, выходыкоторого подключены к адресному . входу блока памяти, выходы групп разрядов с первой по шестую которого подключены к управлякмцим входам соответственно первого, второго, третьего коммутаторов реверсивного счетчика и первого и второго управляемых делителей частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 1983 |

|

SU1120322A1 |

| Число-импульсный функциональный преобразователь | 1982 |

|

SU1043645A1 |

| Частотно-импульсный функциональный преобразователь | 1981 |

|

SU995095A1 |

| Вычислительное устройство | 1983 |

|

SU1080137A1 |

| Цифровой аппроксиматор | 1981 |

|

SU1010619A1 |

| Функциональный преобразовательчиСлА иМпульСОВ B цифРОВОй КОд | 1979 |

|

SU807285A1 |

| Вычислительное устройство | 1983 |

|

SU1083187A1 |

| Измерительный функциональный преобразователь | 1981 |

|

SU983704A1 |

| Цифровой функциональный преобразователь | 1982 |

|

SU1104492A1 |

| Устройство для вычисления элементарных функций | 1982 |

|

SU1045227A1 |

АППРОКСИМИРУЮЩИЙ ФУНКЦИОНАЛЬНЬЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий реверсивный счетчик, первый и второй счетчики, первый управляемый делитель частоты, первую, вторую и третью группы импульснр-потенциальных элет ментов И, первый, второй и третий элементы ИЛИ, первый коммутатор, перйый импульсный сумматор и импульс- ный вычитатель, первый вход и выход которого подключены соответственно к входу преобразователя и счетному входу первого счетчика, разрядные выходы которого подключены к импульсным входам импульсно-потенциальных элементов И первой группы, выходы которых подключены к входам первого элемента ИЛИ, выход которого соединен с вторым входом импульсного вычитателя, выходы импульсно-потенциальных Элементов И второй группы соединены с входами второго элемента ИЛИ, выход которого подключен к первому входу первого импульсного сумматора. выход которого соединен с первым информационным входом первого коммутатора, выход которого соединен со счетным входом реверсивного счетчика, разрядные выходы второго счетчика подключены к импульсньтм входам импульсно-потенциальных элементов И третьей группы, выходы которого соединены с входами третьего элемента ИЛИ, отличающийся тем, что, с целью расширения класса решаемых задач за счет дополнитедь-. ного вычисления функций т,) (Л методом кусочно-нелинейной аппроксимации, в него введены второй импульсный сумматор, дешифратор, блок памяти, второй управляемый делитель частоты, счетчик результата, второй и третий коммутаторы к третий счетчик, счетный вход которого соединен с пера вым входом вычитателя и вторым входом о м со первого импульсного сумматора,разрядные выходы третьего счетчика соединен ны с потенциальными входами импульсВо-потенциальных элементов И первой группы, причем к импульсному входу 1-го элемента И первой группы подключен выход (i+D-ro разряда первого сг1етчика, к потенциальному входу того же элемента И первой группы подкгаочен выход (п-О-го разряда третьегосчетчика (где п - разрядность счетчиков, i 0,1..., W -1) , разрядные выходы третьего счетчика подключены к импульсным входам импульсно-потенциальных элементов И второй группы, потенциальные входы которых подключены

1

Изобретение относится к автоматике, вычислительной и измерительной технике и может быть использовано в качестве специализированного вычислителя, входящего в состав устройств автоматики, управления и контроля, а также для функционального преобразователя импульсных последовательностей, в частности для линеаризации характеристик частотных датчиков.

Известно устройство для воспроизведения степенной функции, содержащее две цепочки двоичных умножителей регистр и реверсивный счетчик Li

Недостатками этого Устройства являются узкийкласс решаемых задач, а также чрезмерная зависимость аппаратурных затрат от значения показателя степени, приводящая к усложнеН1да схемы.

Наиболее близким к изобретению по технической сущности является

функциональный преобразователь числа импульсов в цифровой код, содержащий реверсивный счетчик, первый и второй счетчики, первую, вторую и третью

5 группы импульсно-потенциальных элементов И, первый, второй и третий элементы ИЛИ, первый и второй импульсные сумматоры-вычитатели,. делитель частоты, первый коммутатор,

10;блок управления, содержащий инвертор, формирователь импульсов и три ключа, первые входы которых подключены к источнику питания, а вторые к щине нулевого потенциала, выход

15 первого ключа подключен к управляющему входу первого коммутатора,

выход второго ключа - к сходу управления суммированием и через инвертор ко входу управления вычитанием

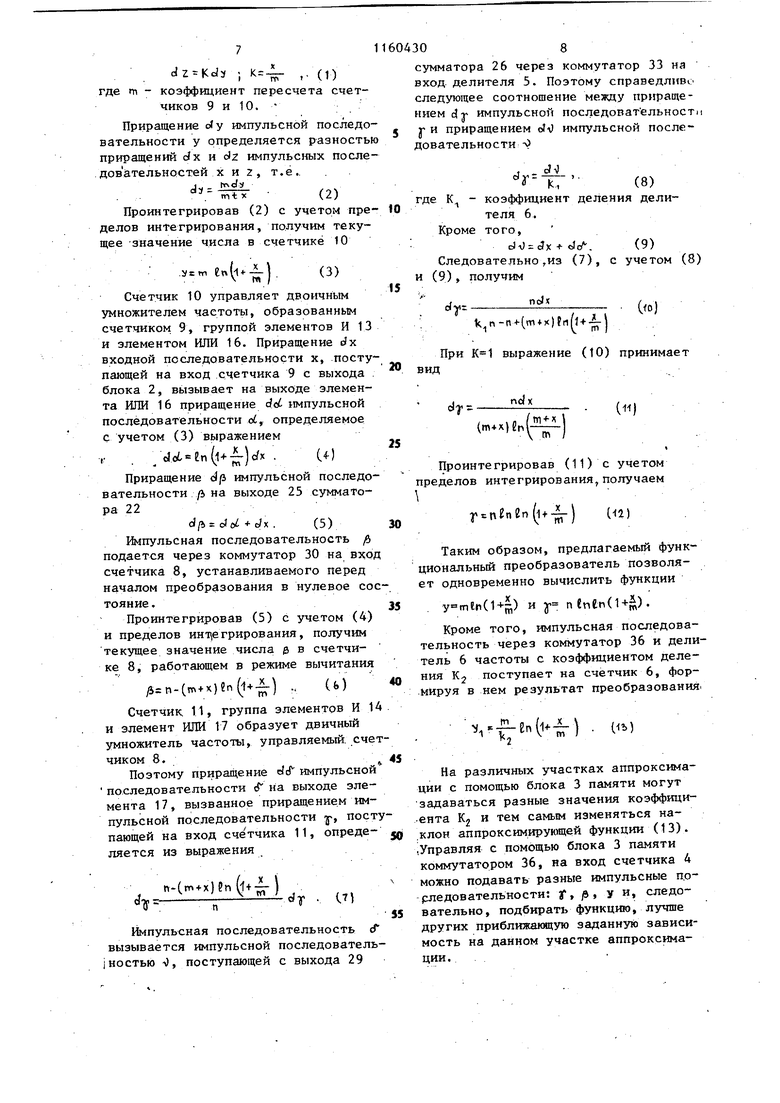

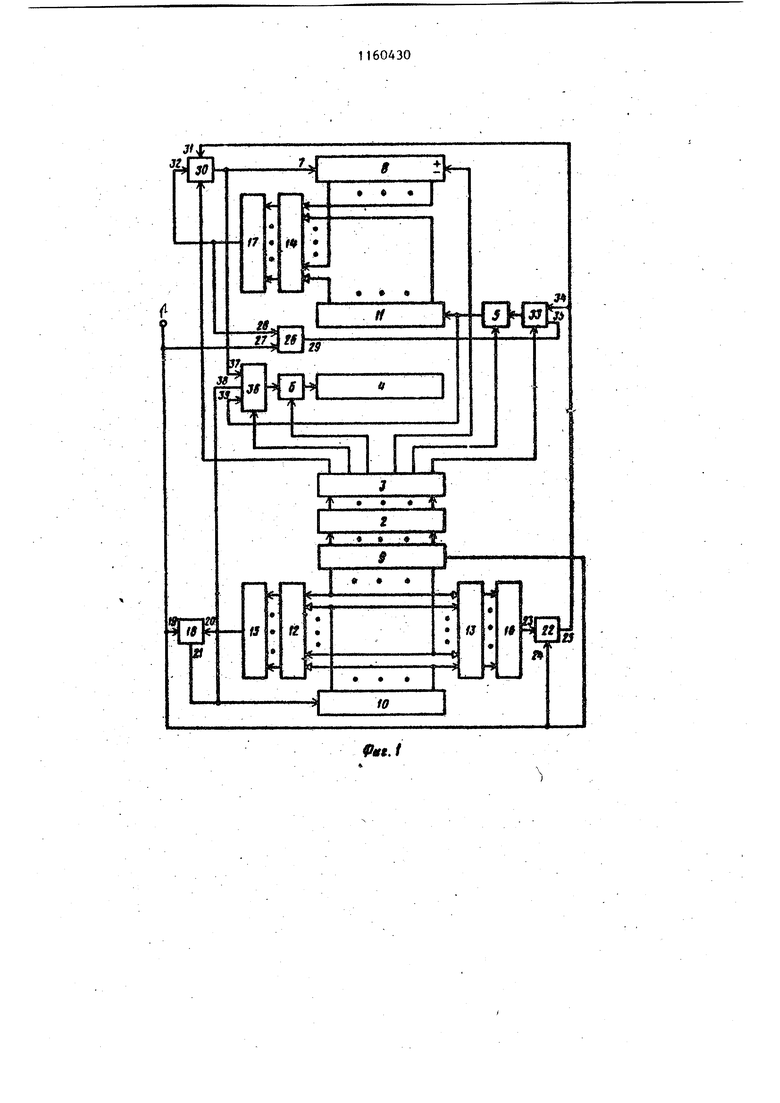

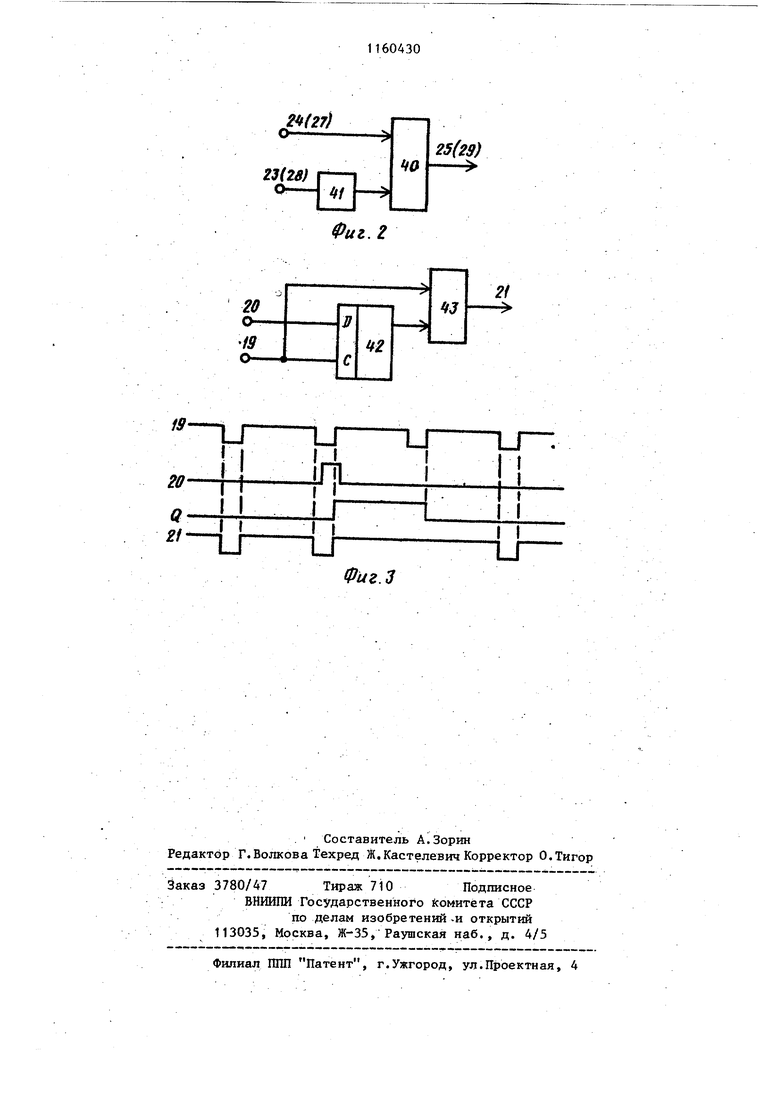

20 реверсивного счетчика, вход формирователя импульсов соединен с входом блока управления, а выход формирователя к первому входу первого импульснего сумматора-вычитателя, выход, которого соединен с входом первого счетчика, разрядные выходы которого подключены к импульсным входам первой группы импульсно-потенциальных элементов И, выходы которой подключены к входам первого элемента ИЛИ, выход которого соединен с вторым входом первого импульсного сумматор вычитателя, выходы второй группы им пульсно-потенциальных элементов И соединены с входами второго элемента ИЛИ, выход которого подключен к первому входу второго импульсного сумматора-вычитателя, выход которого соединен с первым входом первого коммутатора, выход которого соединей с входом реверсивного счётчика, разрядные.выходы второго счетчика подключены к импульсным входам третьей группы импульсно-потенциальных элементов И, выходы которой соединены с входами третьего элемен та ИЛИ 2 3. Недостатками известного устройст ва являются узкий класс решаемых задач, обусловленный невозможностью воспроизведения функции вида : Г, ь(1ф и (i4j), 2 коэффициент преобразо где к и к. вания и невозможность воспроизведения функций методом аппрокси мадии. Целью изобретения является расши рение класса решаемых задач за сче возможности дополнительного вычисле .ния функций , :,Tn.i.en(l.b.),y, e,e,(,,j. методом кусочно-нелинейной аппрокси мации, о Поставленная цель достигается тем, что в аппроксимирующий функцио нальный преобразователь, содержащий реверсивный счетчик, первый и второй счетчики., первый управляемый делитель частоты, первую, вторую, третью группы импульсно-потенциальных элементов И, первый, второй и третий элементы ИЛИ,- первьй коммутатор, первый импульсный сумматор и импульсный вычитатель, первый вход и выход которого подключешл . соответственно к входу преобразователя и счетному входу первого счатчика, разрядные выходы которого .подключены к импульсным входам им30 . 4 пульсно-потенциальных элементов И первой группы, выходы которых подключены к входам первого элемента ИЛИ, выход которого соединен с вторым входом импульсного вычитателя, выходы импульсно-потенциальных элементов И второй группы соединены с входами второго элемента ИЛИ, выход которого подключен к первому входу первого импульсного сумматора, выход которого соединен с первьгм информационным входом первого коммутатора, выход которого соединен с счетным входом реверсивного счетчика, разрядные выходы второго счетчика подключены к импульсным входам импульсно-потенциальных элементов И третьей группы, выходы которых соединены с входами третьего элемента ИЛИ, дополнительно введены второй импульсный сумматор, дешифратор, блок памйти, второй управлчемый делитель частоть, счетчик результата, второй и третий коммутаторы, третий .счетчик, счетный вход ко.торого соединен с первым входомвычйтателя и вторым входом первого импульсного сумматора, разрядные выходы третьего счетчика соединены с потен-, циальными входами импульсно-потенциальных элементов И первой группы, причем к импульсному входу i-ro элемента И первой группы подключен выход (+1)-го разряда первого счетчи- : ка, к потенциальному входу того же элемента И первой группы прдк.пючен выход (п 0-го разряда третьего счетчика п- разрядность счетчиков, , 1,.. ., h -1) , разрядные выходы третьего счетчика подключены к импульсным, входам импульсно-потенциальных элементов И второй группы, потенциальные входы которых подключены к разрядным выходам первого счетчика, прячем к импульсному входу 1-го элемента И второй группы подключен выход (л- i)-FOразряда третьего счетчика, к потенциальному входу того же элемента И второй группы подключен выход; (i+1)-ro разряда первого счетчика, выход ютульсного вЫчитателя соедииен с первым информационньгм входом второго коммутатора,к второму информационному входу которого подключен выход первого коммутатора, к третьему информационному входу второго коммутатора подключен выход импульсного ВЫчитателя, выход второго коммутатора соединен с информационным входом первого управляемого делителя частоты, выход которого соединен с счетным входом счетчика результата, первый вход второго импульсного сумматора подключен к выходу третьего элемента ИЛИ и к второму информационному входу первого коммутатора, второй вход второго импульсногр сумматора .подключен к входу преобразователя, .выход второго импульсного сумматора подключен к первому информационному вхбду т ретьего коммутатора, второй информационньй вход которого подключен к выходу первого импульсного сум матора, выход третьего коммутатора соединен с информационным входом вто рого управляемого делителя частоты, выход которого соединен со счетным входом второго счетчика, разрядые выходы реверсивного счетчика соединены с потенциальными входами импульснопотенциальных элементов И третьей . группы, причем к импульсному входу i-ro элемента И третьей группы подкл ченГ выход (i+D-ro разряда второго счетчика, к потенциальному входу тог же элемента И третьей группы подключен выход (р-0-го разряда реверсивн го счетчика, разрядные выходы третье го счетчика подключены к входам дешифратора, выходы которого подключены к адресному входу блока памяти выходы групп разрядов с первой по шестую которого подключены к управляющим входам соответственно первого второго третьего коммутаторов ревер сивного счетчика и первого и дторого управляемых делителей частоты. На фиг. 1 дана структурная схема цифрового функционального преобразов теля; на фиг. 2 - вариант выполнения импульсного сумматора, на фиг, 3 вариант выполнения импульсного вычитателя и временные диаграммы, поясняющие его работу. Цифровой функциональный преобразо ватель содержит вход 1, дешифратор 2 блок 3 памяти, счетчик А результата управляемые делители 5 и 6 частоты, информационный вход 7 реверсивного счетчика 8, счетчики 9 - 11, группы импульсно-потенциальных элементов И 12 - 14, элементы ИЛИ 15-17 импульсный .вычитатель 18 с входами 19 20 и выходом 21, импульсный сумматор 22 с входами 23 и 24 и выходом 2 импульсный сумматор 26 с входами 2 7 и 28 и выходом 29, коммутатор 30 с входами 31 и 32, коммутатор 33 с входами 34 и 35, коммутатор 36 с входами 37-39. Вариант выполнения схемы импульсного сумматора (фиг. 2) содержит элемент ИЛИ 40 и элемент задержки 41. Вариант выполнения схемы импульсного вычитателя (фиг. 3) содержит триггер 42 и элемент ИЛИ 43, Элемент 41 задержки исключает возможность совпадения импульсов импульсных последовательностей, поступающих на ву.ор, схем1,1 (фиг. 2). Работа схемы вычитания подробно иллюстрируется временными диаграммами (фиг. 3). Функциональный преобразователь работает следующим образом. Импульсная входная последовательность X, поступающая на вход 1 преобразователя, формирует текущее значение X числа в счетчике 9. Код этого числа поступает на входы дещифратора 2, с помощью которого определяются узлы аппроксимации. Код, соответствующий узлам аппроксимации, с выходам дешифратора 2 поступает на адресные входы блока 3 памяти, в ячейках которого хранятся значения коэффициентов деления делителей 5 и 6 частоты и информация о режимах работы коммутаторов 30, 33 и 36 и реверсивного счетчика 8. Пусть для определенности на произвольном участке, аппроксимации сигналом с выходов блока 3 памяти коммутатор 30 переключен в такое положение, что импульсная последовательность на выход коммутатора поступает с входа 31, коммутатор 33 переключен в такое положение, что импульсная последовательность на его выход поступает с входа 35, коммутатор 36 переключен в такое положение, что импульсная последовательность на его выход поступает с входа 39. Сигналами с выходов блока памяти установлены коэффициенты деления К и К, управляемых делитег лей 5 и 6 частоты соответственно. Счетчик 9 с помощью разрядных выходов управляет двоичным умножителем частоты, состоящим из счетчика 10, группы элементов И 12 и элемента ИЛИ 15. Приращение с/у импульсной последовательности у, поступающей на вход счётчика 10 с выхода 21 вычитателя 18, вызывает на выходе элемента ИЛИ 15 приращение dz импульсной последовательности dz-Kd:/ ; i где m - коэффициент пересчета счетчиков 9 и 10. Приращение б(у импульсной последо вательности у определяется разность приращений dx и dz импульсных после довательностей X и 2, т.е.. Проинтегрировав (2) с учетом пре делов интегрирования, получим текущее -значение числа в счетчике 10 .Sew i Счетчик 10 управляет двоичным умножителем частоты, образованным счетчиком 9, группой элементов И 13 и элементом ИЛИ 16. Приращение dx входной последовательности х, .посту пающей на вход счетчика 9 с выхода . блока 2, вызывает на выходе элемента ИЛИ 16 приращение dtf. импульсной последовательности oi, определяемое С учетом (3) выражением т oIo(. en( . (4-) Гп ) Приращение dp импульсной последовательности /i на выходе 25 сумматора 22 d/ir о(г/+С/Х . (5) Импульсная последовательность /6 подается через коммутатор 30 на вход счетчика 8, устанавливаемого перед началом преобразования в нулевое сос тояние. Проинтегрировав (5) с учетом (4) и пределов инт егрирования, получим текущее значение числа /з в счетчике 8, работающем в режиме вычитания (n + x)n(l-t--) ., (ь) Счетчик, 11, группа элементов И 14 и элемент ИЛИ 17 образует двичный умножитель частоты, управляемый, счет чиком 8. Поэтому приращение dcf импульсной последовательности tf на выходе элемента 17, вызванное приращением импульсной последовательности у, посту пающей на вход счетчика 11, определяется из выражения n-C + xlPnOt-) „ Т Импульсная последовательность cf вызывается импульсной последователь|ностью л), поступающей с выхода 29 308 сумматора 26 через кокгмутатор 33 на вход делителя 5. Поэтому справедливо следующее соотношение между приращениeмdJ импульсной последовательности j и приращением о1л) импульсной последовательностигде К. - коэффициент деления делителя 6. Кроме того, d-O dx-KJc/-. (9) Следовательно,из (7), с учетом (8) и (9), получим k.,r(-n-H()tnf;I-«-При выражение (10) принимает / I л /т--ч („.х)еп(-) Проинтегрировав (11) с учетом пределов интегрирования,получаем i snben(i+-) c-ti) Таким образом, предлагаемый функциональный преобразователь позволяет одновременно вычислить ф-ункции . (1+) и у nCnend-i-). Кроме того, импульсная последовательность через коммутатор 36 и делитель 6 частоты с коэффициентом деления К2 поступает на счетчик 6, фор.мнруя в нем результат преобразования 1--г-еп() . им На различных участках аппроксимаии с помощью блока 3 памяти могут задаваться разные значения коэффициента Kj и тем самым изменяться наклон аппрокеимирующе1Й функции (13). Управляя с помощью блока 3 памяти коммутатором 36, на вход счетчика 4 можно подавать разные импульсные п.орледовательности: Г, р, У и, следовательно , подбирать функцию, лучше других приближающую заданную зависимость на данном участке аппроксимации. На другом участке аппроксимации коммутатор 33 пропускает на свой выход с входа 34 импульсную последовательиость , поступакмдую с выхода 25 сумматора 22, а коммутатор 30 пропускает на свой выход импульсную последовательность, поступающую с входа 32. ., tf/s , с учетом (4) и (5) gn(.) Проштегрировав (15) с учетом пределов интегрирования,определим текущее значение числа в счетчике 11 (,i-) . (К) в счетчик 7 перед началом преобра зования записывается число а. Тогда где cf- текущее значение числа в счет чике 8.. Знаки + в выражении (17) ссзртвет ствуют работе счетчика 8.в режиме сум мирования, а знак - - в режиме (вычитания. Принимая во внимание (15) и (17), fei() Отсюда (l4-i- Ч to / В предлагаемом преобразователе по сравнению с известным существенно расширен класс рещаемых задач и функциональные возможности за счет возможности дополнительного вычисления функций ATf4)-frF,)Кроме того, предлагаемый преобразователь обладает значительно большими функциональными вбзможностями, чем известный,за счет обеспечения возможности воспроизведения функций методом кусочно-нелинейной аппроксимации. При этом на различных участках аппроксимации приближение могкет осуществляться разными функциями у, fb , Уд и Л v-Jll-y-f.JL) ft- n-(m4.x),J Ч . 2 f,enb(i.-), .JiiLb(i.xH, : ((|f JLV Xj V W то позволяет более точно воспроизодить drsTHKUHM.. Указанные преимущества получены практически без усложнения устройства, так как вновь введенные элементы не сложнее исключенных.

Фт.г

Фиг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Данчеев В.П | |||

| ЦифрочастотнЫе вычислительные устройства | |||

| М., Энергия, 1976, с | |||

| Железобетонный фасонный камень для кладки стен | 1920 |

|

SU45A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторские свидетельство СССР | |||

| Функциональный преобразовательчиСлА иМпульСОВ B цифРОВОй КОд | 1979 |

|

SU807285A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-06-07—Публикация

1983-12-02—Подача