Изобретение относится к вычислительной технике, в частности к устройствам распределения заданий между процессорами, и может быть испол зовано в неоднородных многопроцессорных вычислительных системах для распределения нагрузки между процессорами.

Известно устройство обмена, соде жащее линейный блок, .блок управления обменом, счетчик номера абонента, дешифраторы, регистр готовности абонентов, схему-сборки сигналов требований обмена 1.

Недостатками известного устройства являются низкое быстродействие и сложность.

Наиболее близким к предлагаемому по технической сущности является устройство для распределения заданий процессорам, содержащее блок управления, к первому входу которог подключен выход элемента ИЛИ к вторым входам блока управления подключены выходы регистра готовности процессоров, а к третьим входам шины необходимого числа процессоров, первый и второй выходы блока управления соединены с входами регистра сдвига, третий выход блока управления подключен к шине отказа от распределения заданий, выходы регистра сдвига подключены к входам элемента ИЛИ и к первым входам каждой из . п групп элементов И,к вторым входам которых подключены, соответствующие выходы регистра готовности процессоров, к третьим входам элементов И подключены шины номера задания, выходы каждой группы элементов и соединены с соответствующими входами группы -элементов ИЛИ, выходы которых соединены с нулевыми входами регистра сдвига и регистра готовности процессоров, к входам процессоров подключены выходы соответствующих групп элементов И, а выходы процессоров соедийены с единичными входами регистра готовности процессоров ГзЗ.

Цель изобретения - расширение области применения устройства за счет возможности его использования в неоднородных вычислительных системах . .

Поставленная цель достигается тем, что в многоканальное устройств для распределения заданий процессорам, содержащее в каждом канале группы элементов И, группу элементо ИЛИ, регистр готовности процессоров и две группы блоков элементов И, введены в. каждом канале регистр код группы процессоров и схема сравнения, причем кодовые входы устройства соединены с первыми входами эл ментов И группы в каждом канале, -вторые входы которых соединены с

выходом схемы сравнения своего канала, первая и вторая группы входов которой соединены соответственно с группой информационных входов устройства и группой выходов регистра готовности процессоров своего канала, выходы элементов И группы в каждом канале соединены с группой входов первого блока элементов И первой группы своего канала и груп0пой входов первого блока элементов И второй группы своего канала, прямой и инверсный выходы разрядов регистра кода группы процессоров в каждом канале, кроме выходов последнего разряда этого регистра, соединены с управляющими входами одноименных блоков элементов и соответственно первой и второй групп, прямой выход последнего разряда регистра кода группы процессоров в каждом канале

0 соединен с управляющим входом последнего блока элементов И второй группы своего канала, выходы каждого блока элементов и первой группы, кроме выходов последнего блока

5 в каждом канале, соединены с группами входов следующих блоков элементов И первой и второй групп своих каналов, выходы последнего блока элементов И первой группы в каж0дом канале соединены с группой входов последнего блока элементов И второй группы своего канала, каждый сигнальный вход устройства соединен с входом сброса одноименного разря5да регистра кода группы процессоров каждого канала, группа выходов каждого блока элементов И второй группы каждого канала является соответствующей группой выходов устрой0ства и соединена с входами одноименного элемента ИЛИ группы своего канала, выход каждого элемента ИЛИ группы соединен с единичным входом одноименного разряда регистра кода группы процессоров своего

5 канала.

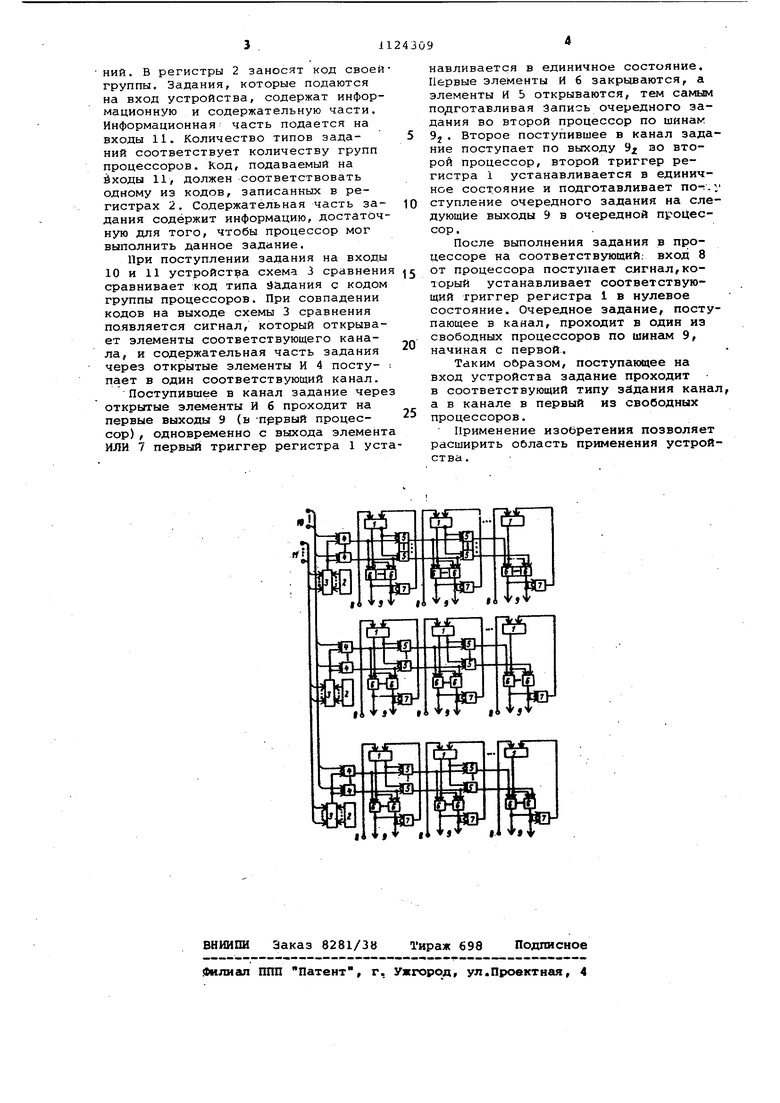

На чертеже представлена структурная схема предлагаемого устройства ,

Устройство содержит в каждой из

0 каналов регистр 1 готовности процессоров, регистр 2 кода группы процессоров, схему 3 сравнения, группу из элементов И 4, группу элементов И 5, группу блоков элементов И б,группу

5 элементов ИЛИ 7, сигнальные входы 8 устройства, выходы 9 устройства, кодовые входы 10 устройства, информационные входы 11 устройства.

Устройство работает следующим

0 образом.

В исходном состоянии регистры 1 находятся в нулевом состоянии. Это означает, что все процессоры

5 свободны и готовы к приему задаНИИ. в регистры 2 заносят код своей группы. Задания, которые подаются на вход устройства, содержат информационную и содержательную части. Информационная часть подается на входы 11. Количество типов заданий соответствует количеству групп процессоров. Код, подаваемый на йходы 11, должен соответствовать одному из кодов, записанных в регистрах 2. Содержательная часть задания содержит информацию, достаточ ную для того, чтобы процессор мог выполнить данное задание. При поступлении задания на входы 10 и 11 устройства схема 3 сравнени сравнивает код типа «задания с кодом группы процессоров. При совпадении кодов на выходе схемы 3 сравнения по.является сигнал, который открывает элементы соответствующего канала, и содержательная часть задания через открытые элементы И 4 поступает в один соответствующий канал. Поступившее в канал задание чере открытые элементы И б проходит на первые выходы 9 (в -пэрвый процессор) , одновременно с выхода элемент ИЛИ 7 первый триггер регистра 1 уст навливается в единичное состояние. Первые элементы И 6 закрываются, а элементы И 5 открываются, тем самым по;1готавливая запись очередного задания во второй процессор по шинам 9j . Второе поступившее в канал задание поступает по выходу 9 зо второй процессор, второй триггер регистра 1 устанавливается в единичное сост.ояние и подготавливает по-.v ступление очередного задания на следующие выходы 9 в очередной процессор , После выполнения задания в процессоре на соответствующий: вход 8 от процессора поступает сигнал,который устанавливает соответствующий триггер регистра 1 в нулевое состояние. Очередное задание, поступающее в канал, проходит в один из свободных процессоров по шинам 9, начиная с первой. Таким образом, поступающее на вход устройства задание проходит в соответствующий типу задания канал, а в канале в первый из свободных процессоров. Применение изобретения позволяет расширить область применения устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для распределения заданий процессорам | 1989 |

|

SU1633407A1 |

| Многоканальное устройство приоритета для распределения заявок по процессорам | 1985 |

|

SU1327105A1 |

| Устройство для распределения приоритетных заявок по процессорам | 1987 |

|

SU1495795A1 |

| Устройство для распределения заявок по процессорам | 1990 |

|

SU1798782A1 |

| Устройство для обслуживания групповых приоритетных запросов | 1990 |

|

SU1753473A1 |

| Устройство для управления распределенной вычислительной системой | 1982 |

|

SU1136159A1 |

| Устройство для распределения заданий вычислительной системе | 1982 |

|

SU1100623A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1259285A1 |

| Устройство для приоритетного распределения заданий процессорам | 1984 |

|

SU1252777A1 |

| Устройство для распределения заданий процессорам | 1983 |

|

SU1151966A1 |

МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ РАСПРЕДЕЛЕНИЯ ЗАДАНИЙ ПРОЦЕССОРАМ, содержащее в каждом канале группы элементов И, группу элементов ИЛИ, регистр готовности процессоров и две группы блоков элементов И, о т л и чающееся тем, что, с целью рас11Ш рения области применения устройства за счет воэможности его использования в неоднородных вычислительных системах,устройство содержит в каждом канале регистр кода группы процессоров и схему сравне- , ния, причем кодовые входы устройства соединены с первыми входами элементов мИ группы-в каждом канале, вторые входы которых соедине ны с выходом схемы сравнения своего канала (К первая и вторая группы входов которой соединены соответственно с группой инфорационных входов устройства и группой выходов регистра готовности процессоров своего канала,выходы элементов И группы в каждом канале соединены с группой входов первого блока элементов И первой группы своего канала и группой в,ходов первого блока элементов И второй группы своего канала, прямой и инверсный выходы разрядов регистра кода группы процессоров в каждом канале, креме выходов последнего разряда этого регистра, соединены с управляющими входами одноименных блоков элементов И соответственйо первой и -второй групп, прямой выход последнего разряда регистра кода, группы .процессоров в каждом канале -соединен с управлякицим входом последнего блока элементов И второй группы своего канала,выходы каждого блока элементов И первой группы, кроме выходов последнего блока в каждом канале, соединены с группами входов следукяоих блоков элементов.И пе1Ьвой и второй групп своих каналов, выходы последнего блока элементов И первой группы в каждом канале соединены с группой уходов последнего блока элементов И второй группы своего канала, каждый сигнальный вход устройства соединен с входом сброса одноименного разряда регистра кода групйы процессоров Nd i :о каждого канала, группа выходов каждого блока элементов И второй группы каждого канала .является соответствующей группой выходов устройства и соединена с входами одноименного элемента ИЛИ группы Ьвоего канала, выход каждого элемента ИЛИ группы соединен с единичным входом .одноименного разряда регистра кода группы процессоров своего канала.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для распределения заданий процессорам | 1977 |

|

SU629538A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-11-15—Публикация

1983-08-29—Подача