первыми входами одноименных элементов И группы и формирователей импульсов записи, вторые входы которых подключены к выходам одноименных элементов И группы, а выходы - к входам разрядных шин ферроакустического накопителя, вторые входы элементов НЕ-И, блока управления и второго блока местного управления соединены с выходом блока управляемой задержки второй вход которого подключен к второму выходу блока управления, третий вход которого является входом устройства отличающееся тем, что, с целью расширения функциональных возможностей устройства- за счет осуществления операций сравнения и вычитания хранящихся в нем чисел, в него введены блок стирания информации, блок приоритета числа, блок коррекции, распределитель корректирующих импульсов, второй усилитель считывания, блок анализа информации элементы задержки, группа элементов ПТИ, первый элемент И, первый и второй элементы ИЛИ и дополнительный ферроакустический накопитель, причем вход второго усилителя считывания подключен к другому концу металлического стержня другой запоминающей ячейки, а вход стробирования - к выходу второго блока местного управления, выход первого усилителя считывания соединен с первыми входами блока приоритета числа и первого элемента И и первым информационным входом распределителя адресных импульсов, второй информационный вход которого подключен к выходу второго усилителя считьшания и вторы входам первого элемента И и блока приоритета числа, третий вход которого соединен с выходом усилителя синхронизации, а первый выход - с первыми входами блока анализа информации, блока коррекции и первого элемента задержки, выход которого подключен к второму входу блока коррекции, третий вход которого соединен с выходом второго элемента задержки, вход которого подключен к зыходу первого элемента И и первому входу первого элемента ИЛИ, выход которого соединен с входом третьего элемента задержки, а второй вход с вторым вьгходом блока приоритета чила и гзходом четвертого элемента заипржкп, вьгхоц которого подключен к );м)ич ,1.у бпока стирания информации и второму входу блока анализа информации, выход которого соединен с вторым входом блока стирания информации выход которого и выходы блока коррекции подключены соответственно к входу стирания и к входам записи распределителя корректирующих импульсов, управлякщий вход которого соединен с первым выходом дополнительного ферроакустического накопителя, а выходы подключены к первым входам одноименных элементов ИЛИ группы, вторые входы которых соединены с выходами одноименных разрядных шин распределителя разрядных импульсов,, выходы элементов ИЛИ группы подключены к вторым входам одноименных элементов И группы, а. третьи входы - к выходу блока управляемой задержки и первому входу второго элемента ИЛИ, второй.вход которого соединен с выходом третьего элемента задержки, а Ш)1ход - с третьими входами элементов И группы, вход дополнительного ферроакустического накопителя подключен к третьему ввкоду блока управления, второй выход - к третьему управлнкщему входу распределителя адресных импульсов, третий выход - к третьему входу второго блока местного управления, а четвертый выход к четвертому входу блока коррекции, четвертый выход блока управления соединен с четвертым управляющим входом распределителя адресных импульсов первый выход блока приоритета числа является выходом устройства.

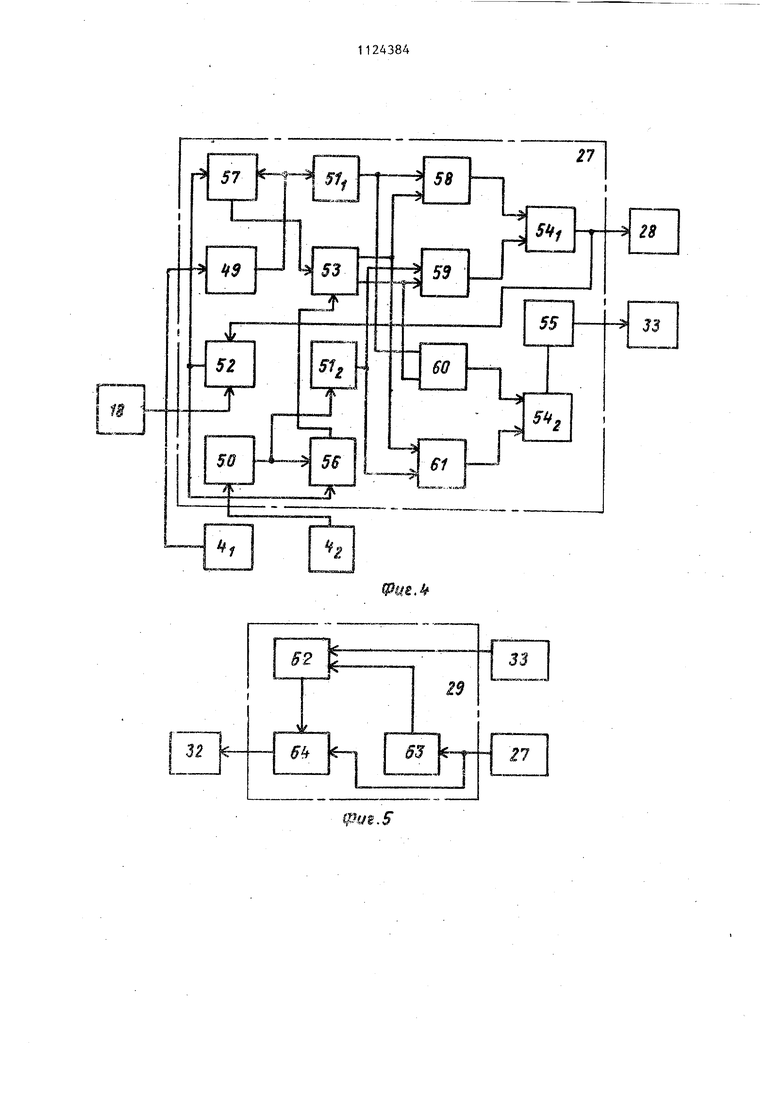

2. Устройство по П.1, отличающееся тем, что блок коррекции содержит формирователи импульсов, ключи, третий и четвертый элементы ИПИ первый триггер и пятый элемент задержки, выход которого подключен к первому входу третьего элемента ШШ, выход которого соединен с входом первого триггера, выход которого подключен к входу пятого элемента задержки и первым входам первого и второго ключей, вторые входы которых и одни из входов первого и второго формирователей импульсов соединены с шиной нулевого потенциала, причем выход четвертого элемента ИЛИ подключен к другому входу первогоформирователя импульсов, второй вход третьего элемента ИЛИ, другой вход второго формирователя импульсов, первый и второй Бходь четвертого :5.пемгпта ИЛИ являются входами-с перяото по

четвертый блока соответственно, выходами которого являются выходы формирователей импульсов и ключей,

3.Устройство по пп,1 и 2, о т личающееся тем, что блок приоритета числа содержит шестой и седьмой элементы задержки, второй и третий триггеры, элементы И с второго по седьмой, пятый и шестой элементы ИЛИ, первый элемент НЕ, третий и четвертый формирователи импульсов, входы которых и первый вход второго триггера являются входами блока, выходами которого являются выходы пятого элемента ИЛИ и первого элемента НЕ, причем выход третьего формирователя импульсов соединен с входом шестого элемента задержки И первым входом второго элемента И, выход которого подключен к первому входу третьего триггера, второй вход которого соединен с выходом третьего элемента И, первый вход которого и вход седьмого элемента задержки подключены к выходу четвертого формирователя импульсов, вторые входы второго и третьего элементов И соединены с выходом второго триггера, второй вход которого подключен к выходу пятого элемента ИЛИ, входы которого соединены соответственно с выходами четвертого и пятого элементов И, первые входы которых подключены соответственно к первому выходу третьего триггера и первому входу седьмого элемента И и к второму выходу третьего триггера и первому входу шестого элемента И, выходы шестого и седьмого элементов задержки соединены соответственно с вторыми входами четвертого и шестого элементов И и с вторыми входами пятого и седьмого элементов И выходы шестого и сепьмого элементов И подключены к входам шестого элемента ИЛИ, выход которого соединен с входом первого элемента НЕ.

4.Устройство по пп.1-3,. о т л ичающееся тем, что блок анализа информации содержит четвертьй триггер, выход которого является выходом блока, восьмой элемент задержки и восьмой элемент И, первый вход которого является первым входом блока, а второй вход и выход соединены соответственно с выходом восьмого элемента задержки и с первым входом четвертого триггера, второй вход которого и вход восьмого элемента задержки являются вторым входом блока.

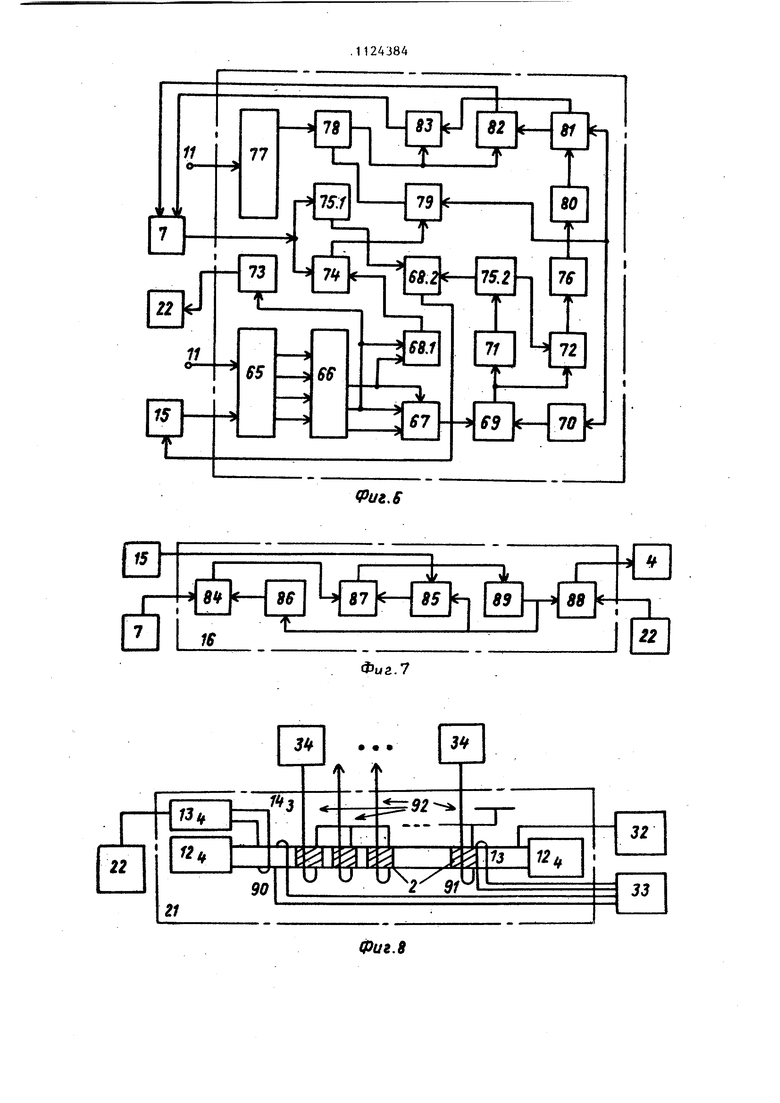

5. Устройство по пп.1-4, отличающееся тем, что блок управления содержи регистр команд, дешифратор команд, регистр адреса,триггеры с пятого .по восьмой, элементы И с девятого по одиннадцатьй, элементы НЕ с второго по четвертый, элементы ИЛИ с седьмого по одиннадцатый и элементы задержки.с девятого по одиннадцатый, причем выходы регистра команд подключены к входам дешифратора команд, первый, второй и третий, выходы которого соединены с входами седьмого элемента ИЛИ, выход которого подключен к первому входу пятого триггера, второй вход которого соединен с выходом второго элемента НЕ, а выход - с входом девятого элемента задержки и первым входом десятого элемента ИЛИ, первый и второй входы восьмого элемента ИЛИ подключены соответственно к второму выходу дешифратора команд и входу десятого элемента задержки и к третьему выходу дешифратора команд, а выход соединен с первым входом шестого триггера, выход которого подключен к пepвc ry входу одиннадцатого элемента ИЛИ, первый вход девятого элемента ИЛИ соединен с выходом третьего элемента НЕ, а второй вход - с первым выходом четвертого элемента НЕ вход которого подключен к выходу девятого элемента задержки, а второй выход к второму входу десятого элемента ИЛИ выход которого соединен с входом седьмого триггера, выход которого подключен к входу второго элемента НЕ второму входу одиннадцатого элемента ИЛИ, входу одиннадцатого элемента задержки и первому входу восьмого триггера, второй вход которого соединен с выходом одиннадцатого элемента задержки, а первый и второй выходы подключены соответственно к первым входам десятого и одиннадцатого элементов .И, вторые входы которых соединены с выходом девятого элемента И, первый вход которого подключен к выходу регистр-а адреса, а второй вход к выходу одиннадцатого элемента ИЛИ, вход третьего элемента НЕ и второй вход шестого триггера являются первым входом блока, вторым входом которого является первый вход регистра команд, второй вход которого и вход регистра адреса являются третьим входом блока, выходами с первого по четвертый которого являются выходы

лесятого -элемента И, девятого эле- и одиннадцатого элемента И соответмента ИЛИ, десятого элемента задержки ственно.

1124384 .

| название | год | авторы | номер документа |

|---|---|---|---|

| Ферроакустическое запоминающее устройство | 1984 |

|

SU1238153A1 |

| Счетное устройство, сохраняющее информацию при отключении питания | 1987 |

|

SU1492476A1 |

| Запоминающее устройство | 1980 |

|

SU911614A1 |

| Логическое запоминающее устройство | 1978 |

|

SU752479A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Ассоциативное запоминающее устройство | 1985 |

|

SU1274002A1 |

| Устройство для контроля информационных характеристик ферроакустического носителя информации | 1985 |

|

SU1386950A1 |

| Запоминающее устройство | 1983 |

|

SU1115105A1 |

| Кольцевая пакетная сеть передачи информации | 1987 |

|

SU1555888A1 |

| Устройство управления | 1984 |

|

SU1171790A1 |

1. ЛОГИЧЕСКОЕ ЗАПОМИНАЩЕЕ УСТРОЙСТВО, содержащее ферроакустический накопитель, первый усилитель считывания, группу элементов И, элементы НЕ-И, распределитель разрядных импульсов, блоки местного управления, распределитель адресных импульсов, блок управления, формирователи -импульсов записи, генераторы ультразвуковых импульсов, блок управляемой задержки, формирователь синхросигналов и усилитель синхронизации, причем запоминающие ячейки ферроакустическо- го накопителя и распределитель раз- рядных импульсов состоят из металлических стержней, ПОКРЫТЫХ тоНкопленочным магнитным материалом, демпферов, закрепленных на концах металлических стержней и разрядных шин, расположенных На металлических.стержнях с постоянным по их длине шагом, одни концы этих металлических стержней соединены с шиной нулевого потенциа- . ла, и через,узлы сопряжения электромеханически соединены с выходами первого второго и третьего генераторов ультразвуковых импульсов соответственно, другой конец металлического стержня одной из запоминающих ячеек подключен к входу первого усилителя считывания другие концы-металлических стержней запоминающих ячеек соединены с шиной синхронизации, выходы которой подключены к входам усилителя синхрониза1Ц1и, выход которого соединен с входом формирователя синхросигналов, выход которого подключен к первому входу первого блока местного управления, выход которого соединен с первым управляющим входом распределителя адресных импульсов и первым i входом второго блока местного управления, выход которого подключен к (Л входу стробирования первого усилителя считывания, выход которого соединен с первым входом блока управляемой задержки, первые вход и выход блока управления подключены соответственно к первому выходу и к второму управляющему входу распределителя адресных импульсов, второй, третий 1C и четвертый выходы которого соедине4ik ны с входами первого, второго и тре00 С 4 тьего генераторов ультразвуковых мпульсов, а пятый выход соединен с вторым входом первого блока местного управления, входы разрядных шин распределителя разрядных импульсов соединены с шиной нулевого потенциала, выходы каждой разрядной шины распре делителя разрядных импульсов, кроме первой, подключены к первому входу предьщущего элемента НЕ-И, а выход первой разрядной шины распределителя разрядных импульсов подключен к первому входу последнего элемента НЕ-И:, выходы элементов НЕ-И соединены с

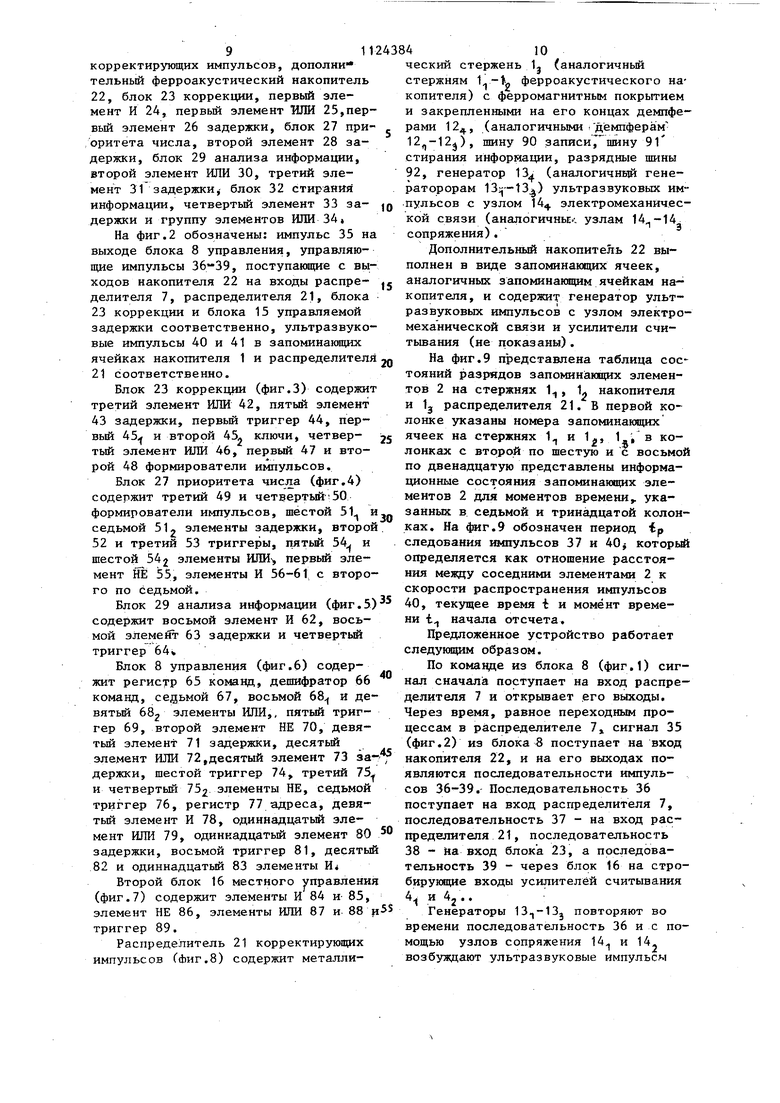

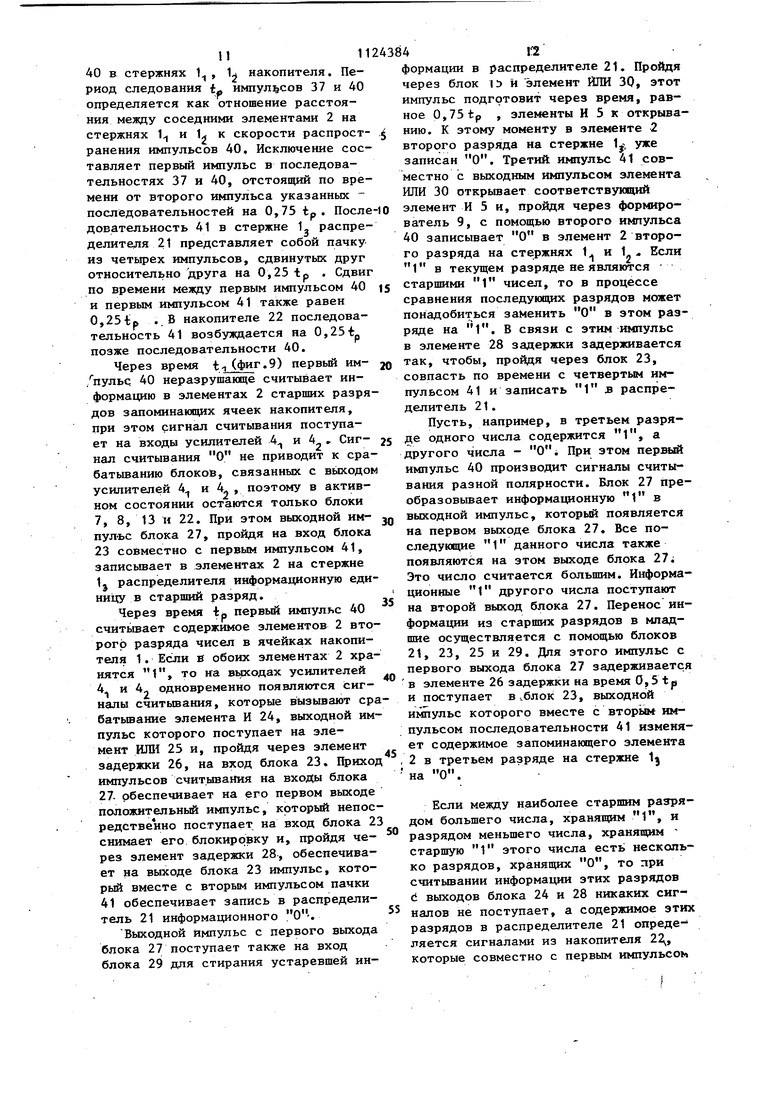

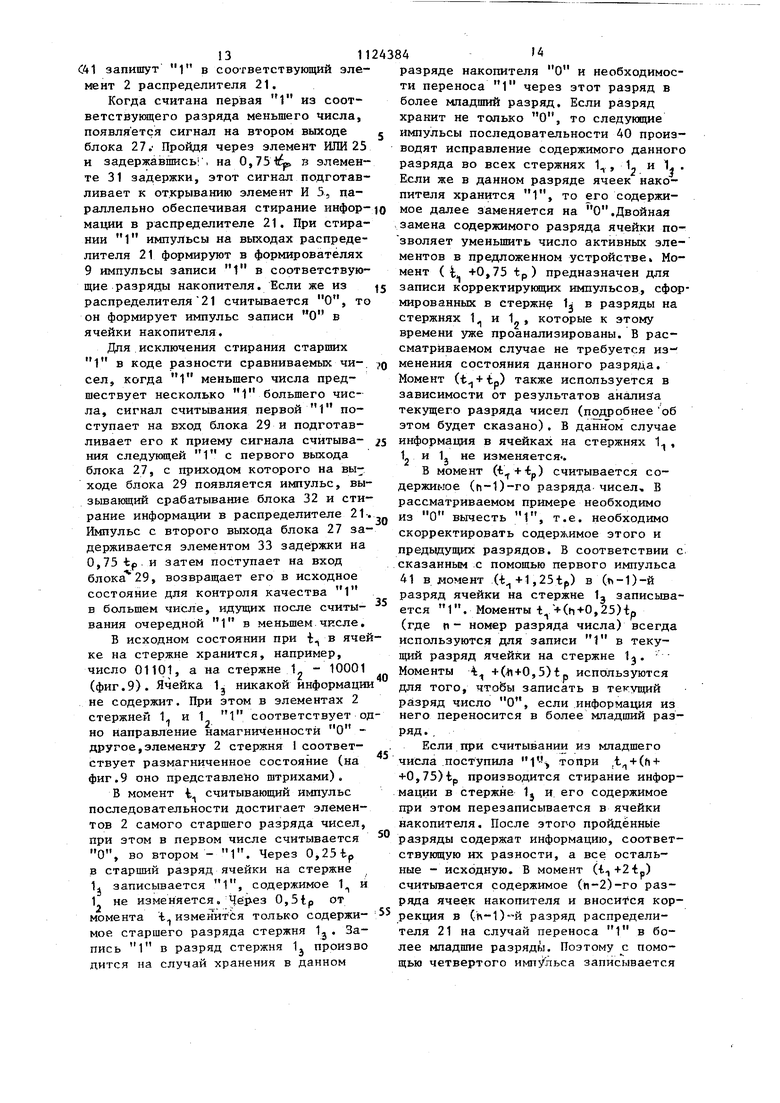

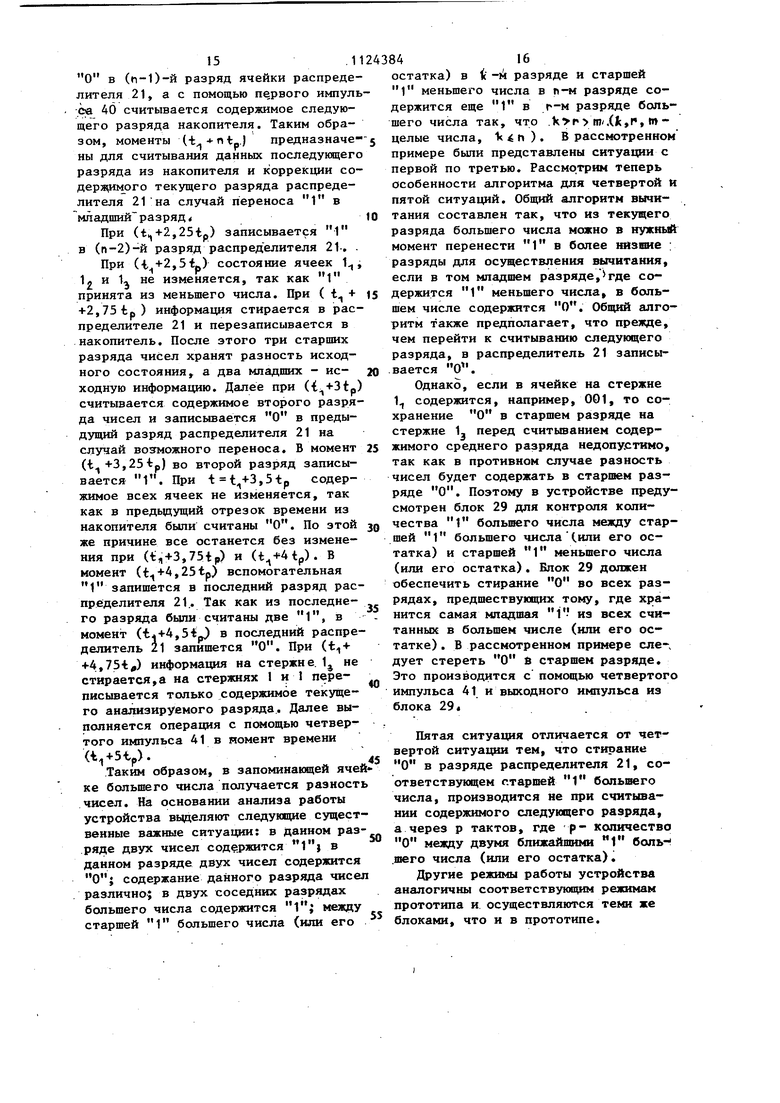

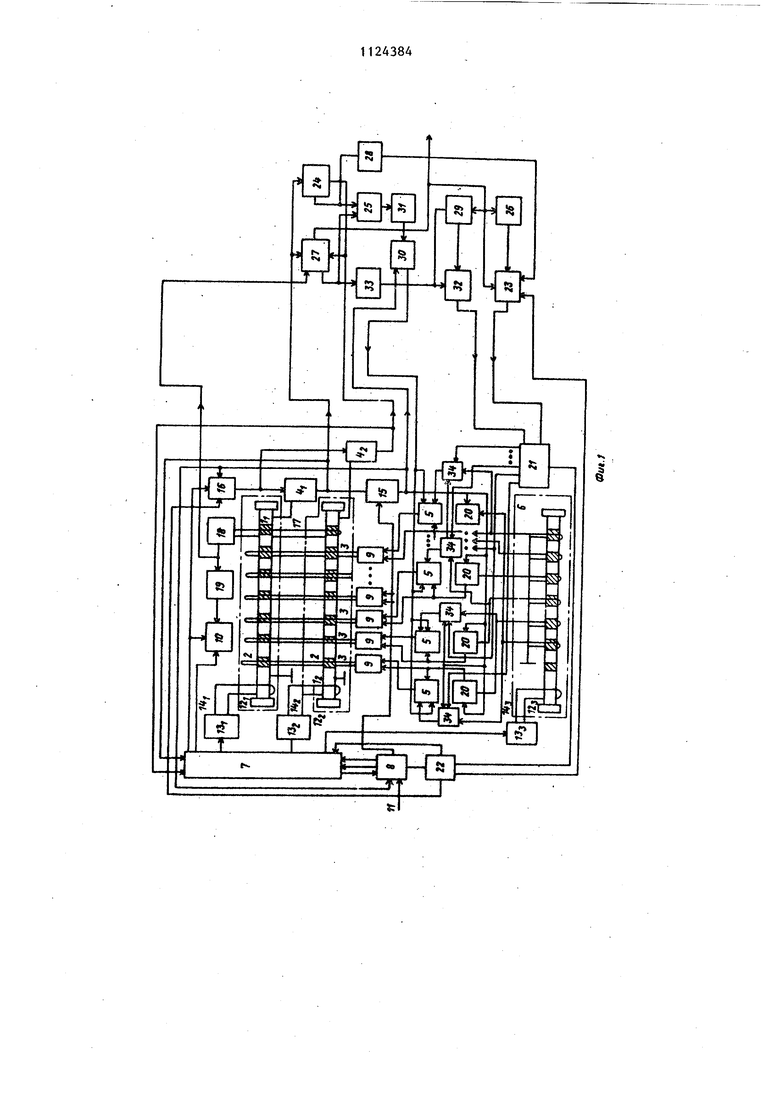

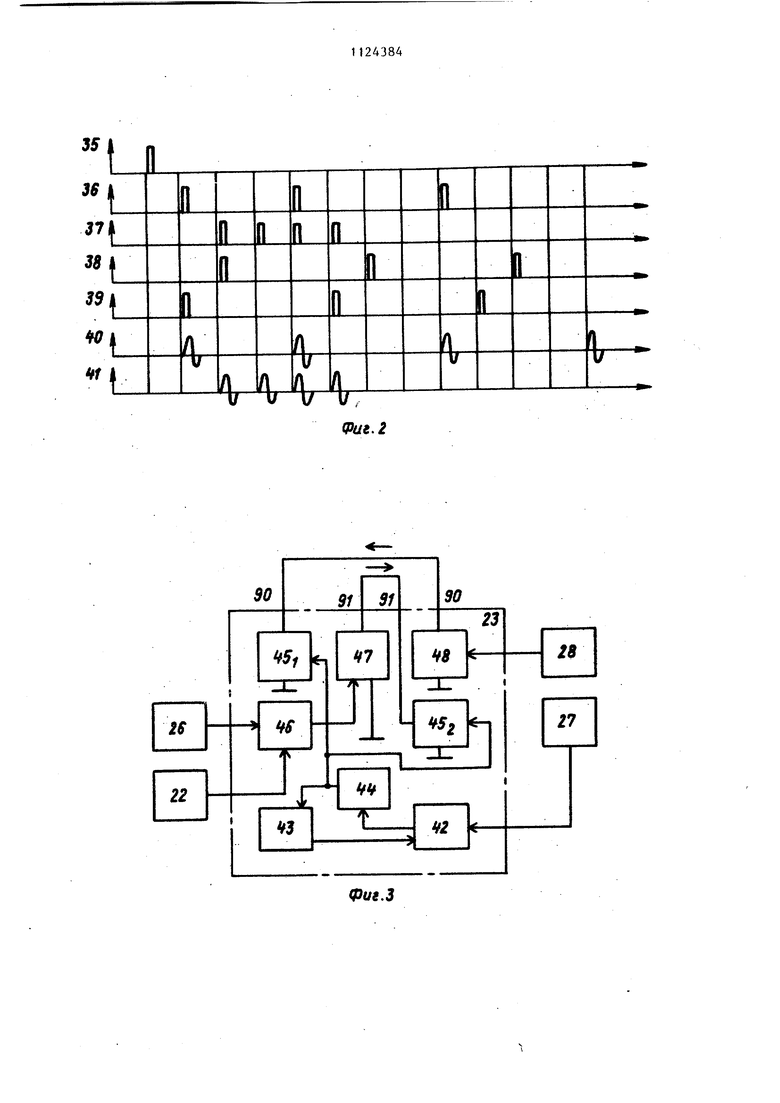

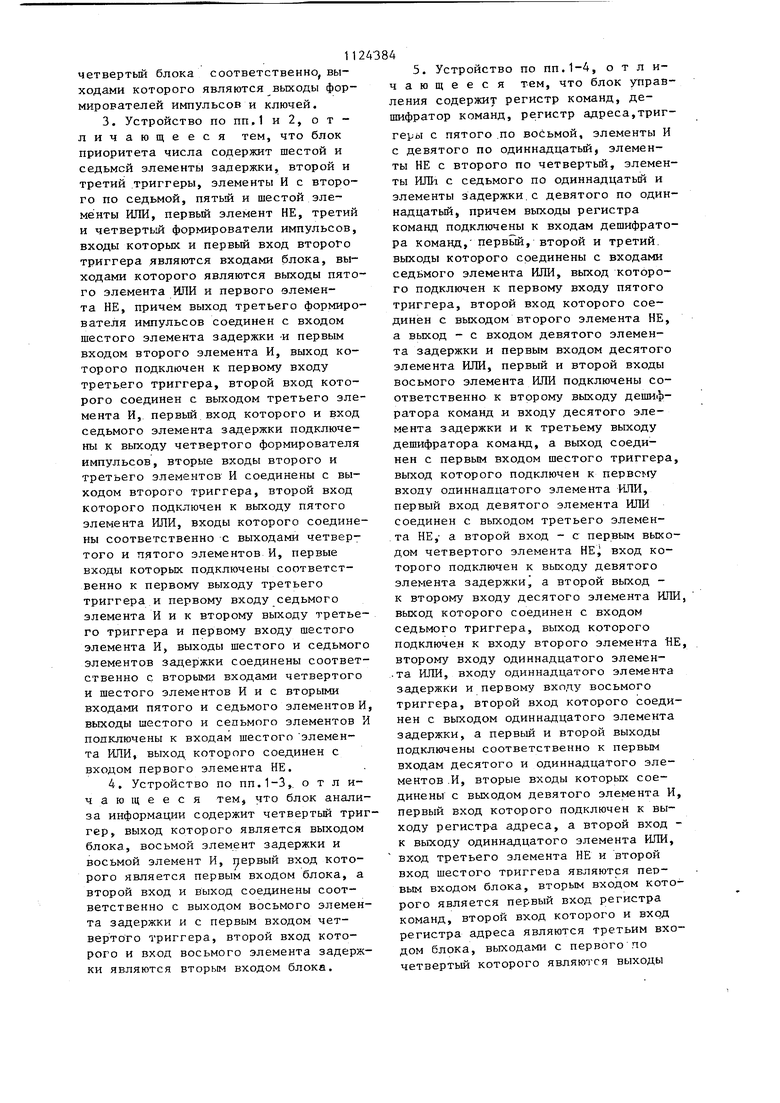

1 Изобретение относится к вычислительной технике и может использоваться в вычислительных и управляющих системах, где требуется хранение данных и вьшолнение арифметических действий над ними, т.е. в системах типа Ассоциативный процессор. Известно логическое запоминающее устройство, содержащее основной блок процессора, который содержит , вьтолненную на цилиндрических магнитных пленках, которые охвачены 256 опросными разрядными шинами, и позволяющуш выполнять последовательную поразрядную запись по адресу и неразрушающее считывание по произвольному доступу, накопитель ответов, выполняющий сравнение с поисковым образом (ПО) при поиске, запись результата и отт-ета и буферную запись информации при вводе-выводе,и блок управле-ния LI , Недостатки известного устройства обусловлены низкой надежностью и сложностью операций по сдвигу и перемещению данных в накопителях ответов. Наиболее .близким, техническим решением к изобретению является логическое запоминакицее устройство, содержащее входной блок, своим выходом под-ключенный к входу блока управления (БУ), выход которого соединен с одним входом адресного распределителя,, выход которого в свою очередь подключен к второму входу БУ, причем другой выход адресного распределителя соединен с входом блока блокировки запоминающих ячеек (БЗЯ), остальные выходы адресного распределителя (АР) подключены к входам соответствующих генераторов последовательностей ультразвуковых импульсов (ПУИ),выход БУ также подключен к соответствующему входу блока управляемой задержки сигнала считывания, а третий вход БУ соединен с выходом блока управляемой задержки (ВУЗ), выходы генераторов ИУИ через узлы сопряжения (УС) связаим с cdivi летствующими им запоминаю2щими ячейками (ЗЯ), которые содержат локальные запоминающие элементы (ЗЭ) числа разрядов в каждой ЗЯ одинаковы, запоминающие элементы в ЗЯ расположены с постоянным шагом, равным шагу меж,цу разрядными шинами и выходными шинами разрядного распределителя (РР), функцию считьшания в устройстве выполняют соединенные гальванически последовательно ЗЯ, изготовленные в виде металлических магнитных лент, один конец которых заземлен, а другой подключен к входу усилителя считывания (УСЧ), выход которого подключен к входу блока ВУЗ, выход которого соединен с одним входом блока блокировки считывания (БС) и одним из входов каж,дого элемента И и каждого элемента НЕ-И, к другому входу блока БС подключен выход блока БЗЯ, который также подключен к второму входу АР, выход блока БС подключен к второму входу УСЧ, индуктивно с помощью обмотки синхронизации (ОС) вход усилителя синхронизации связан с 33 каждои ЗЯ, хранящими постоянно информационные О, выход усилителя синхронизации подключен к входу преобразователя длительности сигнала синхронизации, выход которого подключен к второму входу первого блока местного . управления, с ЗЯ индуктивно сг тзаны разрядные шины (РШ), каждая из которьк соединена с выходом соответствующего формирователя (Ф), один вход которого подключен к соответствующему элементу И,а другой - к соответствующему элементу НЕ-И выход каждого НЕ-И подключен к соответствукщему входу соответствующего элемента И, связанного с тем же блоком Ф, что и данный элемент НЕ-И, каждому разряду накопителя соответствует один элемент И и один элемент НЕ-И, каждому разряду накопителя соответствует один элемент И и один элемент НЕ-И, каждая р-ая выходная шина подключена к третьему входу элемента И (р-1)-го разряда ЗЯ и к второму nxo/iy элемента НЕ-И (р-2)-го разряда, за исключе нием последней (по движению ПУИ) шины, связанной только с элементом НЕ-И Недостатками прототипа являются ограниченные функциональные возможнос ти (вследствие невозможности выполнен Нин операций сравнения и вычитания хранящихся в нем чисел) и низкая надежность из-за низкой дублирующей способности. Цель изобретения - расширение функ циональных возможностей устройства за счет осуществления операций сравнения и вычитания хранящихся в нем чисел. Поставленная цель достигается устройство, содержащее ферроакустический накопгтель, первый усилитель считывания, группу элементов И, элементы НЕ-И, распределитель разрядных импульсов, блоки местного управления распределитель адресных импульсов Ълок управления, формирователи /1мпульсов записи, генераторы ультразвуковых импульсов, блок упфарляемой задержки, формирователь синхросигналов и усилитель синхронизации причем запоминающие ячейки ферроакустического Накопителя и распределител разрядных импульсов состоят из металлических стержней, покрытых тонкогшеночным магнитным материалом, демп5)е- ров, закрепленных на концах металлических стержней и разрядных шин, рас положенных на металлических стержнях с постоянным по их длине шагом, одни концы этих металлических стержней со единены с шиной нулевого потенциала и через узлы сопряжения электромеханически соединены с выходами первого, второго и третьего генераторов ультразвуковых импульсов соответственно, другой конец металлического стержня одной из запоминающих ячеек подключен к входу первого усилителя считывания, другие концы металлических стержней запоминающих ячеек соединены с шиной синхронизации, выходы которой подключены к входам усилителя синхронизации, выход которого соединен с входом формирователя синхросигналов-, выход которого соединен с входом формирователя синхросигналов, выход которого подключен к первому входу первого блока местного управления,- выход которого соединён с первым управлякмцим входом распределителя адресных импульсов и первым входом второго блока местного управления, выход которого подключен к входу стробирования первого усилителя считывания, выход ко орого соединен с первым входом блока управляемой задержки, первые /вход и выход блока управления подключеьы соответственно к первому выходу и к второму управляющему входу распределителя адресных импульсов, второй, третий и четвертый выходы которого соединены с входами первого, второго и третьего генераторов ультразвуковых импульсов, а пятый выход соединен с вторым входом первого блока местного управления, входы разрядных шин распределителя разрядных импульсов соединен с шиной нулевого потенциала, выходы каждой разрядной шины распределителя разрядных импульсов, кроме первой, подключены к первому входу предыдущего элемента НЕ-И, а выход первой разрядной шины распределителя разрядных импульсов подключен к первому входу последнего элемента НЕ-И, выходы элементов НЕ-И соединены с первыми входами одноименных элементов И группы и формирователей импульсов записи, вторые входы которых подключены к выходам одиоимекнык элементов И группы, а выходы - к входам разрядных шин ферроакустического накопителя, вторые входы элементов НЕ-И, блока управления и второго блока местного управления соединены с выходом блока управляемой задержки, второй вход которого подключен к второму выходу блока управления,третий вход которого является входом устройства,- введены блок стирания ин- формации, блок приоритета числа,блок коррекции, распределитель корректирующих импульсов, второй усилитель считывания, блок анализа информации, элементы задержки группы элементов ИЛИ, первый элемент И, первый и второй элементы ИЛИ и дополнительный ферроакустический накопитель, причем вход второго усилителя считывания подключен к другому концу металлического стержня другой запоминающей ячейки, а вход стробирования-- к выходу второго блока местного управления, выход первого усилителя считыва ния соединен с первыми входами блока приоритета числа и первого элемента И и первым информационным входом растпределителя адресных импульсов, второй информационный вход которого подключей к выходу второго усилителя считывания и вторым входам первого элемента И и блока приоритета числа, третий вход которого соединен с выходом усилителя синхронизации, а первый выход - с первыми входами блока анализа информации, блока коррекции и первого элемента(Задержкиу выход которого подключен к второму входу блока коррекции, третий вход которого соединен с выходом второго элемента задержки, вход которого подключен к выходу первого элемента И и первому входу первого элемента ИЛИ, выход которого соединен с входом третьего элемента задержки, а второй вход - с вторым выходом блока приоритета числа и входом четвертого элемента задержки выходкоторого подключен к первому входу блока стирания информации и второму входу блока анализа инфор-f . мации,выход которого соединен с вторым входом блока стирания информации. выход которого и выходы блока коррекции подключены соответственно к входу стирания и к входам записи распределителя корректирунядих импульсов, управлякядий вход которого соединен с первым выходом дополнительного ферроакустического накопителя,- а выходы подключены к первым входам одноименных элементов ИЛИ группы, вторые входы которых соединены с выходами одноименных разрядных, шин распределителя разрядных импульсов,, выходы элементов ИЛИ группы подключены к вторьи входам одноименных элементов И группы, а третьи входы - к выходу блока управляемой задержки и первому входу второго элемента ИЛИ, второй вход которого соединен с выходом третьего элемента задержки, а выход - с тре тьими входами элементов И группЫу вход дополнительного ферроакусТического нако1 итёля подключен к третьему выходу блока управления, второй выход - к третьему управлянщему входу распределителя адресных импульсов, третий выход - к третьему входу второго блока местного управления, а четвертый выход - к четвертому входу блока коррекции четвертый выход блока управления соединен с четвертым управлякицим входом распределител адресньрс импульсов, первый выход бло ка приоритета числа является выходом устройства. Блок коррекции содержит формирова тели импульсов, ключи, третий и четвертый элементы ИЛИ, первьш триггер и пятый элемент задержки, выход которого подключен к первому входу третьего элемента ИЛИ, выход которого соединен с входом первого триггера, выход которого подключен к входу пятого элемента задержки и первым входам первого и второго ключей, вторые входы которых и одни из входов первого и второго формирователей импульсов соединены с шиной нулевого потенциала, причем выход четвертого элемента ИЛИ подключен к другому входу первого формирователя импульсов, второй вход третьего элемента ИЛИ, другой вход второго формирователя импульсов, первый и второй входы четвертого элемента ИЛИ являются входами с первого по четвертый блока соответственно, выходами которого являются выходы формирователей импульсов и ключей. Блок приоритета числа содержит шестой и седьмой элементы задержки, второй и третий триггеры, элементы И с второго по седьмой, пятый и шестой элементы ИЛИ,, первый элемент НЕ, третий и четвертый формирователи импульсов входы которых и первый вход второго триггера являются входами блока, выходами которого являются выходы пятого элемента ИЛИ и первого элемента НЕ, причем выход третьего формирователя импульсов соединен с входом шестого элемента задержки и первым входом второго элемента И, выход которого подключен к первому входу третьего триггера,.второй вход которого соединен с выходом третьего элемента И, первый вход которого и вход седьмого элемента задержки подключены к выходу четвертого формирователя импульсов, вторые входы второго и третьего элементов И соединены с выходом второго триггера.,второй вход которого подключен к выходу пятого элемента ИЛИ, входы которого соединены соответственно с выходами четвертого и пятого элементов И, первые входы которых подключены соответственно к первому выходу третьего триггера и первому входу седьмого И- и к второму выходу третьего триггера и первому входу шестого элемента И, вы ходы шестого и седьмого элементов задержки соединены соответственно с вторыми входами четвертого и шестого элементов И и с вторыми входами пятого и седьмого элементов И, выходы шестого и седьмого элементов И подключены к входам шестого элемента ИЛИ, выход которого соединен с входом первого элемента НЕ, Блок анализа информации содержит четвертый триггер, выход которого является выходом блока, восьмой элемент задержки и восьмой элемент И, первый вход которого является первым входом блока, а второй вход и выход соединены соответственно с выходом восьмого элемента задержки и с первым входом четвертого триггера, второй вход кото рого и вход восьмого элемента задержки являются вторым входом блока. Блок управления содержит регистр команд, дешифратор команд, регистр адреса, триггеры с пятого по восьмой, элементы И с девятого по одиннадцатый, элементы НЕ с второго по четвертый, элементы ИЛИ с седьмого по одиннапиатый и элементы задержки с девято го по одиннадцатый, причем выходы регистра команд подключены к входам дешифратора команд, первый, второй и третий выходы которого соединены с входами седьмого элемента ИЖ, выход котброго подключен к первому входу пятого триггера, второй вход которого ,соединен с выходом второго Цемента НЕ, а выход - с -входом девятого элемента задержки и первым входом десятого элемента ИЛИ, первый и второй входы восьмого элемента ИЛИ подключейы соответственно к второму выходу дешифратора команд и входу десятого элемента задержки и к третьему выходу дешифратора командна выход , соединен с первым входом шестого триггера, выход которого подключен к пер-; вому входу одиннадцатого элемента ИЛИ первый вход девятого элемента ИЛИ соединен с выходом третьего элемента НЕ, а второй вход - с первым выходом четвертого элемента НЕ, вход которого подключен к выходу девятого элемента задержки, а второй выход к второму входу десятого элемента ИШ выход Которого соединен с входом триггера, выход которого подключен к входу второго элемента НЕ,, втор ому входу одиннадцатого элемента ИЛИ, входу одиннадцатого элемента задержки и первому входу восьмого триггера,второй вход которого соединен с выходом одиннадцатого элеменН та задержки, а первый и второй выходы подключены соответственно к первым входам десятого и одиннадцатого элементов И, вторые входы которыхсоеди1148 нены с выходом девятого элемента И, первый вход которого подключен к выходу регистра адреса., а второй вход к вьрсоду одиннадцатого элемента ИЛИ, BXfц третьего элемента НЕ-и второй вход fflecToro триггера являются первым входом блока, вторым входом которого является первый вход регистра команд, второй вход которого и вход регистра адреса являются третьим входом блока, выходами с первого по четвертый которого являются выходы десятого элемента И, девятого элемента ИЛИ, десятого элемента задержки и одиннадцатого элемента И соответственно. На фиг,1 изображена функциональная схема предложенного устройства; на фиг,2 - временные диаграммы последовательностей управля Лцих и информационных импульсов при работе устройства в режиме вычитания; на фиг,3-8 функциональные схемы наиболее пред почтительных вариантов выполнения соответственно блоков; коррекции, приоритета числа, анализа информации, управления, местного управления и распределителя корректирующих импульсов; на фиг,9 - хронометрированные таблицы состояний запоминающих элементов в ячейках накопителя ив распределителе, поясняющие, работу устррйства. Предложенное устройство содержит (Фнг,1) ферроакустический накопитель, включающий металлические стержни 1. и 1j с тонкопленочными запоминающими элементами 2 и разрядные шины 3, первый 4 и второй 4 усилители считывания, группу элементов И 5, распределитель 6 разрядных импульсов, выполненный на элементах, аналогичных ферроакустическому накопителю, распределитель 7 адресных импульсов, блок 8 управления, формирователи 9 импульсов записи, первый блок 10 местного управления. На фиг.1 обозначены вход 11 устройства и демпферы ;12i и 12j, входящие в ферроакустический накопитель и распределитель 6 Устройство содержит также генераторы 13y,-13i ультразвуковых импульсов с первого по третий, узлы сопряжения с первого по третий, блок 15управляемой задержки, второй блок 16местного управления, шину 17 синхронизации, усилитель 18 синхронизации, формирователь 19 синхросигналов, элементы НЕ-И 20, распределитель 21 911 корректирующих импульсов, дополни- тельный ферроакустический накопитель 22, блок 23 коррекции, первый элемент И 24, первый элемент ШШ 25,первьй элемент 26 задерзкки, блок 27 приоритета числа, второй элемент 28 задержки, блок 29 анализа информации, второй элемент ИЛИ 30, третий элемент 31 задержки, блок 32 стирания информации, четвертый элемент 33 задержки и группу элементов ИЛИ 34 На фиг.2 обозначены: импульс 35 на выходе блока 8 управления, управляющие импульсы 36-39, поступающие с выходов накопителя 22 на входы распределителя 7, распределителя 21, блока 23 коррекции и блока 15 управляемой задержки соответственно, ультразвуковые импульсы 40 и 41 в запоминакицих ячейках накопителя 1 и распределителя 21 соответственно. Блок 23 коррекции (фиг.З) содержит третий элемент ШШ 42, пятый элемент 43 задержки, первьш триггер 44, первьй 45 и второй 45 ключи, четвертый элемент ШШ 46, первый 47 и второй 48 формирователи импульсов. Блок 27 приоритета числа (фиг.4) содержит третий 49 и четвертый:50 формирователи импульсов, шестой 51 и седьмой 51 элементы задержки, второй 52 и третий 53 триггеры, пятьй 54. и шестой 542 элементы Ш1И первый элемент НЕ 55, элементы И 56-61 с второго по седьмой. Блок 29 анализа информации (фиг.5) содержит восьмой элемент И 62, восьмой элемент 63 задержки и четвертый триггер 64v Блок 8 управления (фиг.6) содержит регистр 65 команд, дешифратор 66 команд, седьмой 67, восьмой 68 и девятый 68 элементы ИЛИ,, пятый триггер 69, второй элемент НЕ 70, девятый элемент 71 задержки, десятьй элемент ИЛИ 72,десятый элемент 73 заг держки, шестой триггер 74, третий 75 и четвертый 752 элементы седьмой триггер 76, регистр 77 адреса, девятый элемент И 78, одиннадцатьй элемент ИЛИ 79, одиннадцатьй элемент 80 задержки, восьмой триггер 81, десятый 82 и одиннадцатый 83 элементы И4 Второй блок 16 местного управления (фиг.7) содержит элементы И 84 и 85, элемент НЕ 86, элементы ИЛИ 87 и 88 p триггер 89. Распределитель 21 корректирующих импульсов С(Ьиг.8) содержит метапли410ческий стержень 1j (аналогичный стержням ферроакустического накопителя) с ферромагнитным покрытием и закрепленными на его концах демпферами 12, (аналогичными демпферам ), шину 90 записи 91 стирания информации, разрядные шины 92, генератор 13 (аналогичный генераторорам ) ультразвуковых импульсов с узлом 14 электромеханической связи (аналогичны:., узлам сопряжения). Дополнительный накопитель 22 выполней в виде запоминающих ячеек, аналогичных запоминающим ячейкам на- копителя, и содержит генератор ультразвуковых импульсов с узлом электромеханической связи и усилители считьшания (не показаны). На фиг.9 представлена таблица состояний разрядов запоминающих элементов 2 на стержнях 1, 1 накопителя и 1 распределителя 21. В первой колонке указаны номера запоминающих ячеек на стержнях 1 и 1л, U« в колонках с второй по шестую и с восьмой по двенадцатую представлены информационные состояния запомина1сщих элементов 2 для моментов времени,, указанных в. седьмой и тринадцатой колонках. На фиг.9 обозначен период tp следования импульсов 37 и 40 который определяется как отношение расстояния между соседними элементами 2 к скорости распространения импульсов - ... 40, текущее время t и момент времени t начала отсчета. Предложенное устройство работает следующим образом. По комацде из блока 8 (фиг.1) сигнал сначал1а поступает на вход распределителя 7 и открывает .его выходы. Через время, равное переходным процессам в распределителе 7 сигнал 35 (фиг.2) из блока 8 поступает на вход накопителя 22, и на его выходах появляются последовательности импульсов 36-39. Последовательность 36 поступает на вход распределителя 7, последовательность 37 - на вход распределителя 21, последовательность 38 - ha вход блока 23, а последовательность 39 - через блок 16 на стро бирующие входы усилителей считывания 4 и 42 .. Генераторы повторяют во времени последовательность 36 и с помощью узлов сопряжения 14 и 14. возбуждают ультразвуковые импульсы 40 в стержнях 1, 1 накопителя. Период следования t. импульсов 37 и 40 определяется как отношение расстояния между соседними элементами 2 на стержнях 1 и Ь к скорости распространения импульсов 40, Исключение составляет первый импульс в последовательностях 37 и 40, отстоящий по времени от второго импульса указанных последовательностей на 0,75 tp. После довательность 41 в стержне 1, распределителя 21 представляет собой пачку из четьфех импульсов, сдвинутых друг относительно друга на 0,25 tp . Сдвиг по времени между первым импульсом 40 и первым импульсом 41 также равен 0,25tp ..8 накопителе 22 последовательность 41 возбуждается на 0,25t позже последовательности 40. Через время t-i (фиг.9) первьй им/пульс 40 неразрушающе считывает информацию в элементах 2 старших разря дов запоминающих ячеек накопителя, при этом сигнал считывания поступает на входы усилителей 4 и 4 .. Сигнал считывания О не приводит к сра батьшанию блокой, связанных с вькодо усилителей 4 и 4- , поэтому в активном состоянии остаются только блоки 7, 8, 13 и 22, При этом выходной импул-ьс блока 27, пройдя на вход блока 23 совместно с первым импульсом 41, записьшает в элементах 2 на стержне 1j распределителя информационную еди ницу в старший разряд. Через время ip первый импульс 40 считывает содержимое элементов 2 вто рого разряда чисел в ячейках накопителя 1. Если б обоих элементах 2 хра нятся 1, то ка выходах усилителей 4 и 4. одновременно появляются сигналы считывания, которые вызывают ср батьшание элемента И 24, выходной им пульс которого поступает на элемент ШШ 25 и, пройдя через элемент задержки 26, на вход блока 23, Прихо импульсов считывания на входы блока 27- обеспечивает на его первом выходе положительный импульс, крторый непос редственно поступает, на вход блока 2 снимает его блокировку и, пройдя через элемент задержки 28, обеспечивает на выходе блока 23 импульс, который вместе с вторым импульсом пачки 41 обеспечивает запись в распределитель 21 информационного , Выходной импульс с первого выхода блока 27 поступает также на вход блока 29 для стирания устаревшей информации в распределителе 21. Пройдя через блок о и элемент ИЛИ 30, этот импульс подготовит через время, равное 0,75tp , элементы И 5 к открыванию. К этому моменту в элементе 2 второго разряда на стержне Ij, уже записан О, Третий импульс 41 совместно с выходным импульсом элемента ИЛИ 30 открывает соответствующий элемент И 5 и, пройдя через формирователь 9, с помощью второго импульса 40 записывает О в элемент 2 второго разряда на стержнях 1. и 1 , Если 1 в текущем разряде не являются старшими 1 чисел, то в процессе сравнения последующих разрядов может понадобиться заменить О в этом разряде на 1. В связи с этим импульс в элементе 28 задержки задерживается так, чтобы, пройдя через блок 23, совпасть по времени с четвертым импульсом 41 и записать 1 JB распределитель 21. Пусть, например, в третьем разряде одного числа содержится 1, а другого числа - При этом первый импульс 40 производит сигналы считывания разной полярности. Блок 27 преобразовывает информационную 1 в выходной импульс, который появляется на первом выходе блока 27, Все последующие 1 данного числа также появляются на этом выходе блока 27; Это число считается большим. Информационные 1 другого числа поступают на второй выход блока 27. Перенос информации из старших разрядов в младшие осуществляется с помощью блоков 21, 23, 25 и 29, Для этого импульс с первого выхода блока 27 задерживается в элементе 26 задержки на время 0,5 t« и поступает в .блок 23, выходной импульс которого вместе с вторым импульсом последовательности 41 изменяет содержимое запоминающего элемента 2 в третьем разряде на стержне 1 на О, Если между наиболее старшим разрядом большего числа, хранящим 1, и разрядом меньшего числа, хранящим старшую 1 этого числа есть несколько разрядов, хранящих О, то при считывании информации этих разрядов d выходов блока 24 и 28 никаких сигналов не поступает, а содержимое этих разрядов в распределителе 21 опреде- ляется сигналами из накопителя 22, которые совместно с первым импульсоь С41 запишут 1 в соответствующий элемент 2 распределителя 21. Когда считана первая 1 из соответствуклцего разряда меньшего числа, появляется сигнал на втором выходе блока 27. Пройдя через элемент ИЛИ 25 и задержавшись: , на 0,75 в элементе 31 задержки, этот сигнал подготавливает к открыванию элемент И 5. параллельно обеспечивая стирание информации в распределителе 21. При стирании 1 импульсы на выходах распределителя 21 формируют в формирователях 9 импульсы записи 1 в соответствующие разряды накопителя. Если же из распределителя21 считывается О, то он формирует импульс записи О в ячейки накопителя. Для исключения стирания старших в коде разности сравниваемых чи-. сел, когда 1 меньшего числа предшествует несколько 1 большего числа, сигнал считьшания первой 1 поступает на вход блока 29 и подготавего к приему сигнала считываливаетдующей 1 с первого выхода блока 27, с приходом которого на выходе блока 29 появляется импульс, вызьшающий срабатывание блока 32 и стирание информации в распределителе 21Импульс с второго выхода блока 27 задерживается элементом 33 задержки на 0,73 -fcp . и затем поступает на вход блока 29, возвращает его в исходное состояние для контроля качества 1 в большем числе, идущих после считывания очередной 1 в меньшем.числе, В исходном состоянии при t в ячей ке на стержне хранится, например, число 01101, а на стержне 1 - 10001 (фиг.9). Ячейка 1. никакой информации не содержит. При этом в элементах 2 стержней 1, и 1 1 соответствует од но направление намагниченности О другое,элементу 2 стержня 1 соответствует размагниченное состояние (на фиг.9 оно представлено штрихами). Б момент i считывающий импульс последовательности достигает элементов 2 самого старшего разряда чисел, при этом в первом числе считывается О, во втором - 1. Через 0,25tp В старший разряд ячейки на стержне 1 записывается 1, содержимое 1 и 1 не изменяется. Через 0,51р от момента i изменится только содержимое старшего разряда стержня 1j. Запись 1 в разряд стержня 1 произво дится на случай хранения в данном разряде накопителя О и необходимости переноса 1 через этот разряд в более младший разряд. Если разряд хранит не только О, то следуняцие импульсы последовательности 40 производят исправление содержимого данного разряда во всех стержнях 1. ,1 и 1. . Если же в данном разряде ячеек нако1пителя хранится 1, то его содержимое далее заменяется на О.Двойная замена содержимого разряда ячейки по зволяет уменьшить число активных элементов в предложенном устройстве. Момент (Ц +0,75 tp ) предназначен для записи корректирунндих импульсов, сформированных в стержн Ij в разряды на стержнях 1 и 1 , которые к этому времени уже проанализированы. В рассматрйваемом случае не требуется изменения состояния данного разряда. Момент (t + tp) также используется в зависимости от результатов анализа текущего разряда чисел (подробнее об этом будет сказано). В данном случае информация в ячейках на стержнях 1, 1 и 1, не изменяется-. в момент ((;„) считывается содержиыое (п-1)-го разряда чисел, В рассматриваемом примере необходимо цз О вычесть 1, т.е. необходимо скорректировать содержимое этого и предыдущих разрядов. В соответствии с. сказанным с помощью первого импульса 41 в момент (,25tp) в (л-1)-й разряд ячейки на стержне 1j записывается 1. Моменты (,25)-tp (где ц- номер разряда числа) всегда используются для записи 1 в текущий разряд ячейки на стержне 1л. - Моменты Л +(+0,5)tp используются для того, чтобы записать в текущий разряд число О, если информация из него переносится в более младший разряд . , Если при считывании из младшего числа .поступила 1S топри ,t + (fi + +0,75)tp производится стирание информации в стержне 1j и его содержимое при этом перезаписывается в ячейки накопителя. После этого пройденные разряды содержат информацию, соответствующую их разности, а все остальные - исходную. В момент (t +2tp) считывается содержимое (п-2)-го разряда ячеек накопителя и вносился коррекция в (Ь-1)й разряд распределителя 21 на случай переноса 1 в более младшие разряды. Поэтому с помощью четвертого имп/льса записывается О в (п-1)-й разряд ячейки распределителя 21, а с помощью первого импуль са 40 считывается содержимое следующего разряда накопителя. Таким образом, моменты (-fc + nt-.J предназначены для считывания данных последующего разряда из накопителя и коррекции содеря имого текущего разряда распределителя 21 на случай переноса 1 в младший разряд При (,25tp,) записывается 1 в (п-2)-й разряд распределителя 21-. . При (i +2,5tp) состояние ячеек 1 ly и U не изменяется, так как 1 принята из меньшего числа. При ( t + +2,75tp) информация стирается в распределителе 21 и перезаписывается в накопитель. После этого три старпшх разряда чисел хранят разность исходного состояния, а два младших - исходную информацию. Далее при (i;,+3tp) считывается содержимое второго разряда чисел и записывается О в предыдущий разряд распределителя 21 на случай воэтюжного переноса. В момент (,25-tp) во второй разряд записывается 1. При ,5tp содержимое всех ячеек не изменяется, так как в предьщущий отрезок времени из накопителя были считаны О. По этой же причине все останется без изменения при (t,+3,75tp) и (). В момент (,25tp) вспомогательная 1 запишется в последний разряд распределителя 21.. Так как из последнего разряда бьши считаны две 1, в момент (tj+4,5ip в последний распределитель 21 запишется О. При ( +4,75,) информация на стержне. 1 не стирается,а на стержнях 1 и 1 переписывается только содержимое текущего анализируемого разряда. Далее выполняется операция с псмощью четвертого импульса 41 в иомент времени (t Si, ). Таким образом, в запоминающей ячей ке большего числа получается разность чисел. На основании анализа работы устройства вцделяют следующие существенные важные ситуации: в данном разряде двух чисел содержится в данном разряде двух чисел содержится содержание данного разряда чисел различно; в двух соседних разрядах большего числа содержится между старшей 1 большего числа (или его остатка) в t- разряде и старшей 1 меньшего числа в п-м разряде содержится еще 1 в г-м разряде большего числа так, что . тХИ;,, mцелые числа, 1 4 г ). В рассмотренном примере были представлены ситуации с первой по третью. Рассмотрим теперь особенности алгоритма для четвертой и пятой ситуаций. Общий алгоритм вычитания составлен так, что из текущего разряда большего числа можно в нужный 1 в более Низшие момент перенести разряды для осуществления вычитания, если в том младшем разряде,где содержится 1 меньшего числа в бопьтем числе содержится О. Общий алгоритм также предполагает, что прежде, чем перейти к считыванию следующего разряда, в распределитель 21 записы-ваетсяОднако, если в ячейке на стержне 1 содержится, например, 001, то хранение в старшем разряде на стержие 1, перед считыванием содержимого среднего разряда недопустимо, так как в противном случае разность чисел будет содержать в старшем разряде О. Поэтому в устройстве предусмотрен блок 29 для контроля коли- чества 1 большего числа между старшей 1 большего числа Чили его остатка) и старшей 1 меньшего числа (или его остатка). Блок 29 должен обеспечить стирание О во всех разрядах, предшествующих тому, где хранится самая младшая 1 из всех считанных в большем числе (или его остатке) . В рассмотренном примере следует стереть О S старшем разряде. Это производится с помощью четвертого импульса 41 и выходного импульса из блока 29. Пятая ситуация отличается от четвертой ситуации тем, что стирание вертой ситуации тем, что стирание О в разряде распределителя 21, соответствующем старшей 1 большего числа, производится не при считывании содержимого следующего разряда, а через р тактов, где р- количество О между двумя ближайшими 1 боль.шего числа (или его остатка). Другие режимы работы устройства аналогичны соответствую1цим режимам прототипа и осуществляются теми же блоками, что и в прототипе.

55

ч

Ч

36

37

38

39

iPue.2

Фие.З

дзм.5

4Put.S

Фиг.7

Фиг.В

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Ильяшенко Е.И., Рудаков В.Ф | |||

| Ассоциативные запоминаюпще устройства на магнитных элементах | |||

| М., Энергия, 1975, с | |||

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Логическое запоминающее устройство | 1978 |

|

SU752479A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-11-15—Публикация

1983-08-03—Подача