которого подключены к выходам счетчика адресов, а управляющий вход соединен с входом генератора импульсов и управляющим входом счетчика адресов и является третьим управляющим входом устройства, адресными входами которого являются входы счетчика адресов.

2. Устройство по п.1, о т л ичающееся тем, что блок дешифрации и Сдвига информации содержи элементы И с девятого по шестнадцатый, второй элемент НЕ и элементы ИЛИ с четвертого по восьмой, выходы которых являются выходами блока, а первые и вторые входы соединены соответственно с выходами элементов И с девятого по шестнадцатьй, причем вход второго элемента НЕ соединен с первыми входами девятого.

двенадцатого, четьфнадцатого и шестнадцатого элементов И и является управляющим входом блока, выход второго элемента НЕ подключен к первым входам десятого, одиннадцатого, тринадцатого и пятнадцатого элементов И, вторые входы девятого, одиннадцатого, четырнадцатого и пятнадцатого элементов И являются первым входом блока, третьи входы девятого и пятнадцатого и вторые входы тринадцатого и шестнадцатого элементов И являются вторым входом блока, вторые входы десятого и двенадцатого и третьи входы тринадцатого и шестнадцатого элементов И являются третьим входом блока, четвертым входом которого являются третьи входы десятого,одиннадцатого,двенадцатого и четырнадцатого элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1108511A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU980166A1 |

| Репрограммируемое постоянное запоминающее устройство | 1989 |

|

SU1695384A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1096692A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1583938A1 |

| Вычислительная система "Антикон" для предотвращения столкновения судов | 1983 |

|

SU1136178A1 |

| Устройство для обучения | 1987 |

|

SU1559366A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1989 |

|

SU1689983A1 |

| Кольцевая пакетная сеть передачи информации | 1987 |

|

SU1555888A1 |

1. ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее накопитель, выходы которого соединены с входами усилителей считывания, выходы которых подключены к входам регистров числа, формирователи токов считьюания, выходы которых соединены с одними из входов накопителя, другие входы которого подключены соответственно к выходам формирователей адресных токов записи и к выходам формирователей разрядных токов записи, счетчик тактов,, дешифратор, первый злемент НЕ, элемГенты И, элементы ИЛИ, ключ, накопительный элемент и генератор импульсов, выход которого соединен с первыми входами первого и второго элементов И, выходы которых подключены соответственно к первому входу первого элемента ИЛИ и к первЕлм входам третьего и четвертого элементов И и входу счетчика тактов, и второй выходы которых соедине1сы с вторыми входами третьего и четвертого элементов И соответственно, выходы которых подключены соответственно к второму входу первого элемента ШШ и к первым входам формирователей адресных токов записи, причем выход первого элемента ИЛИ соединен с первы в1 входами формирователей токов считывания, третий вькод счетчика тактов .подключен к входу дешифратора, первый выход которого соединен с входом ключа, выход которого подключен к входу накопительного элемента и первым входам формирователей разрядных токов записи, вторые и третьи входы которых соединены соответственно с выходами второго и третьего элементов ИЛИ, входы второго элемента ИЛИ подключены к выходам пятого и шестого элементов И, а входы третьего элемента ИЛИ - к выходам седьмого и восьмого элементов И, второй и третий выходы дешифратора соединены соответственно с первыми входами пяСА того и восьмого элементов И и с первьми входами шестого и седьмого элементов И, вторые входы шестого и восьмого элементов И подключены к выходу первого элемента НЕ, вход которого соединен с вторыми входами пятого и седьмого элементов И и является числовым входом устройства, ел первым и вторым управляющим входами которого являются вторые входы перо вого и второго элементов И, о т л иСП чаюдееся тем, что, с целью повьшгения быстродействия устройства при считывании информации, в него введены блок дешифрахщи и сдвига информации, триггеры, выходы которых подключены к вторым входам формирователей токов считьтания, счетчик адресов и элементы задержки, выходы которых соединены с первыми входами триггеров, а вход - с вторыми входами триггеров и формирователей адресных токов записи и выходами блока дешифрации и сдвига информации,входы

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано в многопроцессорных вычислительных комплексах и вычислительных системах реального масштаба времени.

Известны запоминающие устройства СП и 21.

Одно из известных устройств содержит накопитель информации, регистры числа и адреса,-.дешифратор адреса, формирователи токов опроса и записи С11.

Недостатком этого устройства является малое быстродействие.

Наиболее близким техническим решением к предлагаемому является запоминающее устройство, содержащее накопитель информации, собранньй на элементах, обеспечивающих неразрушающее считьшание, с входами которого соединены формирователи разрядных и адресных токов записи и считывания входы которых через элементы И и ИЛИ соединены с дешифраторами адреса и тактов, генератор импульсов и счетчик тактов 2.

Недостатком известного устройства является малое быстродействие при

считывании информации, поскольку адрес считываемого слова должен находиться в регистре адреса до окончания цикла считьтания, так как он обеспечивает сигнал возбуждения выбранного формирователя адресного тока считывания, который в свою очередь должен присутствовать до окончания цикла считывания, очередной же цикл считьшания должен начинаться только после полного завершения предьщущего.

Цель изобретения - повьш1ение быстродействия запоминающего устройства

при считывании информации.

Указанная цель достигается тем, что в запоминающее устройство, содержащее накопитель, выходы которого соединены с входами усилителей считывания, выходы которых подключены к входам регистров числа, фop fflpoвaтeли токов считывания, выходы которых соединены с одникш из входов накопителя, другие входы которого подключены соответственно к выходам формирователей адресных токов записи и к выходам формирователей разрядных токов записи, счетчик тактов, дешифратор, первый элемент НЕ, элементы И, элементы ИЛИ, ключ, накопительный элемент и генератор импульсов, выход

31115

оторого соединен с первыми входами ервого и второго элементоп И, выоды которых подключены соответствено к первому входу первого элемена ИЛИ и к первым входам третьего и 5

етвертого элементов И н входу счетчика тактов, первый и второй выходы которых соединены с вторыми входами третьего ичетвертого элементов И

.- to соответственно, выходы которых под ключены соответственно к второму вхоу первого элемента ИЛИ и к первьм входам формирователей адресных токов записи, причем выход первого элемента ИЛИ соединен с первыми вхоами формирователей токов считывания, третий выход счетчика тактов подключен к входу дешифратора, первый выход которого соединен с входом ключа, выход которого подключен к вхо- 0

ду накопительного элемента и первым входам формирователей разрядных токов записи, вторые и третьивходы оторых соединены соответственно с

.- 25 выходами второго и третьего элемен тов ИЛИ, входы второго элемента ИЛИ подключены к выходам пятого и шестого элементов И, а входы третьего элемента ИЛИ - к выходам седьмого и восьмого элементов И, второй и 30 третий выходы дешифратора соединены соответственно с первыми входами пятого и восьмого элементов И и с первыми входами шестого и седьмого элементов И, вторые входы шестого и 35 восьмого элементов И подключены

к выходу первого элемента НЕ, вход которого соединен с вторыми входами пятого и седьмого элементов И и является числовьм входом устройства, 40 первым и вторым управляющими входами которого являются вторые входы первого и второго элементов И, введены блок дешифрации и сдвига информации, триггеры, выходы которых подключены 45 к вторым входам формирователей токов считьшания, счетчик адресов и элементы задержки, выходы которых соединены с первыми входами триггеров, а входы - с вторыми входами триггеров и 50 формирователей адресных токов записи и вьпсодами блока дешифрации и сдвига информации, входы которого подключены к выходам счетчиков адресов, а управляющий вход соединен 55 с входом генератора импульсов и управляюищм входом счетчика адресов и является третьим упраапяющим вхо1054

дом устройства, адресными нуодлми которого.являются входы счетчика адресов.

Кроме того, блок де1Ш1фрации и сдвига информации содержит элементы И с девятого по шестнадцатый, второй элемент НЕ и элементы ШТИ с четвертого rio восьмой, выходы которых являются выходами блока, а первые и вторые входы соединены соответственно с выходами элементов И с девятого по шестнадцатый, причем вход второго элемента НЕ соединен с первыми входами девятого, двенадцатого, четырнадцатого и шестнадцатого элементов И и является управляющим входом блока, выход второго элемента НЕ подключен к первым входам десятого, одиннадцатого, тринадцатого и пятнадцатого элементов И, вторые входы девятого, одиннадцатого, четырнадцатого и пятнадцатого элементов И являются первым входом блока, третьи входы девятого и пятнадцатого и вторые входы тринадцатого и шестнадцатого элементов И являются вторым входом блока, вторые входы десятого и двенадцатого и третьи входы тринадцатого и шестнадцатого элементов И являются третьим входом блока, четвертым входом которого являются третьи входы десятого, одиннадцатого, двенадцатого и четырнадцатого элементов. И.

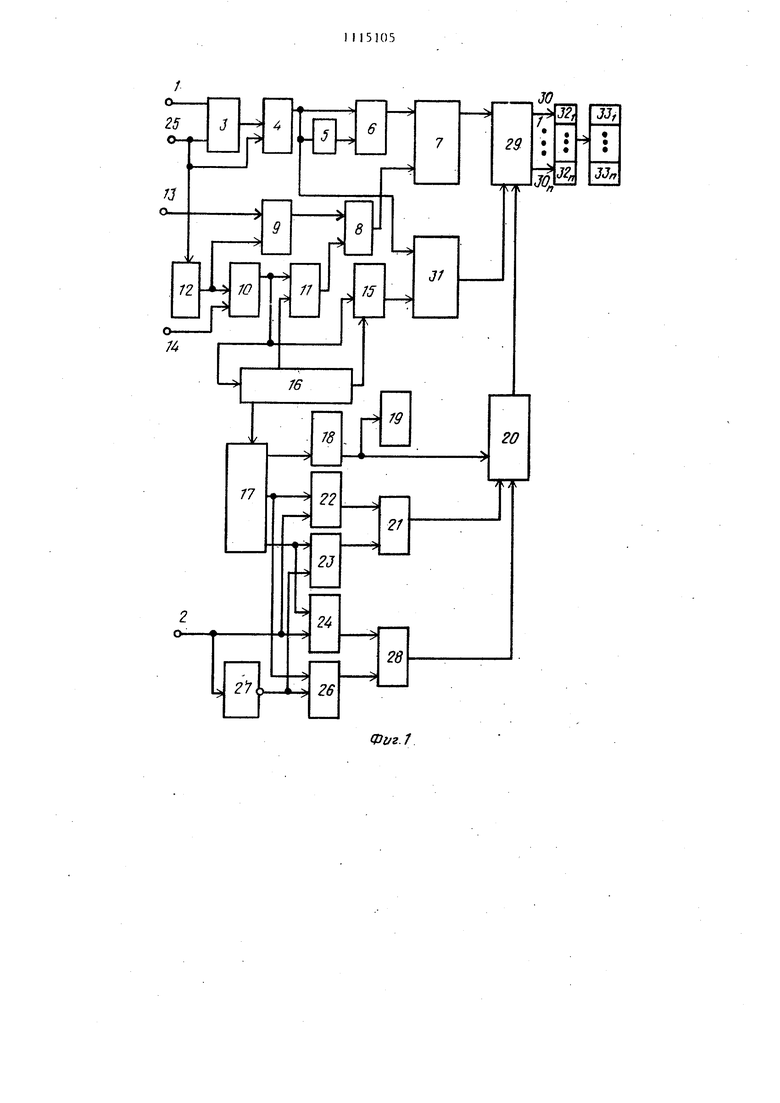

На фиг.1 приведена функциональная схема устройства; на фиг.2 - функциональная схема наиболее предпочтительного варианта выполнения блока дешифрации и сдвига информации, например для дешифрации двухразрядного кода адреса.

Устройство содержит (фиг.1) адресные 1 и числовой 2 входы, счетчик 3 адресов, блок 4 дешифрации и сдвига информации, элементы 5 задержки, триггеры 6, формирователи 7 токов считьшания, первый элемент ИЛИ 8, элементы И 9-11 с первого по третий, генератор 12 импульсов. На фиг.1 обозначены первьй 13 и второй 14 управляющие входы устройства.

Устройство содержит также четвертый элемент И 15, счетчик 16 тактов, депифратор 17, ключ 18, накопительный элемент 19, формирователи 20 разрядных токов записи, второй элемент ИЛИ 21, элементы И 22-24 с пятого по седьмой. На фиг.1 обозначен третий управляющий вход 25 устройства. Устройство содержит также восьмо элемент И 26, первый элемент НЕ 27, третий элемент ИЛИ 28, накопитель 2 с выходами 30, формирователи 31 адресных токов записи, усилители 32,. считывания и регистры 33., числа. Блок дешифрации и сдвига информа ции (фиг.2) содержит второй элемент НЕ 34, элементы И 35-42 с девя того по шестнадцатый и элементы ИЛИ 43-46 с четвертого по восьмо Устройство работает следующим об разом. В режиме записи информации на управляющем входе 14 (фиг.1) имеется разрешающий потенциал, и синхроимпульс с генератора 12 поступает через элемент И 10 на вход счетчика 16 и на элементы И 11 и 15, вторые входы которых управляются счетчиком 16 таким образом, что в течение определе ноге времени синхроимпульс поочередно проходит через один из элементов И 11 и 15, а следовательно, поочередно срабатывают формировател 20 или формирователи 7. Одновременно с этим дешифратор 17, управляемый счетчиком 16, вьщает на первом выходе сигнал включения ключа 18j который подает питание на формирователи 20 и заряжает накопительный элемент 19, кроме того, дешифратор 17, в зависимости от кодовой комбинации на входе, вьщает на своем втором выходе сигнал опроса на элементы И 22 и 26. Код числа, присутствующий на входе 2 -или его инве сия на выходе элемента НЕ 27, разрешает прохождение сигнала опроса через элементы И 22 к 26, ас третьего выхода дешифратора 17 опро вьцt leтcя на элементы И. 23 и 24, которые управляются кодом числа с вхо да 2. Вьщеленный сигнал опроса пост пает на второй или третий входы фор мирователей 20, обеспечивая формирование соответствующей полярности разрядного тока накопителя 29, по разрядным шинам которого протекают токи, обеспечивающие запись информации по выбранному адресу. Отличительной особенностью выбо ра адреса в предлагаемом устройств является то, что каждый очередной адрес (естественный порядок изменения) записываемых слов выбирается не в соседнем регистре матрицы накопителя 29, в которой произведена запись предьщущего слова, а в регистре, которьй находится в соседней матрице накопителя 29. Необходимое для. этого время отсчитывается счетчиком 16, который при достижении определенной кодовой комбинации запрещает прохождение синхроимпульсов через элемент И 11 и 15, запрещая срабатывание формирователей 7 и 31. Одновременно дешифратор 17 снимает сигнал включения ключа 18, вьдает сигнал опроса на своем третьем выходе и снимает сигнал опроса с второго выхода. В этом случае сигнал опро.са, поступающий на третий вход формирователей 20, обеспечивает противоположность в полярности разрядного тока. Смена в вьщаче сигналов опроса с второго и третьего выходов дешифратора 17 будет происходить до достижения заданного количества разнополярных импульсов, в зависимости от типа запоминающего элемента накопителя 29. Так как при прохождении этой пачки разрядных токовых импульсов ключ 18 отключен, их амплитуда в пачке определяется потенциалом накопленной энергии в элементе 19, который снижается до нуля по мере расхода энергии при прохождении этих токов. В режиме считывания информации код адреса .считьгоаемого слова поступает с входов 1 на счетчик 3, где фиксируется, с выхода счетчика 3 код адреса поступает на блок 4,где Дешифрируется. С выхода блока 4 унитарный код поступает на один из входов триггера 6 и через элементы задержки 5 на другие их входы. В результате выбран один из триггеров 6, которьй перейдет в состояние хранения единицы. С выхода выбранного триггера 6 единичный сигнал поступает на соответствующий формирователь 7, куда при наличии разрешающего потенциала на входе 11 будет передан синхроимпульс с генератора 12 через элементы И 9 и ИЛИ 8. Под действием указанных сигналов с выхода формирователя 7 по избранной координате накопителя 29 протекает ток считывания и через интервал времени t, равньй сумме задержек в счетчике 3, 71 блоке 4, триггерах 6, формирователе 7 и накопителе 29, на соответствующем выходе появляется код считанного слова, который через соответствующий ycилиteль передается в соответствующий регистр . В итоге цикл считывания слова начинается с момента подачи адреса считываемого слова и заканчивается с появлением данного слова в регистре 33,-33. В предлагаемом устройстве выходной сигнал блока 4 фиксируется триггером 6, вместе с тем он же и является сигналом возбуждения формирователя 7, вследствие чего адрес слова может быть свободно изменен в счетчике 3 за счет подачи туда импульса с входа 25, период следования которого будет зависеть лишь от времени задержки . при прохождении сигнала через блок 4 и триггер 6 и составит t, Получённьй новый адрес одновременно фиксируется в счетчике 3, а вновь возбужденньй выход блока 4 обеспечивает перевод в единичное состояние очередной триггер 6, который возбудит очередной формирователь 7 в то время когда по предьадущему адресу считьгоани еще не закончено. Такая возможность появляется потому, что очередное считываемое слово находится на соседней матрице в регистре накопителя 29, расположенном вне зоны действия предьдущего сигнала. Элемент 5 задержки обеспечивает обнуление выбираемых триггзров 6 через суммарное время t задержки в триггере 6, формирователе 7, нако58пителе 29, усилителе 32 и регистре 33. Тривиально, что естественный порядок изменения адресов присущ линейным участкам программ. Однако устройство работоспособно и в случае поступления в счетчик 3 нового адреса с входов 1. В этом случае интервал времени, через который возбудится очередной формирователь 7, будет равен сумме времен задержек в счетчике 3, блоке 4 и триггере 6. При этом необходима корректировка частоты генератора 12, которая обеспечивается сигналом с вхола 25.При поступлении полного адреса в счетчик 3 такая корректировка не производится, Таким образом, при цикле считывания каждого слова равном tj появляется возможность параллельно совмещенной выборки слов из различных матриц накопителя 29. При этом начало выборки каждого последующего слова будет запаздывать от начала выборки предыдущего на интервал времени t-L или t, . Таким образом, в предлагаемом устройстве присутствует ускоренная выборка кванта информации, так как за отрезок времени будет опрошено большее число регистров накопителя 29, следовательно, быстродействие запоминающего устройства при считывании информации будет увеличено. Технико-экономическое преимущество предлагаемого устройства заключается в его более высоком, по сравнению с прототипом, быстродействии при считьтании информации.

Фиг.1

fi 5.6,31

| Г | |||

| Запоминающее устройство | 1977 |

|

SU631990A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Запоминающее устройство типа 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах | 1979 |

|

SU773731A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-09-23—Публикация

1983-04-21—Подача