ijn.-.zi:j

(Риг.1

ИзоСфетение относится к электросвязи и может быть использовано в системах связи для передачи дискретных сообщений, в частности, в системах передачи тц1фровой и телеметрической информации, в телеграфии и в системах с импульсно-кодовой модуляцией.

По основному авт.св. № 951739 известно устройство тактовой синхронизаи1ии с дискретным управлением, содержащее последователыю соединенные фазовый детектор и цифровой интегратор, первый и второй входы которого подключены к соответствующим входам усредняющего блока, а третий вход - к выходу подстраиваемого генератора, а также формирователь импульсов, выход которого подключен к первому входу фазового детектора, второй вход которого является входом устройства, последовательно соединенные первый элемент совпадения, инвертор, второй элемент совпадения и ключ, выход которого подключен к входу подстраиваемого генератора, первый вход первого элемента совпадения подсоединен к выходу цифрового интегратора, второй вход - к первому выходу усредняющего блока, второй выход которого подсоединен к другому входу второго элемента совпадения, выход подстраиваемого генератора подключен к входу формирователя импульсов, другие выходы которого под{ :л очены соответственно к третьему входу фазового детектора и к третьему входу усредняющего блока, а цифровой интегратор содержит реверсивный счетчик и суммирую1ций счетчик, выходы которых подключены к входам формирователя импул-ьсов, причем входы реверсивного и суммирующего счетчиков и выход формирователя импульсов являются соответственно входами и выходом цифрового интегратора lj .

Недостатками известного устройства тактовой синхронизации с дискретным управлением являются большое время установления синхронизма и недостаточно пирокая область рабочих частот.

Цель изобретения - сокращение вре мани установления синхронизма и расширение области рабочих частот.

Поставленная цель достигается тем что в устройстве тактовой синхронизации с дискретным упр.тлением, содержащим последовательно сш динениые фазоиый детектор и цифровой интегратор первый и второй входы которого подключены к соответствующим входам усреняю1Ц|;го блока, а третий вход - к выходу подстраиваемого генератора, а также формирователь импульсов, выход которого подключен к перрзому входу фазового детектора, второй вход которого является входом устройства, последовательно соединенные дервый элемент совпадения, инвертор, второй элемент совпадения и ключ, выход которого подключен к входу подстраиваемого генератора, первый вход первог элемента совпадения подсоединен к выходу цифрового интегратора, второй вход - к первому выходу усредняющего блока, второй выход которого подсоединен к другому входу второго элемента совпадения, выход подстраиваемого генератора подключен к входу формирователя импульсов, другие выходы которого подключены соответственно к третьему входу фазового детектора и к третьему входу усредняющего блока, цифровой интегратор выполнен в виде двух цепей, каждая из которых состоит из последовательно соединенных элемента ИЛИ и суммирующего счетчика, причем тактовые входы элементов ИЛИ объединены, а вькоды суммирующих счетчиков подключены к входам полусумматора, выход которого является выходом цифрового интегратора/ а входы элементов ИЛИ входами цифрового интегратора.

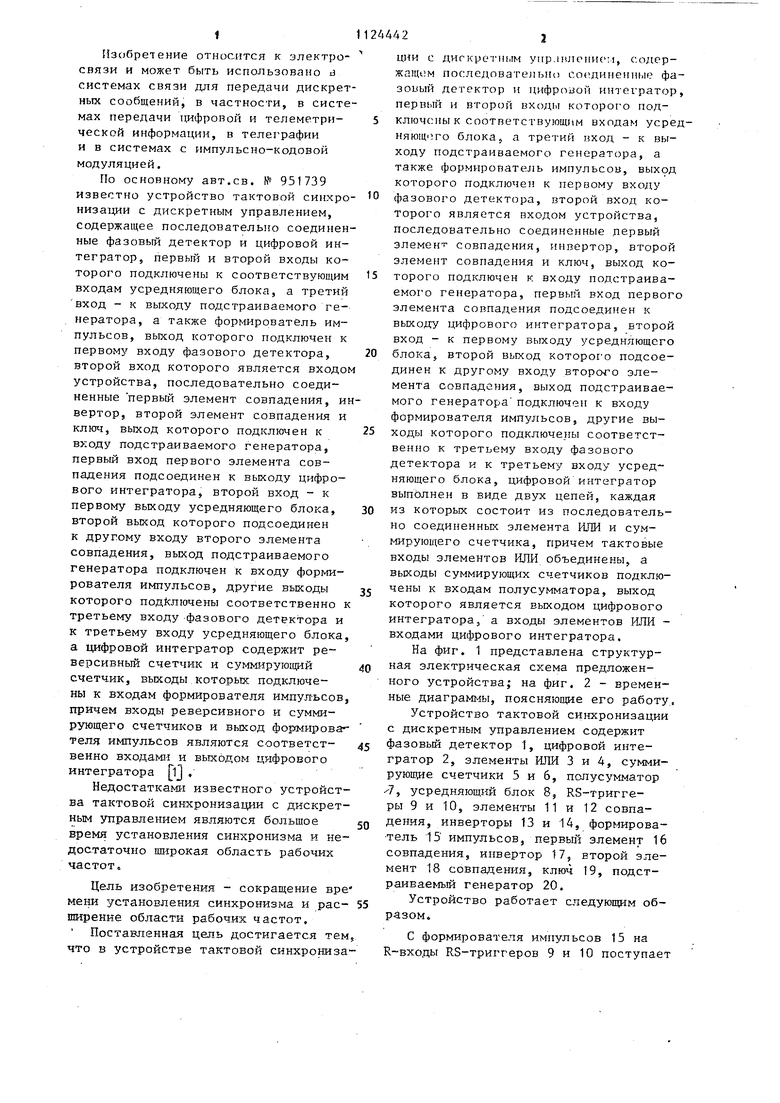

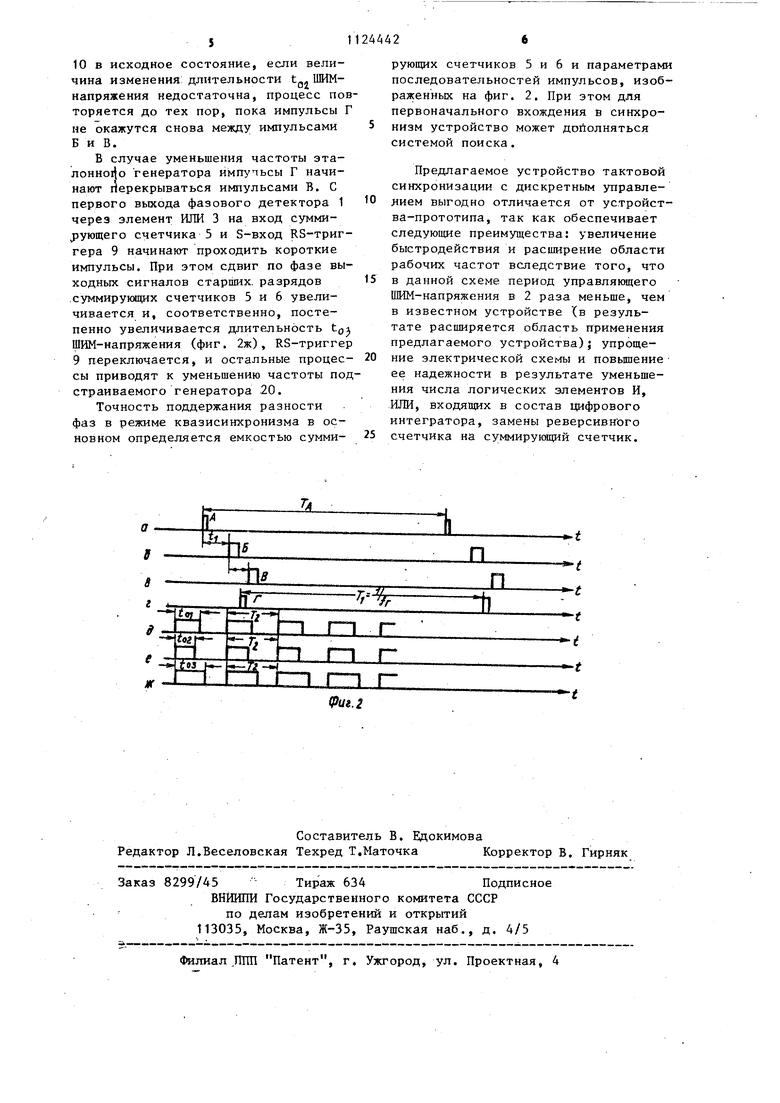

На фиг. 1 представлена структурная электрическая схема предложенного устройства; на фиг. 2 - временные диаграммы, поясняющие его работу

Устройство тактовой синхронизации с дискретным управлением содержит фазовый детектор 1, цифровой интегратор 2, элементы ШШ 3 и 4, суммирующие счетчики 5 и б, полусумматор -7, усредняющий блок 8, RS-триггеры 9 и 10, элементы 11 и 12 совпадения, инверторы 13 и 14, формирователь 15 импульсов, первый элемент 16 совпадения, инвертор 17, второй элемент 18 совпадения, ключ 19, подстраиваемый генератор 20.

Устройство работает следующим обр-азом.

С формирователя импульсов 15 на R-входы RS-триггеров 9 и 10 поступает последовательность импульсов А с пе/риодом . 2а), а на первые два Bxoj.;a фзового детектора 1 с отставанием на премя t подают сдвинутые от носительно друг друга на время tj по следовательности импульсов Б и В тож с периодом Тд (фиг. 26,в). На третий вход фазового детектора 1 поступает последовате,11ьность коротких импульсов Г с частотой f I ,кратной частоте эталонного генератора (фиг. 2г). В случае совпадения частот эталон ного и подстраиваемого генератора (. f ) импульсы Г располагаются между импульсами Б и В. При- этом на обоих выходах фазового детектора 1 и на прямых выходах КЗ-тригг гров 9 и 10 устанавливается логический ноль, а на выходах инверторов 13 и 14 логическая единица.В результате через первый элемент совпадения 16, инвертор 17 и второй элемент 18 совпадения в цепь управления ключа 19 с выхода пoлycy мaтopa 7 цифрового интегратора 2 поступает последовательность прямоугольных импульсов. Для их формирования выходной сигнал подстраиваемого генератора 20 подается на суммирующие счетчики 5 и 6 с одинаковым числом разрядов соответствен но через элементы ИЛИ 3 и 4. Далее выходные сигналы старших разрядов суммирующих счетчиков 5 и 6 поступают на пол у сумматор 7 , за кон фунышонирования которого описывается логическим уравнением -ь Q . Q F Q. где и. - соответственно пря- мые и инверсные выходы старшего разряда суммирующих счетчиков 5 и 6. В результате на выходе полусумматора 7 образуется прямоугольное щи- ротно-импульсно-модулированное (ШИМ) напряжение, период Т которого определяется емкостью суммирующих счетчиков 5 и 6 и частотой подстраиваемого генератора 20 и оказьшается в 2 раза меньщим периода выходного напряжения старших разрядов суммирующих счетчиков 5 и 6. Соответственно, при одинаковой емкости счетчиков щ1фрового интегратора прототипа и предлагаемого устройства, т.е. при одинаковой точности поддержания разся, что приводит к быстрому увеличению частоты подстраиваемого генератора 20, После сброса RS-триггера ности фаз, предлагаемое устройство имеет период управляющего ШШнапряжения Т -j Т. , а следовательно, в 2 раза большее быстродействие и соответственно большую область рабочих частот. Поступая в цепь управления ключа 19, ИНМ-напряжение управляет временем подключения к времязадающей цепи подстраиваемого генератора 20. Поэтому в тот момент времени, когда ключ 19 открыт, его частота уменьшается до значения fj , и увеличивается до значения f, когда ключ 19 закрыт.При этом средняя частота . подстраиваемого генератора 20 определяется выражением Cf f ) Uj t,; „, где Tj - время, равное периоду ШИМнапряжения;t - время внутри периода ШИМ-напряжения, когда последнее равно логической единице и ключ 19 открыт. При выборе частот 5,- гг || + сдвиг по фазе выходных сигналов старших разрядов суммирующих счетчиков 5 и 6 устанавливается равным Т/2, а длительность tg. 1/2 Tj (фиг. 2д) и в процессе работы определяется текущей разностью частот эталонного и подстраива- емого генератора 20, В случае увеличения частоты эталонного генератора импульсы Г начинают перекрываться с импульсами Б. При этом со второпо выхода фазового детектора 1 через элемент ИЛИ 4 на суммирующий счетчик 6 и S-вход RS-триггера 10 начинают проходит короткие импульсы. После . чего сдвиг по фазе выходных сигналов старших разрядов суммирующих счетчиков 5 и 6 уменьшается и, соответственно, постепенно уменьшается длительность t.ШИМ-напряжения (фиг. 2е), т.е. цифровой интегратор 2 постепенно отрабатьгоает изменение частоты эталонного генератора. В то же время RS-триггер 10 переключается, в результате на-втором входе элемента 18 совпадения устанавливается логический ноль и ключ 19 закрывает10 в исходное состояние, если величина изменения длительности t ШИМнапряжёния недостаточна, процесс повторяется до тех пор, пока импульсы Г не Ькажутся снова между импульсами Б и В. В случае уменьшения частоты эталоннойо генератора импупьсы Г начинают Нерекрываться импульсами В. С первого выхода фазового детектора 1 через элемент ИЛИ 3 на вход суммидзующего счетчика 5 и S-вход RS-триггера 9 начинают проходить короткие импульсы. При этом сдвиг по фазе выходных сигналов старших, разрядов .суммируюпщх счетчиков 5 и 6 увеличивается и, соответственно, постепенно увеличивается длительность ШИМ-напряжения (фиг. 2ж), RS-триггер 9 переключается, и остальные процессы приводят к уменьшению частоты под страиваемого генератора 20. Точность поддержания разности фаз в режиме квазисинхронизма в основном определяется емкостью суммирующих счетчиков 5 и 6 и параметрами последовательностей импульсов, изображенных на фиг. 2. При этом для первоначального вхождения в синхронизм устройство может дойолняться системой поиска. Предлагаемое устройство тактовой синхронизации с дискретным управлелием выгодно отличается от устройства-прототипа, так как обеспечивает следующие преимущества: увеличение быстродействия и расширение области рабочих частот вследствие того, что в данной схеме период управляющего ШИМ-напряжения в 2 раза меньше, чем в известном устройстве в результате расширяется область применения предлагаемого устройства); упрощение электрической схемы и повьшение ее надежности в результате уменьшения числа логических элементов И, ИЛИ, входящих в состав цифрового интегратора, замены реверсивного счетчика на суммирующий счетчик.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации с дискретным управлением | 1979 |

|

SU951739A1 |

| ЦИФРОВОЙ ИНТЕГРИРУЮЩИЙ ВОЛЬТАМПЕРМЕТР | 1972 |

|

SU347909A1 |

| Способ определения частотной характеристики испытуемого объекта и устройство для его осуществления | 1984 |

|

SU1223074A1 |

| Устройство для приема частотно-манипулированных сигналов | 1978 |

|

SU768000A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| Устройство для автоматической однократной подстройки частоты | 1980 |

|

SU965002A1 |

| СПОСОБ ТЕЛЕВИЗИОННОГО ВЕЩАНИЯ С ЗАЩИТОЙ ОТ НЕСАНКЦИОНИРОВАННОГО ПРИЕМА И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2013024C1 |

| Устройство для частотно-фазовой автоподстройки | 1986 |

|

SU1405107A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU919124A1 |

| Способ формирования периодических двуполярных колебаний с заданным фазовым сдвигом и устройство для его реализации | 2016 |

|

RU2625047C1 |

УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ С ДИСКРЕТНЫМ УПРАВЛЕНИЕМ по авт.св. № 951739, отличающееся тем, что, с целью сокра- щения времени установления синхронизма и расширения области рабочих частот, цифррвой интегратор вьиол- нен в виде двух цепей, каждая из которых состоит из последовательно соединенных элемента ИЛИ и суммирующего счетчика, причем тактовые входы элемента ИДИ объединены, а выходы суммирующих счетчиков подключены к входам полусумматора, выход которого является выходом цифрового, интегратора, а входы элементов ИЛИ - входами цифрового интегратора. 1

IA

8

п

п

1

S

гп г

S3

гп

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-11-15—Публикация

1983-04-01—Подача