(54) УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ С ДИСКРЕТНЫМ УПРАВЛЕНИЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации с дискретным управлением | 1983 |

|

SU1124442A2 |

| Устройство для автоматической однократной подстройки частоты | 1980 |

|

SU965002A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| Способ определения частотной характеристики испытуемого объекта и устройство для его осуществления | 1984 |

|

SU1223074A1 |

| Устройство синхронизации | 1987 |

|

SU1499494A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU919124A1 |

| Формирователь линейно-частотно-модулированных колебаний | 1980 |

|

SU938359A1 |

| Устройство цифровой фазовой автоподстройки частоты | 1982 |

|

SU1125748A1 |

| Устройство цикловой синхронизации последовательного модема | 1986 |

|

SU1450123A1 |

| ОБНАРУЖИТЕЛЬ ПЕРЕОТРАЖЕННЫХ СИГНАЛОВ | 1999 |

|

RU2191400C2 |

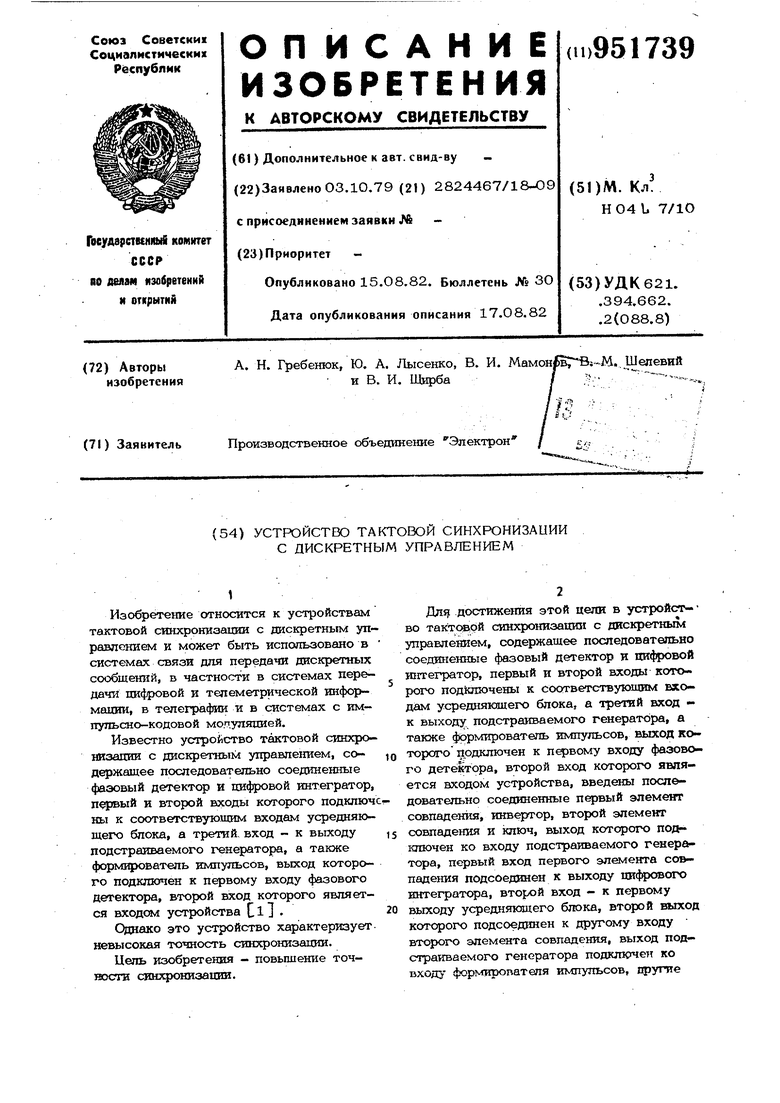

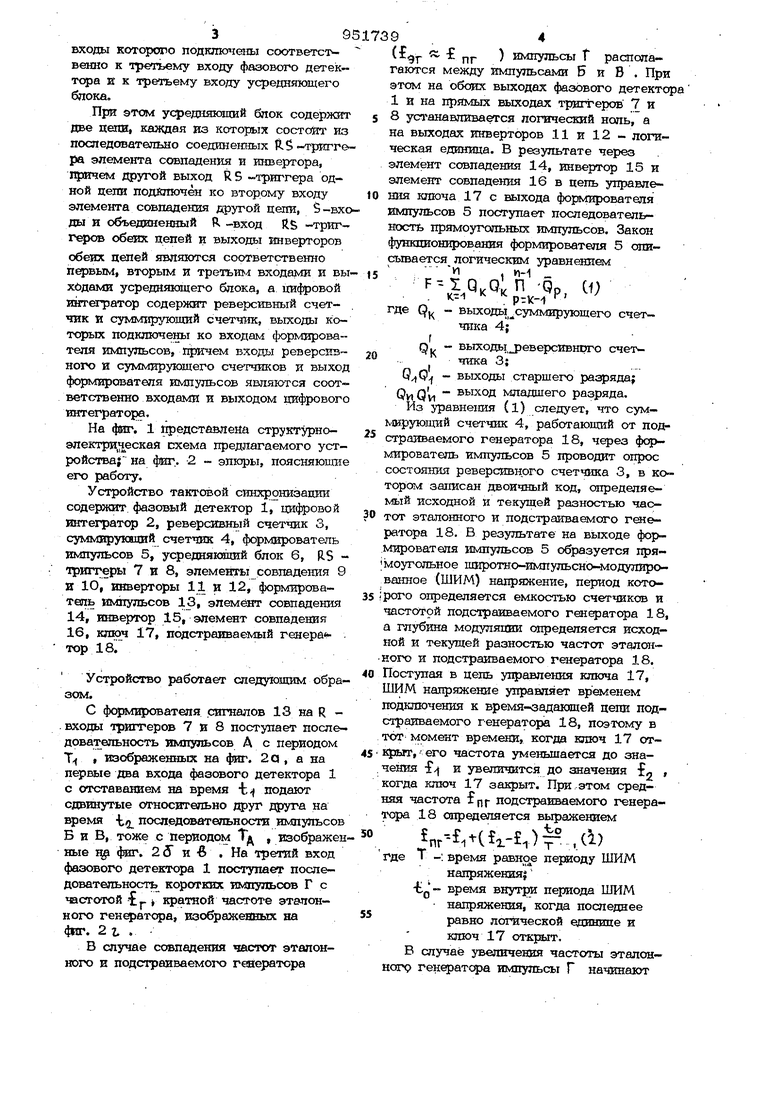

Изобретение относится к устройствам тактовой синхронизации с дискретньпу уп равпением и может быть использовано в системах связи для передачи дискретных сообщений, в частности в системах передачи дифровой и телеметрической информашга, в телеграфии и в системах с импутшсНо-кодовой модуляцией. Известно устройство тактовой синхронизации с дискретным управлением, содержащее последовательно соединенные фазовый детектор и цифровой интегратор, первый и второй входы которого подключ ны к соответствующим входам усредняющего блока, а третий, вход - к выходу подстраиваемого генератора, а также формирователь импульсов, выход которого подключен к первому входу фазового детектора, второй вход которого является входом устройства С11 Однако это устройство характеризует невысокая точность синхронизации. Цель изобретения - повышение точности синхронизашш. Для достиже шя этой цели в устройст- во тактойрй синхронизации с дискретным управлением, содержащее последовательно соединенные фазовый детектор и Го14чх)вой интегратор, первый и второй входы которого под1а1ючены к соответствующим входам усредняющего блока, а третий вход к выход; подстраиваемого генератора, а также формирователь импульсов, выход которого з одключен к первому входу фазового детектора, второй вход которого является входом устройства, введены последовательно соединенные первый элемент совпадения, инвертор, второй элемент совпадения и ключ, выход которого подключен ко входу подстраиваемого генера тора, первый вход первого элемента совпадения подсоединен к выходу цифрового интегратора, второй вход - к первому выходу усредняющего блока, второй выход которого подсоединен к другому входу второго элемента совпадения, выход подстраиваемого генератора под|упочетт ко входу формиропатепя импульсов, пругие 39 входы которого подключены соответст вешю к третьему входу фазового детектора и к третьему входу усредняющего блока. При этом усред11яющий блок содержит две целя, из которых состо)ят из последовательно соединенных Р.5--тригге ра элемента совпадения и инвертора, причем другой выход R5 -триггера одной цепи подключён ко второму входу элемента совпадения другой дели, S-вхо ды и объеданенный R -вход RS тркгг юв обеих депей и выходы инверторов обеих депей являются соответственно первым, вторым и третьш входами и вы ходами усредняющего блока, а цифровой интегратор содержит реверсивный счетчик И суммирующий счетчик, выходы которых подключены ко входам формирователя импульсов, причем входы реверсивного и суммирующего счетчиков и выход формирователя импульсов являю тся соответственно входами и выходом цифрового интегратора. На фиг. 1 представлена структурноэлектри,еская схема предлагаемого устройства; на фиг.. 2 эшоры, поясняющие его работу. Устройство тактовой синхронизации содержзят. фазовый детектор 1, цифровой интегратор 2, реверсивньтй счетчик 3, суммирующий счетчик 4, формирователь импульсов 5, усредйякшшй блок 6, dS триггеры 7 и 8, элемеИты совпадения 9 и 10, инверторы 11 и 12, формирователь импульсов 13, элемент совпадения 14, инвертор 15, элемент совпадения 16, ключ 17, подстраиваемый генералтор 18. Устройство работает следующим обра зом. С формирователя сигналов 13 на R входы триггеров 7 и 8 поступает последовательность импульсов А с периодом Т. , изображенных на фиг. 2а , а на первые два входа фазового детектора 1 с отставанием на время t-f подают сдвинутые относительно друг друга на время последовательноств импульсов Б и В, тоже с периодом Тд , изображен иые 1 фиг 2 б и в . На третий вход фазового детектора 1 поступает последовательность коротких импульсов Г с частотой fp кратной частоте эталонного генератсфа, изображеаных на 4иг. 2 1, . В случае совпадения частот эталонного и подстраиваемого гшератора 9 (fg Р ) Юvшyльcы t располагаются между импульсами 0 и В . При этом на обоих выходах фазового детектора 1 и на прямых выходах триггеров 7 и 8 устанавливается логический ноль, а на выходах инверторов 11 и 12 - логическая единица. В результате через элемент совпадения 14, инвертор 15 и элемент совпадения 16 в цепь управлеВИЯ ключа 17 с иыхода формирователя импульсов 5 поступает последовательность прямоугольных импульсов. Закон функционирования формирователя 5 описьгоается логическим уравнением . и-1 F--IQ Q;n Qp СО - К- ргК-1 где рц - выходь1 суммирующего счетчика 4; Q. - выxoдьI,J)eвepcивнpгo счет чика 3; - выходы старщего разряда; QnQvi Ь1ход младщего разряда. Из уравнения (l) следует, что суммирующий счетчик 4, работающий от подстраиваемого генератора 18, формирователь импульсов 5 проводит опрос состоягаия реверсивного счетчика 3, в котором записан двоичный код, определяемый исходной и текущей разностью частот эталонного и подстраиваемого генератора 18, В результате на выходе формирователя импутхьсов 5 образуется прямоугольное широтно-импульсно- додулированное (ШИМ) напряжение, период которого определяется емкостью счетчиков и частотой подстраиваемого генератора 18, а глубина модуляции определяется исходной и текущей разностью частот этало11 ного и подстразгоаемого генератора 18. Поступая в цепь управле1шя ключа 17, ШИМ напряжение управляет временем подключения к время-задаклцей цепи подстраиваемого генератора 18, поэтому в ТОТ момент времени, когда ключ 17 отЧрьгг, его частота уменыиается до значения -f и увеличится до значения fg , когда ключ 17 закрыт. При этом средняя частота f пг подстраиваемого генератора 18 определяется выражением i Т -; время равное периоду ШИМ напряжения -- время внутри периода ШИМ напряжения, когда последнее равно логической единице и ключ 17 открыт, В случае увеличения частоты эталон- НСХГ9 генератора импульсы Г начинают лерекрьгааться с импульсами Б . При этом через второй выход фазового детектора 1 на вычитающий вход реверсивного с«1етчика 3 и 5 -вход триггера 8 начинают прюходить короткие импульсы. После чего двоичный код, записанный в реверсивном счетчике 3, уменьшается и соответственно постепенно уменьшается время -to ШИМ напряжения, т.е. шяфровой Интегратор 2 постеттенно отрабатывает изменение частоты эталонного генератор В то же время триггер 8 переключается в результате на втором входе схемы сов падения 16 устанавлзявается логический ноль и ключ 17 закрьгоается, что приводит к быстрому увеличению частоты подстраиваемого генератора 18. После сбро са триггера 8 в исходное состояние, есл величина изменения глубины модуляции ШИМ напряжения недостаточна, процесс Повторяется до тех пор, пока импульсы не окажутся снова между импульсами Б и В . В случае уменьшения частоты эталонного генератора импульсы Т начинают перекрываться с импульсами В Теперь уже через первый выход фазового детектора 1 на суммирующий вход реверсивного л;четчика 3 и 6 -вход триггера 7 начинают проходить короткие импульсы. При этом двоичный код, записанный в реверсивный счетчик 3, увеличявается, триггер 7 переключается и остальные процессы приводят к уменьшению частоты подстраиваемого генератора 18. Точность поддержания разности фаз в режиме квазйстасчхмгазма в основном определяется емкостью реверсивного 3 и суммирующего 4 счетчиков и параметрами последовательностей импульсов, изображенных на фиг. 2. Для первоначаль ного вхо)кдения в синхронизм устройство может дополняться системой пояска. Предлагаемое ухлройство позволяет повысить частотный диапазон тактоьой сшсфонизацни известного устройства и увелишть точность сннхронизахши.

Формула изобретения .

1, Устройство тактовой синхронизации с дискретным управлением, содержащее последовательно соединенные фазовый детектор и интегратор, первый 9

Источники информации, принятые во внимание при экспертизе 1. Шахпшьдян В. В. и др. Системы фазовой автоподстройки частоты с элементами дискрстизашп. М., Связь, 1979, с, 152, рис. 4.2П (прототип). 96 и второй входы котсрого подключены к соответствующим -входам усредняющего блока, а третий вход - к выходу подстраиваемого генератора, а также формирователь импульсов., выход которого подключен к первому входу фазового детектора, второй вход которого является входом устройства, отличающееся тем, что, с целью повышения точности синхронизации, введены последовательно соединеншде первый элемент совпадения, инвертор, второй элемент совпадения и ключ, выход которого подключен к входу подстраиваемого генератора, первый вход первого элемента совпадения подсоединен к выходу цифрового интегратора, второй вход - к первому выходу усредняющего блока, второй выход которого подсоединен к другому входу второго элемента совпадения, выход подстраиваемого генератора подключен к входу формирователя импульсов, другие входа.1 которого подключены соответственно к третьему входу фазового детектора и к третьему входу усредняющего блока. 2.Устройство по п. 1, о т л и ч а 1ю щ е е с я тем, что усредняклдий блок содержит две цепи, каждая из которых состоит из последовательно соединенных RS -триггера, элемента совпадения и иьтертора, причем другой выход й.5-тркгг а одной цепи подключен к второму входу элемента совпадения другой цепл, S -входы и объединенный R, -вход RS триггеров обеих цепей и .выходы инверторов обеих цепей явл$потся соответственно первым, вторым и третьим входами и выходами усредняющего блока. 3.Устройство по п. 1, отличающееся тем, что цифровой ин егра- тор содержит реверсивный счетчик и суммирующий счетчик, вьтходы которых подключены к входам формирователя импульсов, причем входы реверсивного и суммирующего счетчиков и выход формирователя импульсов являются соответственно входами и выходом цифрового интегратора.

fur2

Авторы

Даты

1982-08-15—Публикация

1979-10-03—Подача