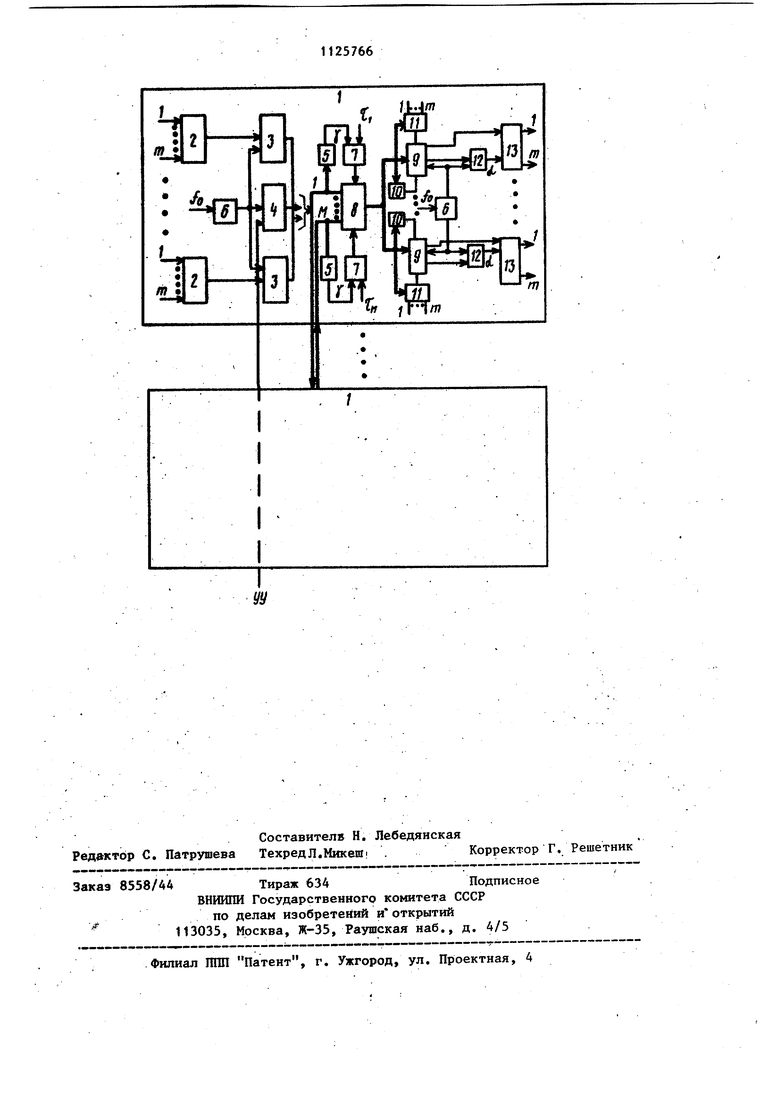

Изобретение относится к технике связи и может использоваться в системах цифровой коммутации. Известна коммутационная система, содержащая входные и выходные преобразователи кода, последовательно соединенные блок управления, блок памяти и блок коммутации, а также считьюакщее устройство и распредели тель, причем первый и второй выходы блока коммутации соединены с входами считывающего устройства,и распре делителя соответственно, выходы входных преобразователей кода соединены с соответствующими входами считывающего устройства, а входы выходных преобразователей кода соед нены с соответствующими выходами распределителя ij Недостатками данной системы являются низкая пропускная способност и низкая помехозащищенность группового тракта. Наиболее близкой к изобретениюявляется многомодульная коммутационная система для асинхронных цифровых сигналов, состоящая из М мо.дулей, каждый из которых содержит 8 входных преобразователей кода, блоки фиксации времени, причем выход каждого входного прербразователя кода соединен с первым входом |соответствующего блока фиксации времени, формирователь кода времени блок памяти адресов, блок первичной памяти, причем выход формирователя кода времени соединен с вторыми входами блоков фиксации времени и с первым входом блока памяти адресов, выходы локов фиксации времени соединены между собой, второй вход блока памяти адреса каждог из М модулей является управляющим входом коммутационной систеквд, а также содержит блоки блокировки записи, блоки вторичной памяти, бло ки сравнения кодов времени и В . выходных преобразователей кода, при чем первый вход блока вторичной памяти соединен с выходом соответству ющего блока блокировки записи, а вторые входы блоков блокировки записи и блоков вторичной памяти соединены с выходом блока первичной памяти, первый выход каждого блока вторичной памяти соединен с первьш входом соответствующего выходного преобразователя кода через блок сра нения кодов времени, второй вход которого соединен с выходом формирователя кода времени и третьим входом блока вторичной памяти, второй выход каждого блока вторичной памяти соединен с вторым входом соответст.вующего выходного преобразователя кода 2J .. Недостатком известной системы является низкая помехозащищенность цепей коммутации системы. Цель изобретения - повьшение помехозащищенности коммутационньк цепей системы. Цель достигается тем, что в многомодульную коммутационную систему для асинхронных цифровых сигналов, состоящую из М модулей, каждый из которых содержит I входных преобразователей кода, блоки фиксации времени, причем выход каждого входного преобразователя кода соединен с входом соответствующего блока фиксации времени, формирователь кода времени, блок памяти адресов, блок первичной памяти, причем выход формирователя кода времени соединен с вторыми входами- блоков фиксации времени и с йервым входом блока памяти адресов, выходы блоков фиксации времени соединены между собой, второй вход блока памяти адресов из М модулей является управляющим входом коммутационной системы, а также содержит блоки блокировки записи, блоки вторичной памяти блоки сравнения кодов времени и выходных преобразователей кода,; причем первый вход блока вторичной памяти соединен с выходом соответствующего блока блокировки записи, а вторые входы блоков блокировки записи и блоков вторичной памяти соединены с выходом блока первичной памяти, первый выход кажДого блока вторичной памяти соединен с первым входом соответствующего выходного преобразователя кода через блок сравнения кодов времени, второй вход которого соединен с выходом формирователя кода времени и третьим входом блока вторичной памяти, второй выход каждого блока вторичной памяти соединен с вторым входом qoответствукицего выходного преобразователя кода, введены в каждьй из М модулей блоки анализа адреса, блоки записи информации и дешифраторы, при этом выход блока памяти адресов и выходы блоков фиксации времени соединены с входами соответствующих блоков анализа адреса и соответству ющими входами блока первичной памяти, выход каждого блока анализа адреса соединен с входом соответствующего блока записи информации, вы ход которого соединен с дополнитель ным входом блока первичной памяти, выход которого соединен с входами дешифраторов, выход каждого дешифратора соединен с четвертым входом блока вторичной памяти. На чертеже представлена структур ная электрическая схема многоуголь- ной коммутационной системы для асинхронных цифровых сигналов. Многоугольная коммутационная сис тема для асинхронных цифровьтх сигналов содержит М модулей 1, содержащих Е входных преобразоватлей 2 кода, блоки 3 фиксации времени, блок 4 памяти .адресов, блоки 5 анализа адреса, формирователь 6 кода времени, блоки 7 записи информации блок 8 первичной памяти, блоки 9 вторичной памяти, дешифраторы 10, блоки 11 блокировки записи, блоки 12 сравнения кодов времени, t выходных преобразователей кода 13. Многомодульная коммутационная система для асинхронных цифровых сигналов работает следующим образо Блок 4 получает из устройства управления коммутациоаной системы номера (адреса) линий связи, которы необходимо скоммутировать между со бой и записывает их в свои ячейки памяти. При этом каждая входящая линия связи модуля коммутационной системы имеет свою ячейку памяти в блоке 4 в которую записьшается адрес коммутируемо с ней исходящей линии связи из числа линий, обслуживаемых коммутационной системой в целом.. Входные преобразователи кода 2 получают коммутируемые сигналы, оп ределяют изменение полярности сигналов и кодируют передний фронт сигналов кодом 1, а задний - О Входные преобразователи кода 2 обслуживают по т линий связи. Код ко мутируемых сигналов (1, О) из входных преобразователей 2 кода выдается далее в сопровождении адресов входящих линий связи, по которым поступили передний или зад ИИ фронт коммутируемых сигналов, блоки 3, в которые поступают также код времени из формирователя 6. локи 3 записывают в свои ячейки амяти код сигнала и код времени. ри этом каждая входящая линия связи модуля 1 имеет свою ячейку памяти в блоках 3. Код времени, записываемый в ячейки 3, фиксирует моменты времени поступления кода сигнала в блоки 3. Формирователь 6 представля- ет собой электронньй счетчик, который вырабатывает код времени и сигналы, синхронизирующие работу всех блоков своего модуля 1. Для того, чтобы формирователи 6 всех М модулей 1 коммутационной системы работали синхронно, на них подается одна и та же последовательность импульсов о от генератора станции. с помощью синхронизирующих сигналов формирователя 6 информация из блоков 3 и 4 циклически считывается и вьщается в соответствующие блоки 5 и блоки 8 всех модулей 1 коммутационной системы. Каждая ячейка памяти блоков 3 и 4 считывается в определенном интервале времени работы группового тракта модуля 1 коммутационной системы. В этом интервале производится такте передача кода сигнала и кода времени из блоков 3 и адреса исходящей линии связи, которой принадлежит эта информация, из блока 4 в блоки 5 и 8 коммутационной систейы. С помощью адреса исходящей линии связи блок 5 контролирует этот адрес по mod 2, а затем, сравнивая его с адресом своего модуля 2, определяет принадлежит ли поступившая информация данному модулю. Если поступивший адрес передан правильно и старшие его разряды соответствуют разрядам адреса модуля 1, то блок 5 вырабатывает сигнал У 1, который поступает в блок 7, разрешая принять поступившую информацию в блок 8. Блок 7 обеспечивает запись поступившего кода сигнала и кода времени в ячейку памяти блрка 8, адрес которой определяется младшим разрядом поступившего из блока 4 адреса исходящей линии связи. При этом каждая исходящая линия связи модуля 1 имеет свою ячейку йамяти в блоке 8. При записи информа.ции в блок 8 она вьщается также вместе с адресом на выход блока 8. Кроме oneрации записи, блоки 7 обеспечивают также и считывание информации из ячеек блока 8. При этом каждый блок 7, вырабатывая сигналы Запись, Считывание и Чтение, обеспечивает запись и считывание информации в своем, интервале времени 2; ( 1,2,..., М). Тактш образом блоки каждый в своем интервале. , обеспе чивают либо запись информации в блок 8 при у 1, либо считывание при у 0. Адрес ячейки памяти, из которой необходимо считывать информацию, определяется счетчиком блока 8. На вход счетчика блока 8 подаются сигналы Чтение из всех блоков -7 модуля 1. После каждого считывания информащш из ячеек блока 8 содержимое его счетчика увеличивается на единицу. При записи информации в блок 8 содержимое его счетчика не изменяется. Код коммутируемого сигнала, код времени из ячеек памяти блока 8 и адрес исходжцей линии связи, кото-г рой принадлежит эта информация, из счетчика блока 8 поступают на входы дешифраторов tO, блоков 9 и блоков 1t. Дешифраторы 10 определяют принадлежит ли поступившая информация своему блоку 9, дешифрируя старшие разряды поступившего адреса. Если адрес: соответствует номеру данного блока 9, то дешифратор -10 выдает сигнал разрешения записи кода коммутируемого сигнала и кода времени в ячейку памяти блока 9 с адресом, определяем младшими разрядами поступившего адреса. Блок 11 сравнивает ко коммутируемого, сигнал а с кодом состояния исходящей линии свя зи, используя при этом поступивший адрес из блока 8. Если эти коды одинаковые, то производится блокиоовка записи поступившей информации 66« в блок 9. А вместо операции записи производится считывание информации. Если же коды отличаются друг от друга, то операция записи не блоки- руется. Запись информации в ячейки памяти блоков 9 производится с одновременной выдачей этой информации, а также адреса ячейки, в которую записьшается информация, на входы выходных преобразователей кода 13. При этом код времени вьщается на входы блоков 12. На другой вход блоков 12 поступает код времени с выхода формирователя 6. В блоках 12 производится сравнение зтих кодов времени. Если коды одинаковые, то вырабатывается сигнал ОС 1, а если различные, то ct 0. Сигнал Л 1 обеспечивает распределение с помощью выходных преобразователей 13 кода кодов коммутируемых сигналов в исходящие линии связи. Блоки 9 вторичной, памяти имеют число ячеек памяти, соответствующее числу исходящих линий связи, которые они обслуживают, т.е. т. Номера ячеек памяти и исходящих линий совпадают. Информация из ячеек блоков 9 считывается циклически с помощью адреса, поступакнцего со счётчика формирователя-6. При записи информации в блок 9 операция считьгоания запрещается. Предложенная коммутационная система для асинхронных цифровых сигналов позволяет практически в М раз повысить помехозащищенность коммутационных цепей, cиcтe я I. Предложенная система позволяет также отказ.аться от резервирования модулей, так как при подключении линий связи исходящих пучков равномерно ко всем модулям выход из строя одного модуля незначительно увеличивает потери на этих пучках.

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутационная система для асинхронных цифровых сигналов | 1978 |

|

SU949839A1 |

| Многомодульная коммутационная система | 1985 |

|

SU1285616A1 |

| Устройство преобразования и коммутации сигналов | 1988 |

|

SU1566505A1 |

| Многомодульная коммутационная система для асинхронных цифровых сигналов | 1986 |

|

SU1394459A1 |

| Устройство для контроля коммутационной системы | 1986 |

|

SU1401639A1 |

| Устройство для пространственновременной коммутации асинхронных цифровых сигналов | 1977 |

|

SU652727A1 |

| Устройство коммутации с эластичной памятью | 1988 |

|

SU1647921A1 |

| Устройство временной коммутации асинхронных цифровых сигналов | 1989 |

|

SU1700762A1 |

| Устройство коммутации асинхронных цифровых сигналов | 1985 |

|

SU1241522A1 |

| Устройство пространсктвенно-временной коммутации | 1978 |

|

SU684772A1 |

МНОГОМОДУЛЬНАЯ КОММУТАЦИОННАЯ СИСТЕМА ДЛЯ АСИНХРОННЬЕХ: ЦИФРОВЬК СИГНАЛОВ, состоящая из М модулей, каждый из которых Содержит с входных преобразователей кода, блоки фиксации времени, причем выход каждого входного преобразователя .кода соединен с первым входом соответствующего блока фиксации времени, формирователь кода времени, блок памяти адресов, блок первичной памяти, причем выход формирователя кода времени соединен с вторыми входами блоков фиксации времени и с первым входом блока памяти адресов, выходы блоков фиксации времени соединены между собой, второй вход блока памяти адресов каждого из М модулей является управляющим входом коммутационной системы, а также содержит блоки блокировки записи, блоки вторичной памяти, блоки сравнения кодов времени и выходных преобразователей кода, причем первый .вход блока вторичной памяти соединен с выходом соответствующего блока блокировки записи, а вторые входы блоков блокировки записи и блоков вторичной памяти соединены с выходом блока первичной памяти, первый выход каждого блока вторичной памяти соединен с первым входом соответствующего выходного преобразователя кода через блок сравнения кодов времени, второй вход которого соединен с выходом формирователя кода времени и третьим входом блока вторичной памяти, второй выход каждого блока вторичной памяти соединен с вторым входом соответствукмдего выходного преобразователя кода, отличающаяся (Л тем, что, с целью повьппения помехозащищенности коммутационных цепей системы, в нее введены в каждый из М . § модулей блоки анализа адреса, блоки записи информации и дешифраторы, при этом выход блока памяти адресов и выходы блоков фиксации времени соединены с входами соответствующих блоков анализа адреса и соответству- S9 (Ющими входами блока первичной памяти, :д выход каждого блок.а анализа адреса соединен с входом соответствующего блока записи информации, выход котоФ а рого соединен с дополнительным входом блока первичной памяти, выход которого соединен с входами дешифраторов, выход каждого дешифратора соединен с четвертым входом блока вторичной памяти.

yy

Авторы

Даты

1984-11-23—Публикация

1982-12-09—Подача