12

Изобретение относится к электросвязи и может быть использовано в системах для цифровой коммутации асинхронные: разноскоростньш сигналов телефонного и телеграфного тина,имеющих скорости передачи до 64 коит/с.

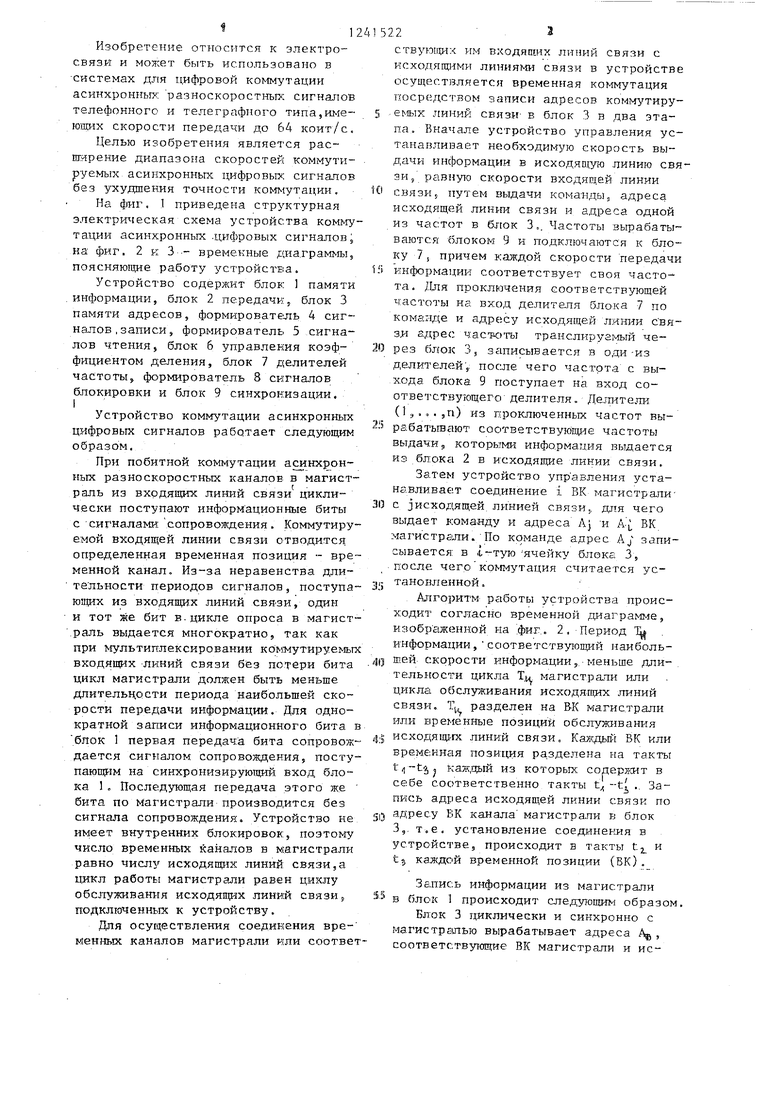

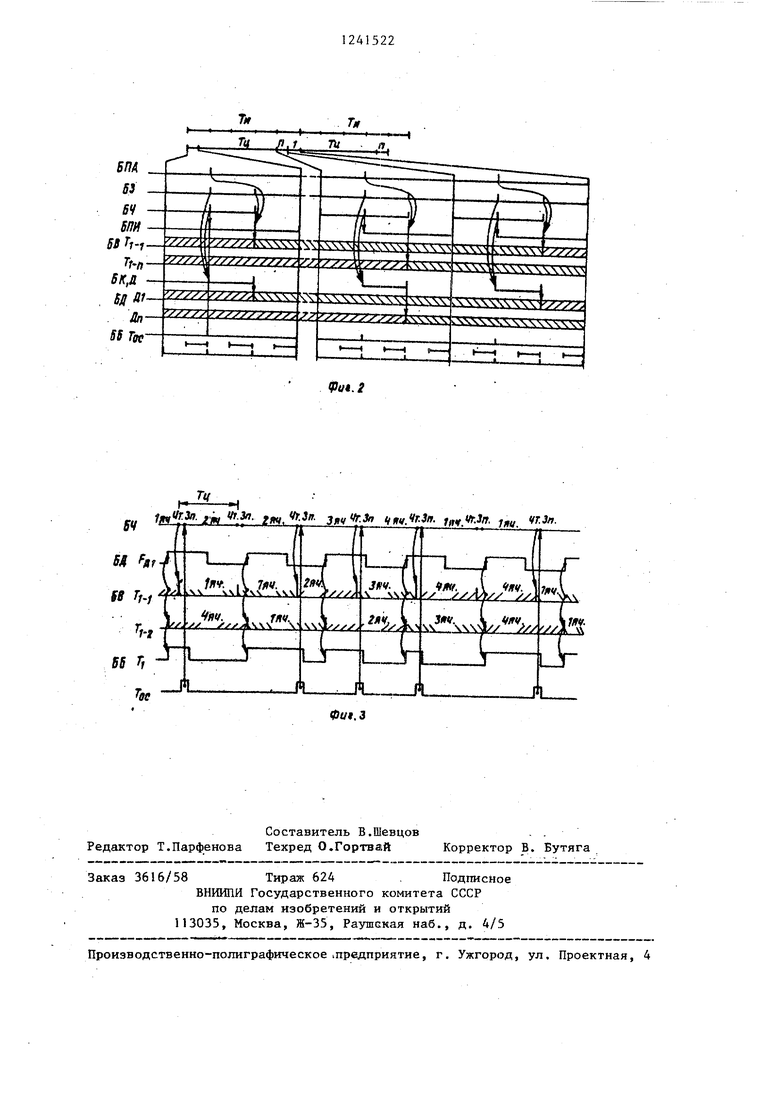

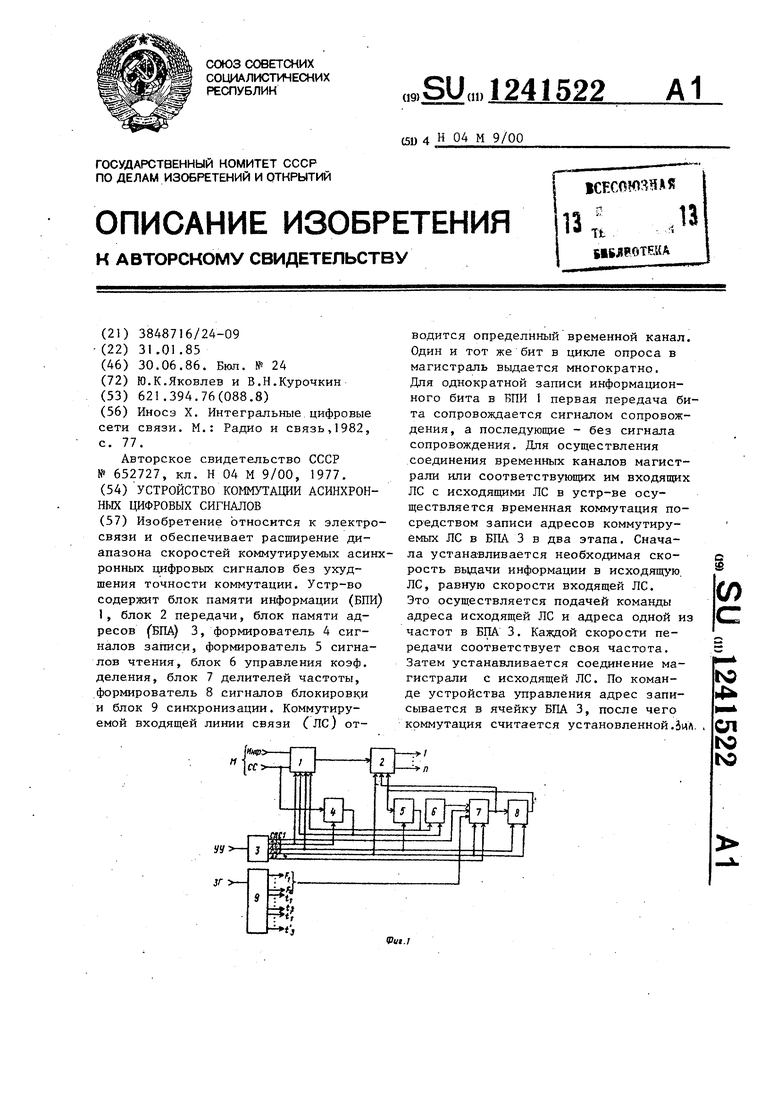

Целью изобретения является рас- тирение диапазона скоростей коммутируемых асинхронных цифровые: сигналов без ухудшения точности коммутации. На фиг, 1 приведена структурная электрическая схема устройства тации асинхронных .цифровых сигналов, на фиг. 2 к 3 -- временные диа,граммь 8 пояснягопще работу устройства.

Устройство содержит блок: 1 памяти . информации, блок 2 передачи у блок 3 памяти адресов, формирователь 4 сигналов .записи, формирователь 5 сигналов чтения, блок 6 управления коэффициентом деления, блок 7 делителей частоты, формирователь 8 сигналов

блокировки и блок 9 сннхронизации. I

Устройство коммутации асинхронных

цифровых сигналов работает следующим образом.

При побитной коммутации асннхр он- ных разноскоростных каналов в магистраль из входящих линий связи циклически поступают информ ационные биты с сигналами: сопровождения. Коммутируемой входящей линии связи отводится определенная временная позиция - временной канал. Из-за неравенства длите льности периодов сигналов, поступающих из входящих линий свя-зи, один

и тот же бит в.цикле опроса в магист .раль выдается многократно так как

при мультиплексировании коммутируемы входящих -линий связи без потери бита цикл магистрали должен быть меньше длительцости периода наибольшей скорости передачи информации. Для однократной записи информационного бита 1 первая передача бита сопровождается сигналом сопрово:ждения5 поступающим на синхронизирующий вход блока 1, Последующая передача этого же бита по Магистрали производится без сигнала сопровождения. Устройство не имеет внутренних блокировок, поэтому число врем€ нньгк йаналов в магистрали равно числу исходящих линий связи,а цикл работы магистрали равен циклу обслуживания исходяп их линий связи р подключенньгх к устройству.

Для осуществления соединения временных каналов магистрали или соотве

1522 2

ствуюи х им входящих линий связи с исходящими линиями связи в устройств осуществляется временная коммутация посредством записи адресов кoм ryтиpy 5 пинии связи- в блок 3 в два этапа. Вначал:е устройство управления устанавливает необходимую скорость выдачи информации в исходяпг/ю линию свзи, равную скорости входящей линии 0 связиS путем выдачи кока-иды; адреса исходящей линют связи и адреса одной из частот в блок 3. Частоты вырабатываются блоком 9 и подключаются к блоку /5 причем каждой скорости передач ifi информации соответствует своя часто- та. проключення соответствующей частоты на вход делителя блока 7 по команде и адресу исходящей л:«нии с вя зл адрес частоте транслируаг ый че- ЙО рез блок 3, записывается в оди-из делителей г после чего частота с выхода блока 9 поступает на вход соответствующего делителя. Делители (Ij.o.jn) из проключенных частот вы- рабатывают соответствунэщие частоты выдачи5 которыми инфо.рмация выдается из блока 2 в исходящие линии связи.

Затем устройство упр авления устанавливает соединение i ВК магистрали с jисходящей, линией связи,, для чего выдает команду и адреса А) и А- ВК магистрали.. По команде адрес Aj записывается в 4,-тую ячейку блока 3, посла чего кo пv yтaция считается ус- :j,j тановленной.

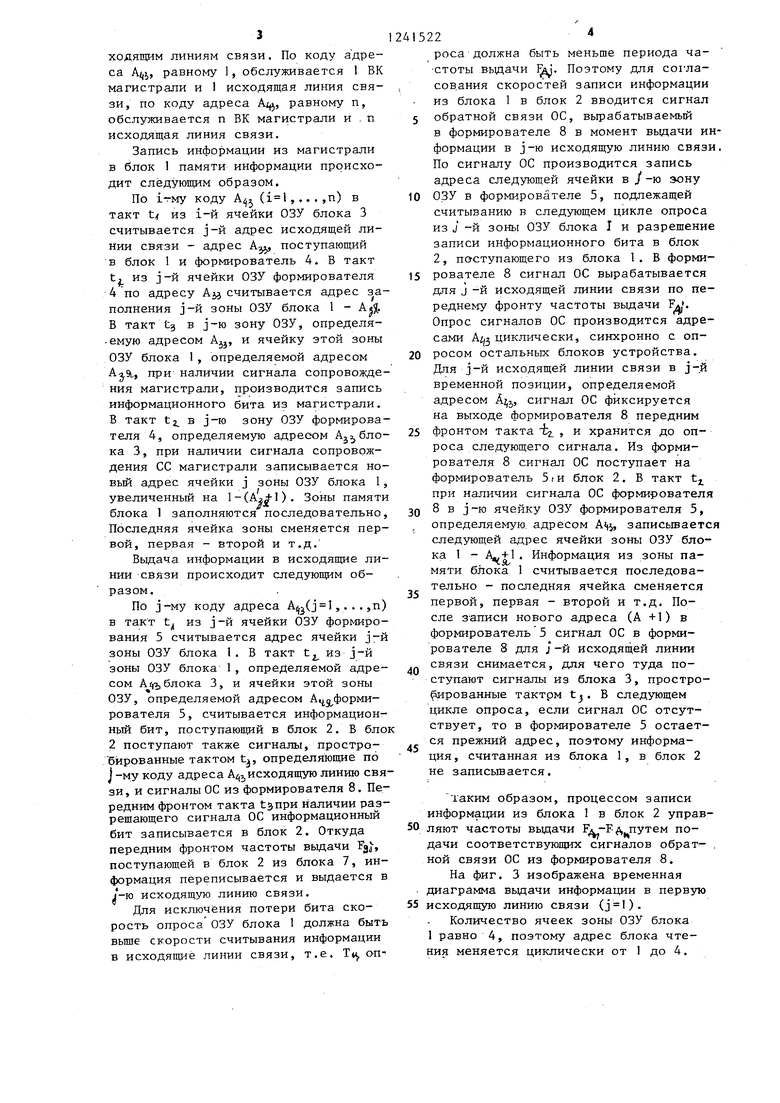

А ггоритм работы устройства происходит согласно временной диаграмме, изображенной иа .фиг.. 2. Период 1 . информации,.соответствующий наиболь- ijjj шей скорости информации,. меньше длит ель нести цикла Т. магистрали или цикла обслуживания исходящих линий связи. Т, разделен на В-К магистрали или временные позиции обслуживания ,ji| исходящ гх линий связи. Каждьш ВК или временная позиция ра.зделена на такты t -t4|« каждый из которых содер: Ят в себе соответственно такты t -tj .. Запись адреса исходящей линии связи по ,jQ адресу БК канала магистрапи в блок 3,. т.е. установление соединения в устрС йстве, происходит в такты t-j и tj каждой временной позиции (ВК).

Запись информации из магистрали в блок 1 происходит слег ующим образо

Бл:ок 3 циклически и синхронно с магистр ЕЛЬЮ вырабатывает адреса А , соответствующие ВК магистрали и ис3

ходящим линиям связи. По коду адреса А(,),, равному 1, обслуживается 1 ВК магистрали и 1 исходящая линия связи, по коду адреса A.i, равному п, обслуживается п ВК магистрали и . п исходящая линия связи.

Запись информации из магистрали в блок 1 памяти информации происходит следующим образом.

По i-гму коду (,...,n) в такт t из i-й ячейки ОЗУ блока 3 считывается j-й адрес исходящей линии связи - адрес А поступающий в блок 1 и формирователь 4. В такт t из j-й ячейки ОЗУ формирователя 4 по адресу А считывается адрес полнения j-й зоны ОЗУ блока 1 - В такт t3 в j-ю зону ОЗУ, определя- .емую адресом Ajj, и ячейку этой зоны ОЗУ блока 1, определяемой адресом , при наличии сигнала сопровождения магистрали, производится запись информационного бита из магистрали. В такт tji, в j-ю зону ОЗУ формирователя 4, определяемую адресом Aji, блока 3, при наличии сигнала сопровождения СС магистрали записывается новый адрес ячейки j зоны ОЗУ блока 1, увеличенный на -(). Зоны памяти блока 1 заполняются последовательно. Последняя ячейка зоны сменяется первой, первая - второй и т.д.

Вьщача информации в исходящие линии связи происходит следующим образом.

По j-му коду адреса A(j l,. .. ,п) в такт t из j-й ячейки ОЗУ формирования 5 считывается адрес ячейки j-й зоны ОЗУ блока 1. В такт t из j-й зоны ОЗУ блока 1, определяемой адресом AfiT, блока 3, и ячейки этой зоны ОЗУ, определяемой адресом А.|5(форми- рователя 5, считывается информацион- нь1й бит, поступающий в блок 2. В бло 2 поступают также сигналы, простро- бированные тактом t, определяющие по -му коду адреса А/,, исходящую линию связи , и сигналы ОС из формирователя 8. Передним фронтом такта tзпpи наличии раз- рещающего сигнала ОС информационный бит записывается в блок 2. Откуда передним фронтом частоты выдачи Fgj-, поступающей в блок 2 из блока 7, информация переписывается и выдается в 1-ю исходящую линию связи.

Для исключения потери бита скорость опроса ОЗУ блока 1 должна быть вьше скорости считывания информации в исходящие линии связи, т.е. Ti оп

41522

роса должна быть меньше периода ча- стоты выдачи 1д). Поэтому для сог ла- сов.ания скорос тей записи информации из блока 1 в блок 2 вводится сигнал 5 обратной связи ОС, вьфабатываемый в формирователе 8 в момент выдачи информации в j-ю исходящую линию связи. По сигналу ОС производится запись адреса следующей ячейки в j-ю зону 10 ОЗУ в формирователе 5, подлежащей считыванию в следующем цикле опроса из J -и зоны ОЗУ блока I и разрещение записи информационного бита в блок 2, поступающего из блока 1. В форми- 15 рователе 8 сигнал ОС вырабатывается для J-и исходящей линии связи по переднему фронту частоты вьщачи FA. Опрос сигналов ОС производится адресами Aij3 циклически, синхронно с оп- 20 росом остальных блоков устройства. Для j-й исходящей линии связи в j-й временной позиции, определяемой адресом AJ;J, сигнал ОС фиксируется на выходе формирователя 8 передним 25 фронтом такта i и хранится до опроса следующего сигнала. Из формирователя 8 сигнал ОС поступает на формирователь 5ги блок 2. В такт tj при наличии сигнала ОС формирователя 30 8 в j -ю ячейку 033 формирователя 5, определяемую адресом Ацг„ записьшается следующей адрес ячейки зоны ОЗУ блока 1 - . Информация из зоны памяти блока 1 считывается последовательно - последняя ячейка сменяется первой, первая - второй и т.д. После записи нового адреса (А +1) в формирователь 5 сигнал ОС в формирователе 8 для J-и исходящей линии связи снимается, для чего туда поступают сигналы из блока 3, простро- рованные тактрм tj. В следующем цикле опроса, если сигнал ОС отсутствует, то в формирователе 5 остается прежний адрес, поэтому информация , считанная из блока 1, в блок 2 не записьшается.

35

40

45

таким образом, процессом записи информации из блока 1 в блок 2 управ 50 ляют частоты выдачи путем подачи соответствующих сигналов обрат- ной связи ОС из формирователя 8.

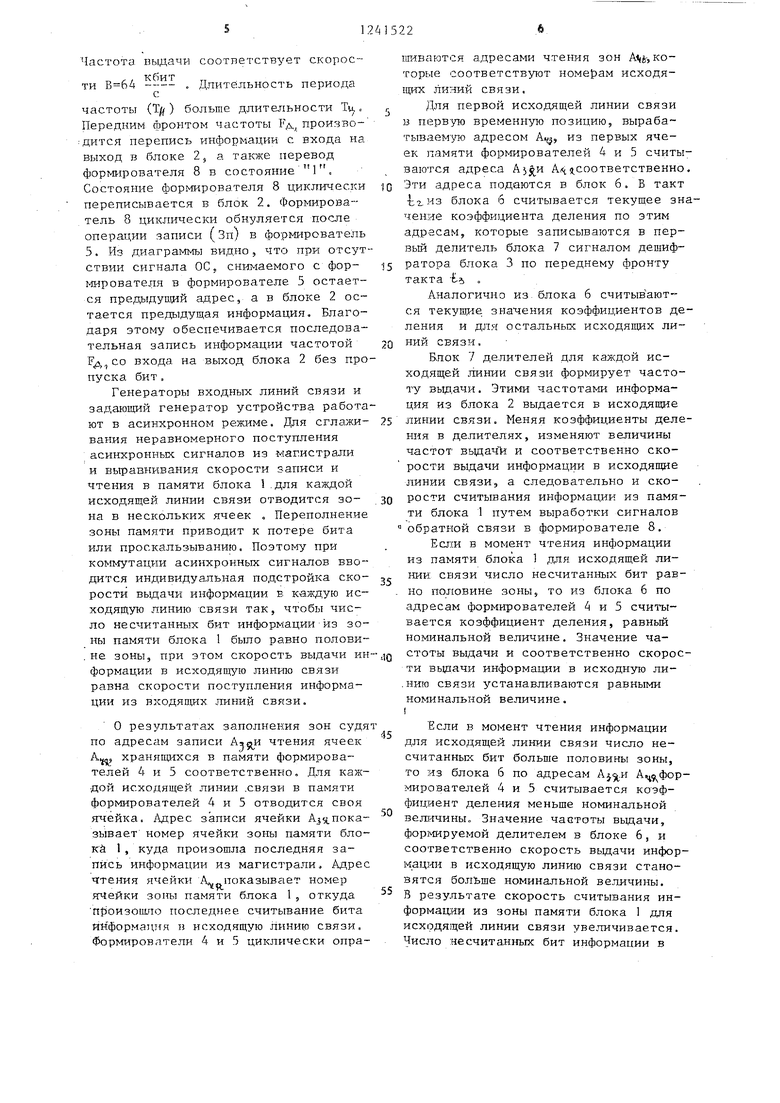

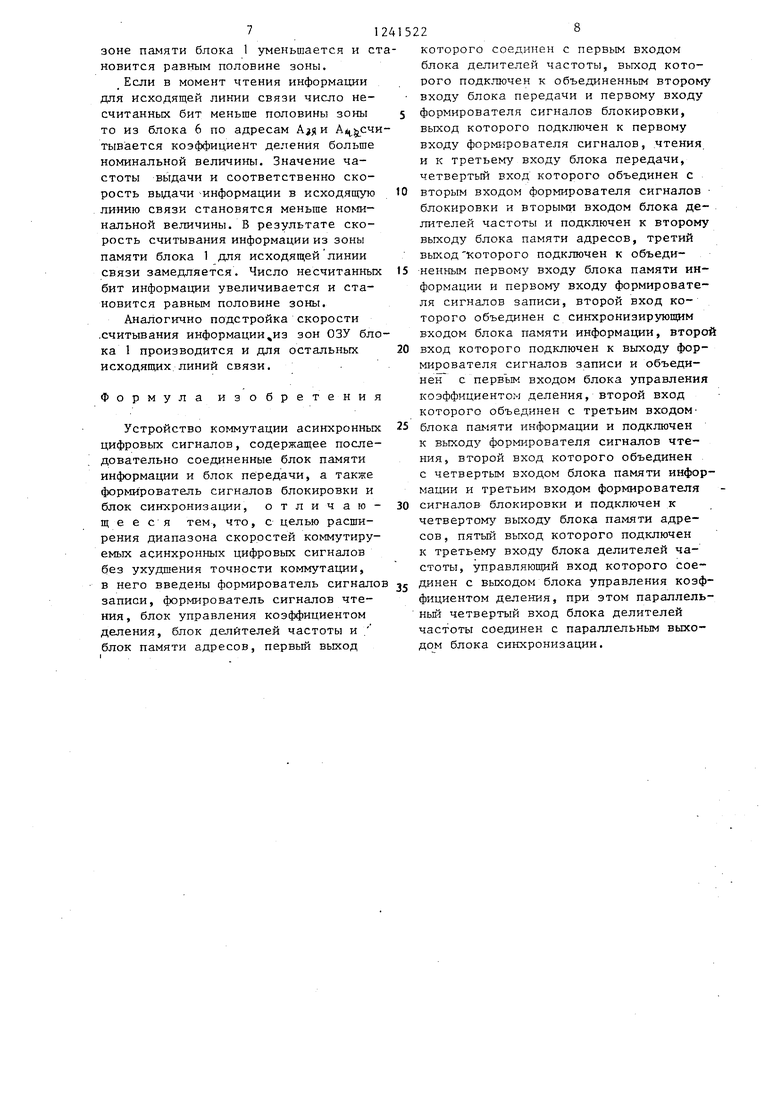

На фиг. 3 изображена временная диаграмма выдачи информации в первую 55 исходящую линию связи ().

Количество ячеек зоны ОЗУ блока 1 равно 4, поэтому адрес блока чтения меняется циклически от 1 до 4.

выдачи соответствует скорое- Длительность периода

кбит

с

частоты (T.jf) больше длительности Ти,, Передним фронтом частоты Рд, производится перепись информации с входа на выход в блоке 2, а также перевод формирователя 8 в состояние 1 Состояние формирователя 8 циклически переписывается в блок 2. Формирова-- тель 8 циклически обнуляется после операции записи (Зп) в формирователь 5. Из диаграммы видно, что при отсутствии сигнала ОС, снимаемого с формирователя в формирователе 5 остается предыдущий адрес, а в блоке 2 остается предыдущая информация. Благодаря этому обеспечивается последовательная запись информации частотой входа на выход блока 2 без пропуска бит.

Генераторы входных линий связи и задающий генератор устройства работают в асинхронном режиме. Для cглaJки- вания неравномерного поступления асинхронных сигналов из магистрали и выравнивания скорости записи и чтения в памяти блока 1.для каждой исходящей линии связи отводится зона в нескольких ячеек , Переполнение зоны памяти приводит к потере бита или проскальзыванию. Поэтому при коммутации асинхронных сигналов вводится индивидуальная подстройка скорости выдачи информации в каждую исходящую линию связи так, чтобы число несчитанных бит информации из зоны памяти блока 1 было равно полови- . не зоны, при этом скорость выдачи информации в исходяшб ю линию связи равна скорости поступления информации из ВХОДЯП1ИХ линий связи.

о результатах заполнения зон судя по адресам записи чтения ячеек А. хранящихся в памяти формирователей 4 и 5 соответственно. Для каждой исходящей линии .связи в памяти формирователей 4 и 5 отводится своя ячейка. Адрес записи ячейки А5япока- зывает номер ячейки зоны памяти блоки 1, куда произошла последняя запись информации из магистрали. Адрес чтения ячейки А показывает номер ячейки зоны памяти блока 1, откуда П{1оизо111г1о послед} ее считывание бита информация в исходящую линию связи. Формирователи 4 и 5 циклически опра5

0

5

0

5

5

шиваются адресами чтения зон , которые соответствуют номерам исходя- шдх линий связи.

Для первой исходящей линии связи в перв-ую временную позицию, выраба- тываем-уто адресом А, из первых ячеек памяти формирователей 4 и 5 считываются адреса А соответственно, Эти адреса подаются в блок 6. В такт блока б считывается текущее значение коэффициента деления по этим адресам, которые записываются в первый делитель блока 7 сигналом дешифратора блока 3 по переднему фронту такта ti ,

Аналогично из блока 6 считыв ают- ся текущие значения коэффициентов деления и для остальных исходяшдх линий связи.

Блок 7 делителей для каждой исходящей линии связи формирует частоту вьщачи. Этими частотами информация из блока 2 выдается в исходящие линии связи. Меняя коэффициенты деления в делителях, изменяют величины частот вьщач и и соответственно скорости выдачи информации в исходящие линии связи, а следовательно и скорости считывания информации из памяти блока 1 путем выработки сигналов обратной связи в формирователе 8.

Если в момент чтения информации из памяти блока 1 для исходящей линии связи число несчитанных бит равно половине зоны, то из блока 6 по адресам форм:ирователей к 5 считывается коэффициент деления, равньш номинальной величине. Значение частоты выдачи и соответственно скорости вьщачи информации в исходную ли- .нию связи устанавливаются равными номинальной величине,

Если в момент чтения информации для исходящей линии связи число несчитанных бит больше половины зоны, то из блока 6 по адресам (,и мирователей 4 и 5 считывается коэффициент деления меньше номинальной веш-1чины„ Значение частоты вьщачи, фор)чируемой делителем в блоке 6, и соответственно скорость выдачи информации в исходящую линию связи становятся больше номинальной величины. В результате скорость считывания ин- формац:ии из зоны памяти блока 1 для исх(рдящей линии связи увеличивается. Число несчитанных бит информации в

зоне памяти блока 1 уменьшается и стновится равным половине зоны.

Если в момент чтения информации для исходящей линии связи число не- считанньк бит меньше половины зоны то из блока 6 по адресам и тывается коэффициент деления больше номинальной величины. Значение частоты выдачи и соответственно скорость выдачи -информации в исходящую линию связи становятся меньше номинальной величины. В результате скорость считывания информации из зоны памяти блока 1 для исходящей линии связи замедляется. Число несчитанных бит информации увеличивается и становится равным половине зоны.

Аналогично подстройка скорости .считывания информации,из зон ОЗУ блока 1 производится и для остальных исходящих линий связи.

Формула изобретения

Устройство коммутации асинхронных цифровых сигналов, содержащее последовательно соединенные блок памяти информации и блок передачи, а также формирователь сигналов блокировки и блок синхронизации, отличаю- щ е е с я тем, что, с целью расширения диапазона скоростей коммутируемых асинхронных цифровых сигналов без ухудшения точности коммутации, в него введены формирователь сигнало записи, формирователь сигналов чтения, блок управления коэффициентом деления, блок делителей частоты и . блок памяти адресов, первый выход

которого соединен с первым входом блока делителей частоты, выход которого подключен к объединенным второму входу блока передачи и первому входу формирователя сигналов блокировки, выход которого подк1дачен к первому входу формирователя сигналов, .чтения и к третьему входу блока передачи, четвертый вход которого объединен с вторым входом формирователя сигналов блокировки и вторыми входом блока де- Л11телей частоты и подключен к второму выходу блока памяти адресов, третий выход которого подключен к объединенным первому входу блока памяти информации и первому входу формирователя сигналов записи, второй вход которого объединен с синхронизирующим входом блока памяти информации, второ вход которого подключен к выходу формирователя сигналов записи и объединен с перв ым входом блока управления коэффициентом деления, второй вход которого объединен с третьим входом блока информации и подключен к выходу формирователя сигналов чтения, второй вход которого объединен с четвертым входом блока памяти информации и третьим входом формирователя сигналов блокировки и подключен к четвертом выходу блока памяти адресов , пятый выход которого подключен к третьему входу блока делителей частоты, управляюш й вход которого соединен с выходом блока управления коэффициентом деления, при этом параллель- ньй четвертый вход блока делителей частоты соединен с параллельным выходом блока синхронизации.

5S Tj.

SSToc

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство коммутации с эластичной памятью | 1988 |

|

SU1647921A1 |

| Устройство коммутации асинхронных разноскоростных дискретных сигналов | 1988 |

|

SU1550630A1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ АСИНХРОННЫХ РАЗНОСКОРОСТНЫХ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2014737C1 |

| Устройство преобразования и коммутации сигналов | 1988 |

|

SU1566505A1 |

| Устройство сопряжения асинхронных разноскоростных цифровых сигналов | 1990 |

|

SU1755386A1 |

| Устройство передачи биимпульсных сигналов | 1989 |

|

SU1653169A1 |

| Многомодульная коммутационная система для асинхронных цифровых сигналов | 1982 |

|

SU1125766A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Устройство временной коммутации биимпульсных сигналов | 1989 |

|

SU1711344A1 |

| Устройство временной коммутации асинхронных цифровых сигналов | 1989 |

|

SU1700762A1 |

Изобретение относится к электросвязи и обеспечивает расширение диапазона скоростей коммутируемых асинхронных цифровьпс сигналов без ухудшения точности коммутации. Устр-во содержит блок памяти информации (БПИ) 1, блок 2 передачи, блок памяти адресов (БПА) 3, формирователь 4 сигналов записи, формирователь 5 сигналов чтения, блок 6 управления коэф. деления, блок 7 делителей частоты, формирователь 8 сигналов блокировки и блок 9 синхронизации. Коммутируемой входящей линии связи (ЛС) отводится определимый временной канал. Один и тот же бит в цикле опроса в магистраль выдается многократно. Для однократной записи информационного бита в БПИ I первая передача бита сопровождается сигналом сопровождения, а последующие - без сигнала сопровождения. Для осуществления соединения временных каналов магистрали или соответствуннцих им входящих ЛС с исходящими ЛС в устр-ве осуществляется временная коммутация посредством записи адресов коммутируемых ЛС в БПА 3 в два этапа. Сначала устанавливается необходимая скорость выдачи информации в исходящую, ЛС, равную скорости входящей ЛС. Это осуществляется подачей команды адреса исходящей ЛС и адреса одной из частот в БПА 3. Каждой скорости передачи соответствует своя частота. Затем устанавливается соединение магистрали с исходящей ЛС. По команде устройства управления адрес записывается в ячейку БПА 3, после чего коммутация считается установленной.Зил. (Л С N 4 ел ND

1in fr3a2 if,Vr.3fi.f,Vr3ir. ипиЧгЗн. „.Vr.Jff, j ЧТ.Зп.

Составитель В.Шевцов. .

Редактор Т.Парфенова Техред О.Гортвай Корректор В. Бутяга

Заказ 3616/58 Тираж 624 . Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое .предприятие, г. Ужгород, ул. Проектная, 4

| Иносэ X | |||

| Интегральные цифровые сети связи | |||

| М.: Радио и связь, 1982, с | |||

| Спускная труба при плотине | 0 |

|

SU77A1 |

| Устройство для пространственновременной коммутации асинхронных цифровых сигналов | 1977 |

|

SU652727A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-06-30—Публикация

1985-01-31—Подача