мация в такт с

см

а затем эта инфор

мация в такт i,3n перезаписывается в блок 10 выдачи сигналов. Общий цикл обращения к блокам 9 и 10 состоит из N (N количество линий канала 1), указанных частных обращений. Величина N определяет число ячеек памяти в блоках 9 и 10. За один общий цикл произ водится преобразование одного бита служебных сигналов, записанных в N ячейках памяти блоков 9 и 10. Число общих циклов определяется счетчиком 14 записи и соответствует числу разрядов в служебных сигналах записанных в блоках 9 и 10. Для того, чтобы преобразовать и передать. в линию связи служебный сигнал, имеющий, на

пример 8 разрядов (Фиг.Юа), необходимо 8 циклов, которые подсчитываются с помощью четырехразрядного счетчика -14 записи. При этом три старших разряда этого счетчика подсчитыва- ,

0

5

0

5

дачи сигналов в такт ,„ без сдвига

эп

разрядов информации. При этом & первый разряд блока 10 вьщачи сигналов информация из регистра 11 не записывается. I

Запись информации из регистра 1 1

в блок 10-1 памяти производится через элементы И 37, ИЛИ 38 в такт Гэг записи. Сигнал записи вырабатывается при о( 0, d 1 . При этом поступающие на элемент И-НЕ 40 разряды (или один из них) сигнала d, равны нулю, а на выходе элемента И-НЕ 40 сигнал о( 1 , который поступает на соответствующие элементы НЕ 39, И 37. В такте С Эп сигнал d(l обеспечивает через соответствующий элемент ИЛИ 38 выработку сигнала записи информации, поступающей из регистра 1 1 и проходящей через соответствующий элемент ИЛИ 38, в блок 36 памяти. При записи информапин в последний из блока 9 служебных сигналов производится выработка сигнала записи с помощью сигнала

Информация из старшего (п+1)-го

разряда регистра 11 (Лиг.9) выдается на соответствующий элемент НЕ 31 (Лиг.6) блока 12 преобразования сигналов,

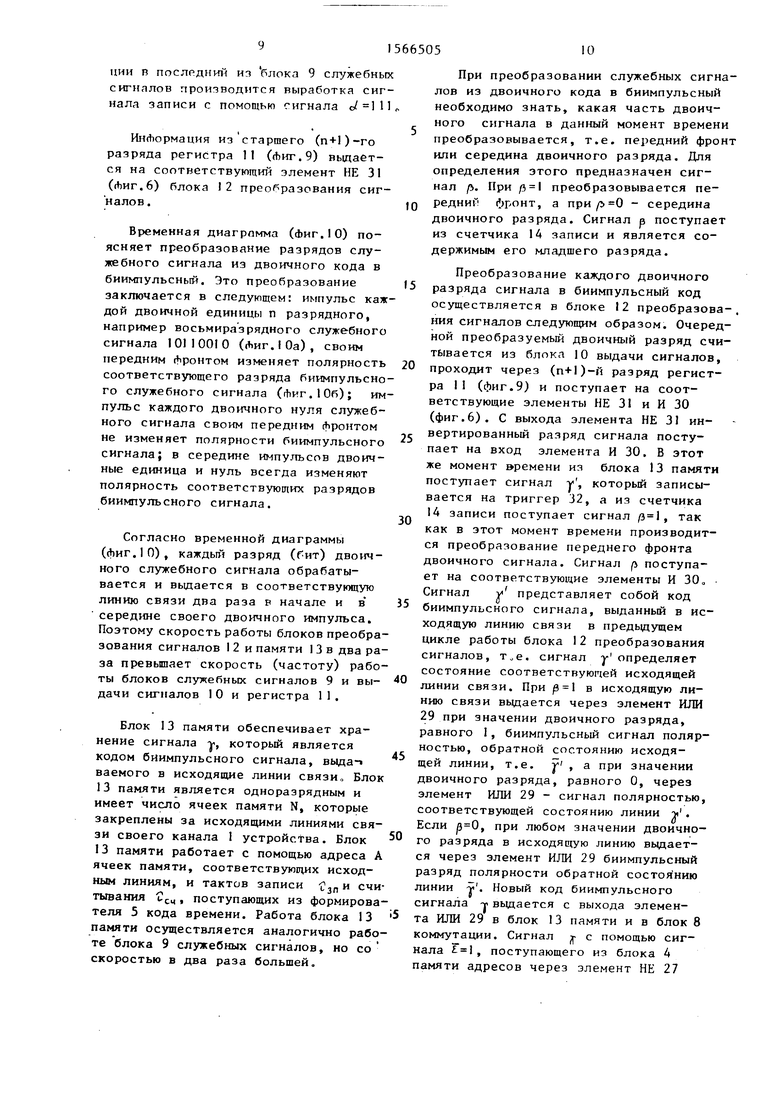

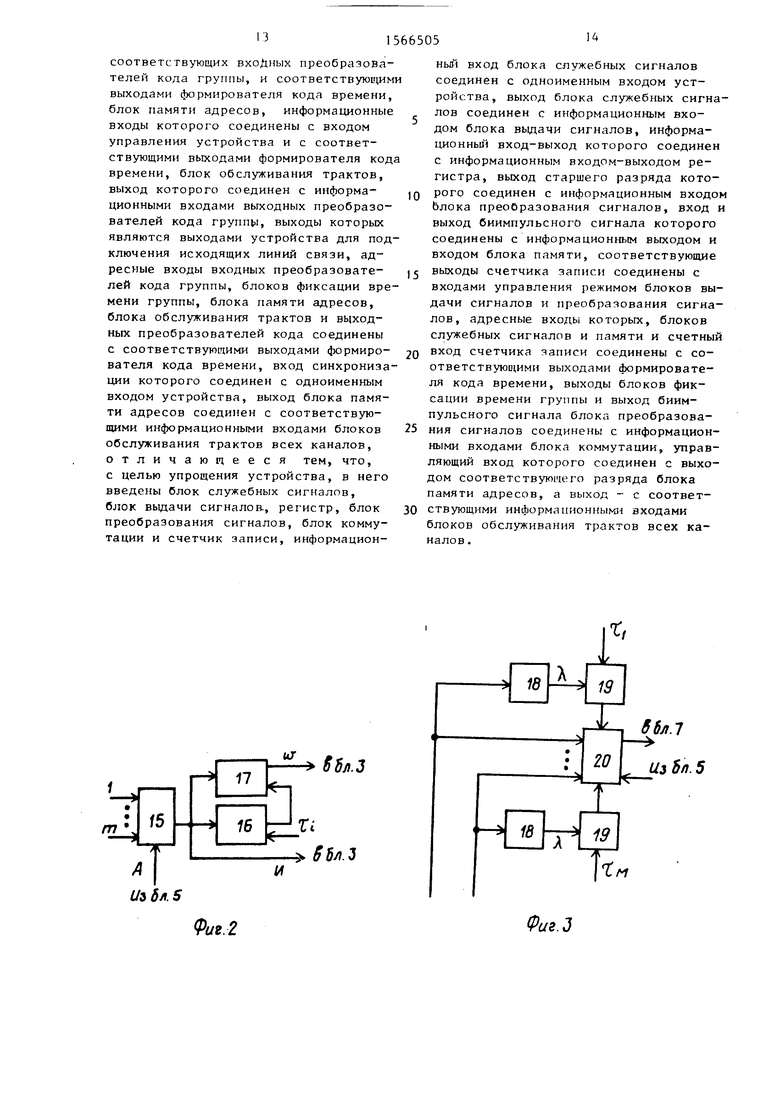

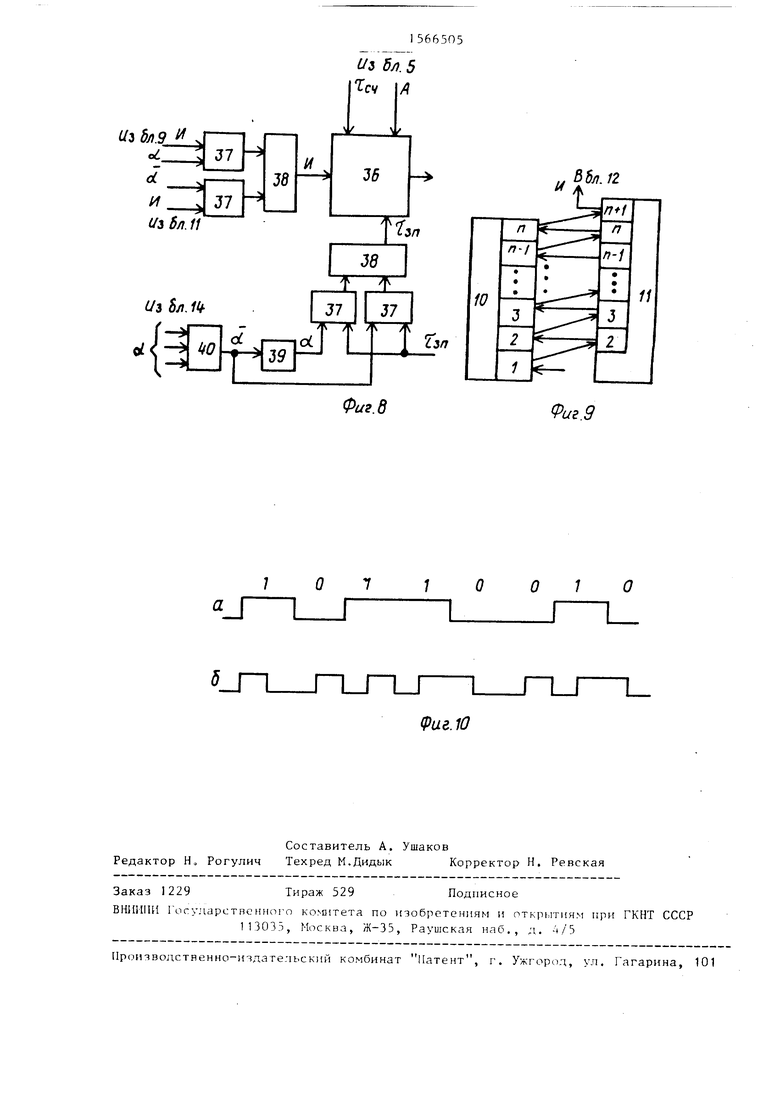

Временная диаграмма (фиг.10) поясняет преобразование разрядов служебного сигнала из двоичного кода в биимпульсный. Это преобразование

заключается в следующем: импульс каждой двоичной единицы п разрядного, например восьмиразрядного служебного сигнала 10110010 (Лиг.10а), своим передним Фронтом изменяет полярность соответствующего разряда биимпульсно- го служебного сигнала (фиг.1 Об); импульс каждого двоичного нуля служебного сигнала своим передним фронтом не изменяет полярности биимпульсного сигнала; в середине импульсов двоичные единица и нуль всегда изменяют полярность соответствующих разрядов биимпульсного сигнала.

Согласно временной диаграммы (Лиг.10), каждый разряд (Гит) двоичного служебного сигнала обрабатывается и выдается в соответствующую линию связи два раза в начале и в середине своего двоичного импульса. Поэтому скорость работы блоков преобразования сигналов 12 и памяти 13 в два раза превышает скорость (частоту) работы блоков служебных сигналов 9 и вы- дачи сигналов 10 и регистра 11.

Блок 13 памяти обеспечивает хранение сигнала у, который является кодом биимпульсного сигнала, выдач ваемого в исходящие линии связи0 Блок 13 памяти является одноразрядным и имеет число ячеек памяти N, которые закреплены за исходящими линиями связи своего канала 1 устройства. Блок 13 памяти работает с помощью адреса А ячеек памяти, соответствующих исходным линиям, и тактов записи Јзп и считывания Јсч, поступающих из формирователя 5 кода времени. Работа блока 13 памяти осуществляется аналогично работе блока 9 служебных сигналов, но со скоростью в два раза большей.

5

to

(5

0

5

0

5 0

5

0

При преобразовании служебных сигналов из двоичного кода в биимпульсный необходимо знать, какая часть двоичного сигнала в данный момент времени преобразовывается, т.е. передний фронт или середина двоичного разряда. Для определения этого предназначен сигнал /. При р преобразовывается пе- редниг фронт, а при/5 0 - середина двоичного разряда. Сигнал р поступает из счетчика 14 записи и является содержимым его младшего разряда.

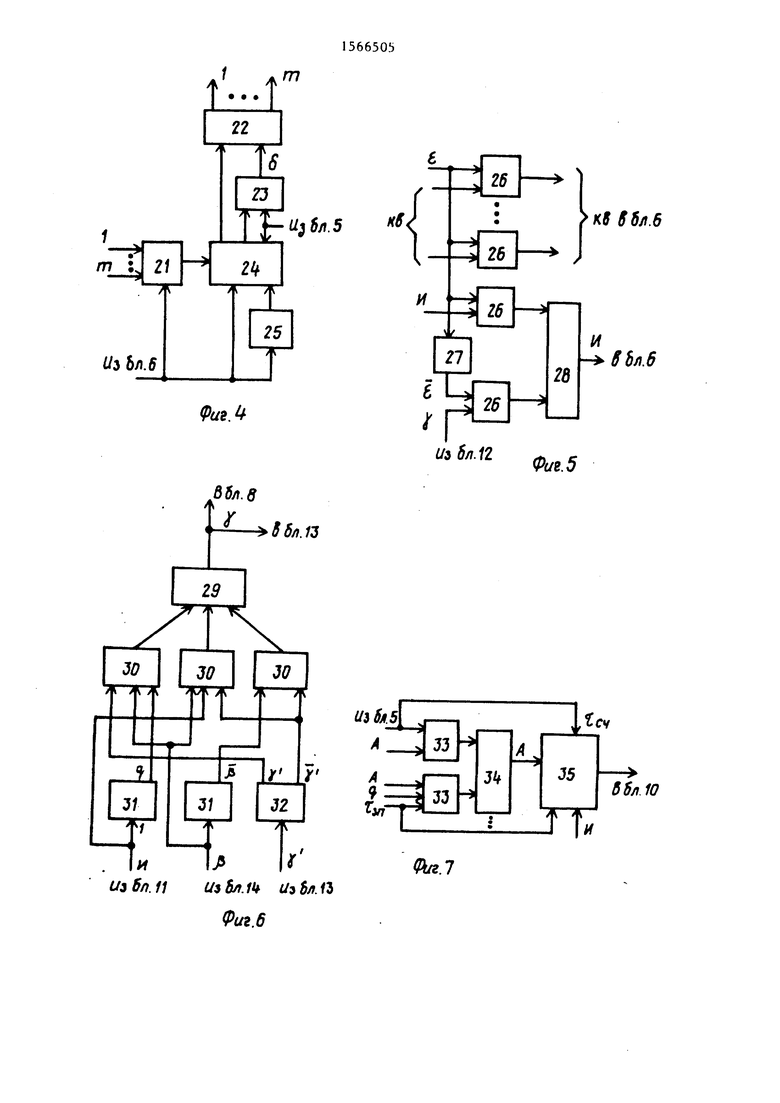

Преобразование каждого двоичного разряда сигнала в биимпульсный код осуществляется в блоке 12 преобразова-. ния сигналов следующим образом. Очередной преобразуемый двоичный разряд считывается из блока 10 выдачи сигналов, проходит через (п+1)-н разряд регистра 11 (фиг.9) и поступает на соответствующие элементы НЕ 31 и И 30 (фиг.6). С выхода элемента НЕ 31 инвертированный разряд сигнала поступает на вход элемента И 30. В этот же момент в-ремени из блока 13 памяти поступает сигнал у , который записывается на триггер 32, а из счетчика 14 записи поступает сигнал /3 1, так как в этот момент времени производится преобразование переднего фронта двоичного сигнала. Сигнал р поступает на соответствующие элементы И 30„ Сигнал У представляет собой код биимпульсного сигнала, выданный в исходящую линию связи в предыдущем цикле работы блока 12 преобразования сигналов, т„е. сигнал у определяет состояние соответствующей исходящей линии связи. При в исходящую линию связи выдается через элемент ИЛИ 29 при значении двоичного разряда, равного I, биимпульсный сигнал полярностью, обратной состоянию исходящей линии, т.е. г , а при значении двоичного разряда, равного 0, через элемент ИЛИ 29 - сигнал полярностью, соответствующей состоянию линии У. Если , при любом значении двоичного разряда в исходящую линию выдается через элемент ИЛИ 29 биимпульсный разряд полярности обратной состоянию линии -V1. Новый код биимпульсного сигнала е выдается с выхода элемента ИЛИ 29 в блок 13 памяти и в блок 8 коммутации. Сигнал с помощью сигнала , поступающего из блока 4 памяти адресов через элемент НЕ 27

(фиг.5), проходит через элементы И 26, ИЛИ 28 и выдается на вход блока 6 обслуживания трактов вместе с нулевым кодом времени с элементов И 26.

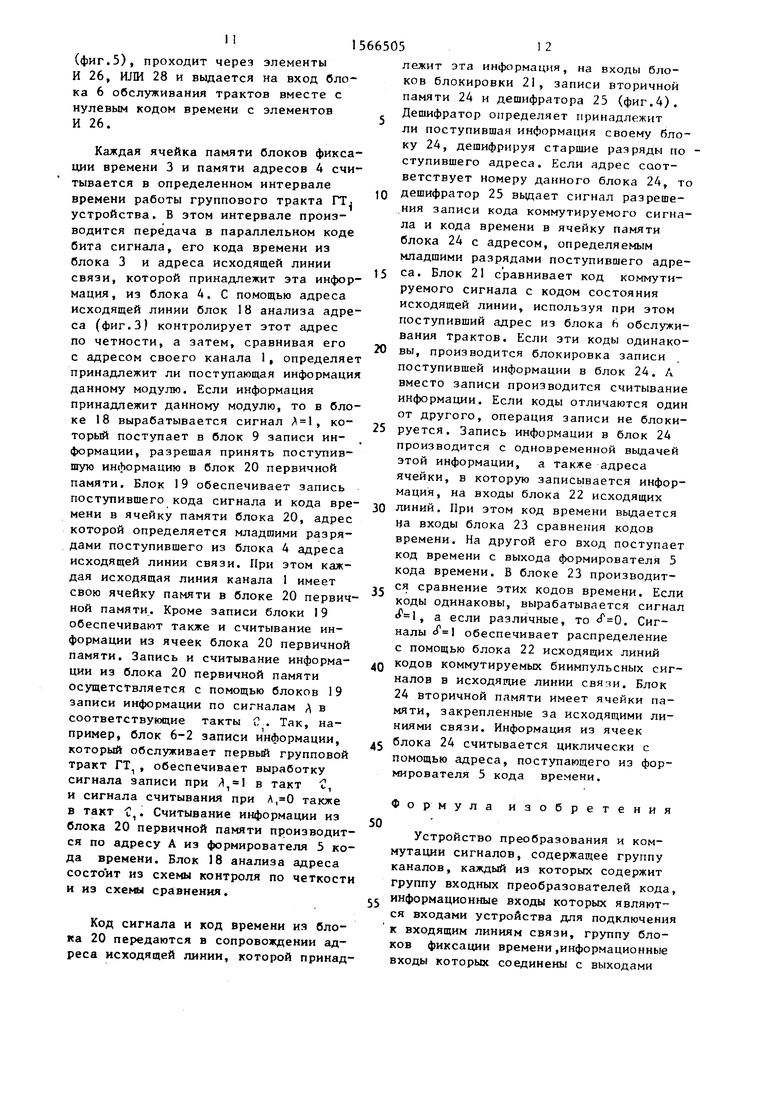

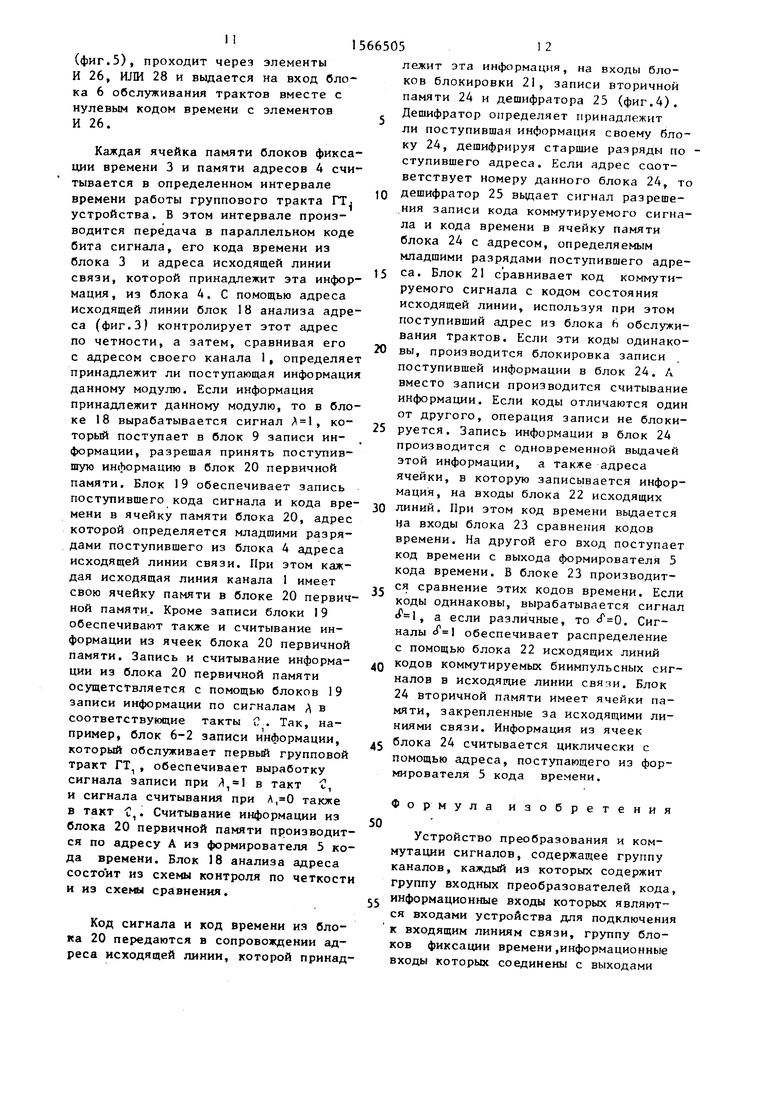

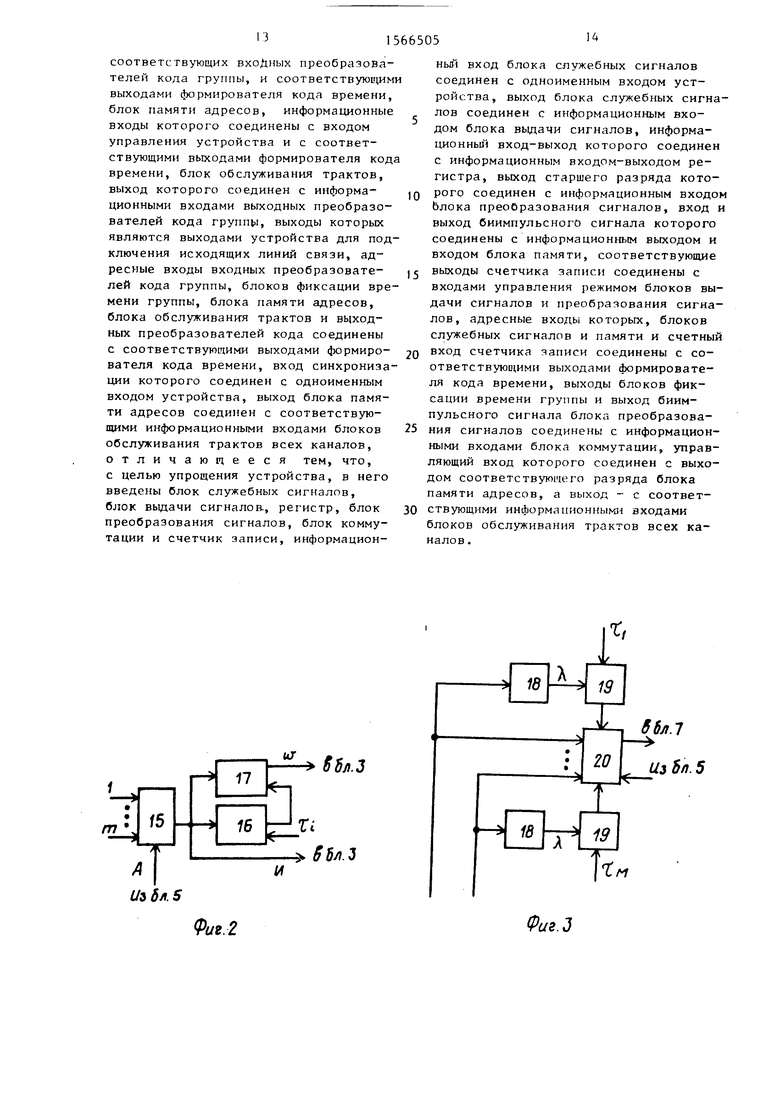

Каждая ячейка памяти блоков фиксации времени 3 и памяти адресов 4 считывается в определенном интервале времени работы группового тракта ГТ устройства. В этом интервале производится передача в параллельном коде бита сигнала, его кода времени из блока 3 и адреса исходящей линии связи, которой принадлежит эта информация, из блока 4. С помощью адреса исходящей линии блок 18 анализа адреса (фиг.З) контролирует этот адрес по четности, а затем, сравнивая его с адресом своего канала 1, определяет принадлежит ли поступающая информация данному модулю. Если информация принадлежит данному модулю, то в блоке 18 вырабатывается сигнал Л 1, который поступает в блок 9 записи ин- формации, разрешая принять поступившую информацию в блок 20 первичной памяти. Блок 19 обеспечивает запись поступившего кода сигнала и кода времени в ячейку памяти блока 20, адрес которой определяется младшими разрядами поступившего из блока 4 адреса исходящей линии связи. При этом каждая исходящая линия канала 1 имеет свою ячейку памяти в блоке 20 первичной памяти. Кроме записи блоки 19 обеспечивают также и считывание информации из ячеек блока 20 первичной памяти. Запись и считывание информации из блока 20 первичной памяти осуществляется с помощью блоков 19 записи информации по сигналам Д в соответствующие такты С . Так, например, блок 6-2 записи информации, который обслуживает первый групповой тракт ГТ1, обеспечивает выработку сигнала записи при / 1 в такт t), и сигнала считывания при А,0 также в такт С1. Считывание информации из блока 20 первичной памяти производится по адресу А из формирователя 5 кода времени. Блок 18 анализа адреса состоит из схемы контроля по четкости и из схемы сравнения.

Код сигнала и код времени из блока 20 передаются в сопровождении адреса исходящей линии, которой принадлежит эта информация, на входы блоков блокировки 21, записи вторичной памяти 24 и дешифратора 25 (фиг.4). Дешифратор определяет принадлежит ли поступившая информация своему блоку 24, дешифрируя старшие разряды по - ступившего адреса. Если адрес соответствует номеру данного блока 24, то

дешифратор 25 выдает сигнал разрешения записи кода коммутируемого сигнала и кода времени в ячейку памяти блока 24 с адресом, определяемым младшими разрядами поступившего адре5 са. Блок 21 сравнивает код коммутируемого сигнала с кодом состояния исходящей линии, используя при этом поступивший адрес из блока Ь обслуживания трактов. Если эти коды одинако0 вы, производится блокировка записи поступившей информации в блок 24. А вместо записи производится считывание информации. Если коды отличаются один от другого, операция записи не блоки5 руется. Запись информации в блок 24 производится с одновременной выдачей этой информации, а также адреса ячейки, в которую записывается информация, на входы блока 22 исходящих

0 линий. При этом код времени выдается На входы блока 23 сравнения кодов времени. На другой его вход поступает код времени с выхода формирователя 5 кода времени. В блоке 23 производит- , ся сравнение этих кодов времени. Если коды одинаковы, вырабатывается сигнал 1, а если различные, то . Сигналы Р обеспечивает распределение с помощью блока 22 исходящих линий

О кодов коммутируемых биимпульсных сигналов в исходящие линии связи. Блок 24 вторичной памяти имеет ячейки памяти, закрепленные за исходящими линиями связи. Информация из ячеек блока 24 считывается циклически с помощью адреса, поступающего из формирователя 5 кода времени.

Формула изобретения

0

Устройство преобразования и коммутации сигналов, содержащее группу каналов, каждый из которых содержит группу входных преобразователей кода, информационные входы которых являются входами устройства для подключения к входящим линиям связи, группу блоков фиксации времени,информационные входы которых соединены с выходами

соответствующих входных преобразователей кода группы, и соответствующим выходами формирователя кода времени, блок памяти адресов, информационные входы которого соединены с входом управления устройства и с соответствующими выходами формирователя код времени, блок обслуживания трактов, выход которого соединен с информационными входами выходных преобразователей кода группы, выходы которых являются выходами устройства для подключения исходящих линий связи, адресные входы входных преобразователей кода группы, блоков фиксации времени группы, блока памяти адресов, блока обслуживания трактов и выходных преобразователей кода соединены с соответствующими выходами формирователя кода времени, вход синхронизации которого соединен с одноименным входом устройства, выход блока памяти адресов соединен с соответствующими информационными входами блоков обслуживания трактов всех каналов, отличающееся тем, что, с целью упрощения устройства, в него введены блок служебных сигналов, блок выдачи сигнале в., регистр, блок преобразования сигналов, блок коммутации и счетчик записи, информационный вход блока служебных сигналов соединен с одноименным входом устройства, выход блока служебных сигналов соединен с информационным входом блока выдачи сигналов, информационный вход-выход которого соединен с информационным входом-выходом регистра, выход старшего разряда кото- Q рого соединен с информационным входом блока преобразования сигналов, вход и выход биимпульсного сигнала которого соединены с информационным выходом и входом блока памяти, соответствующие 5 выходы счетчика записи соединены с входами управления режимом блоков выдачи сигналов и преобразования сигналов, адресные входы которых, блоков служебных сигналов и памяти и счетный Q вход счетчика записи соединены с соответствующими выходами формирователя кода времени, выходы блоков фиксации времени группы и выход биимпульсного сигнала блока преобразова- 5 ния сигналов соединены с информационными входами блока коммутации, управляющий вход которого соединен с выходом соответствующего разряда блока памяти адресов, а выход - с соответ- 0 ствующими информационными входами блоков обслуживания трактов всех каналов .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство временной коммутации биимпульсных сигналов | 1989 |

|

SU1711344A1 |

| Устройство передачи биимпульсных сигналов | 1989 |

|

SU1653169A1 |

| Многомодульная коммутационная система для асинхронных цифровых сигналов | 1986 |

|

SU1394459A1 |

| Устройство пространсктвенно-временной коммутации | 1978 |

|

SU684772A1 |

| Устройство для контроля коммутационной системы | 1986 |

|

SU1401639A1 |

| Устройство преобразования биимпульсных уплотненных сигналов | 1985 |

|

SU1319308A1 |

| Устройство для пространственновременной коммутации асинхронных цифровых сигналов | 1977 |

|

SU652727A1 |

| Устройство для приема цифровых сигналов | 1989 |

|

SU1646065A1 |

| Устройство временной коммутации асинхронных цифровых сигналов | 1979 |

|

SU773955A1 |

| Устройство для приема дискретной информации в системах с решающей обратной связью | 1986 |

|

SU1478361A1 |

Изобретение относится к вычислительной технике и электросвязи и может быть использовано в системах цифровой коммутации сообщений. Цель изобретения - упрощение устройства. Цель достигается за счет введения блоков 9 служебных сигналов, блока 8 коммутации, блока 10 выдачи сигналов, регистра 11, блока 12 преобразования сигналов, блока 13 памяти и счетчика 14 записи, которые позволяют преобразовать двоичные коды управляющих сигналов в биимпульсные сигналы. 10 ил.

Uf

8бл.З

т

А

из 6л. 5

бЬл.З

И

Фиг.2

1

Г,

16

-

19

I

го

б 6л Л из Ьп. 5

18

19

Ytn

Фиг.З

oi щд

дыф

и

91

91

П2

92

е«-дщд w

92

9 Ыф Wiqtfi wvgt/t It vg fл

9Щ С/7

92

И

L

п

ЈJ/0fy-

ц

Ь ( М

1

ш

CZ

f

ш

С,0е9951

Фиг. в

О 7

ЛTIJ LJ

Us Ьл. 5

Фиг.9

10010

Фиг. Ю

| Коммутационная система для асинхронных цифровых сигналов | 1978 |

|

SU949839A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Многомодульная коммутационная система для асинхронных цифровых сигналов | 1982 |

|

SU1125766A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-05-23—Публикация

1988-01-13—Подача