Отцск.

13

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сопряжения асинхронных разноскоростных цифровых сигналов | 1990 |

|

SU1755386A1 |

| Устройство сопряжения разноскоростных асинхронных цифровых сигналов | 1988 |

|

SU1667266A1 |

| Устройство коммутации асинхронных цифровых сигналов | 1985 |

|

SU1241522A1 |

| Устройство для асинхронной коммутации цифровых сигналов | 1987 |

|

SU1506584A1 |

| Устройство для приема цифровых сигналов | 1989 |

|

SU1646065A1 |

| Устройство преобразования и коммутации сигналов | 1988 |

|

SU1566505A1 |

| Устройство коммутации асинхронных разноскоростных дискретных сигналов | 1988 |

|

SU1550630A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ЦИФРОВЫХ СИГНАЛОВ | 1991 |

|

RU2020764C1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ АСИНХРОННЫХ РАЗНОСКОРОСТНЫХ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2014737C1 |

| Многомодульная коммутационная система | 1985 |

|

SU1285616A1 |

Изобретение относится к электросвязи. Цель изобретения - повышение достоверности коммутации путем уменьшения фазовых флуктуации. Устройство содержит блок 1 памяти информации, блок 2 памяти адреса, блок 3 синхронизации, блок 4 эластичной памяти, формирователь 5 сигнала записи, формирователь 6 сигнала чтения, управляемый делитель 9 частоты, блок 11 передачи и формирователь 12 сигнала блокировки. Цель достигается введением блока 7 рассогласования, пространственного коммутатора 10 и его блока 8 управления. В устройстве осуществляется работа эластичной памяти, а именно накопление и удаление фазовых флуктуации входных сигналов без ее переполнения, выдача информации в исходящие линии связи и согласование скорости выдачи со скоростью коммутации. При этом подключение частот выдачи к исходящим линиям производится в коммутаторе 10. Определение необходимой частоты выдачи из заданных частот для удаления накопленных фазовых флуктуации (дрожаний) из эластичной памяти производится в блоке 7 путем сравнения адресов записи и чтения, вырабатываемых формирователями 5 и 6. Хранение адресов частот выдачи производится в блоке 8. 1 ил.

ОтУУ:

ОаЯОК

О.

Јь VJ

чэ

Ю

Изобретение относится к электросвязи и может быть использовано в устройствах коммутации асинхронных цифровых сигналов, осуществляющих коммутацию без потерь.

Цель изобретения - повышение достоверности коммутации путем уменьшения фазовых флуктуации.

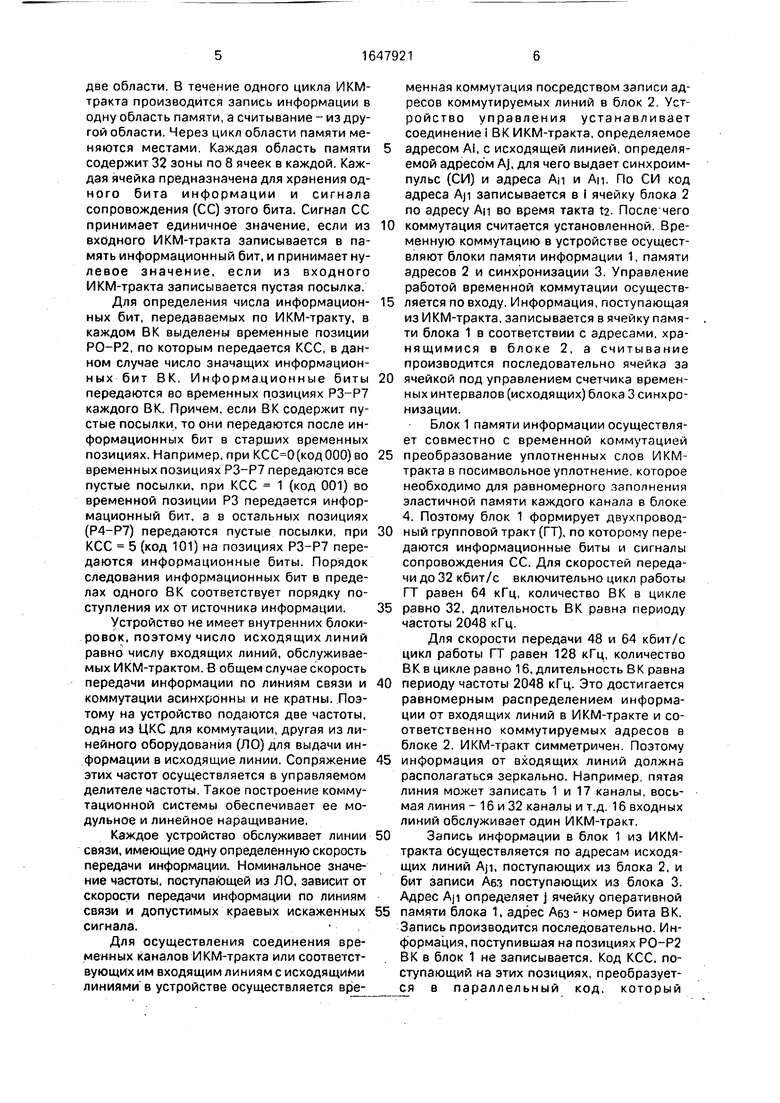

На чертеже изображена структурная схема устройства коммутации с эластичной памятью.

Устройство содержит блок 1 памяти информации, блок 2 памяти адреса, блок 3 синхронизации, блок 4 эластичной памяти, формирователь 5 сигнала записи, формирователь 6 сигнала чтения, блок 7 рассогласования, блок 8 управления пространственным коммутатором, управляемый делитель 9 частоты, пространственный коммутатор 10, блок 11 передачи, формирователь 12 сигнала блокировки и информационный вход 13 устройства.

Устройство работает следующим образом,

Для исключения потери бита при коммутации асинхронных сигналов скорость комму ации в устройстве должна быть выше скорости входящего потока информации. Входной поток поступает по тракту импуль- сно-кодовой модуляции (ИКМ)типа ИКМ-30. имеющему цикл F 8 кГц, 32 временных канала (ВК), 8 бит во временном канале, скорость передачи битов 2048 кбит/с. Емкость предлагаемого устройства равна числу ВК тракта, т.е. число исходящих линий связи h 32.

Информация по ВК тракта передается по методу двухстороннего согласования скорости. Для чего во В К отводится пять временных позиций для передачи информации - позиции РЗ-Р7, три позиции (РО-Р2) - для передачи кода согласования скорости (КСС). КСС показывает число передаваемых информационных бит. Если скорость передачи меньше 8 кбит/с, то во временном канале передается один информационный бит, если больше 8 кбит/с, то во временном канале передается несколько информационных бит.

Для скорости передачи Bi 9,6 кбит/с во временном канале передается от 1 до 2 бит. для 82 16 кбит/с - от 1 до 3 бит, для Вз 32 кбит/с - от 3 до 5 бит. Для скорости передачи В4 48 кбит/с и Bs 64 кбит/с в ИКМ-тракте занимается соответственно два временных канала, при этом емкость устройства уменьшается в два раза, т.е. п 16. В этом случае во временном канале для В4 48 кбит/с передается от 2 до 4 бит, для В 5 64 кбит/с от 3 до 5 бит.

Работа блоков предлагаемого устройства происходит в ритме ИКМ-тракта и кратна частоте 2048 кГц.

Для этого блок 3 синхронизации запитан цикловой частотой Рц 8 кГц и тактовой частотой fT 2048 кГц ИКМ-тракта, поступающими из задающего генератора (30 системы, Блок 3 вырабатывает синхросигналы (такты) и коды адресов. Частоты следования

0 тактов to.ti.t2 равны 2048 кГц. Во время положительного полупериода такта to тактом ti из блоков устройства производится считывание информации, во время отрицательного полупериода to тактом t2 производится

5 запись информации в блоки устройства.

Частота следования такта t3 равна 64 кГц, Он поступает в блок 9 для выработки сигнала, разрешающего переписывать информацию из блока 8 в пространственный

0 коммутатор 10.

Частота такта tj равна 4 кГц, такта ts 256 кГц. Такты t4 и ts поступают в блок 1. Такт ts используется для записи, информации из ИКМ-тракта в оперативную память блока 1,

5 такт т.4 - для переключения оперативной памяти блока 1.

Для записи информации из ИКМ-тракта а блок 1 используются адреса временных каналов тракта Aj2 и бит временного канала

0 Дез. Адреса Ai2 поступают в блок 2 с частотой следования 256 кГц. Адреса Рез поступают в блок 1 с частотой следования 2048 кГц.

Для чтения информации из блоков устройства используются адреса исходящих

5 линий Aj2 и информационных бит Абс. Адре- - са А)2 поступают во все блоки устройства (кроме блока 7) с частотой следования 2048 кГц. Адреса Абс поступают в блок 1 с частотой следования 64 кГц.

0 В блоке 1 осуществляется временная коммутация и преобразование информации уплотненных слов ИКМ в посимвольное уплотнение или преобразование из поблочного вида в побитный.

5 Временная коммутация производится путем записи информации приходящей из ИКМ-тракта, в блок 1 по адресу AJI из блока 2, а считывание информации из блока 1 производится по адресам Aja и Абс, поступаю0 щим из блока 3. Преобразование из поблочного вида в побитный производится путем побитной записи информации ВК в соответствующую зону памяти блока 1 за время одного ВК входного ИКМ-тракта, а

5 считывание бит информации из этой зоны производится равномерно в течение всего цикла ИКМ-тракта. Для исключения изменения порядка следования бит в исходящем информационном потоке по отношению к входному потоку память блока 1 делится на

две области. В течение одного цикла ИКМ- тракта производится запись информации в одну область памяти, а считывание - из другой области. Через цикл области памяти меняются местами. Каждая область памяти содержит 32 зоны по 8 ячеек в каждой. Каждая ячейка предназначена для хранения одного бита информации и сигнала сопровождения (СС) этого бита. Сигнал СС принимает единичное значение, если из входного ИКМ-тракта записывается в память информационный бит, и принимает нулевое значение, если из входного ИКМ-тракта записывается пустая посылка.

Для определения числа информационных бит, передаваемых по ИКМ-тракту, в каждом ВК выделены временные позиции РО-Р2, по которым передается КСС, в данном случае число значащих информационных бит ВК. Информационные биты передаются во временных позициях РЗ-Р7 каждого ВК. Причем, если ВК содержит пустые посылки, то они передаются после информационных бит в старших временных позициях. Например, при (кодООО)во временных позициях РЗ-Р7 передаются все пустые посылки, при КСС 1 (код 001) во временной позиции РЗ передается информационный бит, а в остальных позициях (Р4-Р7) передаются пустые посылки, при КСС 5 (код 101) на позициях РЗ-Р7 передаются информационные биты. Порядок следования информационных бит в пределах одного В К соответствует порядку поступления их от источника информации.

Устройство не имеет внутренних блокировок, поэтому число исходящих линий равно числу входящих линий, обслуживаемых ИКМ-трактом. В общем случае скорость передачи информации по линиям связи и коммутации асинхронны и не кратны. Поэтому на устройство подаются две частоты, одна из ЦКС для коммутации, другая из линейного оборудования (ЛО) для выдачи информации в исходящие линии. Сопряжение этих частот осуществляется в управляемом делителе частоты. Такое построение коммутационной системы обеспечивает ее модульное и линейное наращивание.

Каждое устройство обслуживает линии связи, имеющие одну определенную скорость передачи информации. Номинальное значение частоты, поступающей из ЛО, зависит от скорости передачи информации по линиям связи и допустимых краевых искаженных сигнала.

Для осуществления соединения временных каналов ИКМ-тракта или соответствующих им входящим линиям с исходящими линиями в устройстве осуществляется временная коммутация посредством записи адресов коммутируемых линий в блок 2. Устройство управления устанавливает соединение i ВК ИКМ-тракта, определяемое 5 адресом AI, с исходящей линией, определяемой адресом Aj, для чего выдает синхроимпульс (СИ) и адреса Ап и Ац. По СИ код адреса AJI записывается в i ячейку блока 2 по адресу Аи во время такта t2. После чего

0 коммутация считается установленной. Временную коммутацию в устройстве осуществляют блоки памяти информации 1, памяти адресов 2 и синхронизации 3. Управление работой временной коммутации осуществ5 ляется по входу. Информация, поступающая из ИКМ-тракта, записывается в ячейку памяти блока 1 в соответствии с адресами, хранящимися в блоке 2, а считывание производится последовательно ячейка за

0 ячейкой под управлением счетчика временных интервалов (исходящих) блока 3 синхронизации.

Блок 1 памяти информации осуществляет совместно с временной коммутацией

5 преобразование уплотненных слов ИКМ- тракта в посимвольное уплотнение, которое необходимо для равномерного заполнения эластичной памяти каждого канала в блоке 4. Поэтому блок 1 формирует двухпровод0 ный групповой тракт (ГТ). по которому передаются информационные биты и сигналы сопровождения СС. Для скоростей передачи до 32 кбит/с включительно цикл работы ГТ равен 64 кГц, количество ВК в цикле

5 равно 32, длительность В К равна периоду частоты 2048 кГц.

Для скорости передачи 48 и 64 кбит/с цикл работы ГТ равен 128 кГц, количество ВК в цикле равно 16, длительность ВК равна

0 периоду частоты 2048 кГц. Это достигается равномерным распределением информации от входящих линий в ИКМ-тракте и соответственно коммутируемых адресов в блоке 2. ИКМ-тракт симметричен Поэтому

5 информация от входящих линий должна располагаться зеркально. Например, пятая линия может записать 1 и 17 каналы, восьмая линия - 16 и 32 каналы и т.д. 16 входных линий обслуживает один ИКМ-тракт.

0 Запись информации в блок 1 из ИКМ- тракта осуществляется по адресам исходящих линий AJI, поступающих из блока 2, и бит записи АбЗ поступающих из блока 3. Адрес AJI определяет j ячейку оперативной

5 памяти блока 1, адрес Аез - номер бита В К. Запись производится последовательно. Информация, поступившая на позициях РО-Р2 ВК в блок 1 не записывается. Код КСС, поступающий на этих позициях, преобразуется в параллельный код. который

используется для выработки сигнала сопровождения СС путем сравнения кодов адресов АЫИ КСС. Если код , то сиг налу сопровождения присваивается значение 1, Путем выработки СС отмечаются значащие информационные биты ВК, которые передаются на позициях РЗ-Р7 ВК. Если ВК содержит пустые посылки, то они передаются на более старших позициях. При коде КСС 000 на позициях РЗ-Р7 нет значащих информационных бит. При коде КСС 001 на позиции РЗ передается информационный бит. на остальных позициях - пустые посылки и т.д. Значение СС и информации заносится параллельно в оперативную память.

Посимвольное уплотнение ГТ осуществляется путем последовательного считывания информации из блока 1 по адресам Aj2 и Абс блока 3. Адрес бита считывания Абс указывает номер считываемого бита, адрес Aj2 - номер исходящей линии, для которой считывается очередной бит информации.

Частота поступления адреса Абс равна 64 кГц, адреса Aj2 - 2048 кГц. Потому за первые четыре ВК ИКМ-тракта. определяемых адресом Ai2, считывается последовательно первый (нулевой) бит для 32 исходящих линий, за последующие четыре ВК - второй бит и т.д. За цикл ИКМ-тракта последовательно считывается 8 бит информации для каждой исходящей линии.

Для приема информации из ИКМ-тракта в блок 1 подаются такты to. следующие с частотой 2048 кГц, такты ts - для выработки сигнала СС, следующие с частотой 256 кГц. Чтение адреса AJI из блока 2 по адресу Aia блока 3 производится во время такта ti. Запись Aji по адресу Аи из УУ ЦКС производится во время такта t2. Запись информации из ИКМ-тракта в блок 1 по адресам AJI блока 2 и Абз блока 3 производится в такт t2. Считывание информации и СС из блока 1 по адресам Aj2 и Абс блока 3 производится в такт ti.

Работа эластичной памяти, а именно накопление и удаление фазовых флуктуации входных сигналов без ее переполнения, выдача информации в исходящие линии связи и согласование скорости выдачи со скоростью коммутации производится блоками следующим образом. Эластичная память для каждого канала ГТ расположена в блоке 4. обращение к эластичной памяти производится формирователями сигнала записи 5 и чтения 6, разуплотнение сигналов ГТ и временное согласование скорости коммутации и выдачи производится в блоке 11 передачи, формирование частот для выдачи информации в исходящие линии производится в управляемом делителе 9 частоты, подключение частот выдачи к исходящим линиям производится в пространственном коммутаторе 10. определение необходимой частоты выдачи из частот (РВн

V Рь- V РЬ+) для удаления накопленных фазовых флуктуации (дрожаний) из эластичной памяти производится путем сравнения адресов записи и чтения, вырабатываемых формирователями 5 и б соответственно в

0 блоке 7 рассогласования, хранение адресов частот выдачи производится в блоке 8 управления пространственным коммутатором, управление скоростью считывания информации из эластичной памяти блока 4

5 производится формирователем 12 путем выработки сигналов блокировки (СБ), при помощи которых вырабатываются адреса ячеек чтения эластичной памяти в формирователе 6. Для каждого канала ГТ и исходя0 щей линии в блоке 4 отводится зона памяти, соответственно в формирователях 5 и 6 отводятся ячейки памяти для обращения к этой зоне. В блоке 8 для каждой исходящей линии также отводится ячейка памяти для

5 хранения адреса частоты выдачи. Обращения к этим блокам производятся циклически по адресам Aj2 блока 3.

Запись информации из ГТ в блок 4 происходит следующим образом.

0В такт ti по коду Aj2 0 1...32) и m коду

Абс (m 1...8) из блока 1 считываются биты информации и СС, по j коду Aj2 из формирователя 5 считывается адрес Адз ячейки записи эластичной памяти блока 4. При наличии

5 сигнала СС 1 адрес Адз увеличивается на 1 (Аэз+1) и в такт т.2 по адресам Ag и (Адз+1) информация из ГТ записывается в эластичную память блока 4 и в ячейку формирователя 5 по адресу Aj2 записывается

0 последовательно, последняя ячейка сменяется первой первая - второй и т.д.

Считывание информации из эластичной памяти блока 4 и выдача ее в исходящие линии из блока 11 передачи происходит1 сле5 дующим образом.

Для согласования скорости коммутации и скорости выдачи информации в исходящие линии блок 11 передачи для каждой исходящей линии содержит два последова0 тельно соединенных триггера TI-J и Т2-|. В триггер TI-J информация записывается из эластичной памяти блока 4 на частоте коммутации. В j исходящую линию информация выдается из триггера TI-J.

5 Из эластичной памяти блока 4 информация считывается адресами Aj2 и Ago. поступающими из блоков 3 и 6 соответственно. Адрес Aj2 указывает номера j исходящей линии и j зоны памяти, адрес Адз - номер информационного бита зоны. Скоростью

30

считывания информации из эластичной памяти блока 4 управляет частота выдачи Fbj посредством выработки сигналов блокировок CBj и подачей их е формирователь 6 для формирования адресов ячеек чтения Аяч. 5 которыми опрашивается j эластичная память блока 4. Информация из блока 4 считывается циклически, последняя ячейка сменяется первой, первая, второй и т.д.

Выдача информации в исходящие ли- 10 нии в блоке 11 производится частотами выдачи Ff. Одновременно в формирователе 12 этими же частотами вырабатываются сигна- лы блокировок СВ для каждой исходящей линии. В момент выдачи информации в j 15 исходящую линию в формирователе 12 вырабатывается j сигнал блокировки СБ .

Опрос сигналов блокировок производится адресами Aj2 блока 3 циклически, синхронно с опросом остальных блоков 20 устройства. По j коду адреса из формирователя 6 считывается адрес ячейки чтения Аяч одновремено в формирователь 6 подается CBj. При СБ)1 адрес ячейки чтения увеличивается на 1 (Аяч+1), при СБ, 0 адрес 25 остается прежним. По новому адресу ячейки чтения из памяти блока 4 производится считывание информации и запись нового адреса чтения в формирователь 6.

При CBj 0 из блока 4 считывается прежний бит информации. При СБ 1 - последующий бит. Далее процесс повторяется. Сигналы блокировок из формирователя 12 в формирователе б поступают по ГТ. Длительность сигнала СБ равна длительности j адреса Aj2. Период коммутации или время цикла Aj2 меньше периода частоты выдачи Ffj. Поэтому, для однократного считывания нового бита информации из блока 4 эластичной памяти, триггер в формирователе 12 C5j в конце j временной позиции ГТ обнуляется. При последующих обращениях к j исходящей линии из блока 4 считывается прежний бит информации. Последующий бит информации считывается лишь при вы- 45 работке сигналом выдачи Fbj. После выдачи информации в исходящую линию в блок 12 записывается новый бит информации за цикл коммутации, который меньше периода частоты Fbj, т.е. к моменту выдачи 50 информации в исходящую линию следующего бита данный бит всегда будет записан.

Согласно алгоритму взаимодействия блоков устройства в такт ti из формирователя 6 для j исходящей линии, определяемой 55 ко дом адреса Aj2. считывает- ся АЯч, из формирователя 12 в формирователь 6 подается сигнал блокировки CSj. Если СБ)0, то адрес АЯЧ не изменяется, если СБ)1, то адрес Аяч увели35

40

0

5

0 5

0 5

5 0

5

чивается на 1. Адрес ячейки чтения из формирователя 6 подается в блок 4, из которого в этом же такте t:i производится считывание информационного бита и запись его по заднему фронту такта ti в блоке 11.

В такте t2 e формирователь 6 записывается значение адреса ячейки чтения и обнуляется СБ) в формирователе 12. Во время такта ti производится последовательное обращение к формирователю 6 и блоку 4.

Информация по линиям связи из устройства поступает в линейное оборудование. Скорость коммутации в устройстве и скорость передачи информации по линиям в общем случае не кратны. Поэтому для коммутации широкого набора скоростей линий связи и их развязки от скорости коммутации в устройстве предусмотрен отдельный вход чистоты f0 от задающего генератора (3 Г) Л О. Асинхронный стык между частотами ЗТ центра коммутации сообщений (ЦКС) и ЛО осуществляется в управляемом делителе 9 частоты, который формирует три частоты выдачи информации в исходящие линии - номинальную частоту выдачи FBM и частоты FB+, FB-, причем частота FeO-FBH; частотаРв FBH. Отличаются частоты FB+ и от F0n на величину максимальных допустимых краевых искажений сигнала д. Величина д обычно составляет д 2°/

Для формирования частот выдачи применяются отдельные делители частоты Номинальное значение частот F0 подаваемого из ЗГ ЛО определяется допустимой величи- 5 ной д.Дпя 62% частота f0 64- FBn. откуда

частота F6+ .частота FB fo. Дели- bo ob

тель частоты, формирующий номинальную частоту выдачи FBH. имеет коэффициент деления 64. делитель частоты, формирующий частоту выдачи FB+ , имеет коэффициент деления 63. Делитель частоты формирующий частоту выдачи Fe-. имеет коэффициент деления 65.

Коэффициент нестабильности кварцевых генераторов, запитывающих линии связи и устройство, не хуже Kj 10 5. Для устранения переполнения памяти блока 4 к каждой исходящей пинии подключают одну из трех частот выдачи. При этом изменяют частоту и соответственно скорость выдачи информации в исходящие линии, это изменением FB характеризуется краевыми искажениями сигнала d/де д 2 10.

Асинхронность между генераторами линий связи и устройства приводит к накопле- нию фазовых флуктуации в блоке 4 устройства. Скорость накопления зависит от нестабильности генераторов Kf. Так как

0

Kf, то путем подключения частот выач FB или FB- выбирают накопленные фаовые флуктуации и этим выравнивают корость записи и чтения без потери бита. Подключение частот выдачи к исходяим линиям производится через пространтвенный коммутатор 10, который имеет труктуру 32x32 без внутренних блокировок о встроенной памятью на установление содинения.

Для исключения фазовых искажений нформации, превышающих допустимые краевые искажения сигнала переключение частот выдачи FB в пространственном коммутаторе 10 производится в момент совпадения их передних фронтов, которыми информация переписывается и выдается в j исходящую линию в блоке 11. Для этого фиксируется момент их совпадения в управляемом делителе 9 частоты, вырабатывая сигнал . Этим сигналом коэффициенты его второго и третьего делителей устанавливаются равными 64, и вместо частот выдачи FD+ и FB- формируются номинальные частоты выдачи FBH.

Начало переустановления соединения в пространственном коммутаторе 10 начинается после совпадения сигнала и первого синхросигнала f3, вырабатываемого блоком 3. Для этого фиксируется момент их совпадения в управляемом делителе 9 частоты, вырабатывая сигнал разрешения записи в пространственный коммутатор 10 (ЗпПК 1). Время переустановления соединений определяется периодом синхросиг-, нала t3, который имеет частоту следования 64 кГц. За его период кодами адресов Aj2 блока 3, поступающих с частотой 2048 кГц, осуществляется переус-тановление соединений для всех 32 исходящих линий устройства,

Вторым синхросигналом fa сигналы tc и Зп ПК обнуляются, т.е. tc 0 и Зп ПК - 0. Переустановление соединений заканчивается. Коэффициенты деления второго и третьего делителей управляемого делителя 9 частоты становятся равными 63 и 65 и вновь вырабатываются частоты выдачи FD+ и FB соответственно. Далее процесс повторяется. На входы пространственного коммутатора 10, определяемых адресами 00 и 11, подключается частота FBH, на вход 01 подключается частота F8+, на вхсд 10 подключается частота FB-.

Для установления соединения а пространственном коммутаторе 10 I входной линии с j исходящей линией достаточно подать их адреса AI и AJ. При переустановлении соединений входные i адреса считываются из блока 8 адресами Aj2 в такт

fi. Каждому j адресу Aj2 соответствует i входной адрес. Далее в такт t2 i входная линиг связи соединяется с j выходной линией. Например, для 25 исходящей линии в

такт И из блока 8 считывается код адреса 11, в такт Т2 происходит подключение к 25-й выходной линии частоты выдачи FBH.

Сопряжение асинхросинных частот ЗГ ЛО и ЗГ ЦКС осуществляется в управляемом

делителе 9 частоты при выработке сигнала для разрешения переустановления соединений в пространственном коммутаторе, т.е. сигнала ЗпПК 1.

За время между двумя сигналами из

блока 4 частотой выдачи FBH считывается 64 бита информации, частотой А0+ 65 бит, частотой FB 63 бита. За это время набег фазы входного сигнала по отношению к частоте ЗК ЦКС при Кг составит тысячную дояю периода информационного бита.

Поэтому путем поочередного подключения частот выдачи к j исходящей линии связи устройства, подстраивают скорость считывания информации из блока 4, выравнивая ее со скоростью записи, и этим не допускают ее переполнения.

Путем увеличения коэффициентов деления можно на два порядка уменьшить краевые искажения сигнала, т.е. уменьшить д до

6 2 -10 , что увеличивает время удаления накопленных фазовых флуктуации и уменьшает фазовые флуктуации в системе.

Заполнение блока 4 анализируется в блоке 7 рассогласования по адресам ячеек

записи АЯЗ и чтения Аяч, вырабатываемых

формирователями 5 и 6 соответственно.

, Из-за асинхронности генераторов ЗГ

ЦКС и ЗГЛОскорости записи информации

в блок 4 и чтения из него не равны, что

приводит к накоплению информации или к накоплению фазовых флуктуации входного сигнала. Для устранения переполнения блок 7 путем сравнения кодов адресов записи АЯЗ и чтения Аяч вырабатывает коды адресов частот выдачи Рвн, FB-, FB+. направленных на устранение этого рассогласования.

Заполнение блока 4 разбито на пять областей. Номера областей определяются путем вычитания из кода АЯЗ кода Аяч. К I области заполнения блока 4 эластичной памяти относится область, когда число несчитанных бит информации равно или меньше двум ячейкам. К V области относится область, когда число несчитанных бит информации равно или больше (п-1) ячеек, где п - число ячеек в блоке 4 эластичной памяти. К III области относится область, когда число несчитанных бит информации равно половине зоны, т.е. -«- или -к ячейкам. К II

области относится область заполнения между I и III областями, к IV области относится область заполнения между III и V областями.

I область указывает об опустошении блока 4 эластичной памяти и о необходимости замедления считывания из нее путем подключения частоты выдачи FB- вместо FBH.

V область указывает о переполнении блока 4 и о необходимости ускорения считывания из нее путем подключения частоты выдачи FB+ вместо FBH.

Ill область указывает об оптимальном заполнении блока 4, частота считывания в этом случае должна подключаться равной номинальной величине FBH.

Во II и IV областях переключения частот не производится, I область кодируется сигналами управления (СУ)СУ1. 1, СУ2 0; III область-СУ 1, 1, СУ2 1; V область СУ1 О, СУ2 1; II и IV области-СУ1 0. СУ2 1. Коды сигналов управления соответствуют входным адресам пространственого коммутатора 10, в котором на вход, определяемый адресом 10, подключается частота FB, на вход, определяемый адресом 11 и 00, подключается частота РВн, на вход, определяемый адресом 01, подключается частота FBX.

Вход 00 пространственного коммутатора 10 задействован для первоначальной установки системы. II и IV области используются непосредственно как эластичная память.

При удалении накопленных фазовых флуктуации входного сигнала заполнение блока 4 эластичной памяти смещается либо из I области в HI,проходя через область II, при подключении частоты выдачи FB-; либо из области V в область III, проходя через область IV, при подключении частоты выдачи FB+. По достижении области III производится подключение номинальной частоты выдачи FBH и области II и IV начинают использоваться как эластичная память.

При этом, если скорость поступления информации из ИКМ-тракта в эластичную память выше скорости выдачи информации из нее, то заполнение эластичной памяти смещается из области 111 в область V, проходя через область IV. Если скорость выдачи информации выше скорости поступления, то заполнение эластичной памяти смещается из области III в область I, проходя через область И. Далее происходит подключение соответствующих частот выдачи к исходящим линиям , и процесс повторяется,

Подключение частот выдачи происходит следующим образом.

Для J исходящей линии во время J временной позиции, определяемой адресом Aj2, на блок 7 рассогласования в такт ti поступают адреса записи Аяз и чтения Аяч из

формирователей 5 и 6 соответственно. Блок 7 определяет область запоминания j эластичной памяти блока 4. В такт t2 в случае I, III или V областей заполнения происходит запись соответствующего кода адреса частоты выдачи в j ячейку блока 8. Управляемый делитель 9 частоты вырабатывает частоты выдачи FB, а после совпадения передних фронтов частот выдач подключает вместо частоты FB- частоту FBH, вместо частоты FB+

частоту Рвн.

Далее управляемый делитель 9 частоты вырабатывает сигнал ЗпПК, разрешающий производить переустановление соединений в пространственном коммутаторе 10. Длительность этого сигнала равна циклу работы адресов Aj2. В j временной канал, определяемый адресом Aj2, из j ячейки блока 8 в такт ti считывается 1 код адреса входной, линии связи, на которую подключена соответствующая частота выдачи, втактТ2 в пространственном коммутаторе осуществляется соединение I входной линии с j выходной линией коммутатора. После переустановления соединений вместо частот FBH вновь вырабатываются частоты FB- и FB+.

Формула изобретения

Устройство коммутации с эластичной

памятью, содержащее последовательно соединенные блок памяти адреса и блок памяти информации, информационный вход которого является информационным входом устройства, последовательно соединенные формирователь сигнала блокировки, вход которого объединен с первым входом блока передачи, и формирователь сигнала записи, управляемый делитель частоты и блок синхронизации, выходы которого соединены с входами синхронизации блока памяти информации, блока памяти адреса, управляемого делителя частоты, формирователей сигнала записи и чтения, формирователя сигнала блокировки

и блока передачи, отличающееся тем, что, с целью повышения достоверности коммутации путем уменьшения фазовых флуктуации, введены последовательно соединенные блок рассогласования, блок

управления пространственным коммутатором и пространственный коммутатор, выход которого подключен к входу формирователя сигнала блокировки, а также блок эластичной памяти, первый вход которого подключен к выходу формирователя сигнала записи

и обьединен с первым входом блока рассог- ласования второй вход которого соединен с выходом формирователя сигнала чтения и объединен с вторым входом блока эластичной памяти, третий вход которого объединен с входом формирователя сигнала записи и подключен к первому выходу блока памяти информации, второй выход которого соединен с четвертым входом блока эла

стичной памяти, соединены соответственно с вторым входом блока передачи и выходами блока синхронизации, соответствующие выходы которого подключены к входам синхронизации блока управления пространственным коммутатором и пространственного коммутатора, второй вход которого подключен к выходу управляемого делителя частоты.

| Устройство коммутации асинхронных цифровых сигналов | 1985 |

|

SU1241522A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-05-07—Публикация

1988-06-21—Подача