ственно с группой выходов коммутатора и с группой информационных входов выходного регистра, группа выходов которого соединена с группой выходов устройства, группа информационных входов входного регистра и выход блока контроля соединены соответственно с группой входов и выходом ошибки устройства, отличающ е е ся тем, что, с целью повьше,ния быстродействия, вторая группа входов схемы сравнения приоритетов и третья группа информационных входов регистра микрокоманд соединены с второй группой выходов блока магазинной памяти, вторая группа входов которого соединена с группой выходов дешифратора кода .операций входных выражений, вход сдвига вниз и вход сдвига вверх блока магазинной памяти соединены соответственно с выходом шестого элемента И группы и с выходом седьмого элемента И группы.

2. Устройство по П.1, о т л ичающееся тем, что блок магазинной памяти содержит первый, второй и третий коммутаторы, магазинную память хр-анения приоритетов лексических единиц и магазинную память хранения лексических единиц, группа выходов которой соединена с группой входов первого коммутатора, группа выходов которого соединена с первой группой выходов блока, управляющий вход первого коммутатора соединен с входом чтения блока, управляющие входы второго и третьего коммутатора соединены с входом записи блока, входы сдвига вниз и вверх блока соединены соответственно с входами сдвига вниз и вверх магазинной памяти хранения приоритетов лексических единиц и магазинной памяти хранения лексических единиц, группа входов которой соединена с группой выходов второго коммутатора, группа входов которого соединена с первой группой входов блока,- а вторая группа входов блока соединена .с .группой входов третьего коммутатора, группа выходов которого соединена с гр.уппой входов магазинной памяти хранения приоритетов лексических единиц, груп па выходов которой соединена с второй группой выходов блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для перевода выражений в польскую инверсную запись | 1980 |

|

SU890403A1 |

| Устройство для перевода выражений в польскую инверсную запись | 1981 |

|

SU991437A2 |

| Устройство для преобразования выражений в польскую инверсную запись | 1985 |

|

SU1290358A1 |

| Устройство для перевода выражений в польскую инверсную запись | 1988 |

|

SU1571616A1 |

| Параллельный синтаксический анализатор | 1987 |

|

SU1465894A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

1. УСТРОЙСТВО ДЛЯ ПЕРЕВОДА ВЫРАЖЕНИЙ В ПОЛЬСКУЮ ИНВЕРСНУЮ ЗАПИСЬ, содержащее входной регистр, дешифратор лексических единиц,, дешифратор кодов операций входньгх выражений, схему сравнения приоритетов, коммутатор, блок элементов ИПИ, выГходной регистр, блок магазинной памяти, блок контроля и блок микропрограммного упрагвления, состояпщй из регистра адреса микрокоманд, дешифратора адреса микрокоманд, блока памяти микрокоманд, счетчика, дешифратора адреса команд, элемента И, генератора тактовых импульсов, триггера и группы элементов И, первые входы элементов И группы соединены с выходом элемента И и со счетным входом счетчика группа информационных выходов которого соединена с группой входов дешифратора адреса команд, группа выходов которого соединена с группой адресных входов старших разрядов блока памяти микрокоманд, группа адресных входов младших разрядов которого соединена с группой выходов дешифратора адреса микрокоманд, группа входов которого соединена с группой выходов регистра адреса микрокоманд, первый и второй входы элемента И соединены соответст венно с выходом генератора тактовых импульсов и с выходом триггера, вход установки в О которого соединен с выходом первого элемента И группы, вторые входы элементов И группы соединены с информационными выходами блока памяти микрокоманд, выходы .второго, третьего, четвертого и пятого элементов И группы соединены соответственно с входом записи входного регистра, с управляющим входом коммутатора, с входом записи блока % магазинной памяти и с входом чтения блока магазинной памяти, первая СУ) группа информа1щонных входов регистра адреса микрокоманд соединена с группой выходов дешифратора лексических единиц и с труппой входов, блока контроля, вторая группа информационных входов регистра микрокоманд соединена с группой выходов схеОд мы сравнения приоритетов, вход устао новки в 1 триггера соединен с вхо00 М дом пуска устройства, первая группа входов схемы сравнения приоритетов ;о соединена с группой выходов дешифратора кодов операций входных выражений, первая группа входов блока магазинной памяти соединена с группами входов дешифратора лексических единиц, дешифратора кодов операций входных выражений и коммутатора, а также с группой выходов входного регистра, первая группа выходов блока магазинной памяти соединена с первой группой входов блока элементов ИПИ, вторая группа входов и группа выходов которого соединена соответ

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах обработки данных и производства программ для ЭВМ.

Известно устройство для перевода выражений в польскую инверсную запись. Оно может быть использовано в автоматизированных системах производства программ для ускорения процесса трансляции .

Недостатком его является отсутствие контроля наличия и порядка следования лексических единиц в исходном выражении.

Наиболее близким к изобретению техническим решением является устройство для перевода выражений в польскую инверсную запись, содержащее входной регистр, дешифратор лексических единиц, дешифратор кодов операций входных вьфажений, регистр кодов операций и депифратор кодов

операций магазинной памяти,/схему сравнения приоритетов, магазинную память, блок управления, блок контроля, выходной Регистр, четьще группы элементов И. и группу элементов ИЛИ, причем группа входов входного регистра является входом устройства, а .группа входов дешифратора лексических единиц, дешифратора кодов. операций выражений и элементов И первой и второй групп объединены и подключены к соответствующим выходам входного регистра; группа выходов дешифратора лексических единиц подключена к первой группе входов блока управления и группе входов блока контроля, выход которого является выходом сигнала ошибки; группа выходов дешифратора кодов операций выражений соединена с группой входов схемы сравнения приоритетовj выходы элементов И первой группы подключены соответственно к первым входам

группы элементов ИЛИ, вторые входы которых подключены к выходам соответствующих элементов И третьей группы, а выходы - к группе входов выходного регистра, группа выходов которого является выходом устройства; выходы элементов И второй группы подключены к группе входов магазинной памяти первая группа выходов которой подключена к первым входам соответствующих элементов И третьей группы, вторая группа выходов магазинной памяти под1 лючена к первым входам соответствующих элементов И четвертой группы, выходы которой подключены к группе соответствующих входов регистра кодов операций магазинной памяти, группа выходов которого подключена к группе соответствующих входов дешифратора кодов операций магазинной памяти, а группа его выходов - к второй группе входов, схемы сравнений приоритетов и к второй группе входов блока управления, выход схемы сравнения приоритетов соединен с третьей группой входов блока управления первьй, второй, третий, четвертьш, пятый, шестой и седьмой выходы блока управления подключены соответственно к входам Чтение и Запись магазинной памяти, к вторьм входам элементов И четвертой, второй, третьей и первой групп соответственно к зшравляющему входу входного регистра. .Блок управления содержит регист команд,счетчик команд, дешифратор, команд,.дешифратор микрокоманд, микропрограммную память, генератор импульсов, триггер, группу элементо И, элемент И, причем входы регистра являются соответственно первой, второй и. третьей группой входов блока управления, вход счетчика команд соединен с выходом элемента И, первый вход которого соединен с выходом генератора импульсов, а второй - с единичным выходом триггера, нулевой вход к.оторого соединен с выходом первого элемента И группы а единичный является входом Пуск блока управления, выходы регистра и счетчика команд соединены соответственно с входами дешифратора микро.команд и дешифратора команд, выходы которых соединены соответственно с адресными входами первой и второй групп микропрограммной памяти, информационные выходы которой соединены с первыми входами соответствуюш11х элементов И гpyппы вторые входы которых объединены и подключены к 5 выходу элемента И а выходы являются выходами блока управления с первого по седьмой. Блок контроля содержит реверсивный счетчик, первый, второй и третий элементы ИЛИ, первьш и вто0 рой элементы .И, элемент НЕ, дешифра-, тор состояния, элемент задержки, причем первьш и второй входы первого и второго элементов ИЛИ, первый вход первого элемента И и вход эле5 мента задержки соединены с соответстВ5ТОЩИМИ выходами дешифратора лексических единиц, выходы первого и второго элементов ИЛИ подключены соответ ственно к входам сложения и вычита0 ния реверсивного счетчика, установочный вход которого подключен к вы ходу элемента задержки и к входу элемента НЕ, а выход последнего подключен к входу синхронизации ревер5 сивного счетчика и ко второму входу первого элемента И, третий вход которого подключен к вьпсоду дешифратора состояний, выходы первого и второго элементов И подключены соотзетствен0 но к первому и второму входам третьего элемента ИЛИ, выход которого является выходом Ошибка устройства, входы второго элемента И подключены к соответствуюпщм выходам реверсив-

5 ного счетчика, входы дешифратора состояний подключены к соответствуюшрим инверсным выходам реверсивного счетчика 2 J.Недостатком устройства является

0 сложность и избыточность его схемы, что в конечном счете снижает быстродействие устройства.

Цель изобретения - повышение быстродействия устройства.

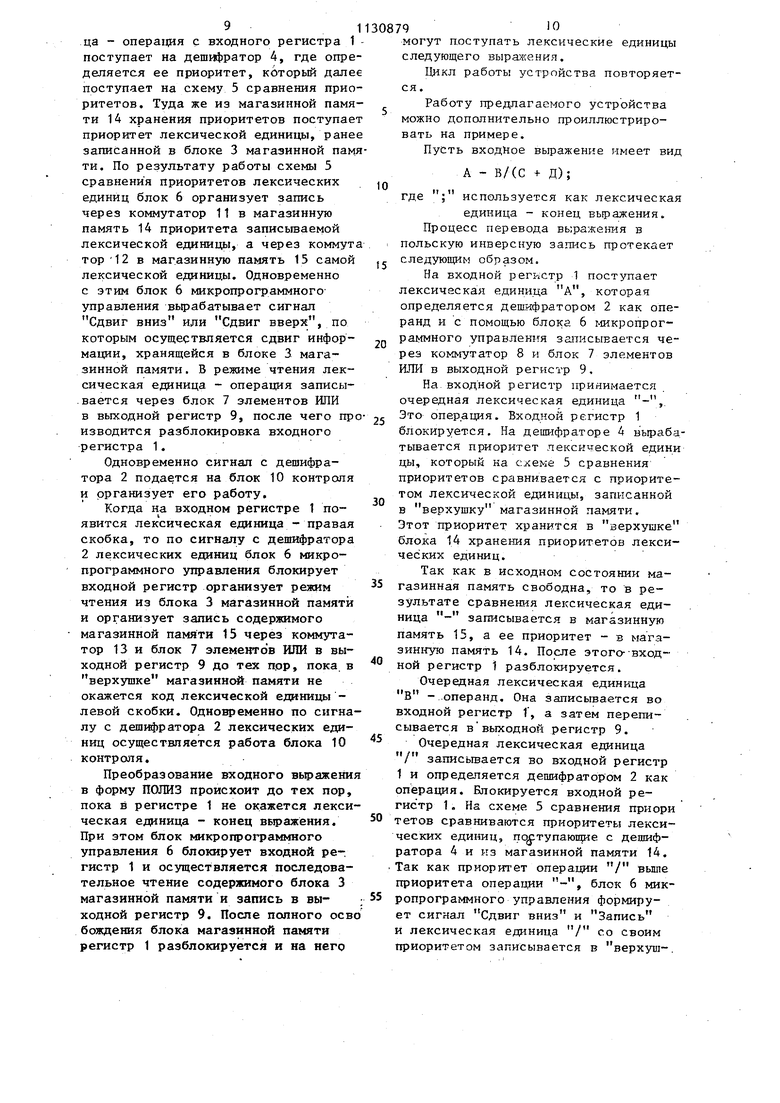

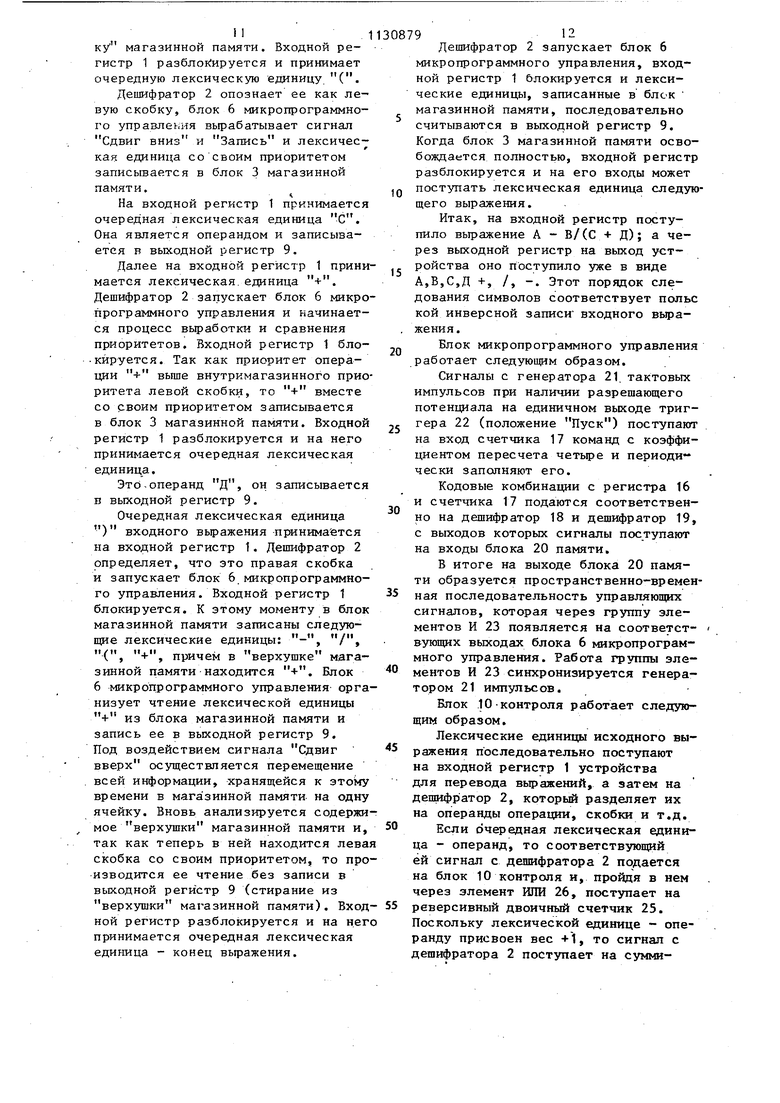

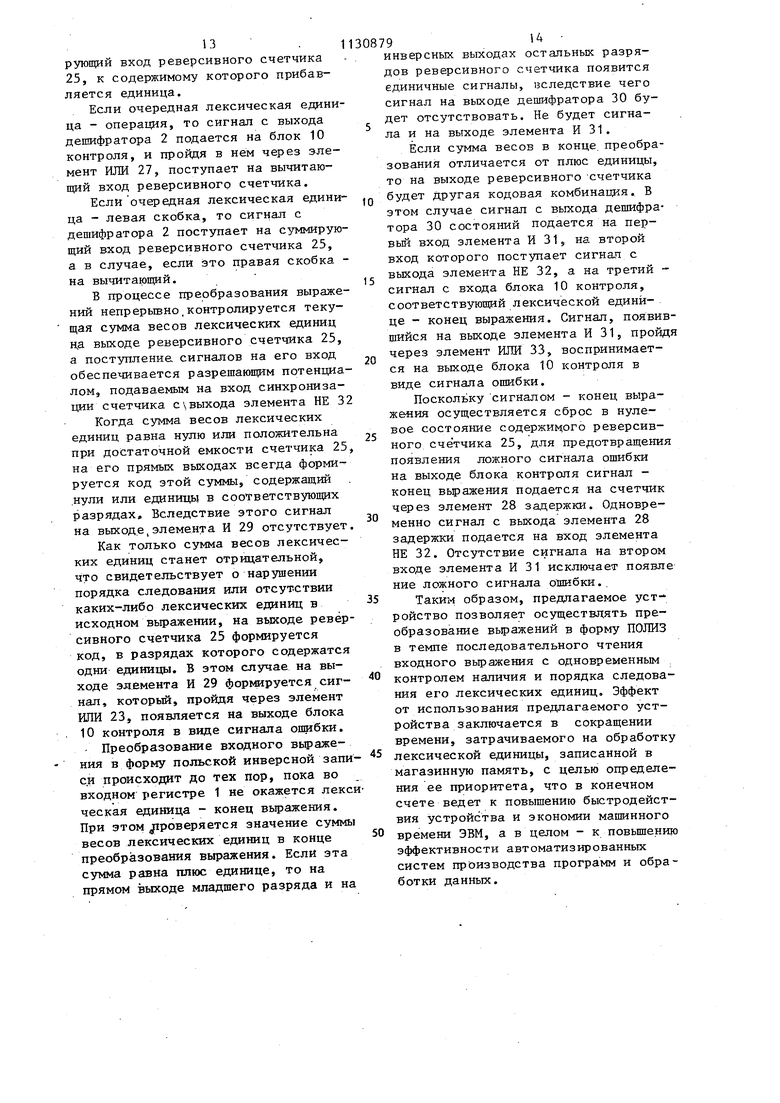

5 Поставленная цель достигается тем, что в устройство дпя перевода выражений в польскую инверсную запись, содержащее входной регистр, дешифратор лексических единиц, дешифратор

0 кодов операций входных выражений,

схему сравнения приоритетов, коммутатор, блок элементов ИПИ, выходной регистр, блок магазинной памяти, блок контроля и блок микропрограммно

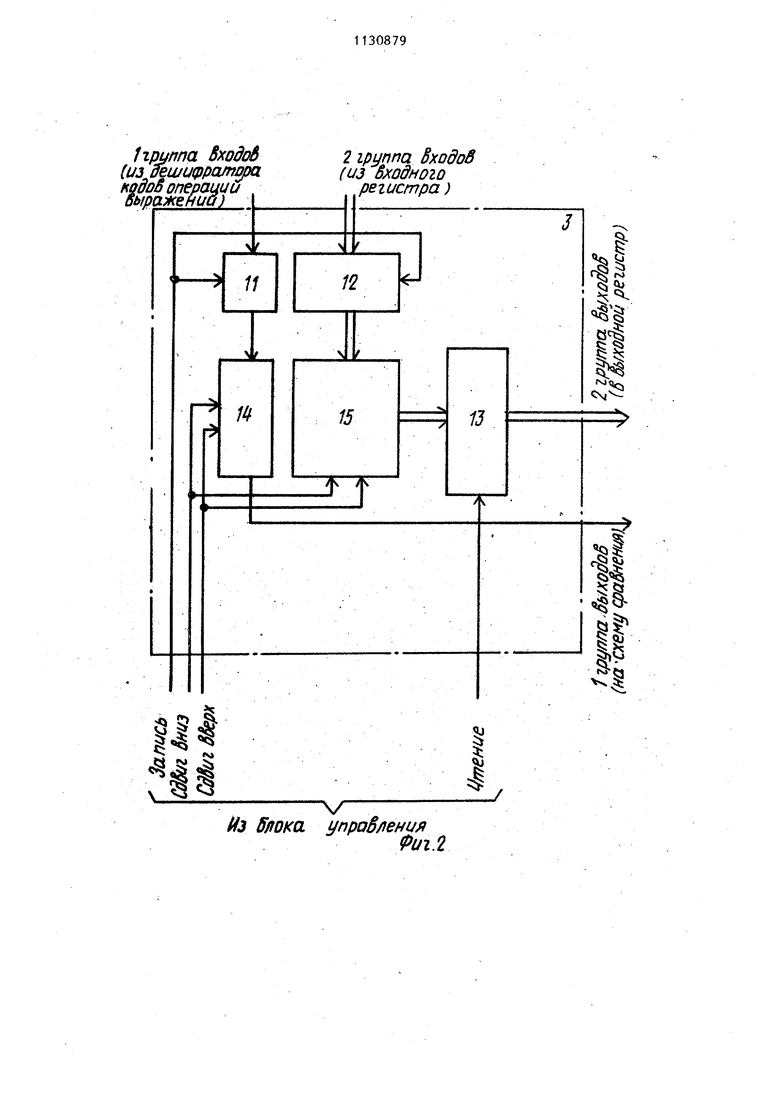

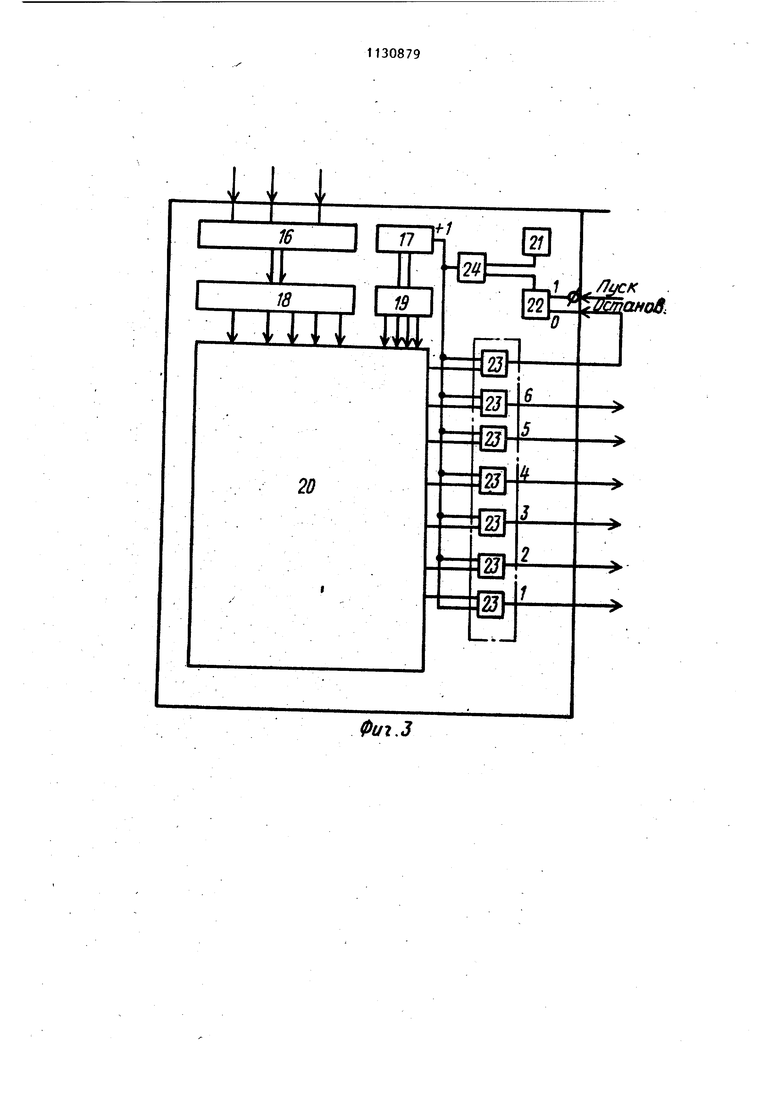

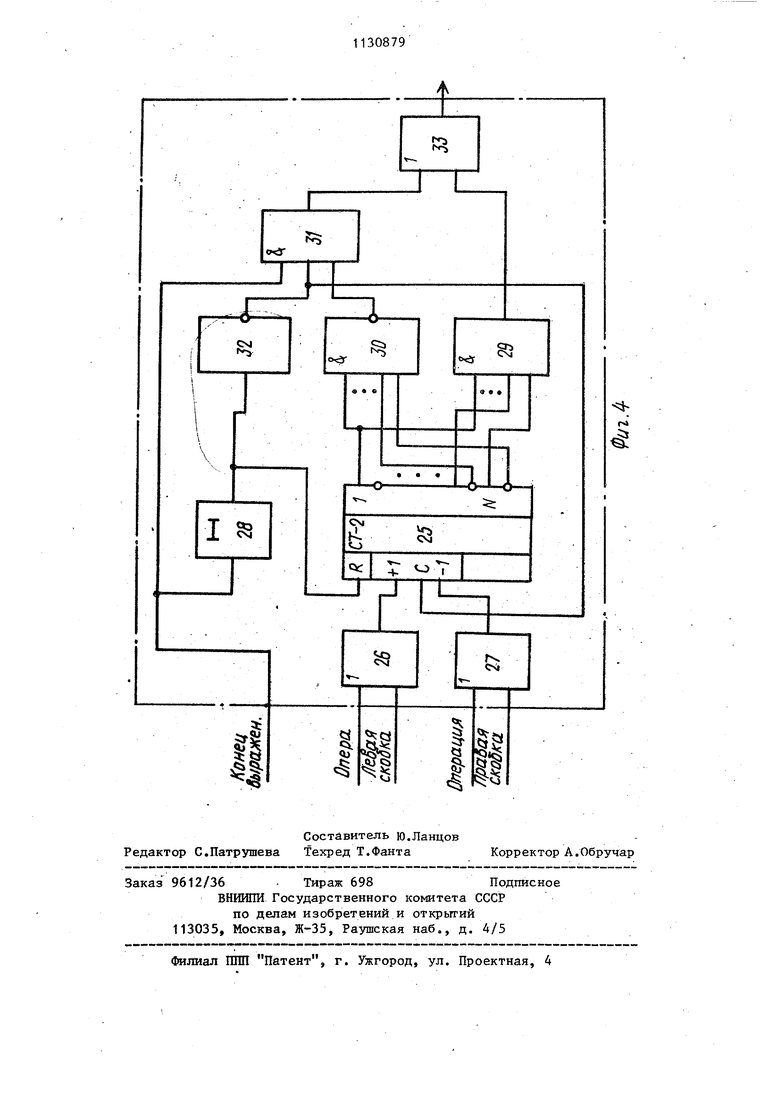

5 го управления, состоягщй из регистра адреса микрокоманд, дешифратора адреса микрокоманд, блока памяти микрокоманд, счетчика, дешифратора адреса команд, элемента И, генерато ра тактовых импулъсов, триггера и группы элементов И, первые входы элементов И группы соединены с выхо дом элемента И и со счетным входом счетчика, группа информационных выходов которого соединена с группой вхбдов дешифратора адреса команд, группа выходов которого соединена с группой адресных входов старших разрядов блока памяти микрокоманд, группа адресных входов младших разрядов которого соединена с группой выходов дешифратора адреса микрокоманд, группа входов которого соединена с группой выходов регистра адреса микрокоманд, первый и второй входы элемента И соединены соответственно с выходом генератора тактовых импульсов и с выходом триггера, вход установки в О которого соеди нен с выходом первого элемента И группы, вторые входы элементов И группы соединены с информационными выходами блока памяти микрокоманд, выходы второго третьего, четвертого и пятого элементов И группы соедине ны соответственно с входом записи входного регистра, с управляющим входом коммутатора, с входом записи блока магазинной памяти и с входом чтения блока магазинной памяти, пер вая группа информационных входов ре гистра адреса микрокоманд соединена с группой выходов дешифратора лексических единиц и с группой входов блока контроля, вторая группа инфор мационных входов регистра микрокоманд соединена с группой выходов схемы сравнения приоритетов, вход установки в 1 триггера, соединен с входом пуска устройства, первая группа входов схемы сравнения приоритетов соединена с группой выходов дешифратора кодов операций входных выражений, первая группа входов блока магазинной памяти соед нена с группами входов дешифратора лексических единиц, дешифратора кодов операций входных выражений и коммутатора, а также с группой выхо дов входного регистра, первая групп выходов блока магазинной памяти соединена с первой группой входов бло ка элементов ИЛИ, вторая группа вхо дов и группа выходов которого соеди нена соответственно с группой выход коммутатора и с группой информацкон ных входов выходного регистра, груп па выходов которого соединена с группой выходов устройства, группа информационных входов входного регистра и выход блока контроля соединены соответственно с группой входов и выходом ошибки устройства, введены вторая группа входов схемы сравнения приоритетов и третья группа информационных входов регистра микрокоманд соединены с второй группой выходов блока магазинной памяти-, первая группа входов которого соединена с 1Т)уппой выходов дешифратора кода операций входных вьфажений, вход сдвига вниз и вход сдвига вверх блока магазинной памяти соединены соответственно с выходом шестого элемента И группы и с выходом седьмого элемента И группы. Кроме того, блок магазинной памяти, содержит первый, второй и третий коммутаторы, магазинную память хранения приоритетов лексических единиц и магазинную память хранения лексических единиц, группа выходов которой соединена с группой входов первого коммутатора, группа выходов которого соединена с второй группой выходов блока, управляющий вход первого коммутатора соединен с входом чтения блока, управляющие входы второго и третьего коммутатора соединены с входом записи блока, входы сдвига вниз и вверх блока соединены соответственно с входами сдвига вниз и вверх магазинной памяти хранения приоритетов лексических единиц и магазинной памяти хранения лексических единиц, группа входов которой соединена с группой выходов второго коммутатора, группа входов которого соединена с первой группой входов блока, а вторая группа входов блока соединена с группой входов третьего коммутатора, группа выходов которого соединена с группой входов магазинной памяти хранения приоритетов лексических единиц, группа выходов которой соединена с первой группой выходов блока. , На фиг. 1 представлена структурная схема устройствам на фиг. 2 структурная схема блока магазинной памяти; на фиг. 3 - структурная схема блока микропрограммного управления; на фиг. 4 - структурная схема блока контроля. Устройство содержит входной регистр 1, дешифратор 2 лексических единиц, блок 3 магазинной памяти, дешифратор 4 кодов операций входных выражений, схему 5 срабнения приоритетов, блок 6 микропрограммного управления, блок 7 элементов ИЛИ, коммутатор 8, выходной регистр 9j блок 10 контроля. В состав блока магазинной памяти входят третий 11, второй 12 и .первы 13коммутаторы, магазинная память 14хранения приоритетов лексических единиц и магазинная память 15 хранения лексических единиц. В состав блока микропрограгмногр управления входят регистр 16 адреса микрокоманд, счетчик 17, дешифра тор 18 адреса микрокоманд, дешифратор 19.адреса команд,блок 20 памяти микрокоманд, генератор 21 тактовых импульсов, триггер 22, группа элементов И 23 и элемент И 24. Блок 10 контроля содержит реверсивный счетчик 25, первый 26 и второй 27 элементы ИЛИ, элемент 28 задержки, первьй .элемент И 29, дешифр тор 30, второй элемент И 31, элемен НЕ 32 и третий элемент ИЛИ 33. Входной регистр 1 используется для хранения очередной лексической единицы исходного вьражения, дешифратор 2 лексических единиц разделяет лексические единицы на операнды, операции, скобки и т.д. Блок ;3 магазинной памяти - это память с посл дoвateльньiм безадресным принципом записи и чтения. Дешифратор 4 кодов операций входных вьражений совместн со схемой 5 сравнения приоритетов и блоком магазинной памяти реализую ют логическую функцию выработки,и сравнения приоритетов ) y443bV94y7V2 J44 4 2XiVy 4342 2 У4Ч2ЧДз ЛЧ4ЧзЧ1 2 ЛУ,ЧэЧ2Х,У 43y2V2V.,. . Блок 6 микропрограммного управле ния организует взаимодействие всех элементов устройства и представляет собой типовую схему, микропрограммно го управления. Блок 7 элементов ИЛИ и коммутатор 8 управляют передачами лексических единиц, а выходной регистр 9 предназначен для хранения очередной лексической: единицы в фор ме ПОЛИЗ. Блок 10 контроля проверяе наличие и порядок следования лексических единиц в исходном вьфажении Коммутатор 11 блока магазинной памяти обеспечивает поступление приоритетов лексических единиц в магазинную память 14, а коммутатор 12 обеспечивает поступление лексических единиц в магазинную память 15 Коммутатор 13 блока магазинной памяти обеспечивает поступление лексических единиц из магазинной памяти в выходной регистр. Устройство работает следующим образом. Лексические единицы исходного выражения последовательно поступают на входной регистр 1, а затем на дешифратор 2 и 4, причем первый разделяет их на операнды, операции и скобки. Если очередная лексическая единица - левая скобка., то дешифратор 2 запускает блок 6 микропрограммного управления, управлякнций сигнал которого разрешает запись этой единицы через коммутатор 12 из входного регистра 1 в магазинную память 15 хранения лексических единиц блока 3 магазинной памяти. Этот же управляюший сигнал разрешает запись приоритета указанной лексической единицы через коммутатор 11 с выхода дешифратора кодов операций 4 в магазинную память 14 хранения приоритетов лексических единиц. Одновременно сигнал с дешифратора 2 подается на блок 10 контроля, где фиксируется наличие и порядок следования лексической единицы. Если очерёдная лексическая единица - операнд, то дешифратор 2 запускает блок 6 микропрограммного управления, управляющий сигнал которого разрешает через коммутатор 8 и блок 7 элементов ИЛИ перепись кода операнда из входного регистра 1 на выходной регистр 9. Одновременно сигнал с деш14)ратора 2 подается на блок 10 контроля, где снова фиксируется наличие и порядок следования этой лексической единицы. Если очередная лексическая единица - операция, то сигнал с выхода дешифратора 2 лексических единиц запускает блок 6 микропрограммного управления, а в блоках 4 и 5 с участием магазинной памяти 14 начинается процесс выработки и сравнения приоритетов. Блок 6 блокирует запись очередной лексической единицы на входной регистр 1. Лексическая едини9ца - операизия с входного регистра 1 поступает на дешифратор 4, где опре деляется ее приоритет, который дале поступает на схему 5 сравнения прио ритетов. Туда же из магазинной памя ти 14 хранения приоритетов поступае приоритет лексической единицы, ране записанной в блоке 3 магазинной пам ти. По результату работы схемы 5 сравнения приоритетов лексических единиц блок 6 организует запись через коммутатор 11 в магазинную память 14 приоритета записьгааемой лексической единицы, а через коммут тор 12 в магазинную память 15 самой лексической единицы. Одновременно с этим блок 6 микропрограммного управления вырабатывает сигнал Сдвиг вниз или Сдвиг вверх, по которым осуществляется сдвиг информации, хранящейся в блоке 3 магазинной памяти, В режиме чтения лексическая единица - операция записы.вается через блок 7 элементов ИЛИ в выходной регистр 9, после чего пр изводится разблокировка входного регистра 1. Одновременно сигнал с дешифратора 2 подается на блок 10 контроля и организует его работу, Когда на входном регистре 1 появится лексическая единица - правая скобка, то по сигналу с дешифратора 2 лексических единиц блок 6 микропрограммного управления блокирует входной регистр организует режим чтения из блока 3 магазинной памяти и организует запись содержимого магазинной памяти 15 через коммутатор 13 и блок 7 элементов ИЛИ в выходной регистр 9 до тех п.ор, пока в верхушке магазинной памяти не окажется код лексической единицылевой скобки. Одновременно по сигна лу с дешифратора 2 лексических единиц осуществляется работа блока 10 контроля. Преобразование входного выражени в форму ПОЛИЗ происхоит до тех пор, пока в регистре 1 не окажется лекси ческая единица - конец вБфажения. При этом блок микропрограммного управления 6 блокирует входной регистр 1 и осуществляется последовательное чтение содержимого блока 3 магазинной памяти и запись в выходной регистр 9. После полного осв бождения блока магазинной памяти регистр 1 разблокируется и на него 910 могут поступать лексические единицы следующего выралсенкя. 11икл работы устройства повторяется. Работу предлагаемого устройства можно дополнительно проиллюстрировать на примере. Пусть входное выражение имеет вид А - В/(С + Д); где ; используется как лексическая единица - конец вь ражения. Процесс перевода выражения в польскую инверсную запись протекает cлeдyющи 5 образом. На входной регистр 1 поступает лексическая единица А, которая определяется дешифратором 2 как операнд и с помощью блока 6 микропрограммного управления записывается через коммутатор 8 и блок 7 элементов ИЛИ в выходной регистр 9, На.входной регистр принимается очередная лексическая единица -,. Это операция. Входной регистр 1 блокируется. На дешифраторе 4 вырггбатывается приоритет лексической едини цы, который на схеме 5 сравнения приоритетов сравнивается с приоритетом лексической единицы, записанной В верхушку магазинной памяти. Этот приоритет хранится в верхушке блока 14 хранения приоритетов лексических единиц. Так как в исходном состоянии магазинная память свободна, то в результате сравнения лексическая единица - записывается в магазинную память 15, а ее приоритет - в магаЗИН1-ГУЮ память 14. После этого--входной регистр 1 разблокируется. Очередная лексическая единица В - -операнд. Она записывается во входной регистр 1, а затем переписывается ввыходной регистр 9. Очередная лексическая единица / записьгоается во входной регистр 1 и определяется дешифратором 2 как операция. Блокируется входной регистр 1. На схеме 5 сравнения приори тетов сравниваются приоритеты лексических единиц, по тупаю11;ие с дешифратора 4 и из магазинной памяти 14. Так как приоритет операции / вьш1е приоритета операши -, блок 6 микропрограммного управления формирует сигнал Сдвиг вниз и Запись и лексическая единица / со своим приоритетом записывается в верхуш-. ку магазинной памяти. Входной регистр 1 разблок ируется и принимает очередную лексическую единицу (. Дешифратор 2 опознает ее как левую скобку, блок 6 микропрограммного управления вьфабатывает сигнал Сдвиг вниз и Запись и лексическая. единица со своим приоритетом записывается в блок 3 магазинной памяти. На входной регистр 1 принимается очередная лексическая единица Она является операндом и записывается в выходной регистр 9. Далее на входной регистр 1 прини мается лексическая, единица +. Дешифратор 2 запускает блок 6 микро программного управления и начинается процесс выработки и сравнения приоритетов. Входной регистр 1 блокйруется. Так как приоритет операции + выше внутримагазинного прио ритета левой скобки, то + вместе со своим приоритетом записывается в блок 3 магазинной памяти. Входной регистр 1 разблокируется и на него принимается очередная лексическая единица. Это-операнд Д, он записывается в выходной регистр 9. Очередная лексическая единица ) входного выражения пщнимается на входной регистр 1. Дешифратор 2 определяет, что это правая скобка и запускает блок 6 микропрограммного управления. Входной регистр 1 блокируется. К этому моменту в блок магазинной памяти записаны следующие лексические единицы: -, /, (, +, причем в верхушке магазинной памяти находится +, Блок 6 микропрограммного управления орга низует чтение лексической единицы + из блока магазинной памяти и запись ее в выходной регистр 9. Под воздействием сигнала Сдвиг вверх осуществляется перемещение всей информации, хранящейся к этому времени в магазинной памяти на одну ячейку. Вновь анализируется содержи мое верхушки магазинной памяти и так как теперь в ней находится лев скобка со своим приоритетом, то пр изводится ее чтение без записи в выходной регистр 9 (стирание из верхушки магазинной памяти). Вход ной регистр разблокируется и на не принимается очередная лексическая единица - конец выражения. Дешифратор 2 запускает блок 6 микропрограммного управления, входной регистр 1 блокируется и лексические единицы, записанные в блок магазинной памяти, последовательно считываются в выходной регистр 9. Когда блок 3 магазинной памяти освобождается полностью, входной регистр разблокируется и на его входы может поступать лексическая единица следующего выражения. Итак, на входной регистр поступило вьфажение А - В/(С + Д); а через выходной регистр на выход устройства оно поступило уже в виде А,В,С,Д +, /, -. Этот порядок следования символов соответствует польс кой инверсной записи входного выражения. Блок микропрограммного управления работает следующим образом. Сигналы с генератора 21 тактовых импульсов при наливши разрешающего потенциала на единичном выходе триггера 22 (положение Пуск) поступают на вход счетчика 17 команд с коэффициентом пересчета четыре и периоди чески заполняют его. Кодовые комбинации с регистра 16 и счетчика 17 подаются соответственно на дешифратор 18 и дешифратор 19, с выходов которых сигналы поступают на входы блока 20 памяти. В итоге на выходе блока 20 памяти образуется пространственно-временная последовательность управляющих сигналов, которая через группу элементов И 23 появляется на соответствующих выходах блока 6 микропрограммного управления. Работа группы элементов И 23 синхронизируется генератором 21 импульсов. Блок 10-контроля работает следующим образом. Лексические единицы исходного выражения последовательно поступают на входной регистр 1 устройства для перевода выражений, а затем на депшфратор 2, который разделяет их на операнды операции, скобки и т.д. Если очередная лексическая единица - операнд, то соответствующий ей сигнал с дешифратора 2 подается на блок 10 контроля и, пройдя в нем через элемент ИЛИ 26, поступает на реверсивный двоичный счетчик 25. Поскольку лексической единице - операнду присвоен вес +1, то сигнал с дешифратора 2 поступает на сумми13 , рующий вход реверсивного счетчика 25, к содержимому которого прибавляется единица.

Если очередная лексическая единица - операция, то сигнал с выхода дешифратора 2 подается на блок 10 контроля, и пройдя в нем через элемент ИЛИ 27, поступает на вычитающий вход реверсивного счетчика.

Еслиочередная лексическая единица - левая скобка, то сигнал с дешифратора 2 поступает на суммирующий вход реверсивного счетчика 25, а в случае, если это правая скобка на вычитающий.

В процессе преобразования выражений непрерьшно,контролируется текущая сумма весов лексических единиц н,а выходе реверсивного счетчика 25, а поступление сигналов на его вход обеспечивается разрешающим потенциалом, подаваемым на вход синхронизации счетчика с выхода элемента НЕ 32

Когда сумма весов лексических единиц равна нулю или положительна при достаточной емкости счетчика 25 на его прямых выходах всегда формируется код этой суммы, содержащий нули или единиць в соответствующих разрядах. Вследствие этого сигнал на выходе,элемента И 29 отсутствует

Как только сумма весов лексических единиц станет отрицательной, что свидетельствует о нарушении порядка следования или отсутствии каких-либо лексических единиц в исходном выражении, на выходе реверсивного счетчика 25 формируется код, в разрядах которого содержатся одни единицы. В этом случае на выходе элемента И 29 формируется сигнал, который, пройдя через элемент ИЛИ 23, появляется на выходе блока 10 контроля в виде сигнала опшбки.

Преобразование входного вьфажения в форму польской инверсной записи происходит до тех пор, пока во входном регистре 1 не окажется лекси ческая единица - конец выражения. При этом (роверяется значение суммы весов лексических единиц в конце преобразования вьфажения. Если эта сумма равна плюс единице, то на прямом выходе младшего разряда и на

08791

инверсных выходах остальных разрядов реверсивного счетчика появится единичные сигналы, вследствие чего сигнал на выходе дешифратора 30 будет отсутствовать. Не будет сигнала и на выходе элемента И 31.

Если сумма весов в конце, преобразования отличается от плюс единицы, то на выходе реверсивного счетчика

Q будет другая кодовая комбинация. В этом случае сигнал с выхода дешифратора 30 состояний подается на первьй вход элемента И 31, на второй вход которого поступает сигнап с выхода элемента НЕ 32, а на третий сигнал с входа блока 10 контроля, соответствующий лексической единице - конец выражения. Сигнал, появившийся на выходе элемента И 31, пройдя через элемент ИЛИ 33, воспринимается на выходе блока 10 контроля в виде сигнала ошибки.

Поскольку сигналом - конец выражения осуществляется сброс в нуле-

вое состояние содержим.ого реверсивного счетчика 25, для предотвращения появления ложного сигнала ошибки на выходе блока контроля сигнал конец вьражения подается на счетчик через элемент 28 задержки. Одновременно сигнал с выхода элемента 28 задержки подается на вход элемента НЕ 32. Отсутствие сигнала на втором входе элемента И 31 исключает появле ние ложного сигнала ошибки.,

5 Таким образом, предлагаемое устройство позволяет осуществлять преобразование выражений в форму ПОЛИЗ в темпе последовательного чтения входного вьфажения с одновременным

О контролем наличия и порядка следования его лексических единиц. Эффект от использования предлагаемого устройства заключается в сокращении времени, затрачиваемого на обработку

5 лексической единицы, записанной в магазинную память, с целью определения ее приоритета, что в конечном счете ведет к повышению быстродействия устройства и экономии машинного

0 времени ЭВМ, а в целом - к повьш1ению эффективности автоматизированных систем производства программ и обработки данных.

2 группа Входов (из Входного

л/

/О SflOKCL управление

иг2

f

16

Я

18

LJffl

V V

20

UOi

Л

Фиг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для перевода выражений в польскую инверсную запись | 1980 |

|

SU890403A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство | |||

| СССР по заявке № 3317931/18-24 (прототип). | |||

Авторы

Даты

1984-12-23—Публикация

1982-07-15—Подача