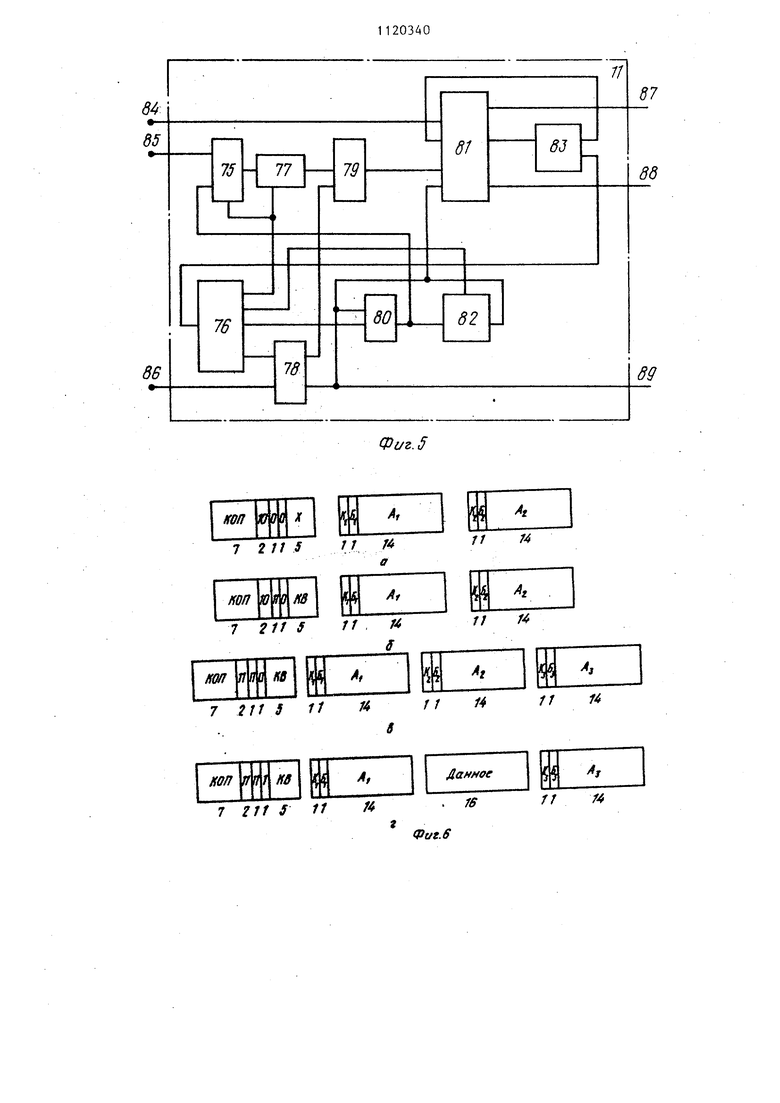

готовности, мультиплексор, счетчик циклов группу элементов задержки регистр команд и узел микропрограммн го Управления, вход разрешения считы вания, адресный вход, вход команд, вход признаков, выход прерывания, адресный выход и выход признака которого подключены соответственно к в ходам элементов задержки группы, вто рому выходу первого блока памяти микропрограмм, выходу регистра команд, выходу мультиплексора, первому входу приоритетного шифратора, адресному входу первого блока памяти микропрограмм и синх{)овходу регистра признаков операции, вход данных, синхровход и выход регистра признаков запросов соединены соответственно с выходом признаков запросов устройства микропрограммного управления, выходом первого дешифратора микроопераций и первыми входами элементов И группы, вторые входы и выходы которых подключены соответственно к выходу первого дешифратора микроопераций и входам триггеро готовности группы, выходы которых соединены с входами элементов задерж ки группы, вход регистра команд подключен к выходу второго блока буферных регистров, входы первого, вто рого, третьего и четвертого дешифраторов микроопераций соединены с вторым выходом первого блока памяти мик ропрограмм, вход и выход счетчика длины вектора подключены соответственно к выходу первого блока буферны регистров и первому входу разреше.ния регистра признаков операции вход данных, второй вход разрешения и выход которого соединены соответст венно с выходом признаков операции векторного арифметико-логического устройства, выходом первого дешифра™ тора микроопераций и входом первого блока буферных регистров, выход второго дешифратора микроопераций подключен к входу счетчика циклов, второй и третий входы и выход приоритетного шифратора соединены соответственно с выходом счетчика длины вектора, выходом третьего дешифра тора микроопераций и входом запроса данных устройства микропрограммного управления, а управляющий вход, первый, второй и третий входы данных мультиплексора подключены соответственно, к выходу четвертого дешифратора микроопераций, выходу признако 40 векторного арифметико-лдгического устройства, выходу регистра признаков операции и выходу счетчика циклов, вход микроопераций, вход данных и выход скалярного арифметико-логического устройства соединены соответственно с вторым выходом второго блока памяти микропрограмм, выходом и входом второго блока буферных ре-гистров, причем блок ускоренной обработки прерываний включает коммутатор, дешифратор микроопераций, регистр признаков, группу системных регистров, мультиплексор, узел сверхоперативной памяти, узел микропрограммного управления, сумматор и узел постоянной памяти, адресный вход, первый и второй выходы которого подключены соответственно к адресному выходу и адресному входу узла микропрограммного управления и входу дешифратора микроопераций, первый, второй, третий и четвертые выходы которого соединены соответственно с синхровходом регистра признаков, входом кода операции сумматора, управляющим входом узла сверхоперативной памяти и синхровходом системных регистров группы, входы данных, первые и вторые выходы которых подключены соответственно к выходу третьего блока буферных регистров, первому входу мультиплексора и входу третьего блока буферных регистров, управляющий вход, первый и второй входы данных и выход коммутатора соединены соответственно с первым выходом дешифратора микроопераций, выходом состояния устройства микропрограммного управления, выходом узла сверхоперативной памяти и входом данных регистра признаков, выход которого подключен к второму входу мультиплексора, вход данных и выход сумматора соединены соответственно с выходом узла сверхоперативной памяти и входом признаков узла микропрограммного управления, а вход разрешения считьгаания, вход команд, вход признаков, выход прерывания и выход признаков узла микропрограммного управления подключены соответственно к выходу текущего прерывания блока приоритетных прерываний, выходу мультиплексора, вторым выходам системных регистров группы, входу опроса прерывания блока приоритетных прерываний и входу переключения задач устройства микропрограммного управления.

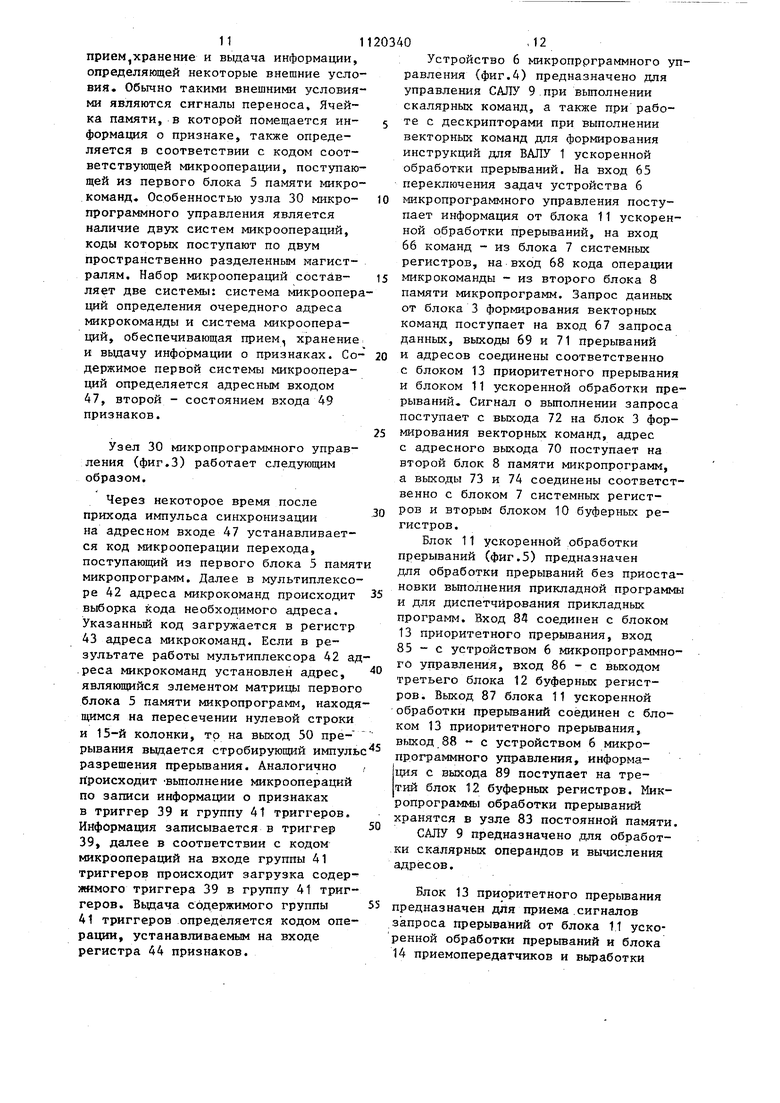

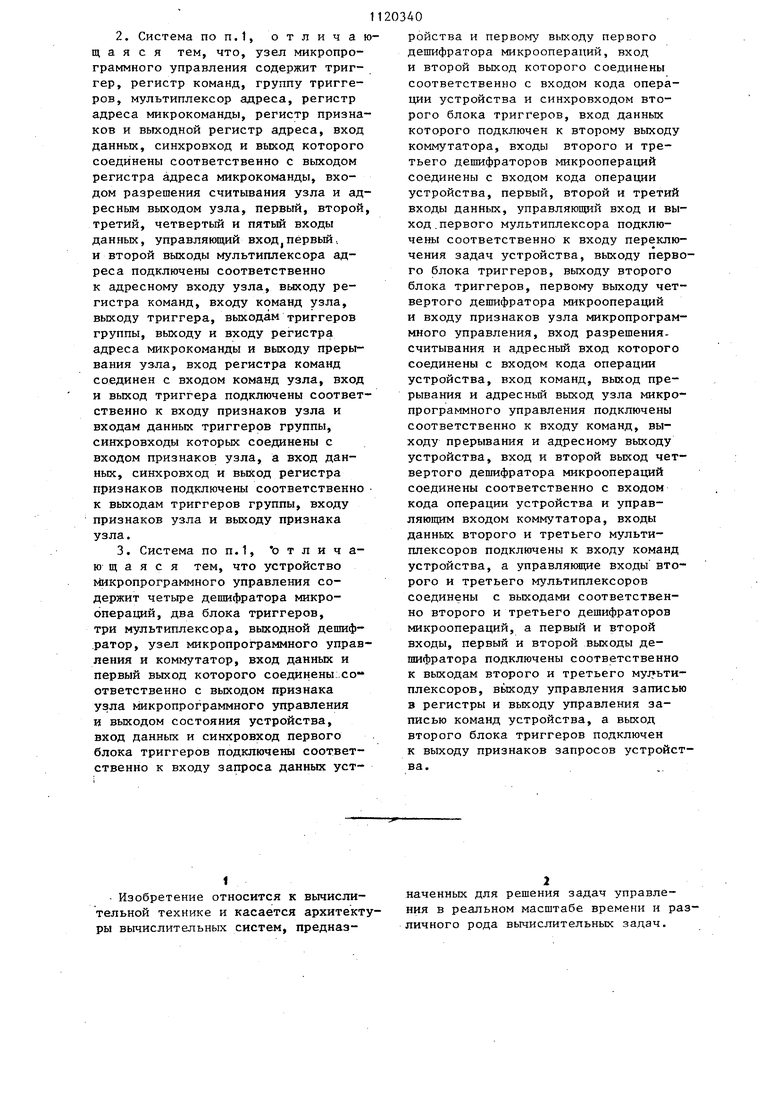

2.Система поп.1, отличащаяся тем, что, узел микропрограммного управления содержит триггер, регистр команд, группу триггеров, мультиплексор адреса, регистр адреса микрокоманды, регистр признаков и выходной регистр адреса, вход данных, синхровход и выход которого соединены соответственно с выходом регистра адреса микрокоманды, входом разрешения считывания узла и адресным выходом узла, первый, второй третий, четвертый и пятый входы данных, управляющий вход первый.

и второй выходы мультиплексора адреса подключены соответственно к адресному входу узла, выходу регистра команд, входу команд узла, выходу триггера, выходам триггеров группы, выходу и входу регистра адреса микрокоманды и выходу прерывания узла, вход регистра команд соединен с входом команд узла, вход и выход триггера подключены соответственно к входу признаков узла и входам данных триггеров группы, синхровходы которых соединены с входом признаков узла, а вход данных, синхровход и выход регистра признаков подключены соответственно к выходам триггеров группы, входу признаков узла и выходу признака узла.

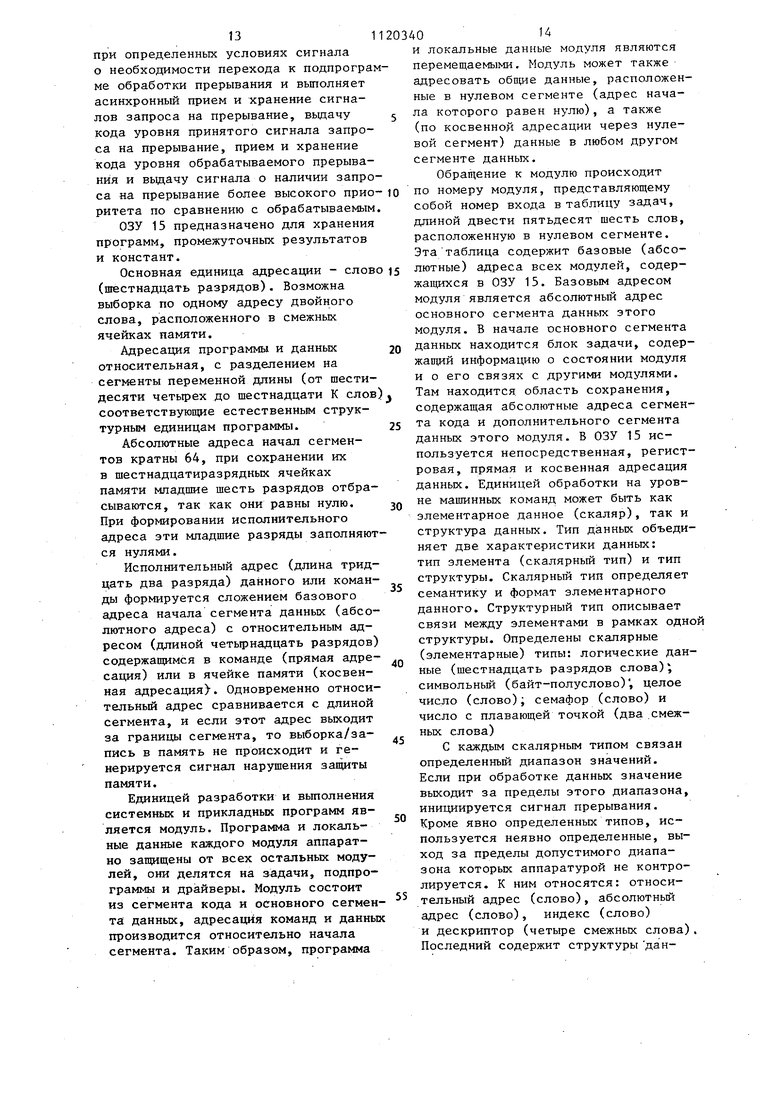

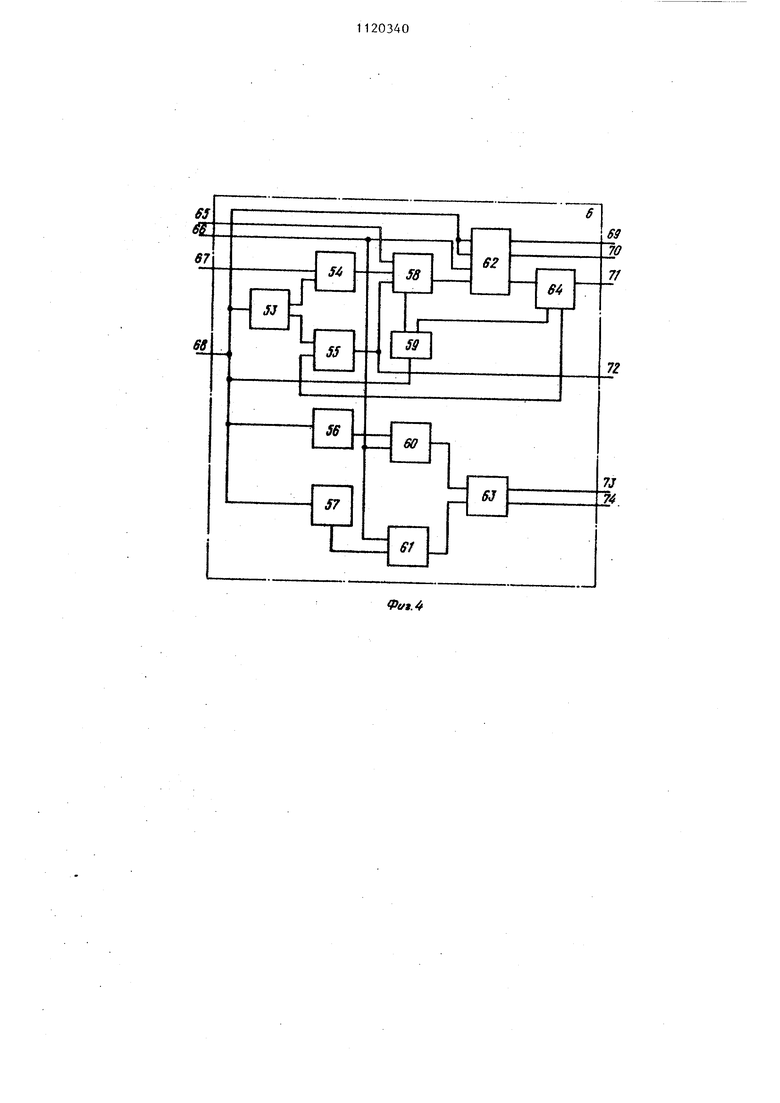

3.Система по п.1, отличающаяся тем, что устройство itoKponporpaMMHoro управления содержит четыре дешифратора микроопераций, два блока триггеров,

три мультиплексора, выходной дешиф.ратор, узел микропрограммного управления и коммутатор, вход данных и первый выход которого соединены.соответственно с выходом признака узла ьшкропрограммного управления и выходом состояния устройства, вход данных и синхровход первого блока триггеров подключены соответственно к входу запроса данных устройства и первому выходу первого дешифратора микроопераций, вход и второй выход которого соединены соответственно с входом кода операции устройства и синхровходом второго блока триггеров, вход данных которого подключен к второму выходу коммутатора, входы второго и третьего дешифраторов микроопераций соединены с входом кода операции устройства, первый, второй и третий входы данных, управляющий вход и выход, первого мультиплексора подключены соответственно к входу переключения задач устройства, выходу первого блока триггеров, выходу второго блока триггеров, первому выходу четвертого дешифратора микроопераций и входу признаков узла микропрограммного управления, вход разрешениясчитывания и адресный вход которого соединены с входом кода операции устройства, вход команд, выход прерывания и адресный выход узла микропрограммного управления подключены соответственно к входу команд, выходу прерывания и адресному выходу устройства, вход и второй выход четвертого дешифратора микроопераций соединены соответственно с входом кода операции устройства и управляющим входом коммутатора, входы данных второго и третьего мультиплексоров подключены к входу команд устройства, а управлякнцие входы второго и третьего мультиплексоров соединены с выходами соответственно второго и третьего дешифраторов микроопераций, а первый и второй входы, первый и второй выходы дешифратора подключены соответственно к выходам второго и третьего мультиплексоров, вькоду управления записью в регистры и вькоду управления записью команд устройства, а выход второго блока триггеров подключен к выходу признаков запросов устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1988 |

|

SU1649540A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Устройство микропрограммного управления | 1987 |

|

SU1539776A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134936A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

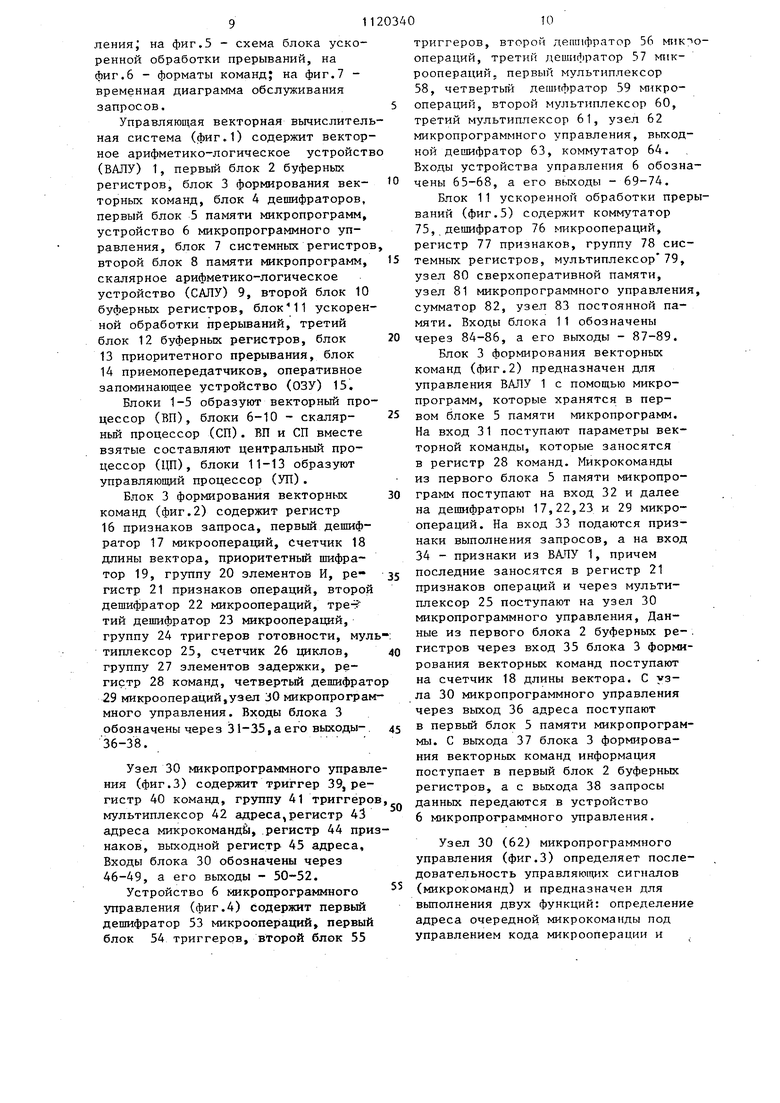

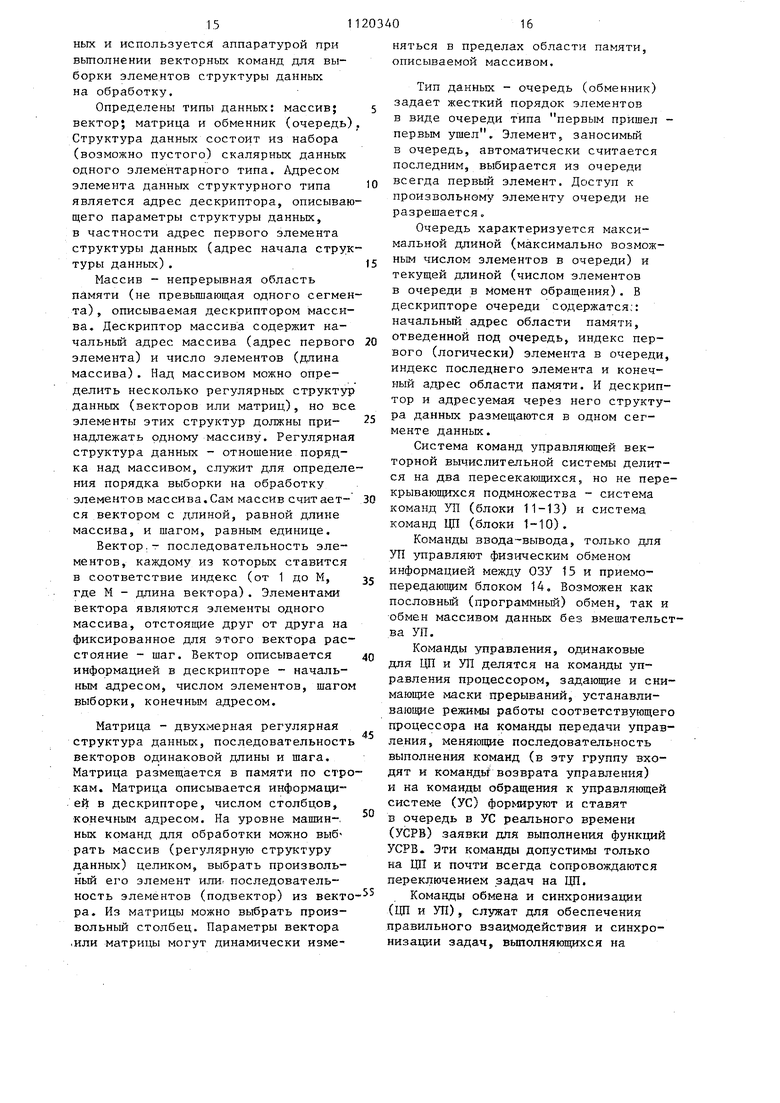

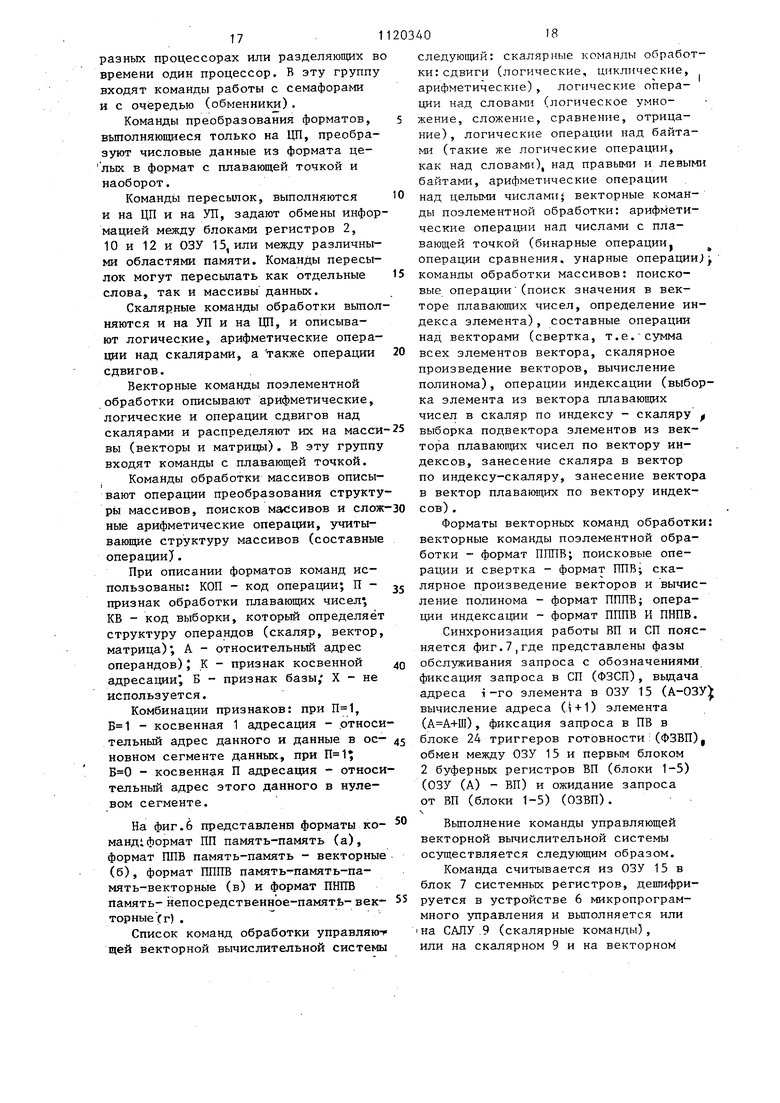

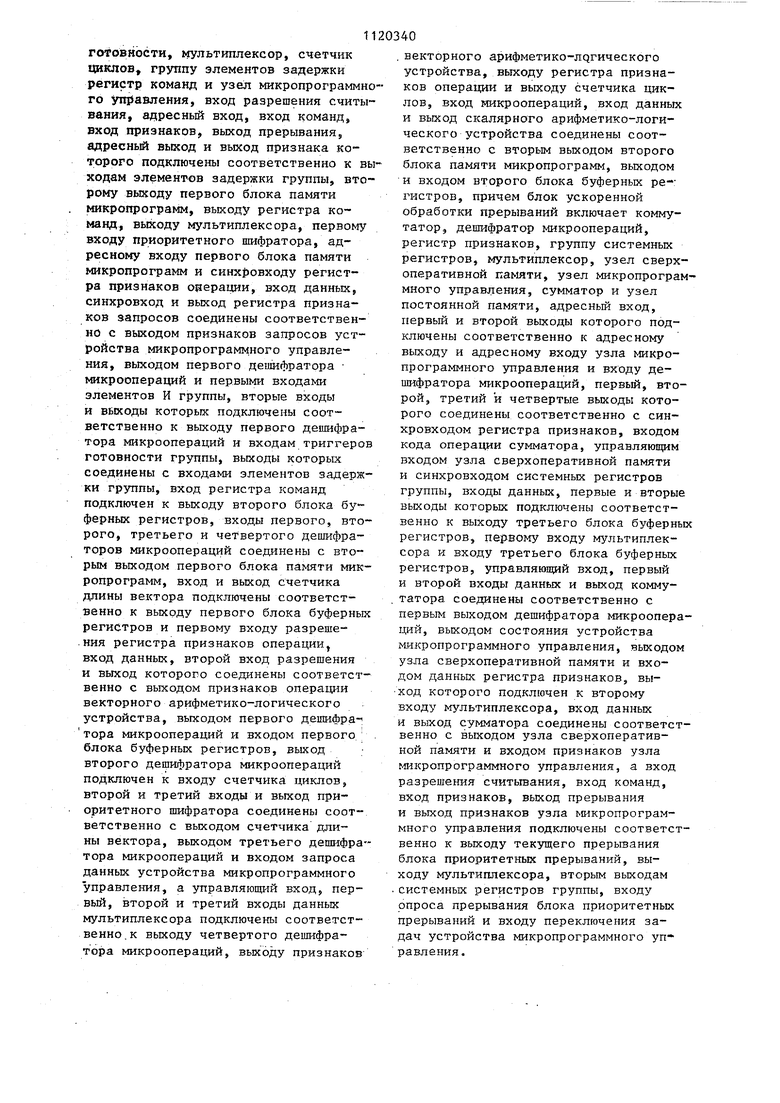

1. УПРАВЛЯЮЩАЯ ВЕКТОРНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА, содержащая векторное арифметико-логическое устройство, три блока буферных регистров, блок дешифраторов, два блока памяти микропрограмм, блок системных регистров, блок приоритетных прерываний, блок приемопередатчиков, оперативное запоминающее устройство и устройство микропрограммного управления, при этом вход и выход блока дешифраторов соединены соответственно с первым выходом первого блока памяти микропрограмм и входом кода операции векторного арифметико-логического устройства, вход данных и выход данных которого подключены соответственно к выходу и входу пер- . вого блока буферных регистров, вход данных оперативного запоминающего устройства соединен с входами первого, второго и третьего блоков буферных регистров и входом блока приемопередатчиков, выход которого подключен к адресным входам блока системных регистров и оперативного запоминающего устройства, выходам первого, второго и третьего блоков буферньЬс регистров и входу внешних прерываний блока приоритетных прерываний, выход внешнего прерывания и вход текущего прерывания блока приоритетных прерываний соединены соответственно с входом блока приемопередатчиков и выходом прерывания устройства микропрограммного управления, | адресный выход, выход управления (О записью в регистры, выход управления записью команд, вход команды и вход кода операции которого подключены соответственно к адресному входу второго блока памяти микропрограмм, входу данных блока системных регистров, входу второго блока буферных регистров, первому выходу данных илока системных регистров и первому выходу второго блока памяти микропрограмм, а второй выход данных блока системных регистров соединен с входом второго блока буферных регистров, отличающаяся тем, что, с целью повышения производительности, она содержит блок ускоренной обработки прерываний, скалярное арифметико-логическое устройство и блок формирования векторных команд, включающий регистр признаков запросов, четыре дешифратора микроопераций, счетчик длины вектора, приоритетный шифратор, группу элементов И, регистр признаков операции, группу триггеров

1

Изобретение относится к вычислительной технике и касается архитектуры вычислительных систем, предназначенных для решения задач управления в реальном масштабе времени и различного рода вычислительных задач. Известны вычислительные системы, содержащие векторные процессоры и использующие конвейерньй принцип обработки данных и С2 }. Недостатком одной из них Cl является большая величина времени реа ции на прерывание относительно времени выполнения команды При работе второй системы С21 также имеет место снижение быстродействия ввиду не возможности совмещения процессов выборки информации из памяти и ее обработки. Наиболее близкой к предлагаемой системе является малая управляющая вычислительная система, содержащая векторное арифметико-логическое устройство, три блока буферных регистров, блок дешифраторов, два бло памяти микропрограмм, блок системных регистров, блок приоритетных прерываний, блок приемопередатчиков оперативное запоминающее устройство и устройство микропрограммного управления, при зтом вход и выход бло ка дешифраторов соединены соответст венно с первым выходом первого блок памяти микропрограмм .-и входом кода операции векторного арифметикологического устройства, вход данных и выход данных которого подключены соответственно к выходу и входу пер вого блока буферных регистров, выход данных оперативного запоминающего устройства соединен с входами первого, второго и третьего блоков буферных регистров и входом блока приемопередатчиков, выход которого подключен к адресным входам блока системных регистров и оперативного запоминающего устройства, выходом первого, второго и третьего блоков буферных регистров и входу внешних прерываний блока приоритетных прерываний, выход внешнего прерывания и вход текущего прерывания блока приоритетных прерываний соединеяы соответственно с входом блока прием передатчиков и выходом прерывания устройства микропрограммного управления, адресньй выход, выход управл ния записью в регистры, вькод управ ления записью команд, вход.команды и вход кода операции которого подключены соответственно к адресному входу второго блока памяти микропро грамм, входу данных блока системных регистров, входу второго блока буферных регистров, первому выходу данных блока системных регистров и первому выходу второго блока памяти микропрограмм,, а второй выход данных блока системных регистров соединен с входом второго блока буферных регистров 3J. Недостатками известной системы являются большая величина времени реакции на прерывание и малое быстродействие при обработке скалярных величин, низкий коэффициент использования оборудования. Цель изобретения - повышение производительности заправляющей векторной вычислительной системы. Указанная цель достигается тем, что управляющая векторная вьгчислительная система, содержащая векторное арифметико-логическое устройство, три блока буферных регистров, блок дешифраторов, два блока памяти микропрограмм, блок системных ре.гистров, блок приоритетных прерываний, блок приемопередатчиков, оперативное запоминающее устройство и устройство микропрограммного управления, при этом вход и выход блока дешифраторов соединены соответственно с первым выходом первого блока памяти микропрограмм и входом кода операции векторного арифметикологического устройства, вход данных и выход данных которого подключены соответственно к выходу и входу первого блока буферных регистров, вход данных оперативного запоминающего устройства соединен с входами первого, второго и третьего блоков буферных регистров и входом блока приемопередатчиков, выход которого подключен к адресным входам блока системных регистров и оперативного запоминающего устройства, выходом первого, второго и третьего блоков буферных регистров и входу внешних прерываний блока приоритетных прерываний, выход внешнего прерывания и вход текущего прерывания блока гфиоритетных прерываний соединены соответственно с входом блока приемопередатчика и выходом прерывания устройства микропрограммного управления, адресный выход, выход управления записью в регистры, выход управления записью команд, вход команды и вход кода операции которого подключены соответственно к адресному входу второго блока памяти микропрограмм, входу данных блока системных регистров, входу второго блока буферных регистров, первому вькоду данных блока системных регис ров и первому вькоду второго блока памяти микропрограмм, а второй выхо данных блока системных регистров соединен с входом второго блока бу.ферных регистров, дополнительно содержит блок ускоренной обработки прерываний, скалярное арифметикологическое устройство и блок формирования векторных команд, включающий регистр признаков запросов, четыре дешифратора микроопераций, счетчик длины вектора, приоритетный шифратор, группу элементов И, регистр признаков операции, группу тр геров готовности, мультиплексор, счетчик циклов, группу элементов за держки, регистр команд и узел микро программного управления, вход разре шения считывания, адресный вход, вход команд, вход признаков, выход прерьшания, адресный выход и вькод признака которого подключены соответственно к выходам элементов задержки группы, вторрму выходу перво блока памяти микропрограмм, выходу регистра команд, выходу .мультиплексора, первому входу приоритетного шифратора, адресному входу первого блока памяти микропрограмм и синхровходу регистра признаков операци вход данньк, синхровход и выход регистра признаков запросов соединены соответственно с выходом признаков запросов устройства микропрограммно го управления, выходом первого дешифратора микроопераций и первыми входами элементов И группы, вторые входы и выходы которых подключены соответственно к выходу первого дешифратора микроопераций и входам триггеров готовности группы, выходы которых соеденены с входами элементов задержки группы, вход регистра кома подключен к выходу второго блока бу ферных регистров, входы первого, второго, третьего и четвертого дешифраторов микроопераций соединены с вторым выходом первого блока памя ти микропрограмм, вход и выход счет чика длины вектора подключены соответственно к выходу первого блока буферных регистров и первому входу разрешения регистра признаков опера ции, вход данных, второй вход разрешения и выход которого соединены соответственно с выходом признаков операции векторного арифметико-логического устройства, выходом первого дешифратора микроопераций и входом первого блока буферных регистров, выход второго дешифратора микроопераций подключен к входу счетчика циклов, второй и третий входы и выход приоритетного шифратора соединены соответственно с выходом счетчика длины вектора, выходом третьего дешифратора микроопераций и входом запроса данных устройства микропроrpaNfMHoro управления, а управляющий вход, первый, второй, и третий входы данных мультиплексора подключены соответственно к выходу четвертого дешифратора микроопераций, выходу признаков векторного арифметико-логического устройства, выходу регистра признаков операции и выходу счетчика циклов, вход микроопераций, вход данных и выход скалярного арифметико-логического устройства соединены соответственно с вторым выходом второго блока памяти микропрограмм, выходом и входом второго блока буферных регистров причем блок ускоренной обработки прерываний включает коммутатор, дешифратор микроопераций, регистр признаков, группу системных регистров, мультиплексор, узел сверхоперативной памяти, узел микропрограммного управления, сумматор и узел постоянной памяти, адресный вход, первый и второй выходы которого подключены соответственно к адресному выходу и адресному входу узла микропрограммного управления и входу дешифратора микроопераций, первый,второй, третий и четвертый выходы которого соединены соответственно с синхровходом регистра признаков, входом кода операции сумматора, управляющим входом узла сверхоперативной памяти и синхровходом системных регистров группы, входы данных, первые и вторые выходы которых подключены соответственно к выходу третьего блока буферных регистров, первому входу мультиплексора и входу третьего бло.ка буферных регистров, управляющий вход, первый и второй входы данных и выход коммутатора соединены соответственно с первым выходом дешифратора микроопераций, выходом состояния устройства микропрограммного управления, выходом узла сверхопера- тивной памяти и входом данных регист ра признаков, выход которого подключен к второму входу мультиплексора, нход данных и выход сумматора соединены соответственно с выходом узла сверхоперативной памяти и входом признаков узла микропрограммного управления, а вход разрешения считыва НИН, вход команд, вход признаков, выход прерывания и выход признаков узла микропрограммного управления подключены соответственно к вькоду текущего прерывания блока приоритетных прерываний, выходу мультиплексора, вторым выходам системных регистров группы, входу опроса прерывания блока приоритетных прерываний и входу переключения задач устройства микропрограммного управления. При этом узел микропрограммного управления содержит триггер, регистр команд, группу триггеров, мультиплек сор адресаJ регистр адреса микрокоманды, регистр признаков и выходной регистр адреса, вход данных, синхровход и выход которого соединены соответственно с выходом регистра адреса микрокоманды, входом регистра считывания узла и адресным выходом узла, первый, второй, третий, четвер тый и пятый входы данных, управлякнций вход, первый и второй выходы мультиплексора адреса подключены соответственно к адресному входу узла, выходу регистра команд, входу команд узла, выходу триггера, выходам триггеров группы, выходу и вх ду регистра адреса микрокоманды и выходу прерьшания узла, вход регистра команд соединен с входом команд узла, вход и выход триггера подключены соответственно к входу признак узла и входам данных триггеров груп пы, синхровходы которых соединены с входом признаков узла, а вход дан ных,, синхровход и выход регистра признаков подключены соответственно к выходам триггеров группы, входу признаков узла и выходу признака узла. Причем устройство микропрограммн го управления содержит четыре дешифратора микроопераций, два блока триггеров, три мультиплексора, выхо ной дешифратор, узел микропрограммн го управления и коммутатор, вхЬд данных и первый выход которого соединены соответственно с выходом признака узла микропрограммного управления и выходом состояния уст- , ройства, вход данных и синхровход первого блока триггеров подключены соответственно к входу запроса данных устройства и первому выходу первого дешифратора микроопераций, вход и второй выход которого соединены соответственно с входом кода операции устройства и синхровходом второго блока триггеров, вход данных которого подключен к второму выходу коммутатора., входы -второго и третьего дешифраторов микроопераций соединены с входом кода операции устройства, первый, второй, и третий входы данных, управляюпщй вход и выход первого мультиплексора подключены соответственно к входу переключения задач устройства, выходу первого блока триггеров, выходу второго блока триггеров, первому выходу четвертого дешифратора микроопераций и входу признаков узла микропрограммного- управления, вход разрешения считывания и адресньй вход которого соединены с входом кода операции устройства, вход команд, выход прерывания и адресный выход узла микропрограммного управления подключены соответственно к входу команд, выходу прерывания и адресному выходу устройства, вход и второй выход четвертого дешифратора микроопераций соединены соответственно с входом кода операции устройства и управляющим входом коммутатора, входы данных второго и третьего мультиплексоров подключены к входу команд устройства, а управляющие входы второго и третьего мультиплексоров соединены с выходами соответственно второго и третьего дешифраторов микроопераций, а первый и второй входы, первый и второй выходь дешифратора подключены соответственно к выходам второго и третьего мультиплексоров, выходу управления записью в регистры и выходу управления записью команд устройства, а выход второго блока триггеров подключен к выходу признаков запросов устройства. На фиг.1 изображена струкгурная схема управляющей векторной вычислительной системы; на фиг,2 - схема блока формирования векторных команд; на фиг.З - схема узла микропрограммного управления; на фиг.4 - схема устройства микропрограммного управ.neHHHj на фиг,5 - схема блока ускоренной обработки прерываний, на фиг.6 - форматы команд; на фиг,7 временная диаграмма обслуживания запросов, Управляющая векторная вычислител ная система (фиг.1) содержит вектор ное арифметико-логическое устройст (ВАЛУ) 1, первьш блок 2 буферных регистров, блок 3 формирования векторных команд, блок 4 дешифраторов, первый блок 5 памяти микропрограмм, устройство 6 микропрограммного управления, блок 7 системных регистро второй блок 8 памяти микропрограмм, скалярное арифметико-логическое устройство (САЛУ) 9, второй блок 10 буферных регистров, ускорен ной обработки прерьшаний, третий блок 12 буферных регистров, блок 13приоритетного прерывания, блок 14приемопередатчиков, оперативное запоминающее устройство (ОЗУ) 15. Блоки 1-5 образуют векторный про цессор (ВП), блоки 6-10 - скалярный процессор (СП). ВП и СП вместе взятые составляют центральный процессор (ЦП), блоки 11-13 образуют управляющий процессор (УП). Блок 3 формирования векторных команд (фиг,2) содержит регистр 16 признаков запроса, первый дешифратор 17 микроопераций, счетчик 18 длины вектора, приоритетньш шифратор 19, группу 20 элементов И, регистр 21 признаков операций, второй дешифратор 22 микроопераций, тре- тий дешифратор 23 микроопераций, группу 24 триггеров готовности, мул типлексор 25, счетчик 26 циклов, группу 27 элементов задержки, регистр 28 команд, четвертый дешифрат 29 микроопераций, уз ел :зО микропрограм много управления, Входы блока 3 обозначены через 31-35,а его выходы-. 36-38, Узел 30 микропрограммного управл ния (фиг,3) содержит триггер 39, регистр 40 команд, группу 41 триггеро мультиплексор 42 адреса,регистр 43 адреса микрокоманд,.регистр 44 при наков, выходной регистр 45 адреса. Входы блока 30 обозначены через 46-49, а его выходы - 50-52. Устройство 6 микропрограммного управления (фиг,4) содержит первый дешифратор 53 микроопераций, первый блок 54 триггеров, второй блок 55 триггеров, второй (ешифратор 56 мик оопераций, третий дешифратор 57 микроопераций, первьп мультиплексор 58, четвертьш дешифратор 59 микроопераций, второй мультиплексор 60, третий мультиплексор 61, узел 62 микропрограммного управления, выходной дешифратор 63, ком гутатор 64, Входы устройства управления 6 обозначены 65-68, а его выходы - 69-74, Блок 11 ускоренной обработки прерываний (фиг,5) содержит коммутатор 75, дешифратор 76 микроопераций, регистр 77 признаков, группу 78 системных регистров, мультиплексор79, узел 80 сверхоперативной памяти, узел 81 микропрограммного управления, сумматор 82, узел 83 постоянной памяти. Входы блока 11 обозначены через 84-86, а его выходы - 87-89, Блок 3 формирования векторных команд (фиг,2) предназначен для управления ВАЛУ 1 с помощью микропрограмм, которые хранятся в первом блоке 5 памяти микропрограмм. На вход 31 поступают параметры векторной команды, которые заносятся в регистр 28 команд. Микрокоманды из первого блока 5 памяти микропрограмм поступают на вход 32 и далее на дешифраторы 17,22,23 и 29 микроопераций. На вход 33 подаются признаки выполнения запросов, а на вход 34 - признаки из БА.ПУ 1, причем последние заносятся в регистр 21 признаков операций и через мультиплексор 25 поступают на узел 30 микропрограммного управления. Данные из первого блока 2 буферных ре- . гистров через вход 35 блока 3 формирования векторных команд поступают на счетчик 18 длины вектора, С узла 30 микропрограммного управления через выход 36 адреса поступают в первый блок 5 памяти микропрограммы. С выхода 37 блока 3 формирования векторных команд информация поступает в первый блок 2 буферных регистров, а с выхода 38 запросы данных передаются в устройство 6 микропрограммного управления. Узел 30 (62) микропрограммного управления (фиг,3) определяет последовательность управляющих сигналов (микрокоманд) и предназначен для вьтолнения двух функций: определение адреса очередной микрокоманды под управлением кода микрооперации и прием,хранение и вьщача информации, определяющей некоторые внешние условия. Обычно такими внешними условиями являются сигналы переноса. Ячейка памяти, в которой помещается информация о признаке, также определяется в соответствии с кодом соответствующей микрооперации, поступаю щей из первого блока 5 памяти микро команд. Особенностью узла 30 микропрограммного управления является наличие двух систем микроопераций, коды которых поступают по двум пространственно разделенным магистралям. Набор микроопераций составляет две системы: система микроопер ций определения очередного адреса микрокоманды и система микроопераций, обеспечивающая прием, хранение и выдачу информации о признаках. Со держимое первой системы микроопераций определяется адресным входом 47, второй - состоянием входа 49 признаков. Узел 30 микропрограммного управления (фиг.З) работает следующим образом. Через некоторое время после прихода импульса синхронизации на адресном входе 47 устанавливается код микрооперагщи перехода, поступающий из первого блока 5 памя микропрограмм. Далее в мультиплексо ре 42 адреса микрокоманд происходит выборка кода необходимого адреса. Указанный код загружается в регистр 43 адреса микрокоманд. Если в результате работы мультиплексора 42 а .реса микрокоманд установлен адрес. являющийся элементом матрицы первог блока 5 памяти микропрограмм, наход щимся на пересечении нулевой строки и 15-й колонки, то на выход 50 прерывания выдается стробирующий импуль разрешения прерьтания. Аналогично Происходит вьшолнение микроопераций по записи информации о признаках в триггер 39 и группу 41 триггеров. Информация записывается в триггер 39, далее в соответствии с кодом микроопераций на входе группы 41 триггеров происходит загрузка содер жимого триггера 39 в группу 41 триг геров. Вьщача содержимого группы 41 триггеров определяется кодом опе рации, устанавливаемым на входе регистра 44 признаков. Устройство 6 микропррграммного управления (фиг.4) предназначено для управления САЛУ 9 при выполнении скалярных команд, а также при работе с дескрипторами при выполнении векторных команд для формирования инструкций для ВАЛУ 1 ускоренной обработки прерьгоаний. На вход 65 переключения задач устройства б г-шкропрограммного управления поступает информация от блока 11 ускоренной обработки прерываний, на вход 66 команд - из блока 7 системных регистров, на вход 68 кода операции микрокоманды - из второго блока 8 памяти микропрограмм. Запрос данных от блока 3 формирования векторных команд поступает на вход 67 запроса данных, выходы 69 и 71 прерываний и адресов соединены соответственно с блоком 13 приоритетного прерывания и блоком 11 ускоренной обработки прерываний. Сигнал о выполнении запроса поступает с выхода 72 на блок 3 формирования векторных команд, адрес с адресного выхода 70 поступает на второй блок 8 памяти микропрограмм, а выходы 73 и 74 соединены соответственно с блоком 7 системных регистров и вторым блоком 10 буферных регистров. Блок 11 ускоренной обработки прерываний (фиг.5) предназначен для обработки прерываний без приостановки вьшолнения прикладной программы и для диспетчйрования прикладных программ. Вход БД соединен с блоком 13приоритетного прерывания, вход 85 - с устройством 6 микропрограммного управления, вход 86 - с выходом третьего блока 12 буферных регистров. Выход 87 блока 11 ускоренной обработки прерываний соединен с блоком 13 приоритетного прерывания, выход 88 - с устройством 6 микропрограммного управления, информация с выхода 89 поступает на третий блок 12 буферных регистров. Микропрограммы обработки прерываний хранятся в узле 83 постоянной памяти. САЛУ 9 предназначено для обработки скалярных операндов и вычисления адресов. Блок 13 приоритетного прерьшания предназначен для приема.сигналов запроса прерываний от блока 11 ускоренной обработки прерьгоаний и блока 14приемопередатчиков и выработки при определенных условиях сигнала о необходимости перехода к подпрогра ме обработки прерывания и вьтолняет асинхронный прием и хранение сигналов запроса на прерывание, вьщачу кода уровня принятого сигнала запроса на прерывание, прием и хранение кода уровня обрабатываемого прерывания и выдачу сигнала о наличии запро са на прерывание более высокого прио ритета по сравнению с обрабатываемым ОЗУ 15 предназначено для хранения программ, промежуточных результатов и констант. Основная единица адресации - слов (шестнадцать разрядов). Возможна выборка по одному адресу двойного слова, расположенного в смежных ячейках памяти. Адресация программы и данных относительная, с разделением на сегменты переменной длины (от шестидесяти четырех до шестнадцати К слов соответствующие естественным структурным единицам программы. Абсолютные адреса начал сегментов кратны 64, при сохранении их в шестнадцатиразрядных ячейках памяти младшие шесть разрядов отбрасываются, так как они равны нулю. При формировании исполнительного адреса эти младшие разряды заполняют ся нулями. Исполнительный адрес (длина тридцать два разряда) данного или команды формируется сложением базового адреса начала сегмента данных (абсолютного адреса) с относительным адресом (длиной четьфнадцать разрядов) содержащимся в команде (прямая адресация) или в ячейке памяти (косвенная адресация). Одновременно относительньш адрес сравнивается с длиной сегмента, и если этот адрес выходит за границы сегмента, то выборка/запись в память не происходит и генерируется сигнал нарушения защиты памяти. Единицей разработки и вьтолнения системных и прикладных программ является модуль. Программа и локальные данные каждого модуля аппаратно защищены от всех остальных модулей, они делятся на задачи, подпрограммы и драйверы. Модуль состоит из сегмента кода и основного сегмен та данных, адресация команд и данны производится относительно начала сегмента. Таким образом, программа и локальные данные модуля являются перемещаемыми. Модуль может также адресовать общие данные, расположенные в нулевом сегменте (адрес начала которого равен нулю), а также (по косвенной адресации через нулевой сегмент) данные в любом другом сегменте данных. Обращение к модулю происходит по номеру модуля, представляющему собой номер входа в таблицу задач, длиной двести пятьдесят шесть слов, расположенную в нулевом сегменте. Эта таблица содержит базовые (абсолютные) адреса всех модулей, содержащихся в ОЗУ 15. Базовым адресом модуля является абсолютный адрес основного сегмента данных этого модуля. В начале основного сегмента данных находится блок задачи, содержащий информацию о состоянии модуля и о его связях с другими модулями. Там находится область сохранения, содержащая абсолютные адреса сегмента кода и дополнительного сегмента данных этого модуля. В ОЗУ 15 используется непосредственная, регистровая, прямая и косвенная адресация данных. Единицей обработки на уровне машинных команд может быть как элементарное данное (скаляр), так и структура данных. Тип данных объединяет две характеристики данных: тип элемента (скалярный тип) и тип структуры. Скалярный тип определяет семантику и формат элементарного данного. Структурный тип описывает связи между элементами в рамках одной структуры. Определены скалярные (элементарные) типы: логические данные (шестнадцать разрядов слова) символьный (байт-полуслово), целое число (слово); семафор (слово) и число с плавающей точкой (два .смежных слова) С каждым скалярным типом связан определенный диапазон значений. Если при обработке данных значение выходит за пределы этого диапазона, инициируется сигнал прерывания. Кроме явно определенных типов, используется неявно определенные, выход за пределы допустимого диапазона которых аппаратурой не контролируется. К ним относятся: относительный адрес (слово), абсолютный адрес (слово), индекс (слово) и дескриптор (четыре смежных слова). Последний содержит структуры дан15ных и используется аппаратурой при выполнении векторньк команд для выборки элементов структуры данных на обработку. Определены типы данных: массив; вектор; матрица и обменник (очередь Структура данных состоит из набора (возможно пустого) скалярных данных одного элементарного типа. Адресом элемента данных структурного типа является адрес дескриптора, описываю щего параметры структуры данных, в частности адрес первого элемента структуры данных (адрес начала стру туры данных). Массив - непрерывная область памяти (не превышающая одного сегме та) , описываемая дескриптором масси ва. Дескриптор массива содержит начальньй адрес массива (адрес первог элемента) и число элементов (длина массива). Над массивом можно определить несколько регулярных структу данных (векторов или матриц), но вс элементы этих структур должны принадлежать одному массиву. Регулярна структура данных - отношение порядка над массивом, служит для определ ния порядка выборки на обработку элементов массива.Сам массив считается вектором с длиной, равной длине массива, и шагом, равным единице. Вектор.- последовательность элементов, каждому из которых ставится в соответствие индекс (от 1 до М, где М - длина вектора). Элементами вектора являются элементы одного массива, отстоящие друг от друга на фиксированное для этого вектора рас стояние - шаг. Вектор описывается информацией в дескрипторе - начальным адресом, числом элементов, шаго выборки, конечным адресом. Матрица - двухмерная регулярная структура данных, последовательност векторов одинаковой длины и шага. Матрица размещается в памяти по стр кам. Матрица описывается информацией в дескрипторе, числом столбцов, конечным адресом. На уровне машин-, ных команд для обработки можно выб рать массив (регулярную структуру данных) целиком, выбрать произвольный его элемент или. последовательность элементов (подвектор) из вект ра. Из матрицы можно выбрать произвольный столбец. Параметры вектора .или матрицы могут динамически изменяться в пределах области памяти, описываемой массивом. Тип данных - очередь (обменник) задает жесткий порядок элементов в виде очереди типа первым пришел первым ушел. Элемент, заносимый в очередь, автоматически считается последним, выбирается из очереди всегда первый элемент. Доступ к произвольном элементу очереди не разрешается„ Очередь характеризуется максимальной длиной (максимально возможным числом элементов в очереди) и текущей длиной (числом элементов в очереди в момент обращения). В дескрипторе очереди содержатся;: начальный адрес области памяти, отведенной под очередь, индекс первого (логически) элемента в очереди, индекс последнего элемента и конечный адрес области памяти. И дескриптор и адресуемая через него структура данных размещаются в одном сегменте данных. Система команд управляющей векторной вычислительной системы делится на два пересекающихся, но не перекрываюшдхся подмножества - система команд УП (блоки 11-13) и система команд ЦП (блоки 1-10). Команды ввода-вывода, только для УП управляют физическим обменом информацией между ОЗУ 15 и приемопередающим блоком 14, Возможен как пословньй (программный) обмен, так и обмен массивом данных без вмешательства УП, Команды управления, одинаковые для ЦП и УП делятся на команды управления процессором, задающие и снимающие маски прерываний, устанавливающие режимы работы соответствующего процессора на команды передачи управления, меняю1Щ1е последовательность выполнения команд (в эту группу входят и командьг возврата управления) и на команды обращения к управляющей системе (УС) формируют и ставят в очередь в УС реального времени (УСРВ) заявки для выполнения функций УСРВ. Эти команды допустимы только на ЦП и почти всегда сопровождаются переключением задач на 1ДП, Команды обмена и синхронизации (ЦП и УП), служат для обеспечения правильного взаимодействия и синхронизации задач, выполняющихся на

разных процессорах или разделяющих во времени один процессор. В эту группу входят команды работы с семафорами и с очередью (обменники).

Команды преобразования форматов, выполняющиеся только на ЦП, преобразуют числовые данные из формата делых в формат с плавающей точкой и наоборот.

Команды пересылок, выполняются и на ЦП и на 5TI, задают обмены информацией между блоками регистров 2, 10 и 12 и ОЗУ 15, или между различными областями памяти. Команды пересылок могут пересылать как отдельные слова, так и массивы данных.

Скалярные команды обработки вьтолняются и на УП и на ЦП, и описывают логические, арифметические операции над скалярами, а также операции сдвигов.

Векторные команды поэлементной обработки описывают арифметические, логические и операции сдвигов над скалярами и распределяют их на массивы (векторы и матрицы), В эту группу входят команды с плавающей точкой.

Команды обработки массивов описывают операции преобразования структуры массивов, поисков массивов и сложные арифметические операции, зачитывающие структуру массивов (составные операции).

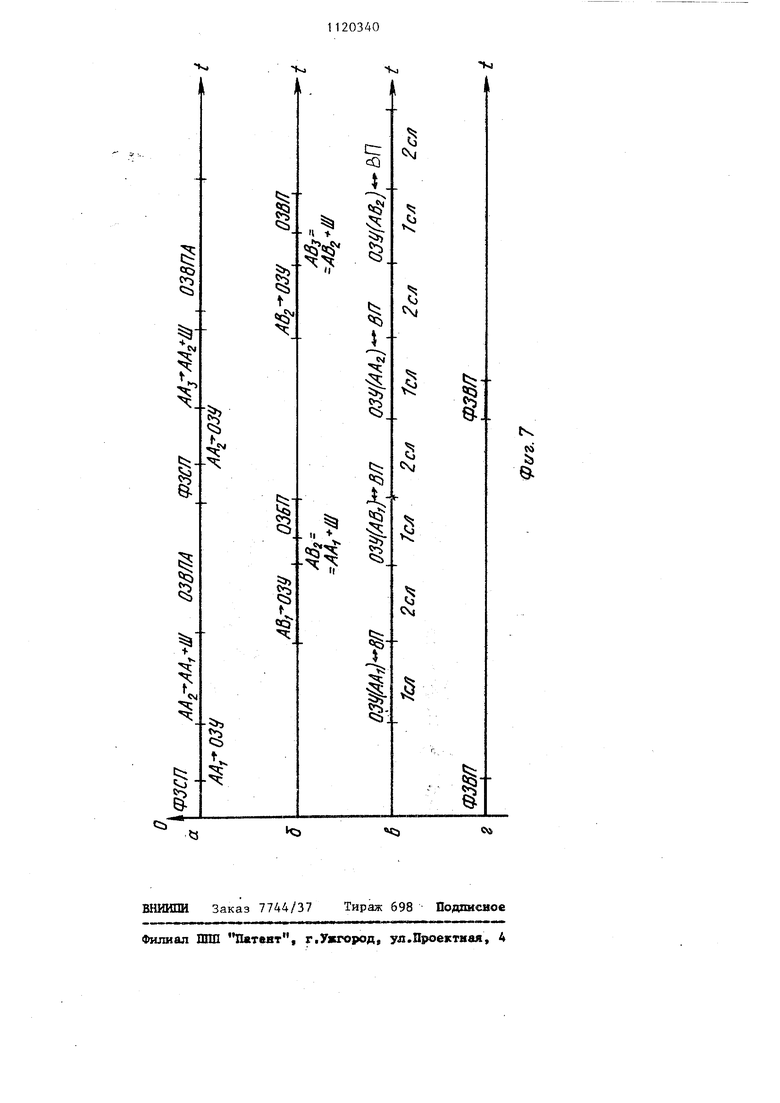

При описании форматов команд использованы: КОП - код операции; П признак обработки плавающих чисел, КБ - код выборки, который определяет структуру операндов (скаляр, вектор, матрица); А - относительный адрес операндов)J К - признак косвенной адресации, В - признак базы, X - не используется.

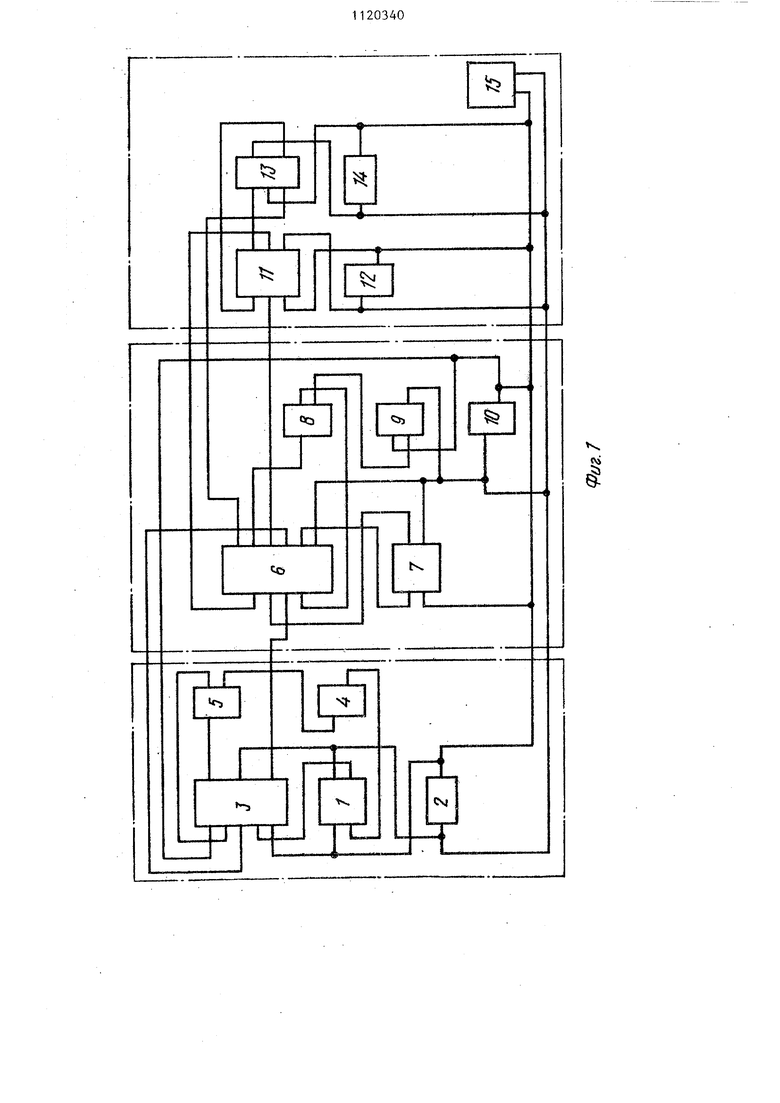

Комбинации признаков: при , - косвенная 1 адресация - ртносительный адрес данного и данные в ос- новном сегменте данных, при - косвенная П адресация - относи тельный адрес этого данного в нулевом сегменте. На фиг.6 представлены форматы команд формат ПП память-память (а), формат ППВ память-память - векторные (б), формат ПППВ память- память-память-векторные (в) и формат ПНПВ память- непосредственное-память- вектор ные f г) . Список команд обработки управляю-f щей векторной вычислительной системы

следующий: скалярные команды обработки: сдвиги (логические, циклические, арифметические), логические операции над словами (логическое умножение, сложение, сравнение, отрицание) , логические операции над байтами (такие же логические операции, как над словами), над правыми и левыми ба 1тами, арифметические операции над целыми числами векторные команды поэлементной обработки: арифметические операции над числами с плавающей точкой (бинарные операции операции сравнения, унарные oпepaции команды обработки массивов: поисковые операции(поиск значения в векторе плавающих чисел, определение индекса элемента), составные операции над векторами (свертка, т.е.сумма всех элементов вектора, скалярное произведение векторов, вычисление полинома), операции индексации (выборка элемента из вектора плавающих чисел в скаляр по индексу - скаляру выборка подвектора элементов из вектора плавающих чисел по вектору индексов, занесение скаляра в вектор по индексу-скаляру, занесение вектора в вектор плавающих по вектору индексов) .

Форматы векторных команд обработки векторные команды поэлементной обработки - формат ПППВ; поисковые операции и свертка - формат ПИВ; скалярное произведение векторов и вычисление полинома - формат ПППВ; операции индексации формат ПППВ И ПНПВ.

Синхронизация работы ВП и СП поясняется фиг.7,где представлены фазы обслуживания запроса с обозначениями фиксация запроса в СП (ФЗСП), вьщача адреса i-го элемента в ОЗУ 15 (А-ОЗУ вычисление адреса Ci+1) элемента (), фиксация запроса в ПВ в блоке 24 триггеров готовности:(ФЗВП), обмен между ОЗУ 15 и первым блоком 2 буферных регистров ВП (блоки 1-5) (ОЗУ (А) - ВП) и ожидание запроса от ВП (блоки 1-5) (ОЗВП). Выполнение команды управляющей векторной вычислительной системы осуществляется следующим образом. Команда считывается из ОЗУ 15 в блок 7 системных регистров, дешифрируется в устройстве 6 микропрограммного управления и выполняется или на САЛУ .9 (скалярные команды), или на скалярном 9 и на векторном

Iарифметико-логическом устройствах одновременно (векторные команды).

В последнем случае САЛУ 9 на основании параметров векторов данных вычисляет поток адресов очередных элементов вект.оров. Этот поток подается на ОЗУ 15 для выборки данных, образующих поток на ВАЛУ, 1, которое, обработав их, подает поток даннь1х на ОЗУ 15 одновременно с потоком адресов результатов, формируемых САЛУ 9. Устройство б микропрограммного управления по асинхронным сигналам, вырабатываемым арифметико-логическими устройствами и 9 и ОЗУ 15, согласует потоки данных и адресов.

При возникновении внешнего прерывания от блока 14 приемопередатчиков, требующего обработки, этот процесс происходит в два этапа. Сначала информация независимо от устройства 6 микропрограммного управления считывается с блока 14 приемопередатчиков и через блок 13 приоритетных прерываний с помощью блока

I1ускоренной обработки прерываний заносится в ОЗУ 15. Далее блок 11 ускоренной обработки прерываний сравнивает приоритет прерываний с маской внешних прерываний, если данное прерывание разрешено, то сравнивается приоритет текущей задачи

с приоритетом задач обработки полученного прерывания. Если последний выше, то на устройство 6 микропрограммного управленияподается сигнал внутреннего прерывания. Получив его, устройство 6 микропрограммного управления определяет номер соответствующей задачи обработки и к концу текущей команды останавливает выполнение текущей задачи, сохраняя ее состояние, и запускает задачз обработки возникающего внешнего прерывания. Далее работа происходит обычным порядком.

Управляющая векторная вычислительная система может работать в многозадачном режиме в реальноммасштабе времени. Максимальное количество задач 256. Задачи подразделяются на две группы: прикладные задачи и задачи обработки прерывания (обслуживание) , которые могут вьшолняться параллельно.

На УП реализуется управляющая система реального времени, состоящая из диспетчера, программ обработки

прерываний, внутренних и внешних (драйверы), и загрузчика. На ЦП вьтолняются прикладные (задачи и процедуры) программы. УП формирует приоритетные очереди готовых задач (шестнадцать уровней приоритета), из которой ЦП загружает задачу высшего приоритета на исполнение. Драйверы выполняются на УП, запускаются по требованию прикладных задач или по прерыванию. Программы обработки внутренних прерываний Щ1 запускаются управляющей системой на УП при получении соответствующего запроса от ЦП, На УП имеется восемь уровней прерываний, и появление сигнала высшего приоритета вызывает сохранение состояния текущей программы в ее локальной области сохранения и сохранение номера программы. Дескриптор обработки запросов от прикладных задач имеет низший приоритет.

В зависимости от характера обмена различаются драйверы пассивного устройства, драйверы инициативного устройства и драйвер пассивноинициативного устройства (основной тип). Драйвер является двухсекционным, т.е. состоит из секции запуска, из секпйи продолжения и оформляется как одна задача с двумя входами.

В,любой момент времени каждая задача пользователя находится в одном из состояний: пассивном, готовом, активном,, блокированном (ожидание некоторого события). Задачи порождаются (переходят в готовое состояние и из пассивного): при загрузке в систему (инициативные задачи), по требованию других исполняюощхся задач. Приоритет присваивается задаче при планировании основного ресурса задачи центрального процессора ЦП,

Дисциплина планирования: процессор получает готовую задачу с высшим, приоритетом - задачу с наибольшим временем ожидания, процессора. Б активном состоянии задача переходит в блокированное состояние, если выдан запрос на ввод-вывод - задача переходит в состояние ожидания конца операции ввода-вывода, если задано время приостанова выполняемой задачи - задача переходит в состоя,ние ожидания заданного интервала времени, в случае обработки особьк ситуаций при выработке активной за.дачей внутреннего прерывания, если активная задача, обращаясь к стандартной программе обнаружила, что семафор закрыт, и в состояние готовности и ставит. себя в конец очереди своего приоритета, если в очереди готовых задач появляется задача высшего приоритета по сравнению с задачей, которая находится в активном состоянии.

В случае блокировки блокированная задача формирует запрос к управляюще системе и причине прерывания, ставит его в системный обменник и переходит в состояние ожидания обработки этой ситуации, соответствующей программой обработки.

ЦП после сохранения состояния блокированной задачи сразу же загружает очередную задачу из очереди готовых задач наивысшего приоритета.

Предлагаемая управляющая векторная вычислительная система по сравнению с известными имеет большее быстродействие и более высокий коэффициент использования оборудования. Высокое быстродействие обеспечивается путем уменьшения времени на реализацию прерываний и ускорения обработки векторной информации, В предлагаемой системе это достигается за счет разделения обработки на восприятие сигнала прерывания и сохранение всей связанной с ней информации в буферах, расположенных в ОЗУ и обработка этой информагщи задачами обработки. Повьппение коэффициента использования оборудования достигается путем вычисления адресов операндов элементов данных, выбираемых для обработки в ВАЛУ. Это достигается за счет введения САЛУ, которое не только выполняет операции над скалярными величинами, но и учасвует в выполнении векторных команд.

«30

К,

46

Фиг. 2

50

7 2П 5 //

7 211 S 11

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Вычислительная техника | |||

| Экспресс-информация, 1978, №28, с.3-8 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-10-23—Публикация

1982-11-10—Подача