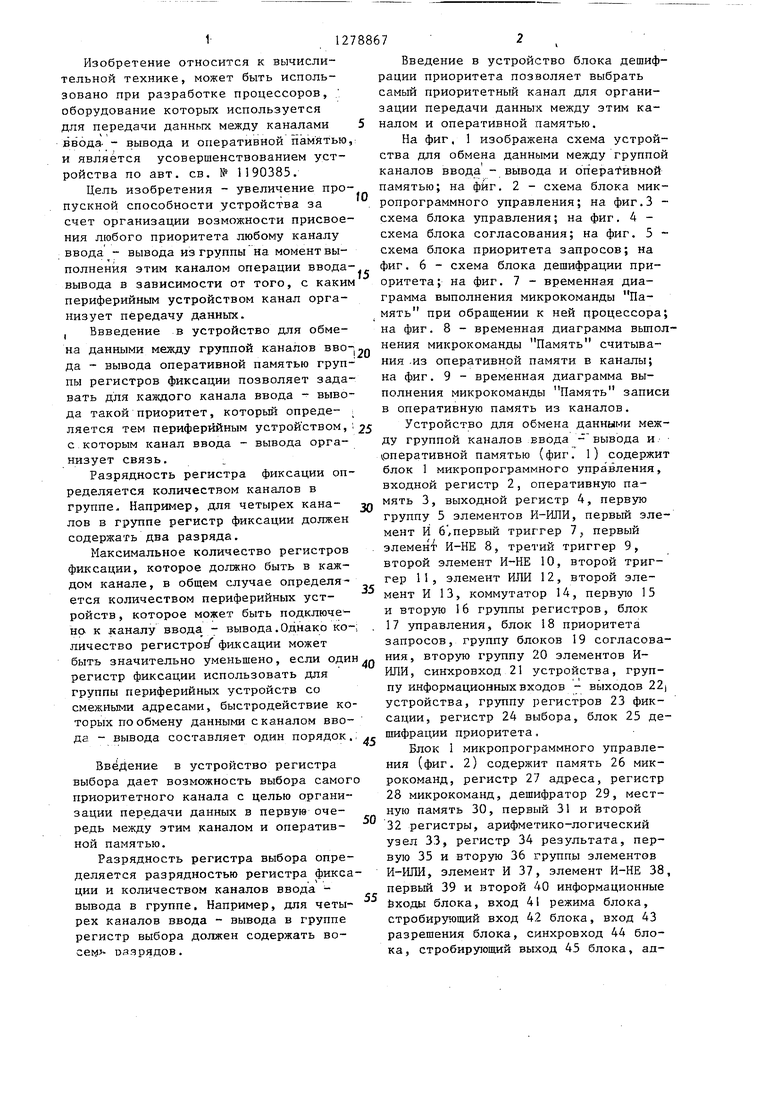

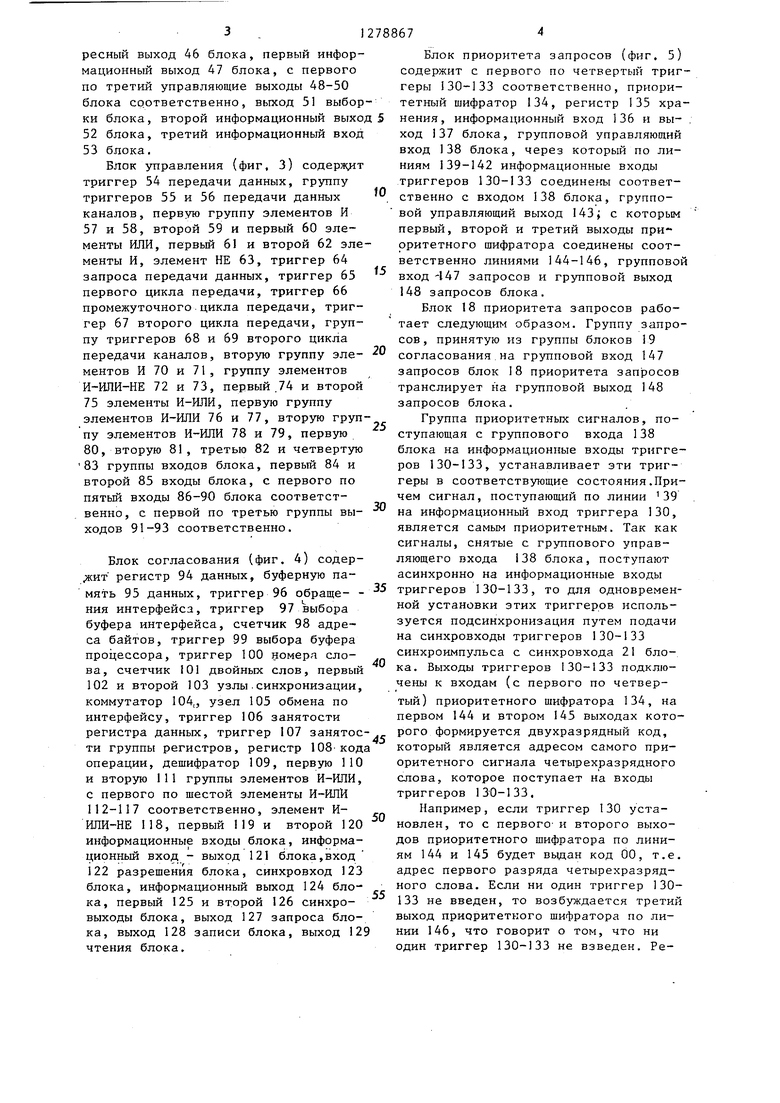

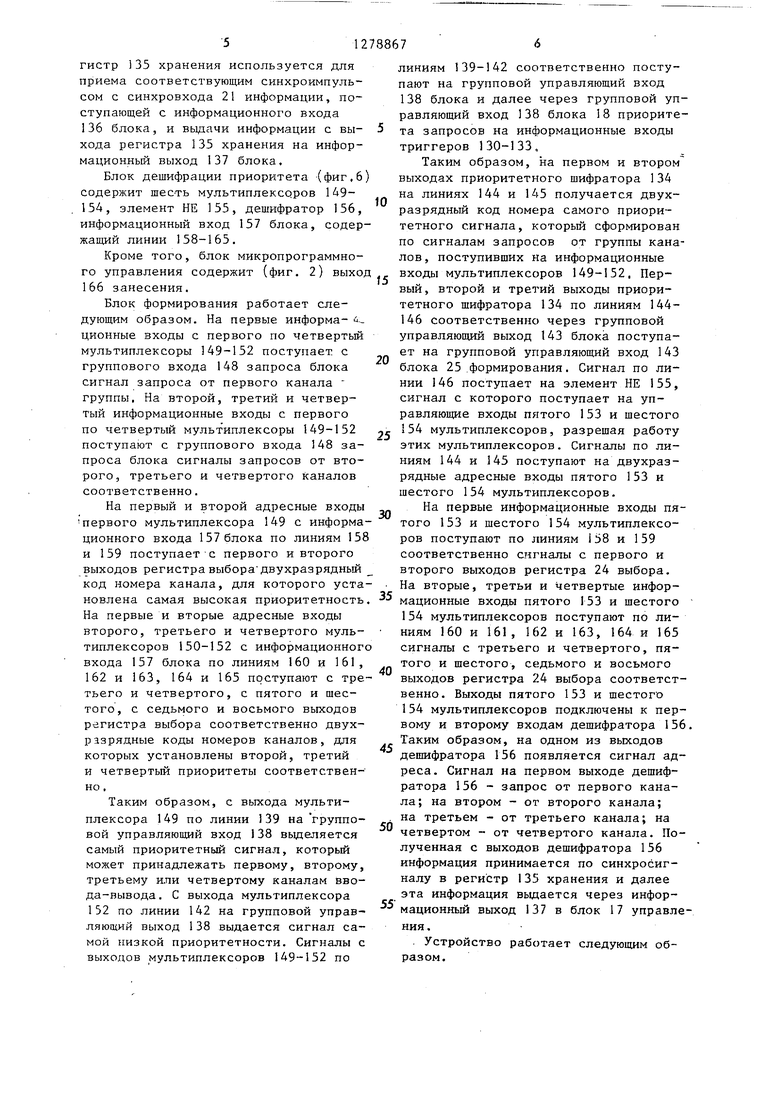

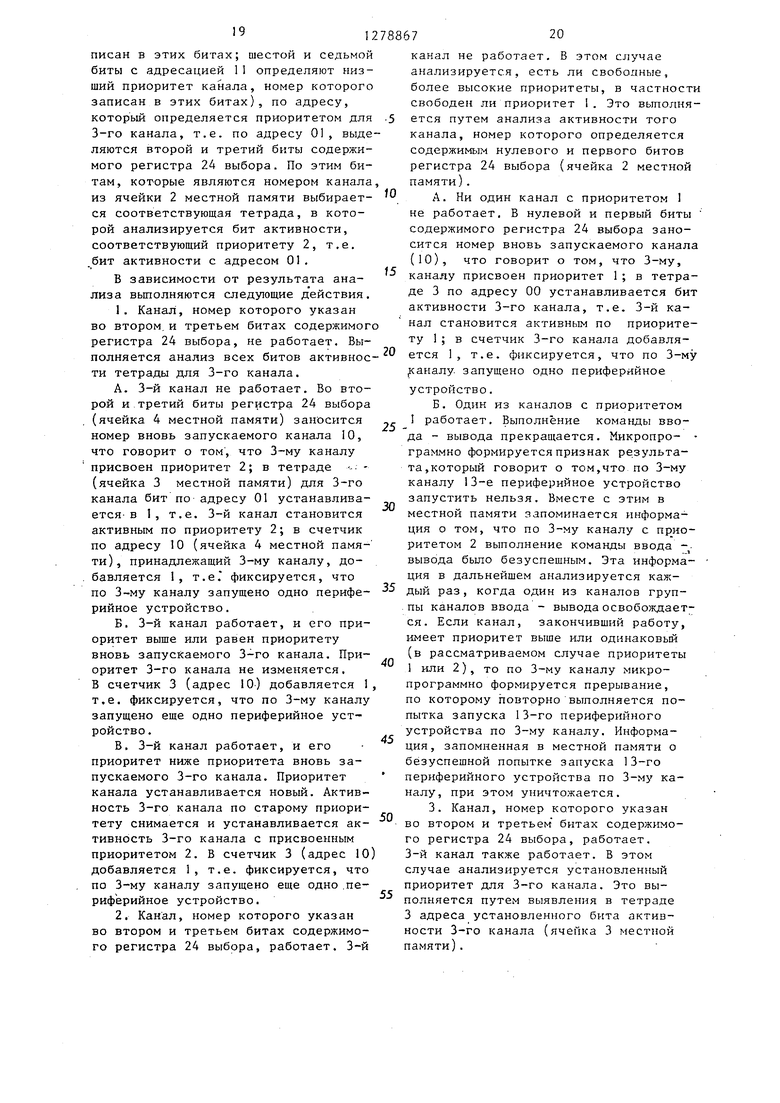

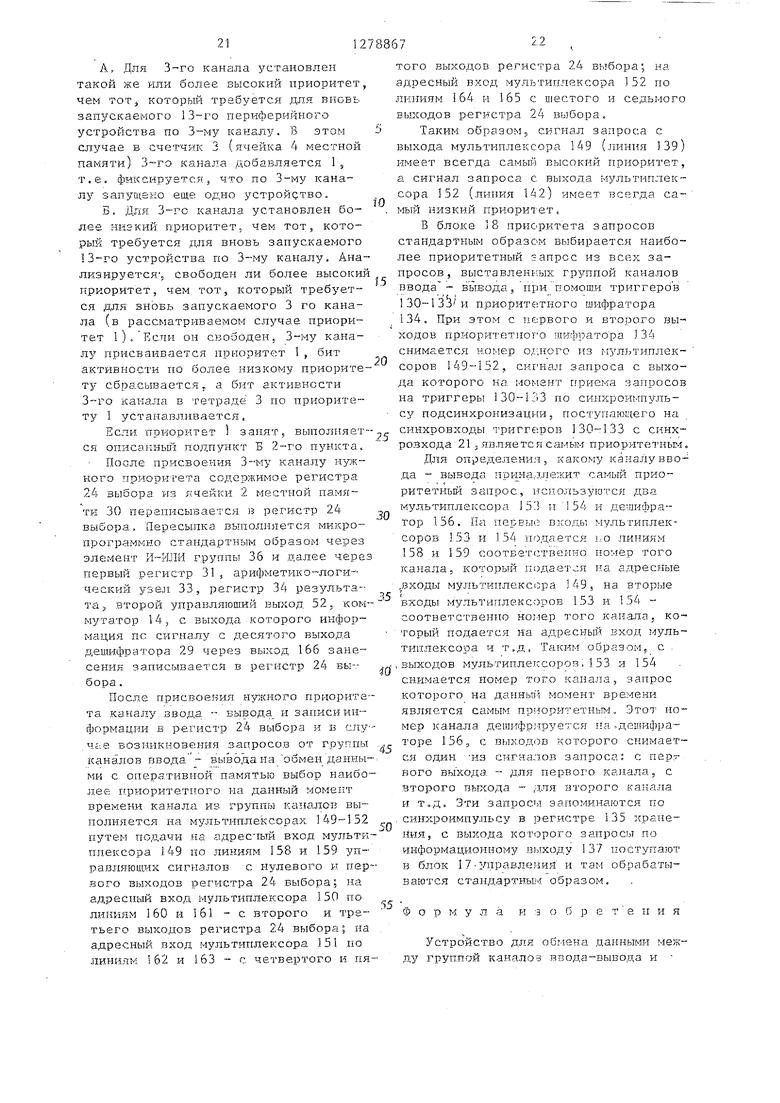

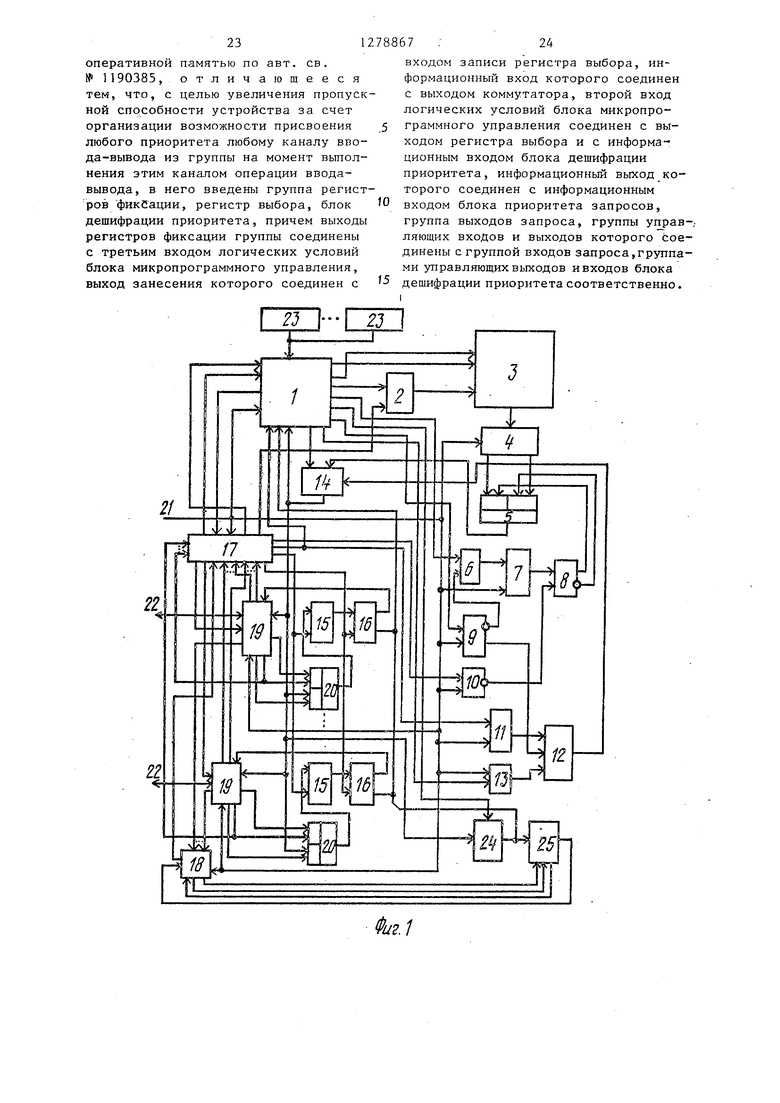

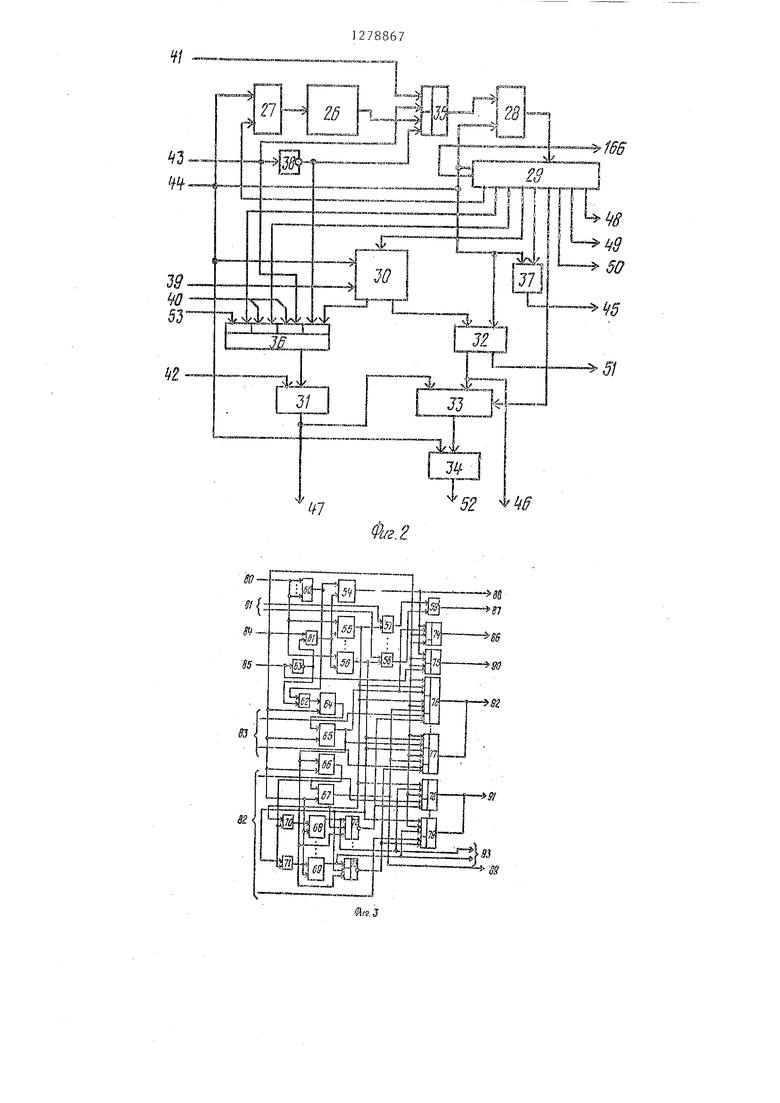

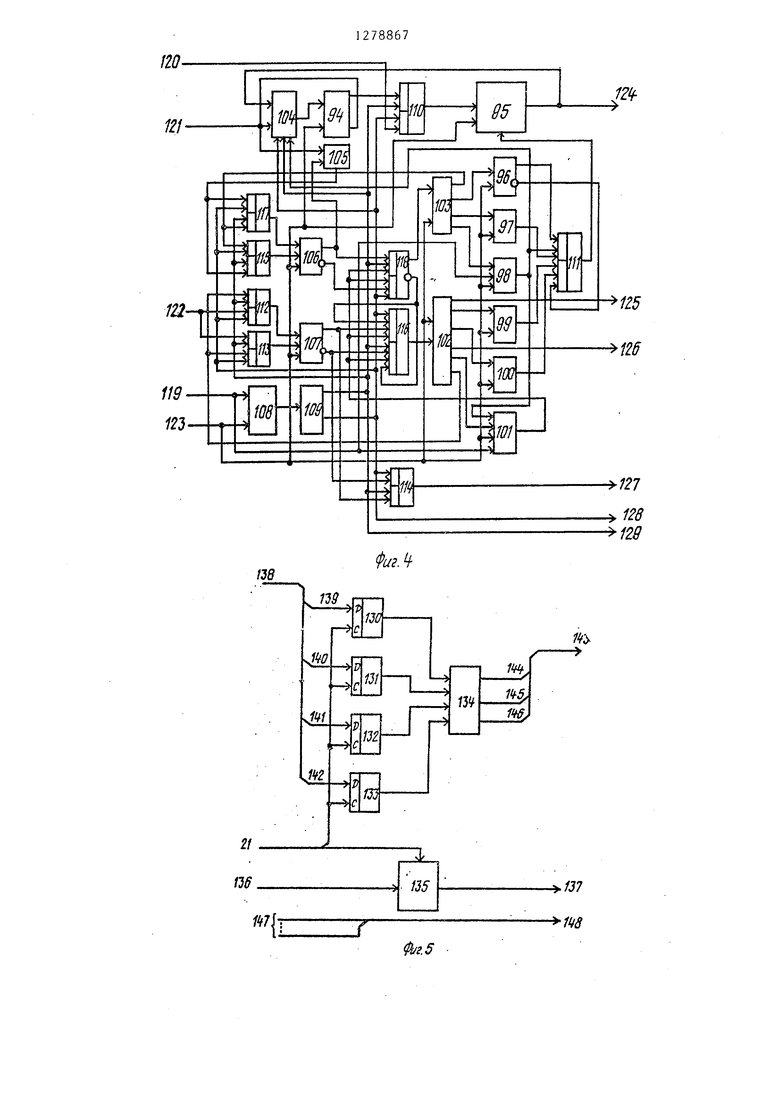

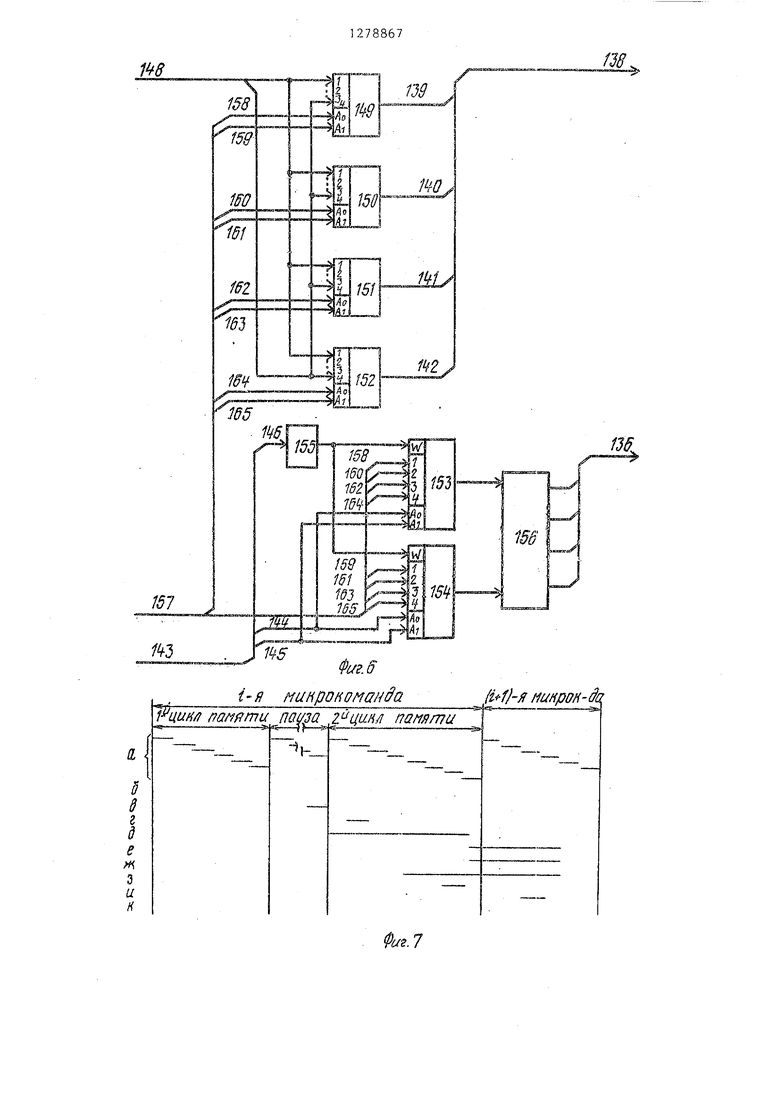

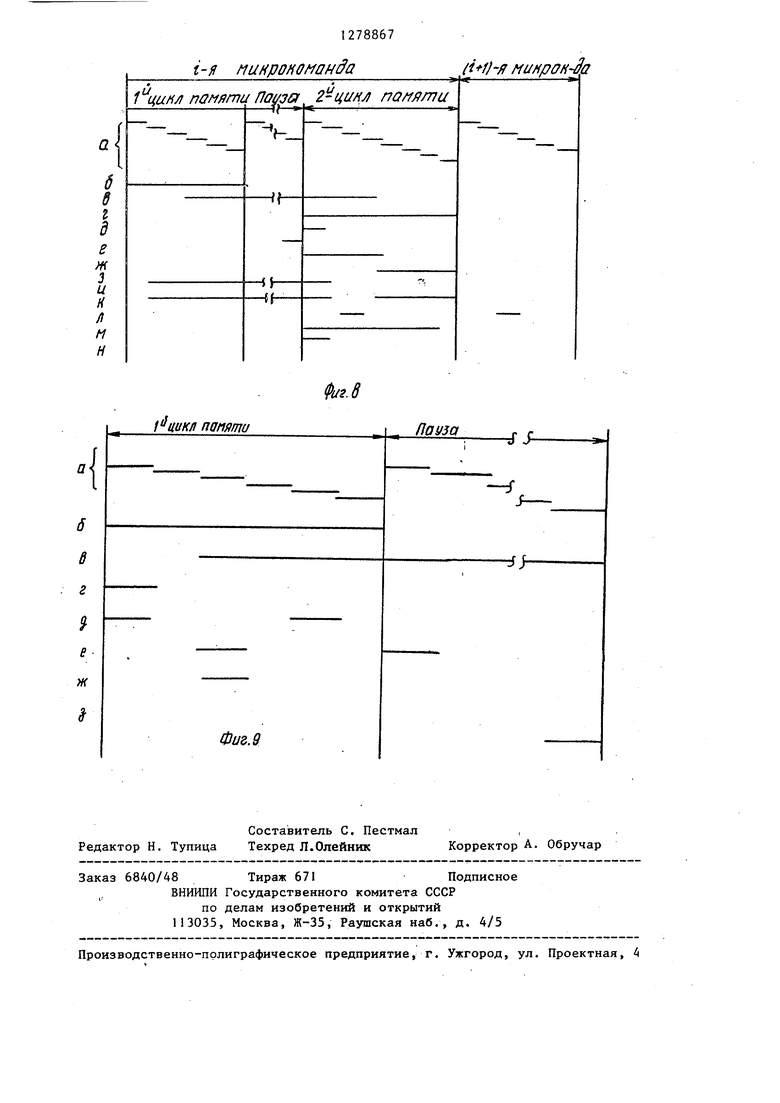

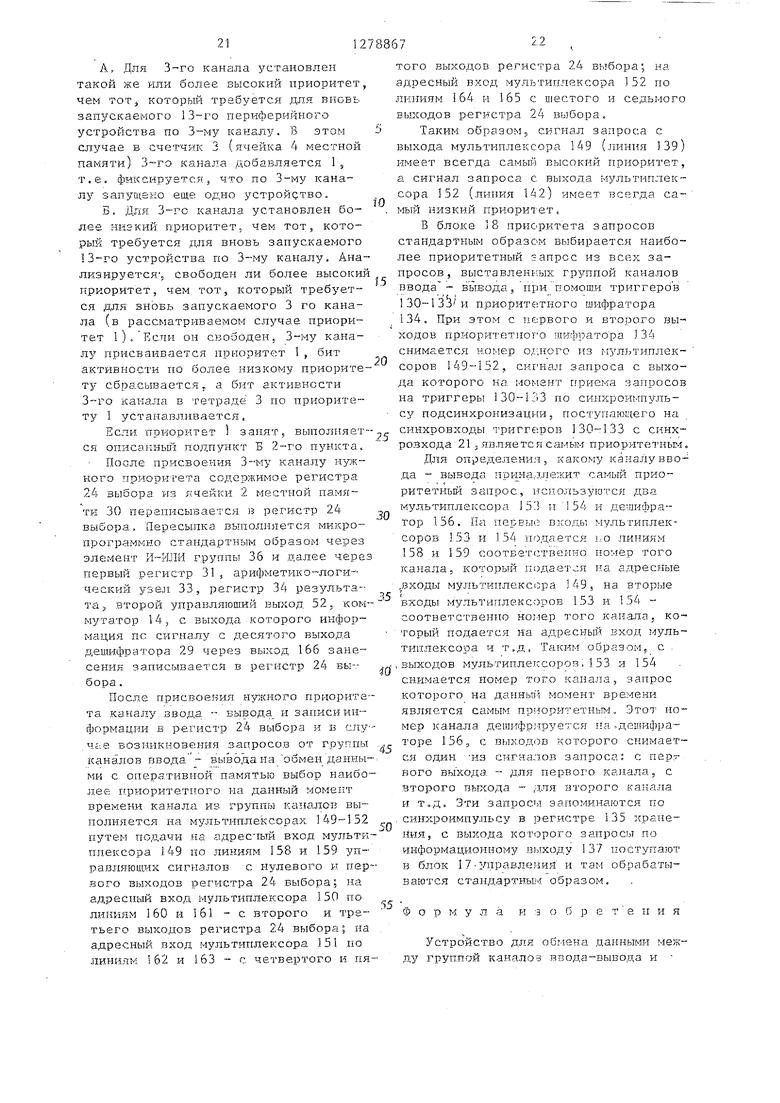

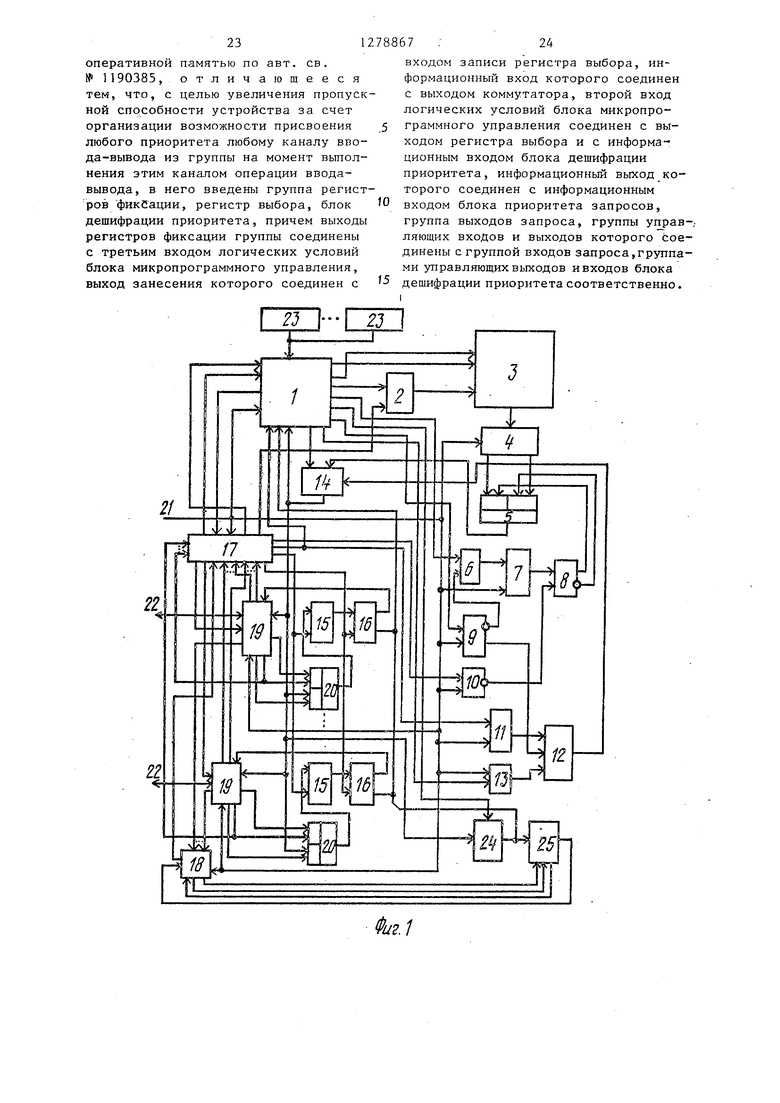

1-12 Изобретение относится к вычислительной технике, может быть использовано при разработке процессоров, оборудование которых используется для передачи данных между каналами ввода- - вывода и оперативной памятью и является усовершенствованием устройства по авт. св. № 1190385. Цель изобретения - увеличение про пускной способности устройства за счет организации возможности присвое ния любого приоритета любому каналу ввода - вывода из группы на момент выполнения этим каналом операции ввода вывода в зависимости от того, с каки периферийным устройством канал организует передачу данных. Ввведение в устройство для обмена данными между группой каналов вво да - вывода оперативной памятью груп пы регистров фиксации позволяет зада вать для каждого канала ввода - выво да такой приоритет, которьш определяется тем периферийным устройством, с которым канал ввода - вывода организует связь. Разрядность регистра фиксации определяется количеством каналов в группе. Например, для четырех каналов в группе регистр фиксации должен содержать два разряда. Максимальное количество регистров фиксации, которое должно быть в каждом канале, в общем случае определяется количеством периферийных устройств , которое может быть подключено- к каналу ввода - вывода.Однако количество регистров фиксации может быть значительно уменьшено, если оди регистр фиксации использовать для группы периферийных устройств со смежными адресами, быстродействие ко торых по обмену данными с каналом ввода - вывода составляет ОДРШ порядок. Введение в устройство регистра выбора дает возможность выбора самог приоритетного канала с целью организации передачи данных в первую очередь между этим каналом и оперативной памятью. Разрядность регистра выбора определяется разрядностью регистра фикса ции и количеством каналов ввода вывода в группе. Например, для четырех каналов ввода - вывода в группе регистр выбора должен содержать восемз. разрядов. 7 Введение в устройство блока дешифрации приоритета позволяет выбрать самый приоритетный канал для организации передачи данных между этим каналом и оперативной памятью. На фиг. 1 изображена схема устройства для обмена данными между группой каналов ввода - вывода и оперативной памятью; на фиг. 2 - схема блока микропрограммного управления; на фиг.З схема блока управления; на фиг. 4 схема блока согласования; на фиг. 5 схема блока приоритета запросов; на фиг. 6 - схема блока дешифрации приоритета ; на фиг. 7 - временная диаграмма выполнения микрокоманды Память при обращении к ней процессора; на фиг. 8 - временная диаграмма вьтолнения микрокоманды Память считывания .из оперативной памяти в каналы; на фиг. 9 - временная диаграмма выполнения микрокоманды Память записи в оперативную память из каналов. Устройство для обмена данными между группой каналов ввода -вывода и оперативной памятью (фиг. 1) содержит блок 1 микропрограммного управления, входной регистр 2, оперативнее память 3, выходной регистр 4, первую группу 5 элементов И-ИЛИ, первый элемент И 6,первый триггер 7, первый элемен- И-НЕ 8, третий триггер 9, второй элемент И-НЕ 10, второй триггер 11, элемент ИЛИ 12, второй элемент И 13, коммутатор 14, первую 15 и вторую 16 группы регистров, блок 17 управления, блок 18 приоритета запросов, группу блоков 19 согласования, вторую группу 20 элементов ИИЛИ, синхровход 21 устройства, группу информационных входов - выходов 22) устройства, группу регистров 23 фиксации, регистр 24 выбора, блок 25 дешифрации приоритета. Блок 1 микропрограммного управления (фиг. 2) содержит память 26 микрокоманд, регистр 27 адреса, регистр 28 микрокоманд, дешифратор 29, местную память 30, первый 31 и второй 32 регистры, арифметико-логический узел 33, регистр 34 результата, первую 35 и вторую 36 группы элементов И-ШШ, элемент И 37, элемент И-НЕ 38, первый 39 и второй 40 информационные Ёходы блока, вход 41 режима блока, стробирующий вход 42 блока, вход 43 разрешения блока, синхровход 44 блока , стробирующий выход 45 блока, адресный выход 46 блока, первый информационный выход 47 блока, с первого по третий управляющие выходы 48-50 блока ср.ответственно, выход 51 выбор ки блока, второй информационный выхо 52блока, третий информационный вход 53блока. Блок управления (фиг, З) содерж 1т триггер 54 передачи данных, группу триггеров 55 и 56 передачи данных каналов, первую группу элементов И 57 и 58, второй 59 и первый 60 элементы ИЛИ, первьш 61 и второй 62 эле менты И, элемент НЕ 63, триггер 64 запроса передачи данных, триггер 65 первого цикла передачи, триггер 66 промежуточного цикла передачи, триггер 67 второго цикла передачи, группу триггеров 68 и 69 второго цикла передачи каналов, вторую группу элементов И 70 и 71, группу элементов И-ИЛИ-НЕ 72 и 73, первый .74 и второй 75 элементы И-ИЛИ, первую группу элементов И-ИЛИ 76 и 77, вторую груп пу элементов И-ИЛИ 78 и 79, первую 80, вторую 81, третью 82 и четвертую 83 группы входов блока, первый 84 и второй 85 входы блока, с первого по пятый входы 86-90 блока соответственно, с первой по третью группы выходов 91-93 соответственно. Блок согласования (фиг. 4) содердит регистр 94 данных, буферную память 95 данных, триггер 96 обраще- НИН интерфейса, триггер 97 выбора буфера интерфейса, счетчик 98 адреса байтов, триггер 99 выбора буфера процессора, триггер 100 номера слова, счетчик 101 двойных слов, первый 102 и второй 103 узлы.синхронизации, коммутатор 104,, узел 105 обмена по интерфейсу, триггер 106 занятости регистра данных, триггер 107 занятос ти группы регистров, регистр 108-код операции, дешифратор 109, первую 110 и вторую 111 группы элементов И-ИЛИ, с первого по шестой элементы И-ИПИ 112-117 соответственно, элемент ИИЛИ-НЕ 118, первый 119 и второй 120 информационные входы блока, информационный вход - выход 121 блока,вход 122 разрешения блока, синхровход 123 блока, информационный выход 124 блока, первый 125 и второй 126 синхровыходы блока, выход 127 запроса блока, выход 128 записи блока, выход 12 чтения блока. Блок приоритета запросов (фиг, 5) содержит с первого по четвертый триггеры 130-133 соответственно, приоритетный шифратор 134, регистр 135 хранения, информационный вход 136 и вы- , ход 137 блока, групповой управляющий вход 138 блока, через который по линиям 139-142 информационные входы триггеров 130-133 соединены соответственно с входом 138 блока, групповой управляющий выход 143; с которым первый, второй и третий выходы приоритетного шифратора соединены соответственно линиями 144-146, групповой вход -147 запросов и групповой выход 148 запросов блока. Блок 18 приоритета запросов работает следующим образом. Группу запросов, принятую из группы блоков 19 согласования на групповой вход 147 запросов блок 18 приоритета запросов транслирует на групповой выход 148 запросов блока. Группа приоритетных сигналов, поступающая с группового входа 138 блока на информационные входы триггеров 130-133, устанавливает эти триггеры в соответствующие состояния.Причем сигнал, поступающий по линии 39 на информационньш вход триггера 130, является самым приоритетным. Так как сигналы, снятые с группового управляющего входа 138 блока, поступают асинхронно на информационные входы триггеров 130-133, то для одновременной установки этих триггеров используется подсинхронизация путем подачи на синхровходы триггеров 130-133 синхроимпульса с синхровхода 21 блока. Выходы триггеров 130-133 подключены к входам (с первого по четвертый) приоритетного шифратора 134, на первом 144 и втором 145 выходах которого формируется двухразрядный код, который является адресом самого приоритетного сигнала четырехразрядного слова, которое поступает на входы триггеров 130-133, Например, если триггер 130 установлен, то с первого- и второго выходов приоритетного шифратора по линиям 144 и 145 будет выдан код ОО, т.е. адрес первого разряда четырехразрядного слова. Если ни один триггер 130133 не введен, то возбуждается третий выход приоритетного шифратора по линии 146, что говорит о том, что ни один триггер 130-133 не взведен. Регистр 135 хранения используется для приема соответствующим синхроимпульсом с синхровхода 21 информации, поступающей с информационного входа 136 блока, и выдачи информации с выхода регистра 135 хранения на информационный выход 137 блока. Блок дешифрации приоритета (фиг,6 содержит шесть мультиплексоров 149154, элемент НЕ 155, дешифратор 156, информационный вход 157 блока, содер жащий линии 158-165. Кроме того, блок микропрограммного управления содержит (фиг. 2) выхо 166 занесения. Блок формирования работает следующим образом. На первые информа- й. ционные входы с первого по четвертьш мультиплексоры 149-152 поступает с группового входа 148 запроса блока сигнал запроса от первого канала группы. На второй, третий и четвертый информационные входы с первого по четвертый мультиплексоры 149-152 поступают с группового входа 148 запроса блока сигналы запросов от второго, третьего и четвертого каналов соответственно. На первый и второй адресные входы первого мультиплексора 149 с информа ционного входа 157 блока по линиям 15 и 159 поступаетС первого и второго выходов регистра выборадвухразрядный код номера канала, для которого уста новлена самая высокая приоритетность На первые и вторые адресные входы второго, третьего и четвертого мультиплексоров 150-152 с информационног входа 157 блока по линиям 160 и 161, 162 и 163, 164 и 165 поступают с тре тьего и четвертого, с пятого и шестого, с седьмого и восьмого выходов регистра выбора соответственно двухразрядные коды номеров каналов, для которых установлены второй, третий и четвертый приоритеты соответственно, Таким образом, с выхода мультиплексора 149 по линии 139 нагрупповой управляющий вход 138 выделяется самый приоритетный сигнал, который может принадлежать первому, второму, третьему или четвертому каналам ввода-вывода. С выхода мультиплексора 152 по линии 142 на групповой управляющий выход 138 выдается сигнал самой низкой приоритетности. Сигналы с выходов мультиплексоров 149-152 по

ния.

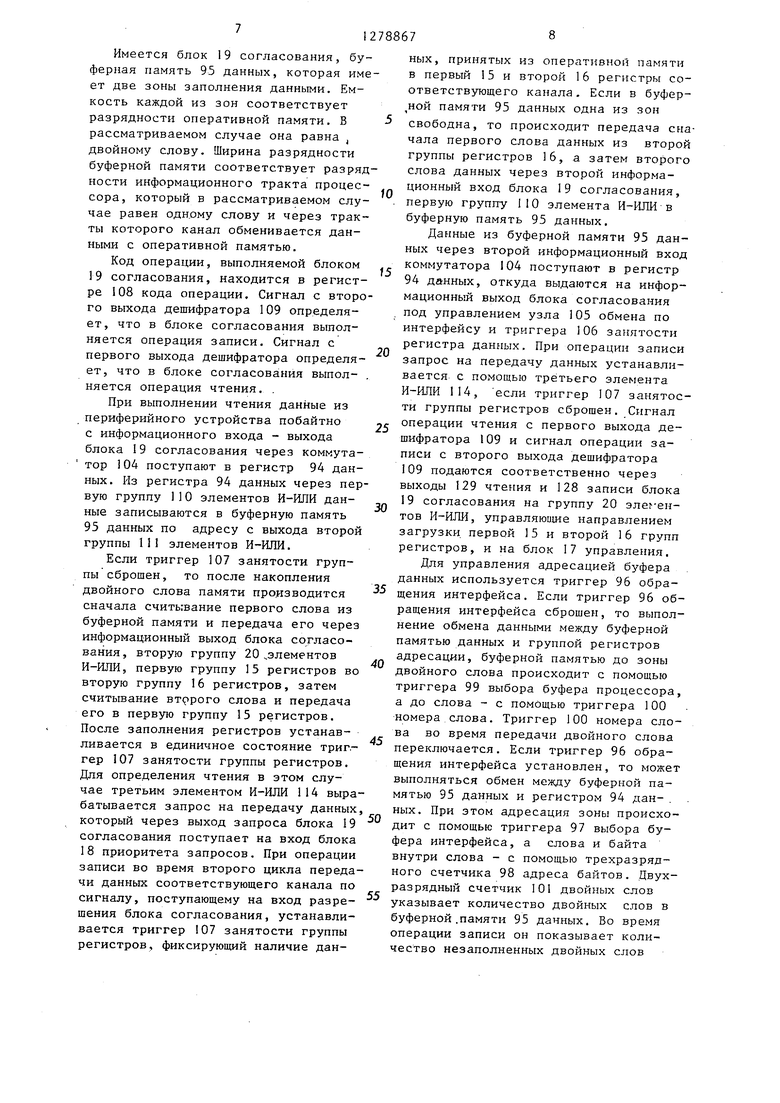

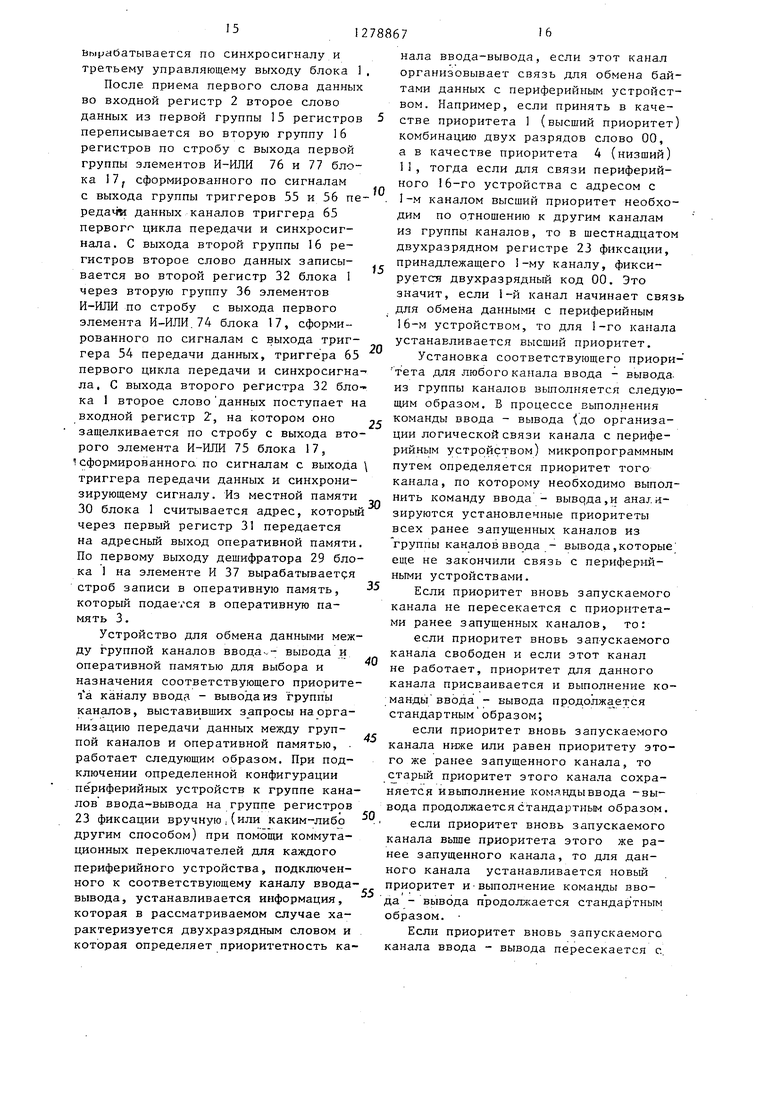

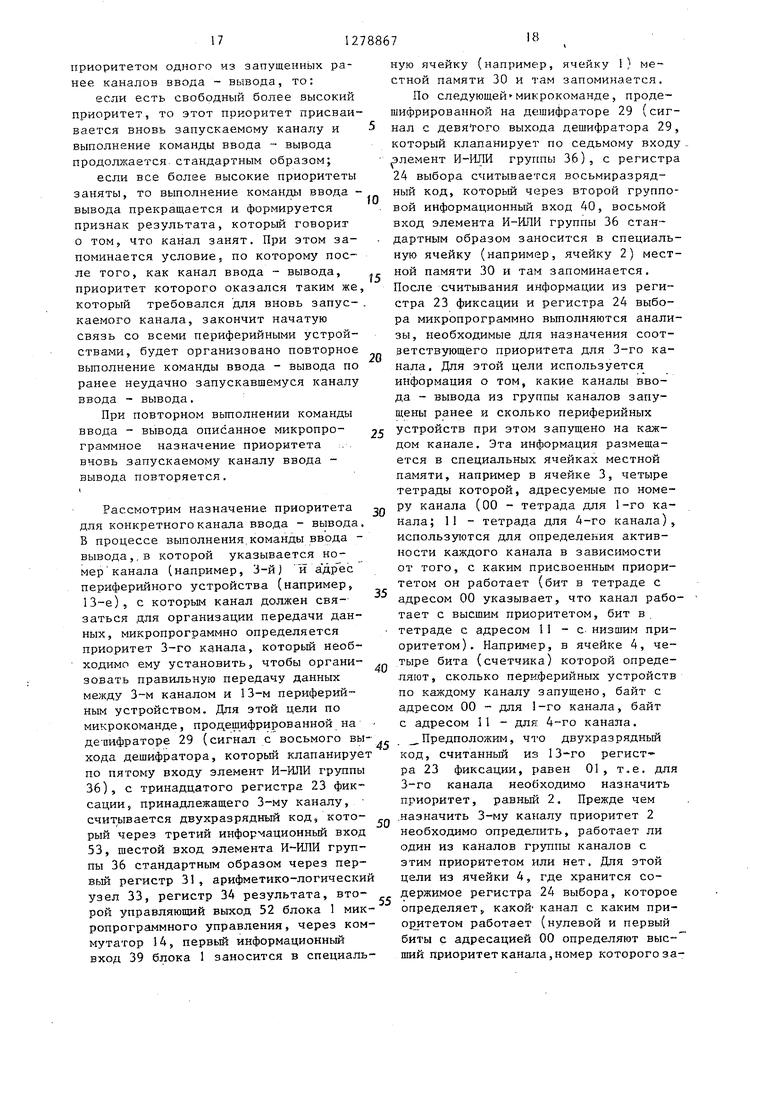

Устройство работает следующим образом. линиям 139-142 соответственно поступают на групповой управляющий вход 138 блока и далее через групповой управляющий вход 138 блока 18 приоритета запросов на информационные входы триггеров 130-133, Таким образом, на первом и втором выходах приоритетного щифратора 134 на линиях 144 и 145 получается двухразрядный код номера самого приоритетного сигнала, которьш сформирован по сигналам запросов от группы каналов , поступивших на информационные входы мультиплексоров 149-152, Первый, второй и третий выходы приоритетного шифратора 134 по линиям 144146 соответственно через групповой управляющий выход I43 блока поступает на групповой управляющий вход 143 блока 25 .формирования. Сигнал по линии 146 поступает на элемент НЕ 155, сигнал с которого поступает на управляющие входы пятого 153 и шестого 554 мультиплексоров, разрешая работу этих мультиплексоров. Сигналы по линиям 144 и 145 поступают на двухразрядные адресные входы пятого 153 и шестого 154 мультиплексоров. На первые информационные входы пятого 153 и шестого 154 мультиплексоров поступают по линиям 158 и 159 соответственно сигналы с первого и второго выходов регистра 24 выбора. На вторые, третьи и четвертые информационные входы пятого 153 и шестого 154 мультиплексоров поступают по линиям 160 и 161, 162 и 163, 164 и 165 сигналы с третьего и четвертого, пятого и шестого, седьмого и восьмого выходов регистра 24 выбора соответственно. Выходы пятого 153 и шестого 154 мультиплексоров подключены к первому и второму входам дешифратора 156. Таким образом, на одном из выходов дешифратора 156 появляется сигнал адреса. Сигнал на первом выходе дешифратора 156 - запрос от первого канала; на втором - от второго канала; на третьем - от третьего канала; на четвертом - от четвертого канала. Полученная с выходов дешифратора 156 информация принимается по синхросигналу в регистр 135 хранения и далее эта информация вьщается через информационный выход 137 в блок 17 управле1Имеется блок 19 согласования, бу ферная память 95 данных, которая име ет две зоны заполнения данными. Емкость каждой из зон соответствует разрядности оперативной памяти. В рассматриваемом случае она равна , двойному слову. Ширина разрядности буферной памяти соответствует разряд ности информационного тракта процессора, который в рассматриваемом случае равен одкому слову и через тракты которого канал обменивается данными с оперативной памятью. Код операции, выполняемой блоком 19 согласования, находится в регистре 108 кода операции. Сигнал с второ го выхода дешифратора 109 определяет, что в блоке согласования выполняется операция записи. Сигнал с первого выхода дешифратора определяет, что в блоке согласования выполняется операция чтения. . При выполнении чтения данные из периферийного устройства побайтно с информационного входа - выхода блока 19 согласования через коммута тор 104 поступают в регистр 94 данных. Из регистра 94 данных через пер вую группу 110 элементов И-ИЛИ данные записываются в буферную память 95 данных по адресу с выхода второй группы 111 элементов И-ИЛИ. Если триггер 107 занятости группы сброшен, то после накопления двойного слова памяти производится сначала считывание первого слова из буферной памяти и передача его через информационный выход блока согласования, вторую группу 20 элементов И-ИЛИ, первую группу 15 регистров во вторую группу 16 регистров, затем считывание слова и передача его в первую группу 15 регистров. После заполнения регистров устанавливается в единичное состояние триг.гер 107 занятости группы регистров. Для определения чтения в этом случае третьим элементом И-ИЛИ 114 выра батывается запрос на передачу данных который через выход запроса блока 19 согласования поступает на вход блока 18 приоритета запросов. При операции записи во время второго цикла переда чи данных соответствующего канала по сигналу, поступающему на вход разрешения блока согласования, устанавливается триггер 107 занятости группы регистров, фиксирующий наличие дан7ных, принятых из оперативной памяти в первый 15 и второй 16 регистры соответствующего канала. Если в буфер ной памяти 95 данных одна из зон свободна, то происходит передача сначала первого слова данных из второй группы регистров 16, а затем второго слова данных через второй информационный вход блока 19 согласования, первую группу 110 элемента И-ИЛИ в буферную память 95 данных. Данные из буферной памяти 95 данных через второй информационный вход коммутатора 104 поступают в регистр 94 данных, откуда выдаются на информационный выход блока согласования под управлением узла 105 обмена по интерфейсу и триггера 106 занятости регистра данных. При операции записи запрос на передачу данных устанавливается с помощью третьего элемента И-ИЛИ 114, если триггер 107 занятости группы регистров сброшен. Сигнал операции чтения с первого выхода дешифратора 109 и сигнал операции записи с второго выхода дещифратора 109 подаются соответственно через выходы 129 чтения и 128 записи блока 19 согласования на группу 20 элегентов И-ШШ, управляющие направлением загрузки первой 15 и второй 16 групп регистров, и на блок 17 управления. Для управления адресацией буфера данных используется триггер 96 обращения интерфейса. Если триггер 96 обращения интерфейса сброшен, то выполнение обмена данными между буферной памятью данных и группой регистров адресации, буферной памятью до зоны двойного слова происходит с помощью триггера 99 выбора буфера процессора, а до слова - с помощью триггера 100 номера слова. Триггер 100 номера слова во время передачи двойного слова переключается. Если триггер 96 обращения интерфейса установлен, то может выполняться обмен между буферной памятью 95 данных и регистром 94 дан- . ных. При этом адресация зоны происходит с помощью триггера 97 выбора буфера интерфейса, а слова и байта внутри слова - с помощью трехразрядного счетчика 98 адреса байтов. Двухразрядный счетчик 101 двойных слов указывает количество двойных слов в буферной.памяти 95 данных. Во время операции записи он показывает количество незаполненных двойных слов 1 в буферной памяти 95 данных, во врем операции чтения - количество заполненных двойных слов, В начале операции записи счетчик устанавливается на 2 (два двойных слова не заполнено) и во время передачи двойного слова из групп 15 и 16 регистров уменьшается. После передачи двойного слова через интерфейс счетчик 101 двойных слов увеличивается. Б начале операции чтения счетчик устанавливается в О и при обмене данными соот ветственно модифицируется. Управление последовательностью работы оборудования блока 19 согласо вания во время передачи данных между буферной памятью 95 данных и регистром 94 осуществляется с помощью второго синхронизатора 103. Управление передачей между буферной памятью 95 данных и группами 15 и 16 регистров производится первым синхронизатором 102. Первый синхронизатор 102 вырабатывает стробы загрузки первой 15 и второй 16 групп регистров соответствующего канала, которые поступают соответственно при передаче данных в буферную память или из буферной памяти на первый и второй синхровходы блока 19 согласования. Запуск второ го син. о.газатора 103 производится через э. V ент И-ИЛИ-НЕ 118, а запуск пе, го синхронизатора 102 через пя и элемент И-ИЛИ 116. Запр сы от всч-х блоков 19 согласования поступают на блок 18 приоритета запросов и далее при помопщ регистра 24 выбора, блока 25 формирования определяется наиболее приоритетный из них и из блока 18 передается в блок 17 управления, в котором устанавливается триггер 54 передачи дан ных и один из группы триггеров 55 и 56 передачи данных каналов, которые указывают, какой блок 19 согласования будет производить обмен дан ными . На вход блока 17 управлен ия на вторую группу входов из блоков 19 согласования поступает код операции который используется для аппаратурного формирования микрокоманды обра щения к оперативной памяти на первой группе элементов И 57 и 58 и вт ром элементе ИЛИ 59, с выхода второ го микрокоманда поступает на вход режима блока 1 микропрограммного уп равления, в регистр 28 микрокоманд 7 через первую группу 35 элементов -ИЛИ. При этом потенциалом с триггера 55 передачи данных блока 17 управления блокируется прием микрокоманд из памяти 26 микрокоманд блока 1 микропрограммного управления на первой группе 35 элементов И-ИЛИ и пропускается команда из блока 17 управления, в ходе выполнения которой должен производиться обмен данными между оперативной памятью и первой 15 и второй 16 группами регистров через внутренние тракты процессора. Для управления прохождением данных блок 17 управления вырабатывает последовательность сигналов с выхода триггера 64 запроса передачи данных, триггера 65 первого цикла передачи, триггера 66 промежуточного цикла передачи, триггера 67 второго цикла передачи, а для управления первой 15 и второй 16 группами регистров с выходов первой группы элементов И-ИЛИ 76 и 77 и второй группы элементов И-ИЛИ 78 и 79. Микрокоманда Память выполняется в два цикла. В первом цикле памяти готовятся адрес данных и в случае записи в память записываемые данные. Чтение и запись производятся в паузе между первым и вторым циклами. Длительность паузы зависит от времени обращения к памяти. Это время намного превосходит первый и второй циклы памяти. Во втором цикле памяти в слу-чае считывания выбираются данные из памяти и пересьшсиотся через внутренние тракты процессора в первую 15 и вторую 16 группы регистров. Триггер 64 запроса передачи данных блока 17 используется для запуска циклов аппаратурно сформированной микрокоманды Память, Блок 18 приоритета запросов , а также регистр 24 выбора и блок 25 формирования предназначены для выбора наиболее приоритетного из каналов. Коммутатор 14 предназначен для выбора данных из оперативной памяти или регистра 34 результата блока 1 микропрограммного управления и представляет собой группу элементов ИИЛИ. На временной диаграмме (фиг. 7) работы устройства для обмена данными между группой каналов вйОда - вывода и оперативной памятью для выполнения микрокоманды Память при обращении к ней процессора приняты следующие обозначения: d- синхронизация; Sприем в первый регистр 31 адреса оперативной памяти; 6- прием двойно го слова данных в выходной регистр 4 I запись в местную память 30 модифицированного адреса оперативной памяти; 5- выдача первого слова, данных с первой группы 5 элементов И-ИЛИ; е- выход третьего триггера 9 тк: - выдача второго слова данных с первой группы 5 элементов И-ИЛИ; з управление коммутатором 14 на выбор данных из оперативной памяти; и - за пись первого слова данных; к - запис второго слова данных. Устройство для обмена данными меж ДУ группой каналов .ввода, - вывода и оперативной памятью для выполнения микрокоманды Память при обращении к ней процессора работает следующим образом. Из памяти 26 микрокоманд блока 1 микропрограммного управления по адресу из регистра 27 адреса чере первую группу 35 элементов И-ИЛИ в регистр 28 микрокоманд заносится мик рокоманда, поступагощая на дешифратор 29, с седьмого выхода которого в местную память 30 подается адрес, по которому на первый регистр 31 считы вается адрес данных оперативной памяти, который через адресньй выход 46 блока 1 микропрограммного управления подается на адресный выход опе ративной памяти. Двойное слово данны из оперативной памяти заносится в вы ходной регистр 4, из которого с помощью первой группы 5 элементов И-ИЛ на коммутатор 14 подается первое сло во данных.. Управление выбором нового слова осуществляется первым элементов И-НЕ 8 по установленному первому триггеру 7, который устанавливается через первый элемент/И 6, по младшему биту адреса двойного слова из первого регистра 31 блока 1 микропрограммного .управления. Адрес данных оперативной памяти подается также на арифметико-логический узел 33, где он модифицируется и через регистр 34 результата и коммутатор 14 записывается в местную память 30. После этого управление коммутатором 14 по выходу второго элемента И 13 переклю чается на выбор первого слова данных из оперативной памяти. После записи первого слова данных по второму выходу дешифратора 29 блока 1 устанавливается третий триггер 9, который инверсным выходом на первом элементе И 6 изменяет младший бит адреса оперативной памяти, который запоминается в конце выполнения микрокоманды Память на первом триггере 7 и через первый элемент И-НЕ 8 изменяет управление первой группы 5 элементов И-ИЛИ на выдачу второго слова данных из выходного регистра 4 на коммутатор 14, а прямой выход третьего триггера 9 управляет передачей этого слова данных через коммутатор 14 на фоне выполнения следующей микропрограммы. На временной диаграмме (фиг. 8) работы устройства для обмена данными между группой каналов ввода - вывода и оперативной памятью для выполнения агшаратурно сформированной микрокоманды Память считывания из оперативной памяти приняты следующие обозначения: а- синхронизация; Б- выход триггера 65 первого цикла передачи; 6- выход триггера 66 промежуточного цикла передачи; г- выход триггера 67 второго цикла передачи; 3прием в первый регистр 31 адреса оперативной памяти и счетчика байтов; е - прием двойного слова данных в выходной регистр 4; эк - выдача первого слова данных с первой группы 5 элементов И-ИЛИ; 3 выдача второго слова данных с первой группы 5 элементов И-ИЛИ; ,ч - выход второго триггера 11;. к - управление коммутатором 14 на выбор данных из оперативной памяти; л - запись в местную память 30 модифицированного адреса оперативнор памяти и счетчика байтов; м- строб первой группы 15 регистров; н - строб второй группы 16 регистров. Устройство для обмена данными между группой каналов и оперативной памятью для считывания данных из оперативной памяти в первую 15 и вторую .16 группы регистров работает следующим образом. Из блока 17 управления в блок 1 микропрограммного управления в регистр 28 микрокоманд заносится аппаратурно сформированная микрокоманда, которая поступает на дешифратор 29, с седьмого выхода которого в местную память 30 подается адрес, по которрму на первый регистр 31 в первом цикле памяти считывается ад- Dfic данных оперативной памяти, который подается иа адресный вход оперативной памяти и на арифметико-логический узел 33, на котором он модифицируется . Из оперативной памяти в выходной регистр А считывается двойное слово данных. Младший бит адреса оперативной памяти, адресующий первое слово данных из первого регистра 31 блока 1 через первый элемент И 6, устанавливает первый триггер 7, который через первый злемент И-НЕ 8 управляет выбором на первой группе 5 элементов И-ИЛИ первого слова данных которое поступает на коммутатор 14. С выхода триггера 54 передачи данных блока 17 управления на информационный вход второго триггера 11 подается сигнал, который устанавливает этот триггер в начале первого цикла микро команды Память, Второй триггер 1 1 управляет передачей через коммутатор 14 первого слова данных оперативной памяти, которое проходит через вторую группу 20 элементов И-ЯЛИ под управлением выхода записи блока 19 согласования и через первую группу 1 регистров, так как на синхронизируюпшй вход подается постоянный строб и защелкивается во второй группе 16 регистров по стробу, сформированному на первой группе элементов И-ИЛИ 76 и 77 блока 17 управления по сигналам с выхода группы триггеров 55 и 56 передачи данных каналов триггера 67 второго цикла передачи и синхросигна ла, Из местной памяти 30 блока 1 микр программного управления во втором цикле памяти на первый регистр 31 считывается счетчик байтов, который указывает то колшчество байтов, которое осталось передать из оперативно ; памяти в каналы. Счетчик байтов передается на арифметико-логический узел 33, на котором он модифицирует ся. После сброса второго триггера 11 управление коммутатором 14 переключа ется на выдачу из регистра 34 резуль тата модифицированного адреса, который записывается в местную память 30 Затем на втором элементе И-НЕ 10 по сигналу с выхода триггера 67 второго цикла передачи блока 17 и сигналу с синхровхода 21 устройства вырабатывается сигнал, который поступает на второй вход первого элемента И-НЕ 8 и инвертирует выходы этого элемента. Таким образом, первая группа 5 элементов И-ИЛИ выбирает второе слово данных, которое через коммутатор 14 под управлением сигнала с выхода второго элемента И 13 поступает через вторую группу 20 элементов И-ИЛИ на первую группу 15 регистров, где оно и защелкивается по стробу, сформированному на второй группе элементов И-ИЛИ 78 по сигналам с выхода группы триггеров 55 и 56 передачи данных каналов, синхросигнала и сигнала с выхода группы триггеров 68 и 69 второго цикла передачи каналов, Запись модифицированного счетчика из регистра 34 результата блока 1 в местную память 30 выполняется на фоне выполнения следующей микрокоманды. На временной диаграмме (фиг. 9) работы устройства для обмена данными между группой каналов ввода - вывода и оперативной памятью для выполнения аппаратурно сформированной команды Память записи в оперативную память приняты следующие условные обозначения: р- синхронизация; 8- выход триггера65 первого цикла передачи; &- выход триггера 66 промежуточного цикла передачи; г- прием в первый регистр 31 адреса оперативной памяти; д прием во второй регистр 32 данных из второй группы 16 регистров; е- прием данных во входной регистр 2; лс- строб второй группы 16 регистров; з запись в оперативную память. Устройство для обмена данными между группой каналов ввода - вывода и оперативной памятью для записи даннь1х из первой 15 и второй 16 групп регистров в оперативную память работает следующим образом. Со второго информационного выхода группы 16 регистров в блок микропрограммного управления во второй регистр 32 через вторую 36 группу элементов И-ИЛИ под управлением сигнала с выхода триггера 54 передачи данных блока 17 управления принимается первое слово данных по стробу с выхода первого элемента И-ИЛИ 74 блока 17 управления, который перерабатывается по синхросигналу. После приема первого слова во второй регистр 32 блока 1 данные через первый информационный выход 47 блока 1 подаются на входной регистр 2, где они принимаются по стробу, сформированному на втором элементе И-ИЛИ 75 блока 17, который Бы1 абатывается по синхросигналу и третьему управляющему выходу блока 1 После, приема первого слова данных во входной регистр 2 второе слово данных из первой группы 15 регистров переписывается во вторую группу 16 регистров по стробу с выхода первой группы элементов И-ИЛИ 76 и 77 блока 17, сформированного по сигналам с выхода группы триггеров 55 и 56 пе редачи данных каналов триггера 65 первог цикла передачи и синхросигнала. С выхода второй группы 16 регистров второе слово данных записывается во второй регистр 32 блока 1 через вторую группу 36 элементов И-ИПИ по стробу с выхода первого элемента И-ИЛИ.74 блока 17, сформированного по сигналам с выхода триггера 54 передачи данных, триггера 65 первого цикла передачи и синхросигна ла, С выхода второго регистра 32 бло ка 1 второе словоданных поступает н входной регистр 2, на котором оно защелкивается по стробу с выхода вто рого элемента И-ИЛИ 75 блока 17, 1 сформированного по сигналам с выхода триггера передачи данных и синхронизирующему сигналу. Из местной памяти 30 блока 1 считывается адрес, которы через первый регистр 31 передается на адресный выход оперативной памяти По первому выходу дешифратора 29 бло ка 1 на элементе И 37 вырабатывает(;я строб записи в оперативную память, который подаеуся в оперативную память 3. Устройство для обмена данными меж ду группой каналов ввода--- вывода и оперативной памятью для выбора и назначения соответствующего приорите каналу ввод - вывода из группы каналов, выставивших запросы на организацию передачи данных между группой каналов и оперативной памятью, работает следующим образом. При подключении определенной конфигурации периферийных устройств к группе каналов ввода-вывода на группе регистров 23 фиксации вручную,(или каким-либо другим способом) при помощи коммутационных переключателей для каждого периферийного устройства, подключенного к соответствующему каналу вводавывода, устанавливается информация, которая в рассматриваемом случае характеризуется двухразрядным словом и которая определяет приоритетность канала ввода-вывода, если этот канал организовывает связь для обмена байтами данных с периферийным устройством. Например, если принять в качестве приоритета 1 (высший приоритет) комбинацию двух разрядов слово 00, а в качестве приоритета 4 (низший) 11, тогда если для связи периферийного 16-го устройства с адресом с I-м каналом высший приоритет необходим по отношению к другим каналам из группы каналов, то в шестнадцатом двухразрядном регистре 23 фиксации, принадлежащего 1-му каналу, фиксируется двухразрядный код 00. Это значит, если 1-й канал начинает связь для обмена данными с периферийным 16-м устройством, то для 1-го канала устанавливается высший приоритет. Установка соответствующего приоритета для любого канала ввода - вывода, из группы каналов выполняется следующим образом. В процессе выполнения команды ввода - вывода (до организации логической связи канала с периферийным устройством) микропрограммным путем определяется приоритет того канала, по которому необходимо выполнить команду ввода - выв9да,и ана/.изируются установленные приоритеты всех ранее запущенных каналов из группы каналов ввода - вывода,которые еще не закончили связь с периферийными устройствами. Если приоритет вновь запускаемого канала не пересекается с приоритетами ранее запущенных каналов, то: если приоритет вновь запускаемого канала свободен и если этот канал не работает, приоритет для данного канала присваивается и выполнение команды/ввода - вывода пррд. стандартным образом; если приоритет вновь запускаемого канала ниже или равен приоритету этого же ранее запущенного канала, то старый приоритет этого канала сохраняется ивьшолнение комаьщыввода -выода продолжается стандартным образом, если приоритет вновь запускаемого канала вьшзе приоритета этого же ранее запущенного канала, то для даного канала устанавливается новый риоритет и-выполнение команды ввоа - вывода продолжается стандартным бразом. Если приоритет вновь запускаемого анала ввода - вывода пересекается с приоритетом одного из запущенных ранее каналов ввода вывода, то: если есть свободный более высокий приоритет, то этот приоритет присваи вается вновь запускаемому каналу и выполнение команды ввода - вырода продолжается, стандартным образом; если все более высокие приоритеты заняты, то выполнение команды ввода вывода прекращается и формируется признак результата, который говорит о том, что канал занят. При этом запоминается условие, по которому после того, как канал ввода - вывода, приоритет которого оказался таким же который требовался для вновь запускаемого канала, закончит начатую связь со всеми периферийными устройствами, будет организовано повторное вьтолнение команды ввода - вывода по ранее неудачно запускавшемуся каналу ввода - вывода. При повторном вьшолнении команды ввода - вывода описанное микропрограммное назначение приоритета вновь запускаемому каналу ввода вывода повторяется. Рассмотрим назначение приоритета для конкретного канала ввода - вывода В процессе выполнения.команды ввода вывода,,в которой указывается номер канала (например, З-й) и адрес периферийного устройства (например, 13-е), с которым канал должен связаться для организации передачи данных, микропрограммно определяется приоритет 3-го канала, который необходимо ему установить, чтобы организовать правильную передачу данных между 3-м каналом и 13-м периферийным устройством. Для этой цели по микрокоманде, продешифрированной на де-пифраторе 29 (сигнал с восьмого вы хода дешифратора, который клапанируе по пятому входу элемент И-ИЛИ группы 36), с тринадцатого регистра 23 фиксации, принадлежащего 3-му каналу, считывается двухразрядный код, который через третий информациоиньш вход 53, шестой вход элемента И-ИЛИ груп пы 36 стандартным образом через первый регистр 31, арифметико-логически узел 33, регистр 34 результата, вто рой управляюпщй выход 52 блока 1 ми ропрограммного управления, через ко мутатор 14, первый информационный вход 39 блока 1 заносится в специал ную ячейку (например, ячейку 1} местной памяти 30 и там запоминается. По следующеймикрокоманде, продешифрированной на дешифраторе 29 (сигнал с девягого выхода дешифратора 29, который клапанирует по седьмому входу лемент И-ИЛИ группы 36), с регистра 24 выбора считывается восьмиразрядный код, который через второй групповой информационный вход 40, восьмой вход элемента И-ИЛИ группы 36 стандартным образом заносится в специальную ячейку (например, ячейку 2) местной памяти 30 и там запоминается. После считывания информации из регистра 23 фиксации и регистра 24 выбора микропрограммно выполняются анализы, необходимые для назначения соответствующего приоритета для 3-го канала. Для этой цели используется информация о том, какие каналы ввода - вывода из группы каналов запущены ранее и сколько периферийных устройств при этом запущено на каждом канале. Эта информация размещается в специальных ячейках местной памяти, например в ячейке 3, четыре тетрады которой, адресуемые по номеру канала (00 - тетрада для 1-го канала; 11 - тетрада для 4-го канала), используются для определения активности каждого канала в зависимости от того, с каким присвоенным приоритетом он работает (бит в тетраде с адресом 00 указывает, что канал работает с высшим приоритетом, бит в. тетраде с адресом 11 - с. низшим приоритетом). Например, в ячейке 4, четыре бита (счетчика) которой определяют , сколько периферийных устройств по каждому каналу запущено, байт с адресом 00 - для 1-го канала, байт с адресом 11 - для 4-го канала. Предположим, что двухразрядный код, считанный из 13-го регистра 23 фиксации, равен 01, т.е. для 3-го канала необходимо назначить приоритет, равный 2. Прежде чем .назначить 3-му каналу приоритет 2 необходимо определить, работает ли один из каналов группы каналов с этим приоритетом или нет. Для этой цели из ячейки 4, где хранится содержимое регистра 24 выбора, которое определяет, какой канал с каким приО1зитетом работает (нулевой и первый биты с адресацией 00 определяют вые- пмй приоритетканапа,номер которого записан в этих битах; шестой и седьмой биты с адресацией 11 определяют низший приоритет канала, номер которого записан в этих битах), по адресу, который определяется приоритетом для 3-го канала, т.е. по адресу 01, выде ляются второй и третий биты содержимого регистра 24 выбора. По этим битам, которые являются номером канала из ячейки 2 местной памяти выбирается соответствующая тетрада, в которой анализируется бит активности, соответствующий приоритету 2, т.е. бит активности с адресом 01. В зависимости от результата анализа вьшолняются следзпощие действия. 1.Канал, номер которого указан во втором, и третьем битах содержимог регистра 24 выбора, не работает. Выполняется анализ всех битов активнос ти тетрады для 3-го канала. A.3-й канал не работает. Во второй и третий биты регистра 24 выбора (ячейка 4 местной памяти) заносится номер вновь запускаемого канала 10, что говорит о том, что 3-му каналу присвоен приоритет 2; в тетраде - (ячейка 3 местной памяти) для 3-го канала бит по адресу 01 устанавливается- в I, т.е. 3-й канал становится активным по приоритету 2; в счетчик по адресу 10 (ячейка 4 местной памяти), принадлежащий 3-му каналу, добавляется 1, т.е. фиксируется, что по 3-му каналу запущено одно периферийное устройство. Б. 3-й канал работает, и его приоритет выше или равен приоритету вновь запускаемого 3-го канала. Приоритет 3-го канала не изменяется. В счетчик 3 (адрес 10) добавляется 1 т.е. фиксируется, что по 3-му каналу запущено еще одно периферийное устройство . B.3-й канал работает, и его приоритет ниже приоритета вновь запускаемого 3-го канала. Приоритет канала устанавливается новый. Активность 3-го канала по старому приоритету снимается и устанавливается активность 3-го канала с присвоенным приоритетом 2. В счетчик 3 (адрес 10 добавляется 1, т.е. фиксируется, что по 3-му каналу запущено еще одно .периферийное устройство. 2.Канал, номер которого указан во втором и третьем битах содержимого регистра 24 выбора, работает. 3-й канал не работает. В этом случае анализируется, есть ли свободные, более высокие приоритеты, в частности свободен ли приоритет 1. Это вьтолняется путем анализа активности того канала, номер которого определяется содержимым нулевого и первого битов регистра 24 выбора (ячейка 2 местной памяти). А. Ни один канал с приоритетом 1 не работает, В нулевой и первый биты содержимого регистра 24 выбора заносится номер вновь запускаемого канала (10), что говорит о том, что 3-му, каналу присвоен приоритет 1; в тетраде 3 по адресу 00 устанавливается бит активности 3-го канала, т.е. 3-й канал становится активным по приоритету I ; в счетчик 3-го канала добавляется 1, т.е. фиксируется, что по 3-му аналу запущено одно периферийное устройство. Б. Один из каналов с приоритетом I работает. Выполнение команды ввода - вывода прекращается. Микропро- граммно формируется признак результата,который говорит о том,что по 3-му каналу 13-е периферийное устройство запустить нельзя. Вместе с этим в местной памяти запоминается информация о том, что по 3-му каналу с приоритетом 2 выполнение команды ввода - вывода было безуспешным. Эта информация в дальнейшем анализируется каждый раз, когда один из каналов группы каналов ввода - вывода освобождается. Если канал, закончивший работу, имеет приоритет выше или одинаковый (в рассматриваемом случае приоритеты 1 или 2), то по 3-му каналу микропрограммно формируется прерывание, по которому повторно выполняется попытка запуска 13-го периферийного устройства по 3-му каналу. Информация , запомненная в местной памяти о безуспешной попытке запуска 13-го периферийного устройства по 3-мз каналу, при этом уничтожается. 3. Канал, номер которого указан во втором и третьем битах содержимого регистра 24 выбора, работает. 3-й канал также работает. В этом случае анализируется установленный приоритет для 3-го канала. Это выполняется путем выявления в тетраде 3 адреса установленного бита активности 3-го канала (ячейка 3 местной памяти). А, Для 3-го канала установлен такой же или более высокий нриоритет, чем TOTj который трабуется для вновь запускаемого периферийного устройства по 3-му каналу. В этом случае в счетчик 3 (ячейка 4 местной памяти) З-го канала добавляется 1, т.е. фиксируется; что по 3-му каналу запуа ено еще одно устройство. Б. Для канала установлен более низкий приоритет,, чем тот, который требуется для вновь запускаемого 13-то устройства по 3-му каналу. Анализируется-,, свободен ли более высокий приоритет, чем тот, который требуется для вновь запускаемого 3 го канала (в рассматриваемом случае приоритет 1 .) Если он свободен,, 3-му каналу присваивается приоритет 1, бит активности но более низкому приорите ту сбрасывается у а бит активности 3--ГО канала в тетраде 3 по приоритету 1 устанавливается. Если приоритет 1 занят, выполняет ся описанный подпункт Б 2-го пункта. После присвоения 3-му каналу нужного приоричета содержимое регистра 24 выбора из ячейки 2 местной памяти 30 перепршывается в регистр 24 выбора. Пересылка выпо1П яется микропрограммно стандартным образом через элемент И-ИЛИ группы 36 и далее чере первый регистр 31, арифметико-логический узел 33, регистр 34 результата, второй управляюший выход 52, ком мутатор 14, с выхода которого информация ПС сигналу с десятого выхода дешифратора 29 через выкод 166 занесения записывается в регистр 24 выбора . После присвоения нужного приорите та каналу ввода - вывода и записи информации в регистр 24 выбора и в слу ,,е возникновения запросов от группы каналов ввода - выво,цана обмен данны ми с оперативной памятью выбор наибо лее приоритетного на данный момент времени канала из группы каналов выполняется на мультиплексорах 149-152 путем подачи на адресный вход мульти плексора 149 но линиям 158 и 159 управляющих сигналов с нулевого и пер вого выходов periicTpa 24 выбора; н.а адресный вход мультиплексора 150 по линиям 160 и 161 - с второго и третьего выходов регистра 24 выбора; на адресный вход мультинлексора 151 но линиям J62 и 163 -- с четвертого и пя того выходов регистра 24 выбора; на адресный вход, мультиплексора 152 по линиям 164 и 165 с шестого и седьмого выходов регистра 24 выбора. Таким образом, сигнал запроса с выхода мультиллексора 149 (линия 139) имеет всегда самый высокий приоритет, а сигнал запроса с выхода мультинлексора 52 (линия 142) имеет всегда самый низкий приори7 ет, В блоке 18 приоритета запросов стандартным образом выбирается наиболее приоритетный запрос из всех запросов , выставленг ых грешной каналов ввода - вывода, при помоши триггеров 130-1 33и приорите:тного шифратора 134. При этом с первого и второго выходов приоритетного шифратора 134 снимается номер о,г,ного из мул)зтиплексорОЕ 149-152, снгнал занроса с выхода которого на момент ггриема запросов на триггеры 130-133 но сипхрои пульсу подсинхронизации, поступающего на синхровходы триггеров 130-133 с синхроззхода 21 5 являете самым приоритетньи„ Для определения, какому каь:алу ввода - выБО,цз принадлежит самый приоритетньй запрос, используются два мультиплексора 153 и 154 и дешифратор 156. Па первые входы мультиплексоров 153 и 154 подается линиям 158 и 159 соответственно помер того канала, который подается на адресные ,входы мультиплексора 149, на вторые входы мультиплексоров 153 и 154 соответственно номер того канала, ко торый подается на адресный вход мультиплексора и т.д. Таким образом,, с . выходов муль-типле.тссоров , 1 53 и 154 снимается номер того канала, запрос которого на данньп- момент времени является самым приоритетньм. Этот номер санала дешифр -1руется на -дешифраторе 156, с выходов которого снимается один ИЗ сигналов запроса; с первого выхода - для первого канала, с Второго выхода - для второго канала и т,д. Эти ,запросл запоминаются по синхроимпульсу в регистре 135 хранения, с выхода которого запросы по информационному выходу 137 поступают в блок 17Управлеиия и там обрабатываются стандартным образом. Ф о р м у Устройство для обмена данными между группой каналов внода-вывода и

оперативной памятью по авт. св. № 1190385, отличающееся тем, что, с целью увеличения пропускной способности устройства за счет организации возможности присвоения любого приоритета любому каналу ввода-вывода из группы на момент вьшолнения этим канапом операции вводавывода, в него введены группа регистров фиксации, регистр выбора, блок дешифрации приоритета, причем выходы регистров фиксации группы соединены с третьим входом логических условий блока микропрограммного управления, выход занесения которого соединен с

I fj I-LU

входом записи регистра выбора, информационный вход которого соединен с выходом коммутатора, второй вход логических условий блока микропрограммного управления соединен с выходом регистра выбора и с информационным входом блока дешифрации приоритета, информационный выход которого соединен с информационным входом блока приоритета запросов, группа выходов запроса, группы управляющих входов и выходов которого соединены с группой входов запроса,группами управляющих выходов и входов блока дешифрации приоритета соответственно.

W

.m

сГ

n.::3ft TL J ri

j .U I . I ,.J . ,..

5f

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для управления каналами | 1979 |

|

SU877519A1 |

| Устройство для управления каналами | 1974 |

|

SU520592A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Устройство управления каналами | 1972 |

|

SU545983A1 |

| Процессор ввода-вывода | 1979 |

|

SU798782A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для управления каналами | 1984 |

|

SU1372329A2 |

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке процессоров, оборудование которых используется для передачи данных между каналами ввода - вывода и оперативной памятью. Целью изобретения является увеличение пропускной способности устройства за счет организации возможности присвоения любого приоритета любому каналу ввода - вывода из группы на момент выполнения этим каналом операции ввода - вывода в зависимости от того, с каким периферийным устройством канал организует пере- дачу данных. Это дает возможность с максимальной эффективностью использовать менее приоритетные каналы за счет возможности подключения к ним тех же периферийных устройств, которые могут подключаться к самому приоритетному каналу ввода - вывода.Устройство содержит блок микропрограммного управления, входной и выходной регистры, две группы элементов И-ШШ, с & два элемента И, три триггера, два элемента И-НЕ, элемент ИЛИ, коммута(Л тор, две группы регистров, блок упс равления, блок приоритета запросов, группу блоков согласования, группу регистров фиксации, регистр отбора, блок дешифрации приоритета. 9 tm. ю | 00 00 о

P8i

./{:

5

Т-4

-15/H-,

:.f

W-Б

Wp-|-iИ

Й

И

f-Я.

n

S

§2.

6ff

OJ

™j,«j

138

Фиг.

фиг. 5

{Я нимрономанда

Wuufiff nQfiflmu naysa i LLH/ па mm и

J V.

1й1}-я fiuHpoH-da

а

6 г

д г т

3

и н fl н н

па пяти

{

5 в г

в ж

Фиг.9

Пауза

| Авторское свидетельство СССР № 1190385, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-23—Публикация

1985-06-07—Подача