2. Устройство по п.1j о т л и ч а- ю щ е е с я тем, что блок микропрограммного -управления содержит память микрокоманд, дешифратор, регистр микрокоманд, местную память, арифметико- логический узел, регистр результата, регистр адреса,четыре регистра,два триггера, две группы элементов И-ШШ три элемента И-ИПИ, три элемента И, элемент И-НЕ, два элемента НЕ, причем выход первого регистра соединен с первым информационным входом ариф- метико-логического узла и является первым управляющим выходом блока микропрограммного управления, выход регистра результата, первый, второй, третий выходы дешифратора являются

.вторым, третьим, четвертым,пятым управляющими выходами блока микропрограммного управления соответственно, группа выходов дешифратора образует группу управляющих выходов блока микропрограммного управления, выход первого элемента И, первый выход вто.рого регистра являются стробирующим выходом и выходом второго блока микропрограммного управления, второй выход второго регистра соединен с вто- рым информационным входом арифметико- логического узла и является адресным выходом блока микропрограммного управления, первый вход первого элемента И-ИЛй является адресным входом блока микропрограммного управления, информационный вход первого триггера соединен с информационным входом второго триггера, с первым входом второго элемента И-ИЛИ, с входом первого элемента НЕ и является входом переключения режима блока микропрограммного управления, первый вход второго элемента соединен с вторым и третьим входами первого элемента И-ИЛИ, с синхровходом регистра результата и является синхровходом блока микропрограммного управления, первый вход элементов И-ИЛИ первой группы является входом режима блока микропрограммного управления, вход элемента И-НЕ соединен с вторым входом элементов И-ИЛИ первой группы, с первым входом элементов И-ИЛИ второй группы и является входом разрешения блока микропрограммного управления, информационный вход местной памяти, второй вход элементов И-ИПИ второй группы, третий вход третьего элемента И-ИЛИ являются первым, вторым, третьим информационными вход ами блока микропрограммного управления соответственно, вход второго элемента НЕ соединен с четвертым входом третьего элемента И-ИЛИ и является потенциальным входом первого цикла блока микропрограммного управления, синхровход первого регистра является стробирующим входом блока микропрограммного управления, при этом в блоке микропрограммного управления информационный вход регистра результат соединен с информационным выходом арифметико-логического узла, запускающий вход которого соединен с четвертым выходом дешифратора, старший разряд группы вькодов которого соединен с вторым входом третьего элемента И, выход которого соединен с нулевым входом первого триггера, единичный и нулевой выходы которого соединены с четвертым и пятым входами первого элемента И-ИПИ соответственно, выход которого соединен с информационным входом третьего регистра, выход которого соединен с вторым входом второго элемента И-ИЛИ, выход которого соединен с информационным входом регистра адреса, выход которого соединен с адресным входом памяти микрокоманд,- информационный выход которой соединен с третьим входом элементов И-ИЛИ первой группы, выходы которых соединены с группой информационных входов регистра микрокоманд, выход которого соединен с информационным входом дешифратора, пятый выход которого соединен с шестым входом первого элемента И-ИЛИ и с вторым входом элемента И, выход которого соединен с информационным входом четвертого регистра, выход которого соединен с третьим входом второго элемента И-ИЛИ, четвертый вход которого соединен с выходом первого элемента НЕ, второй вход пер вого элемента И соединен с шестым выходом дешифратора, седьмой выход которого соединен с адресным входом местной памяти, первый и второй информационные выходы которой соединен с пятым входом третьего элемента И-ИЛИ и третьим входом элементов И-ИЛИ второй группы соответственно, выходы которых соединены с информационными входами второго и первого регистров соответственно, четвертый вход элементов И-Ш1И второй группы соединен с четвертым входом элементов И-ИЛИ первой группы и выходом элемента И-НЕ, шестой вход третьего элемента И-ИЛИ соединен с выходом второго элемента НЕ, нулевой выход второго триггера соединен с третьим входом второго элемента И.

3.Устройство по п.1, о т л и - чающееся тем, что блок анализа содержит три триггера, элемент ИЛИ, элемент И, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ,причем группа входов элемента ИЛ образует группу входов логических условий блока анализа, первый вход элемента И является входом логического условия блока анализа, выход первого триггера является управляющим выходом блока анализа, синхровход второго триггера соединен с синхро- входом третьего триггера, с вторым входом элемента И, с нулевым входом первого триггера и является синхро- входом блока анализа, при этом в блоке анализа единичный вход первого триггера соединен с выходом элемента И, третий вход которого соединен

с выходом третьего триггера, информационный вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с выходом второго триггера, информационный вход которого соединен с выходом элемента ИЛИ и с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.

4,Устройство по п.1,о т л и чающееся тем, что каждый блок формирования сигналов перезаписи группы содержит три триггера, пять элементов И, элемент ИЛИ, причем единичный вход первого триггера и первый вход элемента ИЛИ образуют уста- новочньй вход блока, синхровход второго триггера соединен с первыми входами первого, второго, третьего элементов И, является синхровходом блока, первый вход четвертого элемента И является вторым входом логического условия блока, второй вход четвертого элемента И объединен с первым входом пятого элемента И и является третьим входом логических условий блока, третий вход четвертого элемента И является первым входом логических условий блока, единичньй

и нулевой выходы второго триггера являются выходами перезаписи блока.

выход пятого элемента И является информационным выходом блока, нулевой выход первого триггера соединен с вторым входом пятого элемента И, выход четвертого элемента И соединен с нулевым входом третьего триггера, единичный вход которого соединен с выходом элемента ИЛИ,второй вход которого соединен с вторым входом второго элемента И и с выходом второго триггера, информационный вход которого соединен с выходом первого элемента И, второй вход которого соединен с единичным выходом первого триггера, нулевой вход которого со- . единен с выходом второго элемента И, второй вход которого соединен с единичным выходом первого триггера, нулевой вход которого соединен с выходом второго элемента И, нулевой выход третьего триггера соединен с третьим входом первого элемента И. 5. Устройство по П.1, отличающееся тем, что блок фиксации приоритета содержит приоритетный шифратор, дешифратор, триггер, два элемента И, элемент ИЛИ, группу элементов И, причем группа информационных, входов приоритетного шифратора образует группу информационных входов блока фиксации приоритета, синхровход триггера соединен с первыми входами первого и второго элементов И и является синхровходом блока фиксации приоритета, второй вход второго элемента И является установочньм входом блока фиксации приоритета, выход элемента ИЛИ является адресным выходом блока фиксации приоритета, информационный выход приоритетного шифратора соединен с информционным входом триггера и является выходом переключения режима блока фиксации приоритета, при этом в блоке фиксации приоритета группа входов элемента ИЛИ соединена с выходами элемен- тов И группы, входы которых соединены с группой выходов дешифратора, группа информационных входов соединена с группой информационных выходов приоритетного шифратора, управляющий вход которого соединен с выходом первого элемента И, второй вход которого соединен с нулевым выходом триггера, нулевой вход которого соединен с выходом второго элемента И.

Изобретение относится к вычисли- тельной технике, может быть исполь- зовано при. разработке систем ввода- вывода и является усовершенствовани- ем устройства по авт.св. № 1190385.

Цель изобретения - повьшение производительности за счет организации блочного обмена данными.

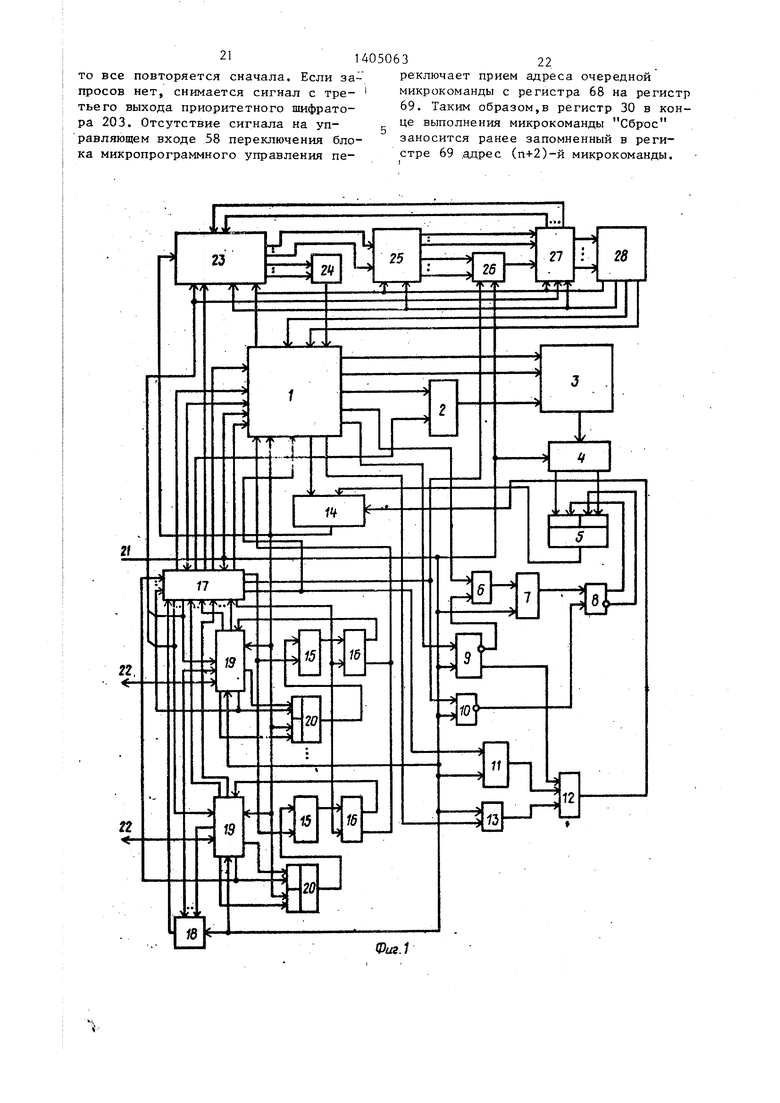

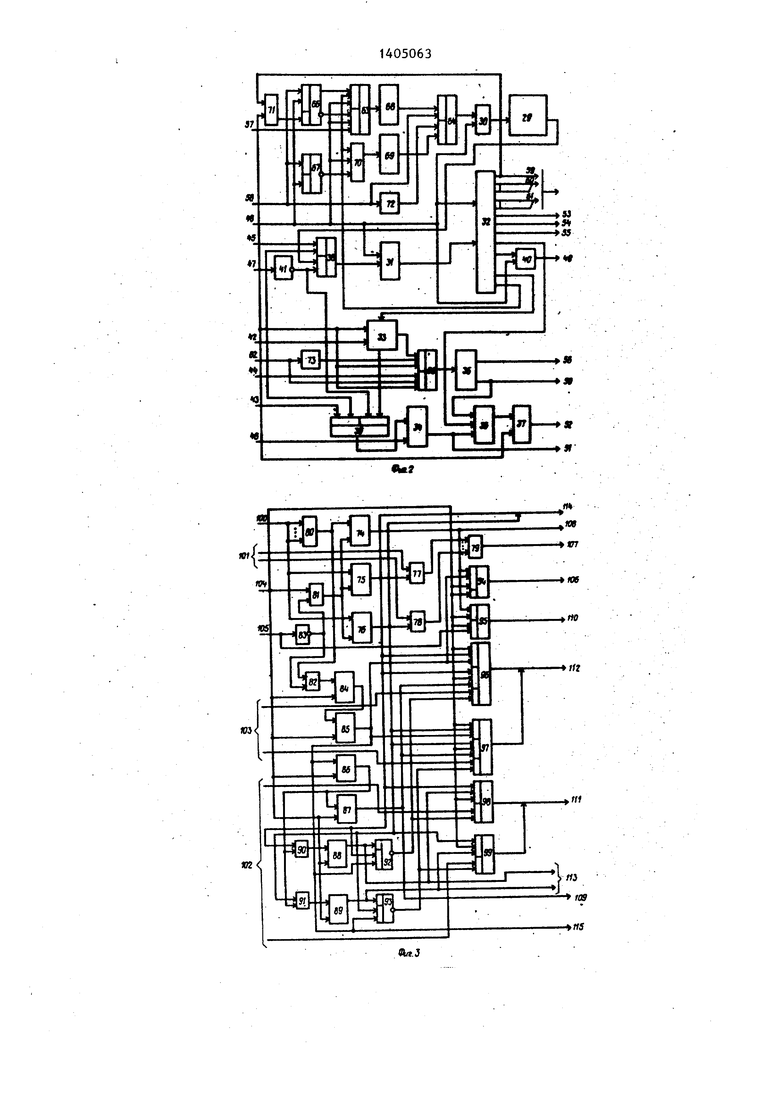

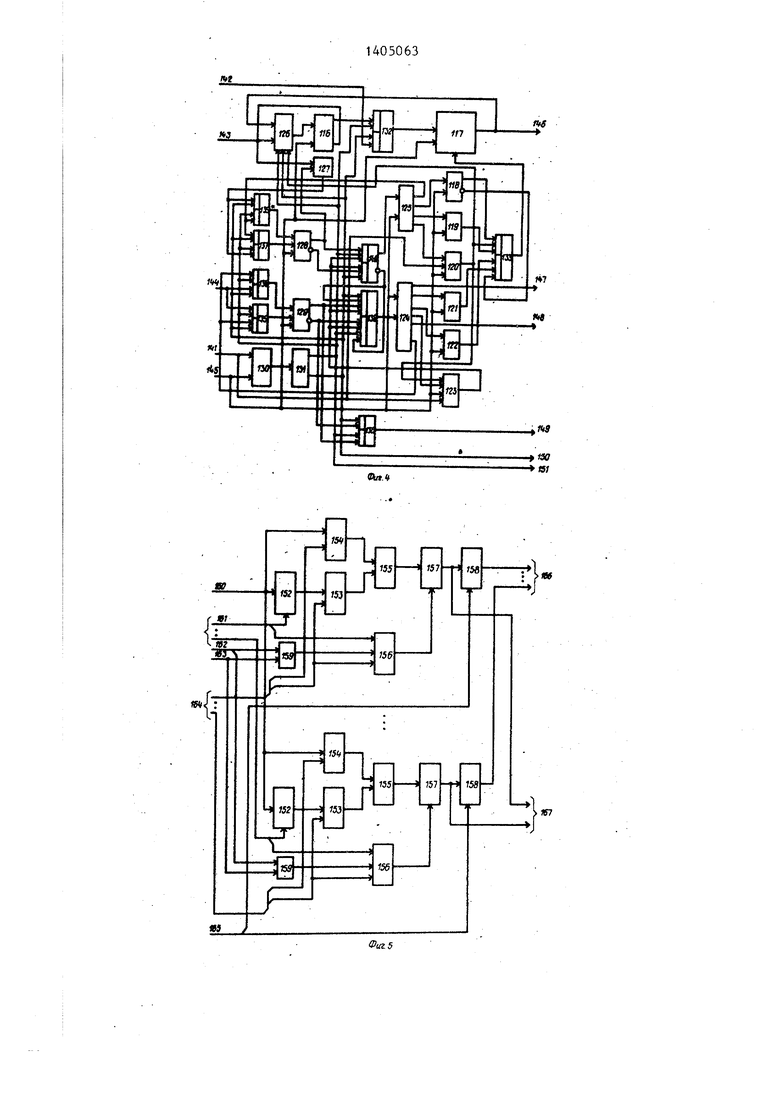

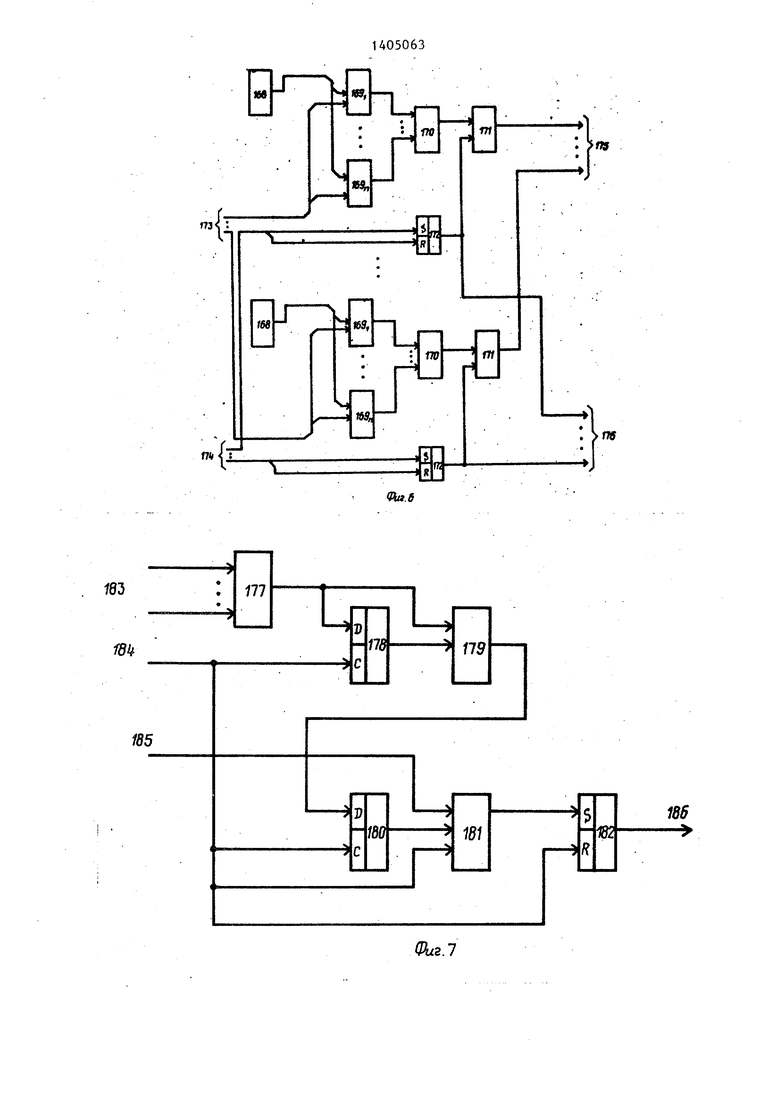

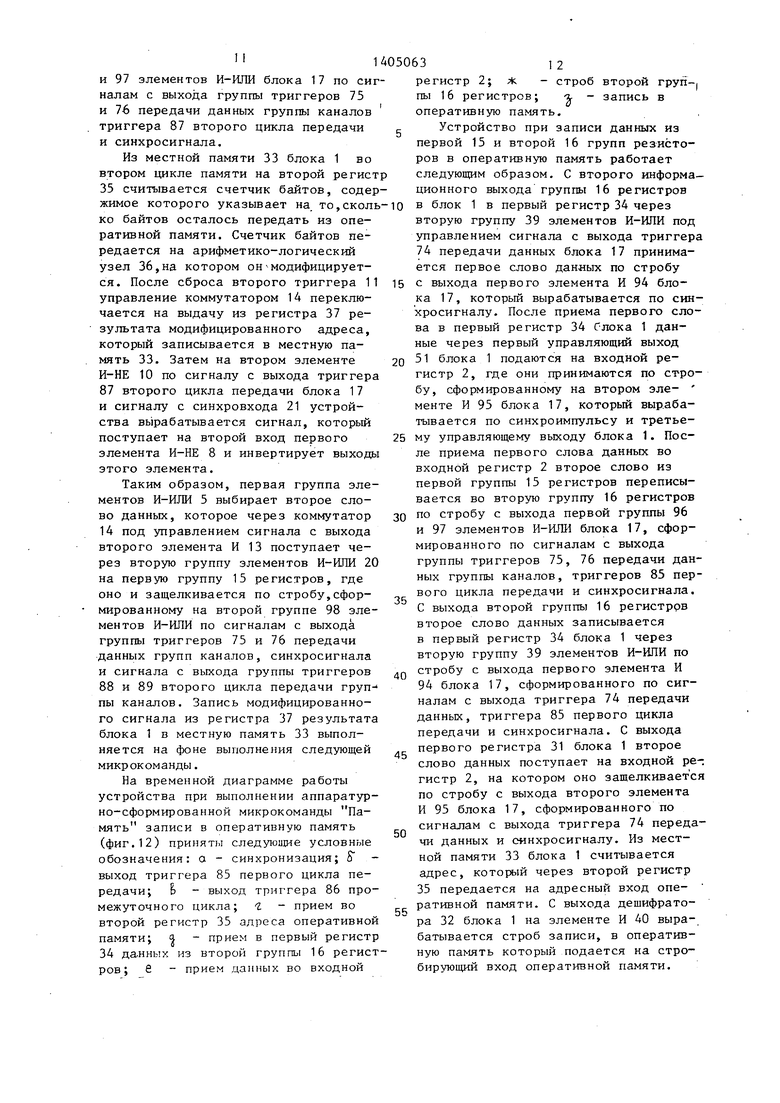

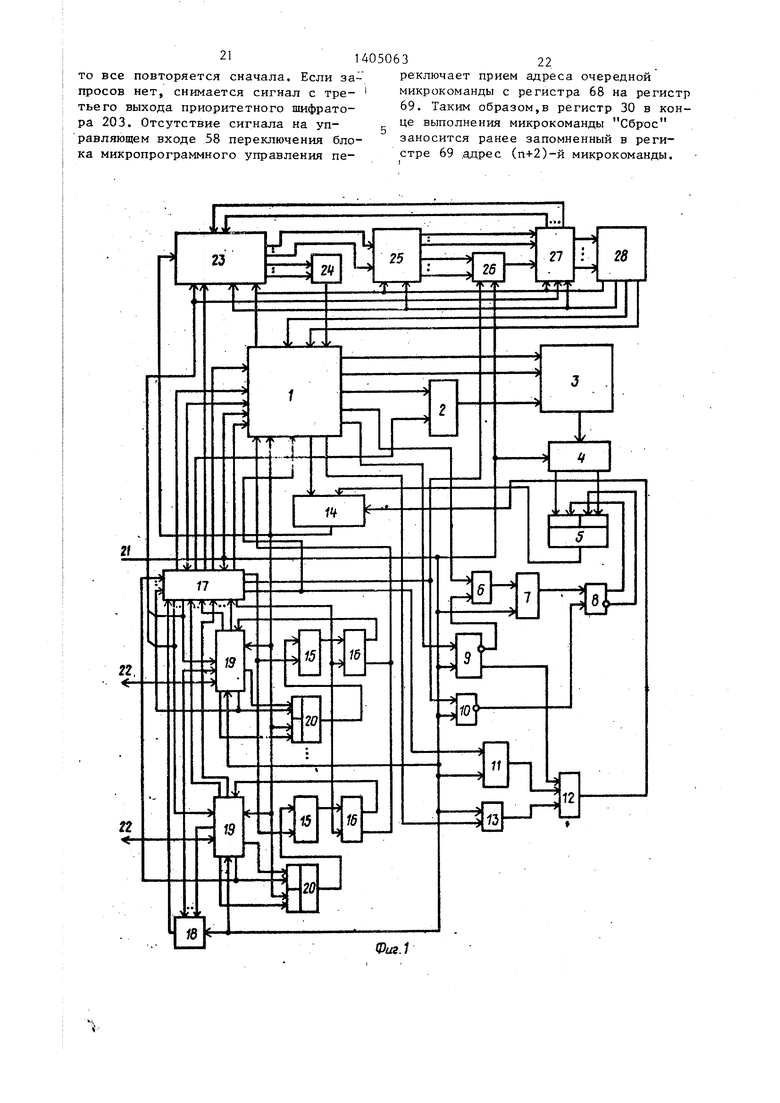

На фиг.1 изображена структурная схема устройства для передачи данных между группой каналов ввода-вывода и оперативной памятью; на фиг.2 - функциональная схема блока, микропрограммного з равления; на фиг.З - функциональная схема блока управления; на фиг.4 - функциональная схема блока согласования; на фиг.5 - функциональная схема группы .блоков регистров; на фиг.6 - функциональная схема группы узлов маски; на фиг.7 - функциональная схема блока анализа;на фиг. 8- фyнкциoнaльнaя схема группы блоков формирования; на фиг.9 - функциональ ная схема блока фиксации;на фиг.10 - временная диаграмма вьшолнения микрокоманды Память при обращении к ней процессора; на г.11 - временная диаграмма выполнения микрокоманды Память считывания из оператив- ной памяти в каналы; на фиг.12 - временная диаграмма выполнения микрокоманды Память записи в оперативную память из каналов;на фиг.13 - временная диаграмма модификации ад- реса и счетчика байтов при организации блочного обмена данными;на фиг, 14 временная диаграмма анализа конца передачи обменного массива, выработки приоритетного сигнала запроса на вы- полнёние микропрограммы замены старого очередного адреса на новый и выполнение этой микропрограммы, содержащей, к примеру, две микрокоманды - Запись Г и Сброс.

Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью содержит блок 1 микропрограммного управления, входной регистр 2, оперативную память 3, выходной регистр 4, первую группу элементов И-ИЛИ 5, первый элемент И 6, первьй триггер 7, первьш элемент И-НЕ 8, третий триггер 9, второй элемент И-НЕ 10, второй триггер 11, элемент ИЛИ 12, второй элемент И 13, коммутатор 14, первую 15 и вторую 16 группы регистров, блок 17 управления блок 18 приоритета запросов, группу

блоков 19 согласования, вторую группу элементов И-ИЛИ 20, синхровход Z1 устройства, группу информационных входов-выходов 22 устройства, группу 23 блоков регистров, элемент ИЛИ 24, группу 25 узлов маски, блок 26 анализа 5 группу 27 блоков формирования сигналов перезаписи, блоки 28 фиксации приоритета.

Блок 1 микропрограммного управления содержит память 29 микрокоманд, регистр 30 адреса, регистр 31 микрокоманд, дешифратор 32, местную память 33, fiepBbm 34 и второй 35 регистры, арифметико-логический узел 36, регистры 37 результата, первую 38 и вторую 39 группы элементов И-ШШ, первый элемент И 40, элемент И-НЕ 41, первый 42, второй 43 и третий 44 информационные входы блока, вход 45 режима блока, стробирующий вход 46 блока, вход 47 разрешения блока, синхровход 48 блока, стробирующий вы- ход 49 блока, адресный выход 50 блока, первый 51 и второй 52 управляющие выходы блока, третий 53, четвертый 54 и пятый 55 управляющие выходы блока, выход 56 выборки блока, адресный вход 57 блока, вход 58 переключения режима блока, группу управляющих выходов 59-61, потенциальный вход 62 первого цикла, элементы И-ИЛИ 63-65, первьй 66 и второй 67 триггеры, третий 68 и четвертый 69 регистры, второй 70 и третий 71 элементы И,первый 72 и второй 73 элементы НЕ.

Блок 17 управления (фиг.З) содержит триггер 74 передачи данных, группу триггеров 75 и 76 передачи дан- ньк группы каналов, первую группу элементов И -77 и 78, второй 79 и первый 80 элементы ИЛИ, первый 81 и второй 82 элементы И,элемент НЕ 83,триггер 84 запроса, передачи данных,триггер 85 первого цикла передачи, триггер 86 промежуточного цикла передачи, триггер 87 второго цикла передачи, группу триггеров 88 и 89 второго цикла передачи группы каналов, вторую группу элементов 90 и.91, группу элементов И-ИЛИ-НЕ 92 и 93, первый 94 и второй 95 элементы И, первую группу 96 и 97 элементов И-ИЛИ, вторую группу 98 и 99 элементов И-ИПИ, с первой по четвертую группы входов 100-103 блока соответственно, первый 104 и второй 105 входы блока, с первого по пятый выходы 106-1 ТО блока

31

соответственно, с первой по третью группы выходов 111-113 соответственно, четвертую группу выходов 114, шестой выход 115.

Блок 19 согласования (фиг.4) содержит регистр 116 данных, буферную память 117 данных, триггер 118 обращения интерфейса, триггер 119 выбора буфера интерфейса, счетчик 120 адреса байтов, триггер 121 выбора буфера процессора, триггер 122 номера слова, счетчик 123 двойньк слов, первый 124 и второй 125 узлы синхронизации, коммутатор 126, узел 127 обмена по интерфейсу, триггер 128 занятости регистра данных, триггер 129 занятости группы регистров, регистр 130 кода операции, дешифратор 131, первую 132 и вторую 133 группы элементов И-Ш1И с первого по шестой элементы И-ИЛИ 134-139 соответственна, элемент И-ИЛИ-НЕ 140,первый 141 и второй 142 информационные входы блока, информационный вход-выход 143 блока, вход 144 разрешения блока, синхровход 145 блока, информационный выход 146 блока, первый 147 и второй 148 синхровходы блока, выход 149 запроса блока, выход 150 записи блока, выход 151 чтения блока.

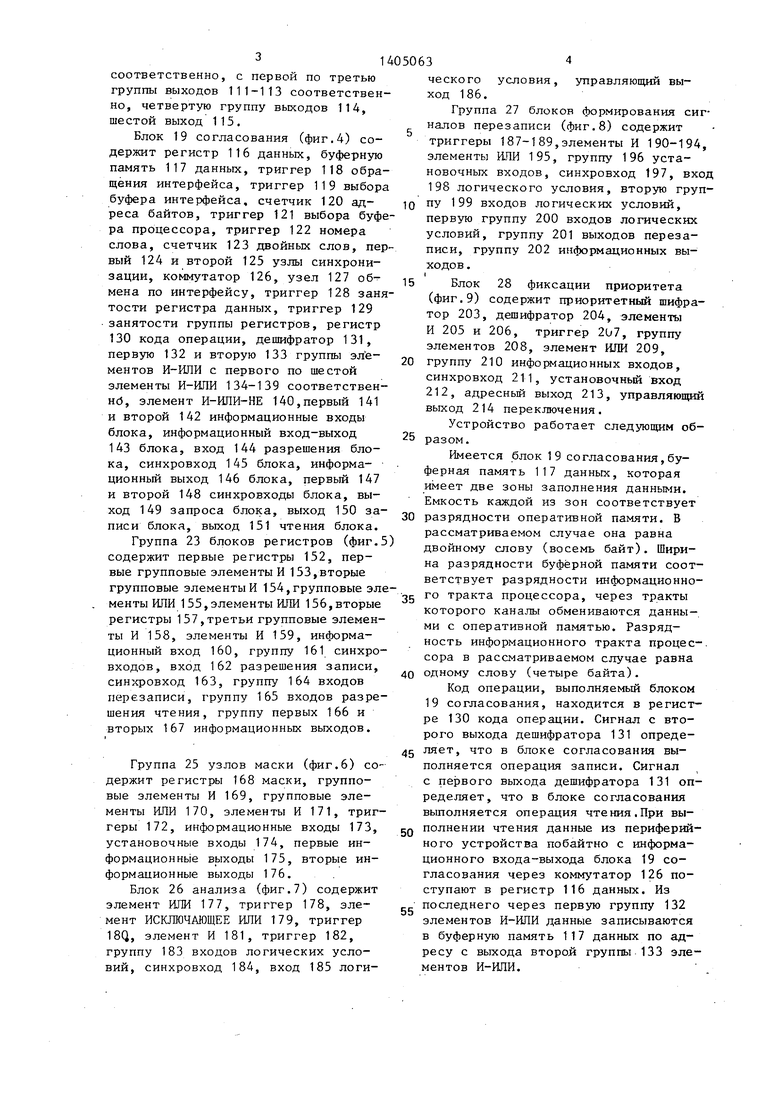

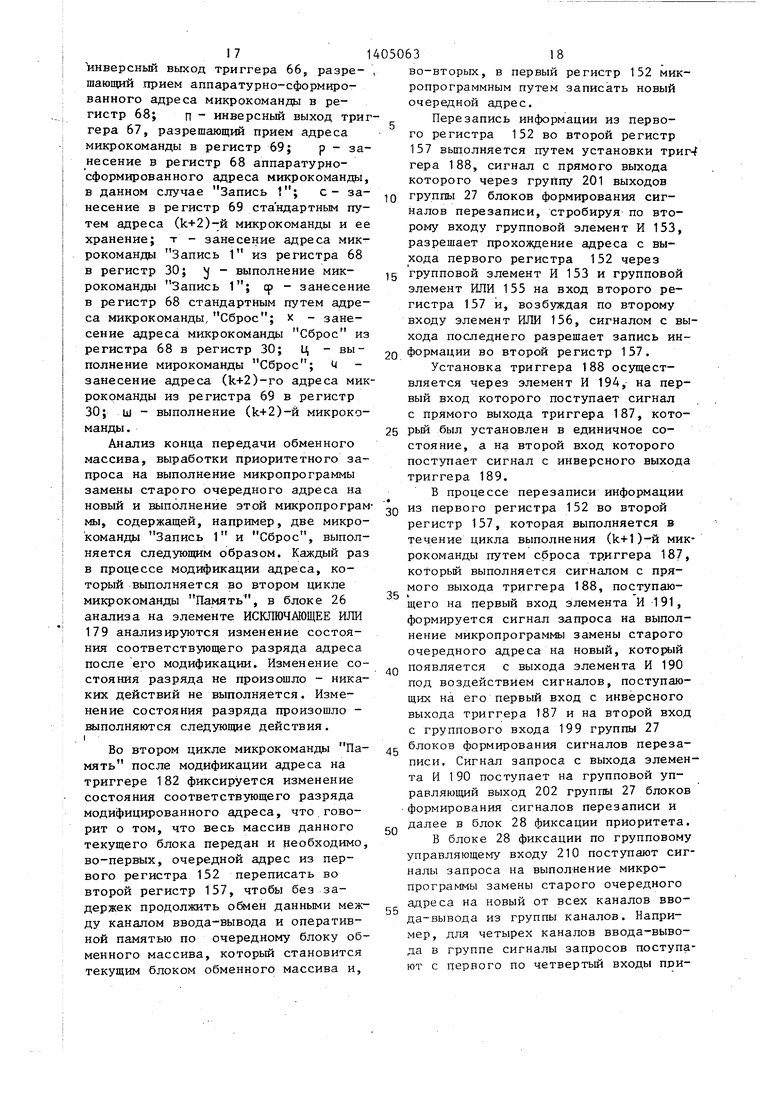

Группа 23 блоков регистров (фиг,5 содержит первые регистры 152, первые групповые элементы И 153,вторые групповые элементы И 154, групповые элементы ИЛИ 155,элементы ИЛИ 156,вторые регистры 157,третьи групповые элементы И 158, элементы И 159, информационный вход 160, группу 161 синхро- входов, вход 162 разрешения записи, синзфовход 163, группу 164 входов перезаписи, группу 165 входов разрешения чтения, группу первых 166 и вторых 167 информационных выходов.

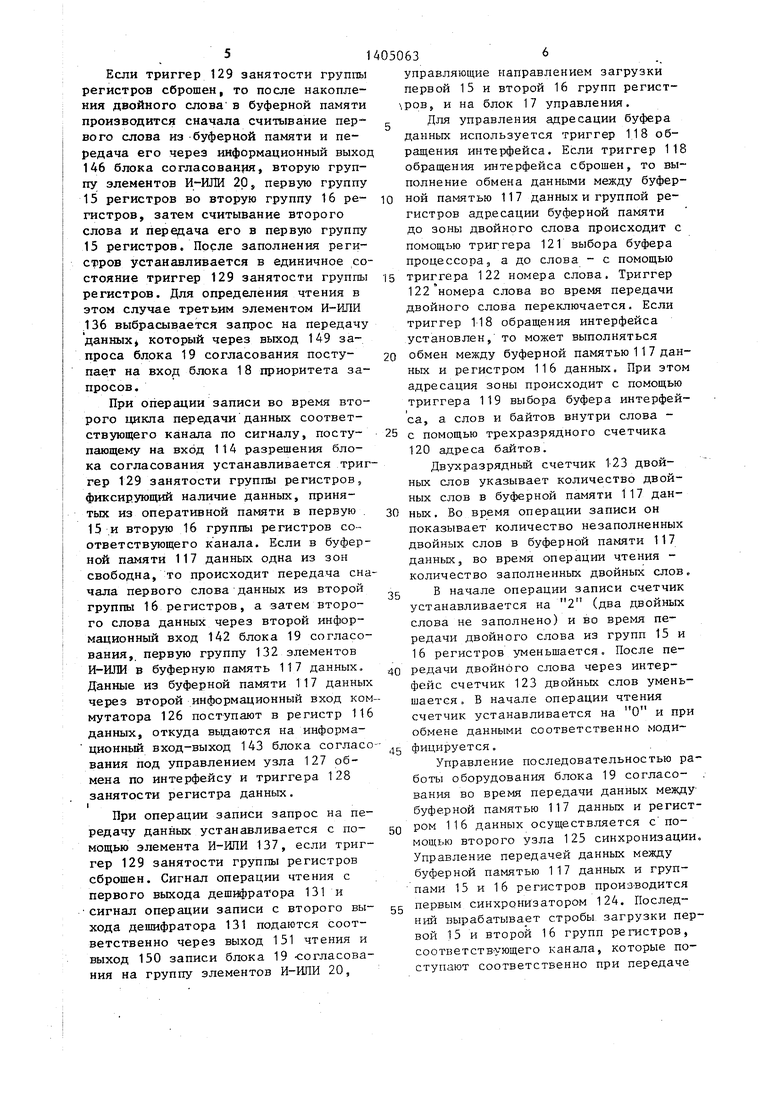

Группа 25 узлов маски (фиг.6) содержит регистры 168 маски, групповые элементы И 169, групповые элементы ИЛИ 170, элементы И 171, триггеры 172, информационные входы 173, установочные входы 174, первые информационные выходы 175, вторые информационные выходы 176.

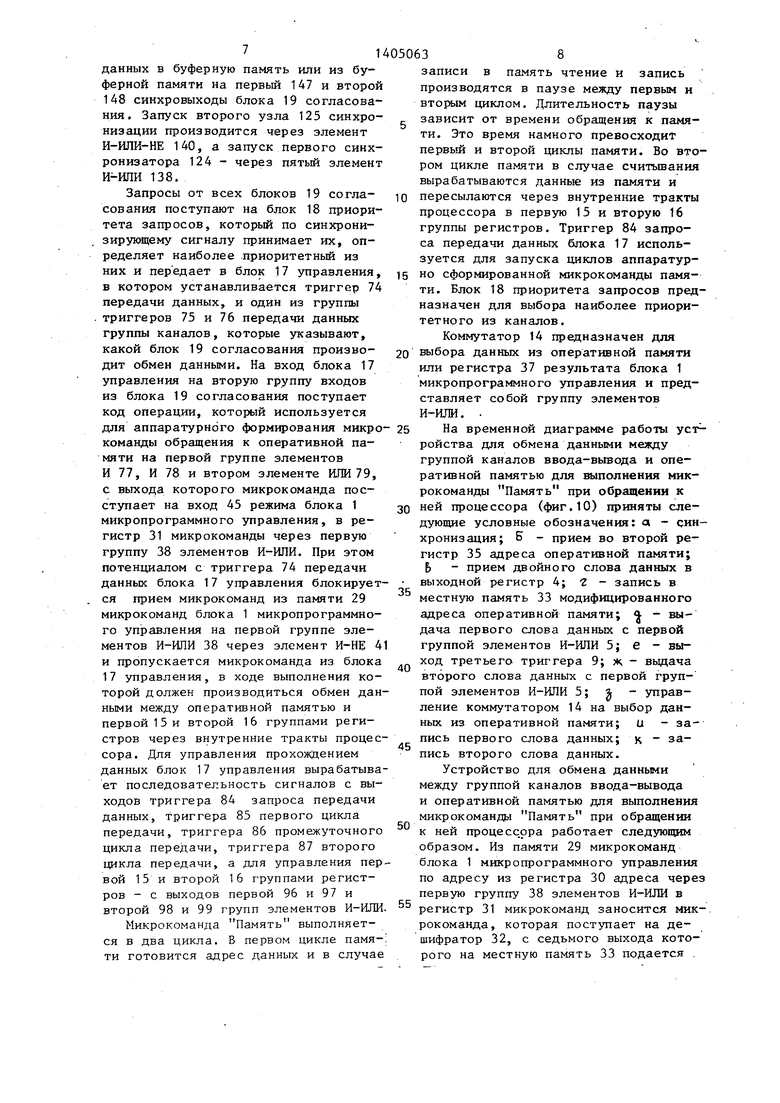

Блок 26 анализа (фиг.7) содержит элемент ИЛИ 177, триггер 178, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 179, триггер 18Ц, элемент И 181, триггер 182, группу 183 входов логических условий, синхровход 184, вход 185 логи0

5

условия, управляющий вы5

0

ческого ход 186.

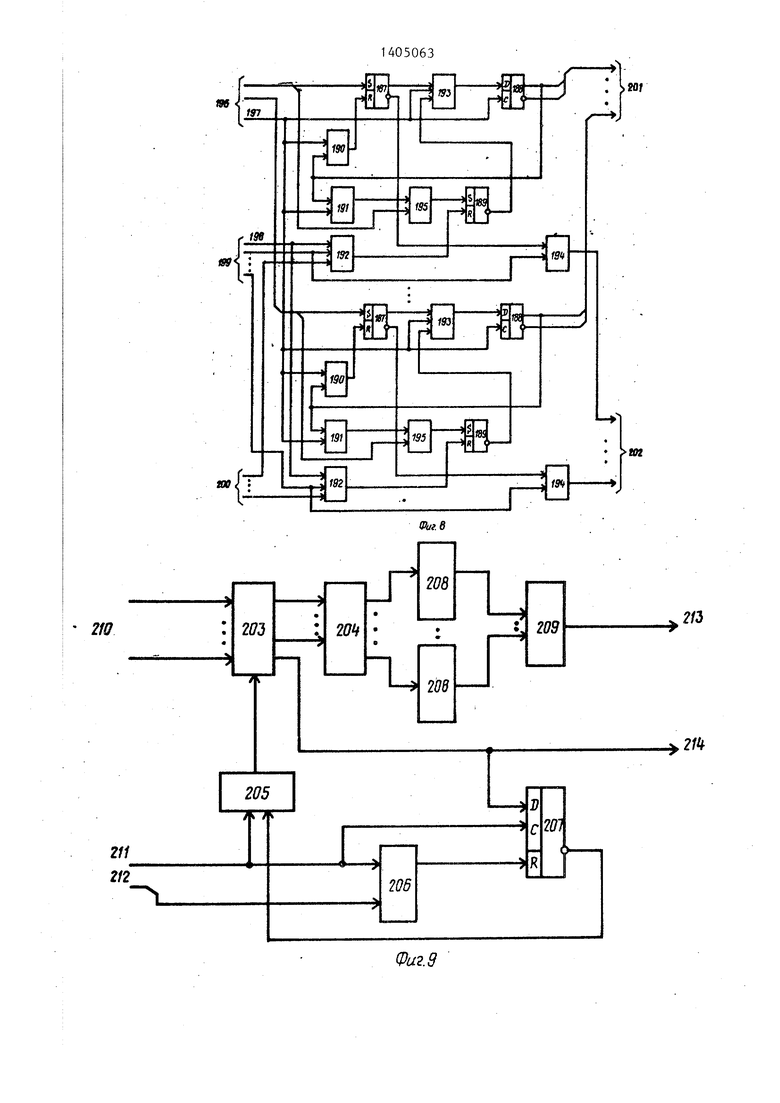

Группа 27 блоков формирования сигналов перезаписи (фиг.8) содержит триггеры 187-189,элементы И 190-194, элементы ИЛИ 195, группу 196 установочных входов, синхровход 197, вход 198 логического условия, вторую группу 199 входов логических условий, первую группу 200 входов логических условий, группу 201 выходов перезаписи, группу 202 информационных выходов .

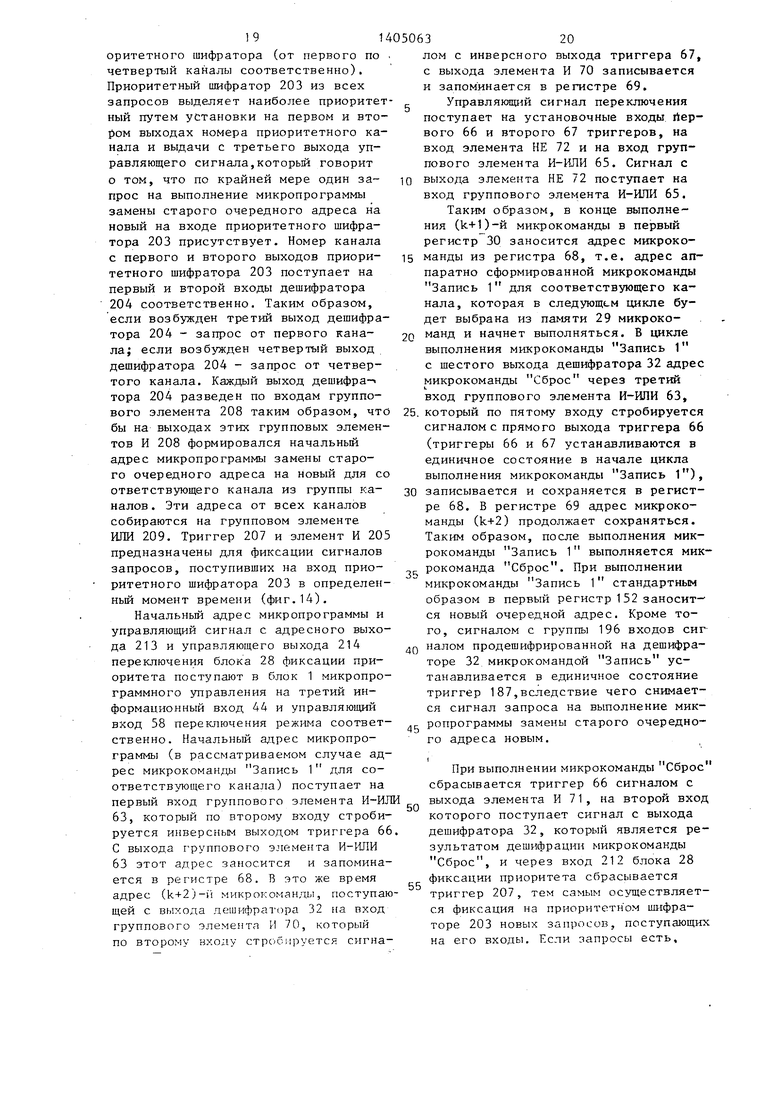

Блок 28 фиксации приоритета (фиг.9) содержит приоритетный шифратор 203, дешифратор 204, элементы И 205 и 206, триггер 2L/7, группу элементов 208, элемент ИЛИ 209, группу 210 информационных входов, синхровход 211, установочный вход 212, адресный выход 213, управляющий выход 214 переключения.

Устройство работает следующим образом.

И меется блок 19 согласования, буферная память 117 данных, которая имеет две зоны заполнения данными. Емкость каждой из зон соответствует разрядности оперативной памяти. В рассматриваемом случае она равна двойному слову (восемь байт). Ширина разрядности буферной памяти соответствует разрядности информационного тракта процессора, через тракты которого каналы обмениваются данными с оперативной памятью. Разрядность информационного тракта процес-. сора в рассматриваемом случае равна одному слову (четыре байта).

Код операции, выполняемый блоком 19 согласования, находится в регистре 130 кода операции. Сигнал с второго выхода дешифратора 131 определяет, что в блоке согласования выполняется операция записи. Сигнал с первого выхода дешифратора 131 определяет, что в блоке согласования вьтолняется операция чтения.При выл полнении чтения данные из периферийного устройства побайтно с информационного входа-выхода блока 19 согласования через коммутатор 126 поступают в регистр 116 данных. Из последнего через первую группу 132 элементов И-ИЛИ данные записываются в буферную память 117 данных по адресу с выхода второй группы 133 элементов И-ИЛИ.

5

0

5

5

10

25

51405063

Если триггер 129 занятости группы регистров сброшен, то после накопления двойного слова в буферной памяти производится сначала считывание первого слова из буферной памяти и передача его через информационный выход 146 блока согласования, вторую группу элементов И-ИЛИ 20, первую группу 15 регистров во вторую группу 16 регистров, затем считывание второго слова и передача его в первую группу 15 регистров. После заполнения регистров устанавливается в единичное состояние триггер 129 занятости группы регистров. Для определения чтения в этом случае третьим элементом И-ИЛИ .136 выбрасывается запрос на передачу данныхj который через выход 149 запроса блока 19 согласования посту- пае.т на вход блока 18 приоритета запросов.

При операции записи во время второго цикла передачи данных соответствующего канала по сигналу, поступающему на вход 114 разрешения блока согласования устанавливается триггер 129 занятости группы регистров, фиксирующий наличие данных, принятых из оперативной памяти в первую . 15 ,и вторую 16 группы регистров соответствующего канала. Если в буферной памяти 117 данных, одна из зон свободна, то происходит передача сначала первого слова данных из второй группы 16 регистров, а затем второго слова данных через второй информационный вход 142 блока 19 согласования, первую группу 132 элементов И-ИЛИ в буферную память 117 данных, Данные из буферной памяти Т17 данных через второй информационный вход коммутатора 126 поступают в регистр 116 данных, откуда выдаются на информа- ционньш вход-выход 143 блока согласования под управлением узла 127 обмена по интерфейсу и триггера 128

занятости регистра данных,

При операции записи запрос на передачу данных устанавливается с помощью элемента И-ИЛИ 137, если триггер 129 занятости группы регистров сброшен. Сигнал операции чтения с первого выхода дешифратора 131 и сигнал операции записи с второго выхода дешифратора 131 подаются соотетственно через выход 151 чтения и выход 150 записи блока 19 -согласоваия на группу элементов И-ИПИ 20,

упр пер ро

да ращ обр пол ной ги до пом про

15 тр 12 дво три уст

20 об ных ад три

са

35

40

с п 120

ных ных

30 ных пок дво дан кол уст сл ред 16 ред фей ша сч обм

45 фи

бо ва буф ром мощ Уп бу па

gc пе ний во со ст

50

управляющие направлением загрузки первой 15 и второй 16 групп регист- ров, и на блок 17 управления.

Для управления адресации буфера данных используется триггер 118 обращения интерфейса. Если триггер 118 обращения интерфейса сброшен, то выполнение обмена данными между буферной памятью 117 данных и группой регистров адресации буферной памяти до зоны двойного слова происходит с помощью триггера 121 выбора буфера процессора3 а до слова - с помощью

триггера 122 номера слова. Триггер 122 номера слова во время передачи двойного слова переключается. Если триггер 118 обращения интерфейса установлен, то может выполняться

обмен между буферной памятью 11 7 данных и регистром 116 данных. При этом адресация зоны происходит с помощью триггера 119 выбора буфера интерфейса, а слов и байтов внутри слова

с помощью трехразрядного счетчика 120 адреса байтов.

Двухразрядный счетчик 1-23 двойных слов указывает количество двойных слов в буферной памяти 117 данных. Во время операции записи он показывает количество незаполненных двойных слов в буферной памяти 117 данных, во время операции чтения - количество заполненных двойных слов. В начале операции записи счетчик устанавливается на 2 (два двойных слова не заполнено) и во время передачи двойного слова из групп 15 и 16 регистров уменьшается. После передачи двойного слова через интерфейс счетчик 123 двойных слов уменьшается . В начале операции чтения счетчик устанавливается на О и при обмене данными соответственно модифицируется.

Управление последовательностью работы оборудования блока 19 согласования во время передачи данных между буферной памятью 117 данных и регистром 116 данных осуществляется с помощью второго узла 125 синхронизации. Управление передачей данных между буферной памятью 117 данных и группами 15 и 16 регистров производится

первым синхронизатором 124. Последний вырабатывает стробы загрузки первой 15 и второй 16 групп регистров, соответств-ующего канала, которые поступают соответственно при передаче

10

20

данных в буферную память или из буферной памяти на первый 147 и второй 148 синхровыходы блока 19 согласования. Запуск второго узла 125 синхронизации производится через элемент И-ИЛИ-НЕ 140, а запуск первого синхронизатора 124 - через пятый элемент И-ИЛИ 138,

Запросы от всех блоков 19 согласования поступают на блок 18 приоритета запросов, который по синхронизирующему сигналу принимает их, определяет наиболее приоритетный из них и передает в блок 17 управления, в котором устанавливается триггер 74 передачи данных, и один из группы . триггеров 75 и 76 передачи данных группы каналов, которые указывают, какой блок 19 согласования производит обмен данными. На вход блока 17 управления на вторую группу входов из блока 19 согласования поступает код операции, который используется для аппаратурного формирования микро- 25 команды обращения к оперативной памяти на первой группе элементов И 77, И 78 и втором элементе ИЛИ 79, с выхода которого микрокоманда пос- ступает на вход 45 режима блока 1 микропрограммного управления, в регистр 31 микрокоманды через первую группу 38 элементов И-ИПИ. При этом потенциалом с триггера 74 передачи данных блока 17 управления блокируется прием микрокоманд из памяти 29 микрокоманд блока 1 микропрограммного уп равления на первой группе элементов И-ИЛИ 38 через элемент И-НЕ 41 и пропускается микрокоманда из блока 17 управления, в ходе выполнения которой должен производиться обмен данными между оперативной памятью и первой 15 и второй 16 группами регистров через внутренние тракты процессора. Для управления прохождением данных блок 17 управления вырабатывает последовательность сигналов с выходов триггера 84 запроса передачи данных, триггера 85 первого цикла передачи, триггера 86 промежуточного цикла передачи, триггера 87 второго цикла передачи, а для управления первой 15 и второй 16 группами регистров - с выходов первой 96 и 97 и

записи в память чтение и запись производятся в паузе между первым и вторй 1м циклом. Длительность паузы зависит от времени обращения к памяти. Это время намного превосходит первый и второй циклы памяти. Во втором цикле памяти в случае считьшания вырабатываются данные из памяти и пересылаются через внутренние тракты процессора в первую 15 и вторую 16 группы регистров. Триггер 84 запроса передачи данных блока 17 используется для запуска циклов аппаратур- 15 но сформированной микрокоманды памяти. Блок 18 приоритета запросов предназначен для выбора наиболее приоритетного из каналов.

Коммутатор 14 предназначен для выбора данных из оперативной памяти или регистра 37 результата блока 1 микропрограммного управления и представляет собой группу элементов И-ИЛИ. .

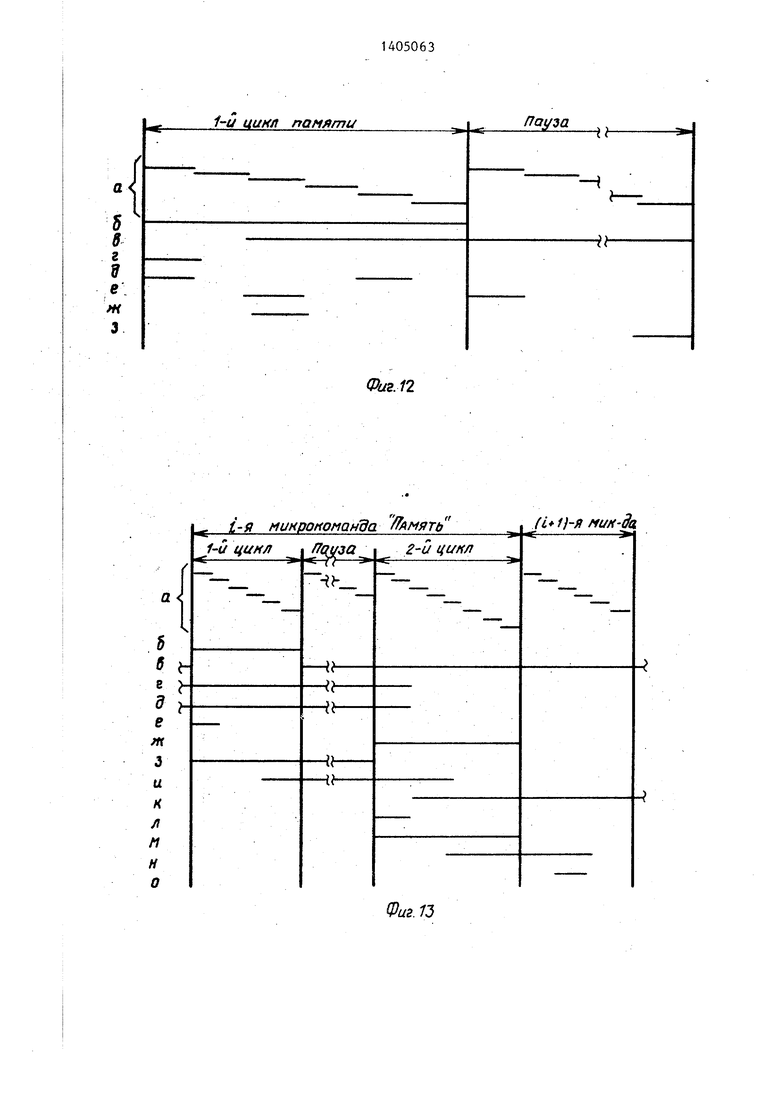

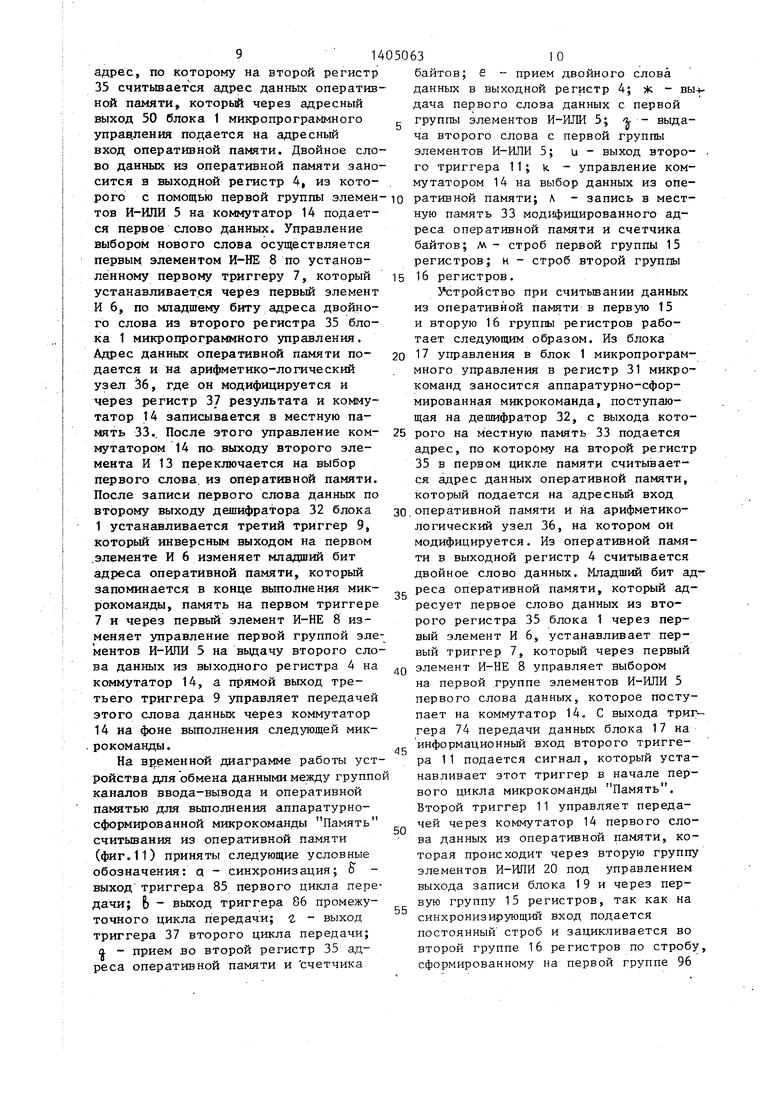

На временной диаграмме работы устройства для обмена данными между группой каналов ввода-вьтода и оперативной памятью для выполнения микрокоманды Память при обращении к ней процессора (фиг.10) приняты следующие условные обозначения: а - синхронизация; Б - прием во второй регистр 35 адреса оперативной памяти; EI - прием двойного слова данных в выходной регистр 4; 1 - запись в местную память 33 модифицированного адреса оперативной памяти; - выдача первого слова данных с первой группой элементов И-ИЛИ 5; е - выход третьего триггера 9; ж - выдача второго слова данных с первой груп- пой элементов И-ИПИ 5; % - управление коммутатором 14 на выбор данных из оперативной памяти; и - запись первого слова данных; к - запись второго слова данных.

Устройство для обмена данньми между группой каналов ввода-вывода и оперативной памятью дпя выполнения микрокоманду Память при обращении к ней процесс рра работает следующим образом. Из памяти 29 микрокоманд блока 1 микропрограммного управления по адресу из регистра 30 адреса через первую группу 38 элементов И-ИЛИ в

30

40

45

50

второй 98 и 99 групп элементов И-ИЛИ. регистр 31 микрокоманд заносится мик-.

Микрокоманда Память выполняется в два цикла, В первом цикле памя-; ти готовится адрес данных и в случае

рокоманда, которая поступает на дешифратор 32, с седьмого выхода которого на местную память 33 подается .

0

5

записи в память чтение и запись производятся в паузе между первым и вторй 1м циклом. Длительность паузы зависит от времени обращения к памяти. Это время намного превосходит первый и второй циклы памяти. Во втором цикле памяти в случае считьшания вырабатываются данные из памяти и пересылаются через внутренние тракты процессора в первую 15 и вторую 16 группы регистров. Триггер 84 запроса передачи данных блока 17 используется для запуска циклов аппаратур- 5 но сформированной микрокоманды памяти. Блок 18 приоритета запросов предназначен для выбора наиболее приоритетного из каналов.

Коммутатор 14 предназначен для выбора данных из оперативной памяти или регистра 37 результата блока 1 микропрограммного управления и представляет собой группу элементов И-ИЛИ. .

На временной диаграмме работы устройства для обмена данными между группой каналов ввода-вьтода и оперативной памятью для выполнения микрокоманды Память при обращении к ней процессора (фиг.10) приняты следующие условные обозначения: а - синхронизация; Б - прием во второй регистр 35 адреса оперативной памяти; EI - прием двойного слова данных в выходной регистр 4; 1 - запись в местную память 33 модифицированного адреса оперативной памяти; - выдача первого слова данных с первой группой элементов И-ИЛИ 5; е - выход третьего триггера 9; ж - выдача второго слова данных с первой груп- пой элементов И-ИПИ 5; % - управление коммутатором 14 на выбор данных из оперативной памяти; и - запись первого слова данных; к - запись второго слова данных.

Устройство для обмена данньми между группой каналов ввода-вывода и оперативной памятью дпя выполнения микрокоманду Память при обращении к ней процесс рра работает следующим образом. Из памяти 29 микрокоманд блока 1 микропрограммного управления по адресу из регистра 30 адреса через первую группу 38 элементов И-ИЛИ в

0

0

5

0

рокоманда, которая поступает на дешифратор 32, с седьмого выхода которого на местную память 33 подается .

адрес, по которому на второй регистр 35 считьшается адрес данных оперативной памяти, который через адресный выход 50 блока 1 микропрограммного упрацления по;р;ается на адресный вход оперативной памяти. Двойное слово данных из оперативной памяти заносится в выходной регистр 4, из которого с помощью первой группы элементов И-ИПИ 5 на коммутатор 14 подается первое слово данных. Управление выбором нового слова осуществляется первым элементом И-НЕ 8 по установленному первому триггеру 7, который устанавливается через первый элемент И 6, по младшему биту адреса двойного слова из второго регистра 35 блока 1 микропрограммного управления. Адрес данных оперативной памяти подается и на арифметико-логический узел 36, где он модифицируется и через регистр 37 результата и коммутатор 14 записывается в местную память 33.. После зтого управление коммутатором 14 по выходу второго элемента И 13 переключается на выбор первого слова, из оперативной памяти. После записи первого слова данных по второму выходу дешифратора 32 блока 1 устанавливается третий триггер 9, который инверсным выходом на первом .элементе И 6 изменяет младший бит адреса оперативной памяти, который запоминается в конце выполнения микрокоманды, память на первом триггере 7 и через первый элемент И-НЕ 8 изменяет управление первой группой элементов И-ИПИ 5 на вьщачу второго слова данных из выходного регистра 4 на коммутатор 14, а прямой выход третьего триггера 9 управляет передачей этого слова данных через коммутатор 14 на фоне выполнения следующей мик- рокоманды.

На временной диаграмме работы устройства для обмена данными между группой аналов ввода-вывода и оперативной памятью для вьшолнения аппаратурно- сформированной микрокоманды Память считьшания из оперативной памяти (фиг.11) приняты следующие условные обозначения: а - синхронизация; S - ыход триггера 85 первого цикла переачи; Ь - выход триггера 86 промежуочного цикла передачи; 1 - выход триггера 37 второго цикла передачи; а - прием во второй регистр 35 адреса оперативной памяти и счетчика

5

0

5

0

5

0

5

0

5

байтов; е - прием двойного слова данных в выходной регистр 4; ;К - ВЫ4- дача первого слова данных с первой группы элементов И-ИЛИ 5; о- - вьща- ча второго слова с первой группы элементов И-ИЛИ 5; ц - выход второ- . го триггера 11; к - управление коммутатором 14 на выбор данных из оперативной памяти; Л - запись в местную память 33 мод1гфицированного адреса оперативной памяти и счетчика байтов; м - строб первой группы 15 регистров; н - строб второй группы

16регистров.

Устройство при считывании данных из оперативной памяти в первую 15 и вторую 16 группы регистров работает следующим образом. Из блока

17управления в блок 1 микропрограммного управления в регистр 31 микрокоманд заносится аппаратурно-сфор- мированная микрокоманда, поступающая на дешифратор 32, с выхода которого на местную память 33 подается адрес, по которому на второй регистр 35 в первом цикле памяти считывается адрес данных оперативной памяти, который подается на адресный вход оперативной памяти и на арифметико- логический узел 36, на котором он модифицируется. Из оперативной памяти в выходной регистр 4 считывается двойное слово данных. Младший бит адреса оперативной памяти, который адресует первое слово данных из второго регистра 35 блока 1 через первый элемент И 6, устанавливает первый триггер 7, который через первый элемент И-НЕ 8 управляет выбором

на первой группе элементов И-ИЛИ 5 первого слова данных, которое поступает на коммутатор 14, С выхода триггера 74 передачи данных блока 17 на информационный вход второго триггера 11 подается сигнал, который устанавливает этот триггер в начале первого цикла микрокоманды Память. Второй триггер 11 управляет передачей через коммутатор 14 первого слова данных из оперативной памяти, которая происходит через вторую группу элементов И-ИПИ 20 под управлением выхода записи блока 19 и через первую группу 15 регистров, так как на синхронизирующий вход подается постоянный строб и зацикливается во второй группе 16 регистров по стробу, сформированному на первой группе 96

140

и 97 элементов И-ИЛИ блока 17 по сигналам с выхода группы триггеров 75 и 76 передачи данных группы каналов триггера 87 второго цикла передачи и синхросигнала.

Из местной памяти 33 блока 1 во втором цикле памяти на второй регистр 35 считывается счетчик байтов, содер

регистр 2; ж - строб второй груп-| пы 16 регистров; о. - запись в оперативную память.

Устройство при записи данных из первой 15 и второй 16 групп резисторов в оперативную память работает следующим образом. С второго информационного выхода группы 16 регистров

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для управления каналами | 1979 |

|

SU877519A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Устройство для сопряжения процессора с периферийными устройствами | 1985 |

|

SU1359780A1 |

| Устройство управления каналами | 1972 |

|

SU545983A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для управления каналами | 1974 |

|

SU520592A1 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1305693A2 |

жимое которого указывает на то,сколь-1о в блок 1 в первый регистр 34 через

ко байтов осталось передать из оперативной памяти. Счетчик байтов передается на арифметико-логический узел 36,на котором он модифицируется. После сброса второго триггера 11 управление коммутатором 14 переключается на выдачу из регистра 37 результата модифицированного адреса, который записывается в местную память 33. Затем на втором элементе И-НЕ 10 по сигналу с выхода триггера

87второго цикла передачи блока 17 и сигналу с синхровхода 21 устройства вырабатывается сигнал, который поступает на второй вход первого элемента И-НЕ 8 и инвертирует выходы этого элемента.

Таким образом, первая группа элементов И-ИЛИ 5 выбирает второе слово данных, которое через коммутатор 14 под управлением сигнала с выхода второго элемента И 13 поступает через вторую группу элементов И-ИЛИ 20 на первую группу 15 регистров, где оно и защелкивается по стробу,сформированному на второй группе 98 элементов И-ИЛИ по сигналам с выхода группы триггеров 75 и 76 передачи данных групп каналов, синхросигнала и сигнала с выхода группы триггеров

88и 89 второго цикла передачи груп- пы каналов. Запись модифицированного сигнала из регистра 37 результата блока 1 в местную память 33 выполняется на фоне выполнения следующей микрокоманды.

На временной диаграмме работы устройства при выполнении аппаратур- но-сформированной микрокоманды Память записи в оперативную память (фиг. 12) приняты следующие условн; 1е обозначения: а - синхронизация; - выход триггера 85 первого цикла передачи; р - выход триггера 86 промежуточного цикла; 1 - прием во второй регистр 35 адреса оперативной памяти; - прием в первый регистр 34 данных из второй группы 16 регистров; е - прием данных во входной

15

20

30

вторую группу 39 элементов И-ИЛИ п управлением сигнала с выхода тригг 74 передачи данных блока 17 приним ется первое слово данных по стробу с выхода первого элемента И 94 бло ка 17, который вырабатывается по с хросигналу. После приема первого с ва в первый регистр 34 Слока 1 дан ные через первый управляющий выход 51 блока 1 подаются на входной регистр 2, где они принимаются по ст бу, сформированному на втором элементе И 95 блока 17, который выраб тывается по синхроимпульсу и треть 25 му управляющему выходу блока 1. По ле приема первого слова данных во входной регистр 2 второе слово из первой группы 15 регистров перепис вается во вторую группу 16 регистр по стробу с выхода первой группы 9 и 97 элементов И-ИЛИ блока 17, сфо мированного по сигналам с выхода группы триггеров 75, 76 передачи д ных группы каналов, триггеров 85 п вого цикла передачи и синхросигнал С выхода второй группы 16 регистрр второе слово данных записывается в первый регистр 34 блока 1 через вторую группу 39 элементов И-ИПИ п стробу с выхода первого элемента И 94 блока 17, сформированного по си налам с выхода триггера 74 передач данных, триггера 85 первого цикла передачи и синхросигнала. С выхода первого регистра 31 блока 1 второе слово данных поступает на входной гистр 2, на котором оно защелкивае по стробу с выхода второго элемент И 95 блока 17, сформированного по сигналам с выхода триггера 74 пере чи данных и синхросигналу. Из мест ной памяти 33 блока 1 считывается адрес, который через второй регист 35 передается на адресный вход опе ративной памяти. С выхода дешифрат ра 32 блока 1 на элементе И 40 выр батывается строб записи, в операти ную память который подается на стр бирующий вход оперативной памяти.

35

40

45

50

55

0

0

вторую группу 39 элементов И-ИЛИ под управлением сигнала с выхода триггера 74 передачи данных блока 17 принимается первое слово данных по стробу с выхода первого элемента И 94 блока 17, который вырабатывается по синхросигналу. После приема первого слова в первый регистр 34 Слока 1 данные через первый управляющий выход 51 блока 1 подаются на входной регистр 2, где они принимаются по стробу, сформированному на втором эле менте И 95 блока 17, который вырабатывается по синхроимпульсу и третье- 5 му управляющему выходу блока 1. После приема первого слова данных во входной регистр 2 второе слово из первой группы 15 регистров переписывается во вторую группу 16 регистров по стробу с выхода первой группы 96 и 97 элементов И-ИЛИ блока 17, сформированного по сигналам с выхода группы триггеров 75, 76 передачи данных группы каналов, триггеров 85 первого цикла передачи и синхросигнала. С выхода второй группы 16 регистррв второе слово данных записывается в первый регистр 34 блока 1 через вторую группу 39 элементов И-ИПИ по стробу с выхода первого элемента И 94 блока 17, сформированного по сигналам с выхода триггера 74 передачи данных, триггера 85 первого цикла передачи и синхросигнала. С выхода первого регистра 31 блока 1 второе слово данных поступает на входной регистр 2, на котором оно защелкивается по стробу с выхода второго элемента И 95 блока 17, сформированного по сигналам с выхода триггера 74 передачи данных и синхросигналу. Из местной памяти 33 блока 1 считывается адрес, который через второй регистр 35 передается на адресный вход оперативной памяти. С выхода дешифратора 32 блока 1 на элементе И 40 выра-, батывается строб записи, в оперативную память который подается на стро- бирующий вход оперативной памяти.

5

0

5

0

5

13

Организация передачи данных между группой каналов ввода-вывода и one- ративной памятью по блочному принципу выполняется следующим образом. Перед началом работы ручным или каким- либо другим способом в регистрах 168 маски группы 25 узлов маски для каждого канала ввода-вывода из группы фиксируется тот объем информации, который должен передаваться по блочному принципу. Например, для передачи блока объемом в 2048 байт возбуж дается (устанавливается в единицу) двенадцатый разряд регистра 168 маски.

В процессе выполнения команды ввода-вывода, если по этой команде необходимо передать несколько блоков данных между каналом ввода-вывода оперативной памяти, по микрокоманде, продешифрированной на дешифраторе 32 блока 1 микропрограммного управления, устанавливается триггер 172 группы 25 узлов маски. Установка выполняется с восьмого выхода группы выходов 59 по групповому выходу 60. В функции триггера 172 входит разрешение через элемент И 171 передачи результатов сравнения, выполненных на элементах И 169 группы 25 узлов маски, а также постоянного стробиро- вания по входу элемента И 193 через группу 199 входов логических условий группы 27 блоков формирования сигналов перезаписи. I

Далее в процессе выполнения команд ввода-вывода по микрокомандам Запись 1 и Запись 2, продешиф- рированным на дешифраторе 32 из местной памяти 33 стандартным путем (через первый вход группового элемента И-ИПИ 64j второй регистр 35, арифметико-логический узел 36, регистр 37 результата, второй управляющий выход 52, коммутатор 14), в первый 152 и второй 157 регистры заносятся начальные адреса очередного и текущего блоков в группу 23 блоков регистров по информационному входу 160, стробирование этих регистров выполняется по группе 161 син- хровходов. Причем сначала выполняется микрокоманда Запись 2, а затем Запись 1. Указанная последовательность выполнения микрокоманд Запись 1 и Запись 2 подготавливает к работе группу 27 блоков формирования , в которую с дешифратора 32

0506314

по группе 196 установочных входов поступают сначала сигнал Запись 2 на вход элемента ИЛИ 195, сигнал с выхода которого устанавливает в единичное состояние триггер 189, затем сигнал Запись 1, который устанавливает в единичное состояние триггер 187.

10

Запись текущего адреса во второй регистр 157 выполняется через групповой элемент И 154, который стро- бируется инверсным выходом триггера

15 188, и групповой элемент ИЛИ 155. Стро бирование второго регистра 157 выполняется сигналом Запись 2 с входа 161, который поступает на вход элемента ИЛИ 156. Стробирование пер20 вого регистра 152 выполняется сигналом Запись 1 с входа 161 группы 23 блоков регистров.

После выполнения указанных действий аппаратура устройства для об25 мена данными между группой каналов ввода-вывода и оперативной памятью подготовлена для организации обмена данными между группой каналов ввода- вывода и оперативной памятью по блоч30 ному принципу.

Каждый раз в процессе выполнения микрокоманды Память, аппаратурно- сформированной одним из каналов группы,, выполняется модификация ад35 реса и счетчика байтов. При блочном принципе обмена данными эта модификация отличается от описанной модификации адреса и счетчика байтов (фиг.11 и 12), когда по одной коман- 40 да ввода-вывода передается только один блок данных.

На временной диаграмме модификации адреса и счетчика байтов при организации блочного обмена байтами

45 (фиг.13) приняты следующие условные обозначения: а - синхронизация; о - выход триггера 85, который задает время первого цикла микрокоманды Память ; Ь - выход элемента НЕ

50 73, который переключает стробирование группового элемента И-ИЛИ 64; г - выход триггеров 75 и 76, фиксирующих приоритетность выполнения аппаратурно-сформированной микро55 команды Память для конкретного канала ввода-вывода группы; - время вьдачи адреса с выхода групповых элементов И 158; е - клапа- нирование адреса на групповом эле

5

менте И-ИЛИ 64, поступающего на четвертый вход группового элемента И-И 64 с выхода группового элемента ИЛИ 24 через третий информационный вход 44 блока 1 микропрограммного управления; Ж - выход 113 группы триггеров, фиксирующих второй цикл выполнения микрокоманды Память для конкретного канала ввода-вывода гру пы; 4 - занесение и модификация адреса в арифметико-логическом узле 36; и - запись и хранение модифицированного адреса в регистре 37 результата; к - запись адреса из регистра 37 результата во второй регистр . 157 и его хранение; д - кл панирование счетчика байтов на групповом элементе И-ИЛИ 64, поступающего из местной памяти 33 на шестой вход группового элемента И-ИЛИ 64; АЛ - занесение и модификация счетчика байтов в арифметико-логическом узле 36; Н - запись и хранение модифицированного счетчика байтов в регистре 37 результата; о - запись счетчика байтов из регистра 37 результата в местную память 33,

Модификация адреса (модификация счетчика байтов не отличается от описанного) выполняется следующим оразом. В первом цикле выполнения мирокоманды Память сигналом с управляющего потенциального входа 62 первого цикла, который поступает с выхда триггера 85, запрещается прием информации из местной памяти 33 и разрешается прием по третьему информационному входу 44 .в арифметико-логический узел 36. Таким образом, в первом цикле микрокоманда Память с группового выхода 167 группы 23 блоков регистров с выхода групповог элемента И 158 одного из каналов, кторый определяется наличием строба на втором входе группового элемента И 158, который поступает с группового входа 165 разрешения чтения, на котором появляется сигнал с триггеров 75 и 76 того канала ввода-вывода, который на данный момент времен

является самым приоритетным, т.е., по которому выполняется микрокоманда Память, адрес с второго регистра 157 поступает на вход арифметико-логического узла и там модифицируется. Во втором цикле по сигналу с входа 162 соответствующего канала, который стробируется синхроимпульсом на эле5

0

5063

16

менте И 159, с выхода которого сигнал через элемент ИЛИ 156 поступает на вход разрешения записи второго регистра 157, модифицированный адрес с выхода коммутатора 14 поступает на информационный вход 160, групповой элемент И 154, групповой элемент ИЛИ 155, заносится во второй регистр 157.

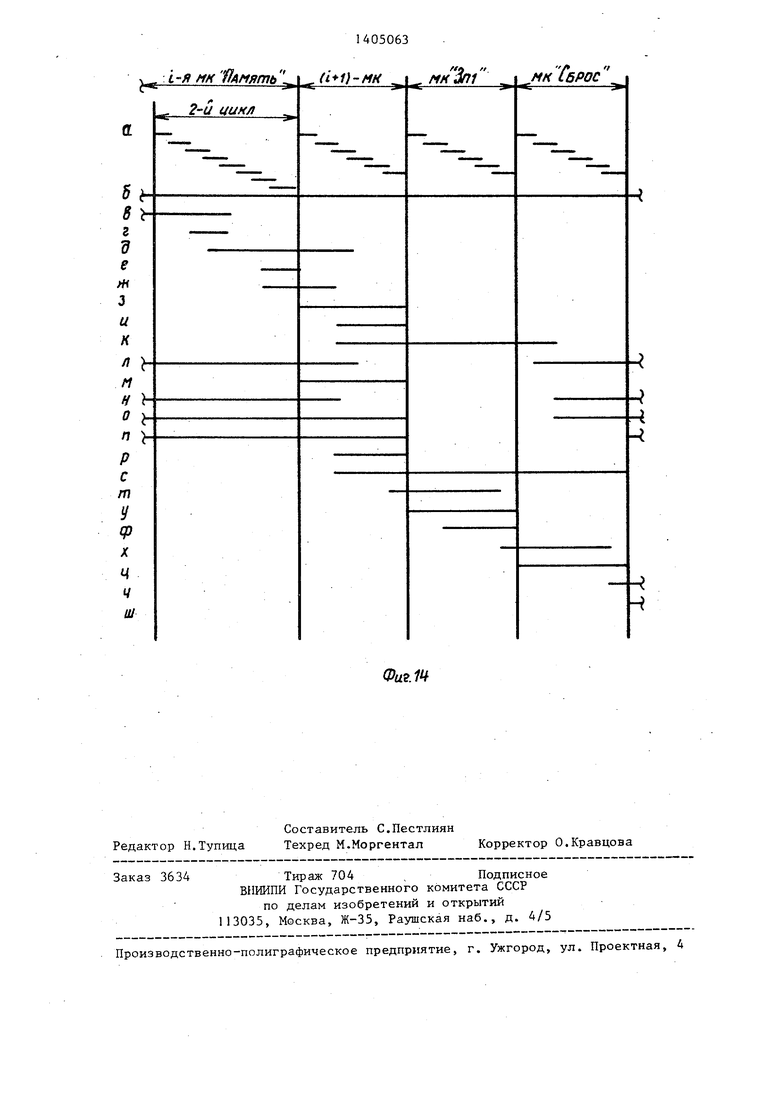

На временной диаграмме анализа конца передачи обменного массива, выработки приоритетного запроса на выполнение микропрограммы замены старого очередного адреса на новый и выполнение этой микропрограммы, содержащей, например, две микрокоманды Запись Г и Сброс (ф1 г,14) приняты следующие условные обозначения: а - синхронизация; S - выход триггера 172, который фиксирует, что канал организует передачу данных по блочному принципу; i - выход триггера 178, который каждый раз устанав- 5 ливается после очередной модифика- . ции; -г/ - выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 179, который возбуждается, если при очередной модификации адреса со- - ответствующий разряд адреса изменил свое состояние; ij - выход триггера 180, который фиксирует изменение разряда адреса; е - выход триггера 182, который может быть установлен только при наличии второго цикла выполнения микрокоманды Память, ап- паратурно-сформированной из каналов группы; Ж - инверсньй выход триггера 189, который создает условия, для перезаписи очередного адреса на место текущего и для формирования сигнала запроса на выполнение микропрограммы замены старого очередного адреса на новый; - прямой выход триггера 188, с помощью которого выполняется перезапись и формирование сигнала запроса; U - инверсный выход триггера 187; к - третий упраб- ляющий выход приоритетного шифратора 203 и адресный выход элемента ИЛИ 209; л - инверсньй выход триггера 207, фиксирующий прием сигналов запроса на приоритетный шифратор 203; м - выполнение (и+1)-й микрокоманды после второго цикла микрокоманды Память ; h - выход элемента НЕ 72, запрещающий прием адреса микрокоманды из регистра 69 в регистр 30 и разрешающий прием адреса микрокоманды из регистра 68 в регистр 30; о., г

0

5

0

5

0

5

17

Инверсный выход триггера 66, разре- шающий прием аппаратурно-сформиро- ванного адреса микрокоманды в регистр 68; п - инверсный выход тригера 67, разрешающий прием адреса микрокоманды в регистр 69; р - занесение в регистр 68 аппаратурно- сформированного адреса микрокоманды Б данном случае Запись с- занесение в регистр 69 ста ндартным путем адреса (k+2)-й микрокоманды и ее хранение;

т - занесение адреса микрокоманды Запись i из регистра 68 в регистр 30; - выполнение микрокоманды Запись ср - занесение в регистр 68 стандартным путем адреса микрокоманды,Сброс ; х - занесение адреса микрокоманды Сброс из регистра 68 в регистр 30; Ц - выполнение мирокоманды Сброс ; Ч занесение адреса (k+2)-ro адреса микрокоманды из регистра 69 в регистр 30; ш - выполнение (k+2)-u микрокоманды.

Анализ конца передачи обменного массива, выработки приоритетного запроса на выполнение микропрограммы замены старого очередного адреса на новый и выполнение этой микропрограм мы, содержащей, например, две микрокоманды Запись 1 и Сброс, выполняется следующим образом. Каждый раз в процессе модификации адреса, который выполняется во втором цикле микрокоманды Память, в блоке 26 анализа на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 179 анализируются изменение состояния соответствующего разряда адреса после его модификации. Изменение состояния разряда не произошло - никаких действий не выполняется. Изменение состояния разряда произошло наполняются следующие действия.

I

Во втором цикле микрокоманды Па- мять после модификации адреса на триггере 182 фиксируется изменение состояния соответствующего разряда модифицированного адреса, что говорит о том, что весь массив данного текущего блока передан и необходимо, во-первых, очередной адрес из первого регистра 152 переписать во второй регистр 157, чтобы без задержек продолжить данными меж- ду каналом ввода-вывода и оперативной памятью по очередному блоку обменного массива, который становится текущим блоком обменного массива и.

, 15

20

30

35

25

45 50

40506318

,во-вторых, в первый регистр 152 микропрограммным путем записать новый очередной адрес.

Перезапись информации из первого регистра 152 во второй регистр 157 выцолняется путем установки триг-f гера 188, сигнал с прямого выхода которого через группу 201 выходов 10 группы 27 блоков формирования сигналов перезаписи, стробируя по второму входу групповой элемент И 153, разрешает прохождение адреса с выхода первого регистра 152 через групповой элемент И 153 и групповой

40

элемент ИЛИ 155 на вход второго регистра 157 и, возбуждая по второму входу элемент ИЛИ 156, сигналом с выхода последнего разрешает запись информации во второй регистр 157.

Установка триггера 188 осуществляется через элемент И 194, на первый вход которого поступает сигнал с прямого выхода триггера 187, который был установлен в единичное состояние, а на второй вход которого поступает сигнал с инверсного выхода триггера 189.

В процессе перезаписи информации из первого регистра 152 во второй регистр 157, которая выполняется в течение цикла выполнения (k+1)-й микрокоманды путем сброса тр.иггера 187 которьй выполняется сигналом с прямого выхода триггера 188, поступающего на первый вход элемента И 191, формируется сигнал запроса на выполнение микропрограммы замены старого очередного адреса на новый, который появляется с выхода элемента И 190 под воздействием сигналов, поступающих на его первый вход с инверсного выхода триггера 187 и на второй вход с группового входа 199 группы 27 блоков формирования сигналов перезаписи. Сигнал запроса с выхода элемента И 190 поступает на групповой управляющий выход 202 группы 27 блоков формирования сигналов перезаписи и далее в блок 28 фиксации приоритета.

В блоке 28 фиксации по групповому управляющему входу 210 поступают сигналы запроса на выполнение микропрограммы замены старого очередного адреса на новый от всех каналов ввода-вывода из группы каналов. Например, для четырех каналов ввода-вывода в группе сигналы запросов поступают с первого по четвертый входы приоритетного шифратора (от первого по четвертый каналы соответственно). Приоритетный шифратор 203 из всех запросов выделяет наиболее приоритетный путем установки на первом и втором выходах номера приоритетного канала и выдачи с третьего выхода управляющего сигнала,которьй говорит о том, что по крайней мере один запрос на выполнение микропрограммы замены старого очередного адреса на новый на входе приоритетного шифратора 203 присутствует. Номер канала с первого и второго выходов приоритетного шифратора 203 поступает на первый и второй входы дешифратора 204 соответственно. Таким образо-м, если возбужден третий выход дешифратора 204 - запрос от первого канала; если возбужден четвертый выход дешифратора 204 - запрос от четвертого канала. Каждый выход дешифра- тора 204 разведен по входам группового элемента 208 таким образом, что 25. который по пятому входу стробируется

сигналом с прямого выхода триггера 66 (триггеры 66 и 67 устанавливаются в единичное состояние в начале цикла выполнения микрокоманды Запись 1), 30 записывается и сохраняется в регистре 68. В регистре 69 адрес микрокоманды (k+2) продолжает сохраняться. Таким образом, после выполнения микрокоманды Запись 1 выполняется микбы на выходах этих групповых элементов И 208 формировался начальньй адрес микропрограммы замены старого очередного адреса на новый для со ответствующего канала из группы каналов. Эти адреса от всех каналов собираются на групповом элементе ИЛИ 209. Триггер 207 и элемент И 205 предназначены для фиксации сигналов запросов, поступивших на вход приоритетного шифратора 203 в определен- ньй момент времени (фиг.14).

Начальный адрес микропрограммы и управляющий сигнал с адресного выхода 213 и управляющего выхода 214 переключения блока 28 фиксации приоритета поступают в блок 1 микропрограммного управления на третий информационный вход 44 и управляющий вход 58 переключения режима соответственно. Начальньш адрес микропрограммы (в рассматриваемом случае адрес микрокоманды Запись Г для соответствующего канала) поступает на первый вход группового элемента И-ИЛИ 63, который по второму входу стробируется инверсным выходом триггера 66. С выхода группового элемента И-ИЛИ 63 этот адрес заносится и запоминается в регистре 68. В это же время адрес (k+2)-ii микрокоманды, поступающей с дешифратора 32 на вход группового элемента И 70, который по второму входу стрс)б||руется сигна35

рокоманда Сброс. При выполнении

40

микрокоманды Запись 1 стандартным образом в первый регистр 152 заносится новый очередной адрес. Кроме того, сигналом с группы 196 входов сигналом продешифрированной на дешифраторе 32 микрокомандой Запись устанавливается в единичное состояние триггер 187,вследствие чего снимается сигнал запроса на выполнение мик- дг ропрограммы замены старого очередного адреса новым.

При выполнении микрокоманды Сброс сбрасывается триггер 66 сигналом с выхода элемента И 71, на второй вход которого поступает сигнал с выхода дешифратора 32, который является результатом дешифрации микрокоманды Сброс, и через вход 212 блока 28 фиксации приоритета сбрасывается триггер 207, тем самым осуществляется фиксация на приоритетн ом шифраторе 203 новых запросов, поступающих на его входы. Если запросы есть.

50

55

лом с инверсного выхода триггера 67, с выхода элемента И 70 записывается и запоминается в регистре 69.

Управляющий сигнал переключения поступает на установочные входы rtep- вого 66 и второго 67 триггеров, на вход элемента НЕ 72 и на вход группового элемента И-ИПИ 65. Сигнал с

выхода элемента НЕ 72 поступает на вход группового элемента И-ИЛИ 65. Таким образом, в конце выполнения (k+1)-й микрокоманды в первый регистр 30 заносится адрес микрокоманды из регистра 68, т.е. адрес ап- паратно сформированной микрокоманды Запись 1 для соответствующего канала, которая в следующем цикле будет выбрана из памяти 29 микрокоманд и начнет выполняться. В цикле выполнения микрокоманды Запись 1 с шестого выхода дешифратора 32 адрес микрокоманды Сброс через третий вход группового элемента И-ШИ 63,

35

рокоманда Сброс. При выполнении

40

микрокоманды Запись 1 стандартным образом в первый регистр 152 заносится новый очередной адрес. Кроме того, сигналом с группы 196 входов сигналом продешифрированной на дешифраторе 32 микрокомандой Запись устанавливается в единичное состояние триггер 187,вследствие чего снимается сигнал запроса на выполнение мик- дг ропрограммы замены старого очередного адреса новым.

При выполнении микрокоманды Сброс сбрасывается триггер 66 сигналом с выхода элемента И 71, на второй вход которого поступает сигнал с выхода дешифратора 32, который является результатом дешифрации микрокоманды Сброс, и через вход 212 блока 28 фиксации приоритета сбрасывается триггер 207, тем самым осуществляется фиксация на приоритетн ом шифраторе 203 новых запросов, поступающих на его входы. Если запросы есть.

25140506322

то все повторяется сначала. Если за- реключает прием адреса очередной

просов нет, снимается сигнал с третьего выхода приоритетного шифратора 203. Отсутствие сигнала на управляющем входе 58 переключения блока микропрограммного управления пемикрокоманды с регистра 68 на рег 69. Таким образом,в регистр 30 в це выполнения микрокоманды Сброс заносится ранее запомненный в рег стре 69 .адрес (п+2)-й микрокоманд

реключает прием адреса очередной

микрокоманды с регистра 68 на регистр 69. Таким образом,в регистр 30 в конце выполнения микрокоманды Сброс заносится ранее запомненный в регистре 69 .адрес (п+2)-й микрокоманды.

«и

ffS

1

л

«к

153

I. г

:

-I

иъ

1S3

F

л

1Яа.Ч

;

1S7 -ТН

hJ UJ г-

вв

м -f

158

«7

Ш

Фиг.

Фи2.9

Ф1Л.Ю

Фил. 11

f-t/ иинл noMflmu

6 г д в

W 3

Пауъа

t г

-э

{Г

й/г/2

Фиг. /J

ФМ.1

| Способ получения камфоры | 1921 |

|

SU119A1 |

Авторы

Даты

1988-06-23—Публикация

1985-07-02—Подача