ячейки и с одним из входов второго компаратора, другой вход которого через третий резистор соединен с выходом второй запоминающей ячейки и через четвертый резистор с общим выводом устройства, выход второго компаратора через второй формирователь импульсов управления соединен с управляющим входом первой запоминающей ячейки, отличаю щеес я . тем, что, с целью повышения точности измерения, в него введены пятый, шестой, седьмой, восьмой, девятый, десятьй, одиннадцатый резисторы, второй расширитель импульсов, третья и четвертая запоминающие ячейки, третий компаратор, третий и четвертый формирователи импульсов управления, второй согласующий усилитель, сумматор, третий конденсатор, четвертый, пятый и шестой ключи, причем первый вход второго согласующего усилителя соединен с первой обкладкой третьего конденсатора, с общим выводом устройства и через последовательно соединенные четвертый и пятый ключи - с вторым входом второго согласующего усилителя, с второй обкладкой третьего конденсатора, которая через последовательно соединенные пятый резистор и шестой ключ соединена с выводом для подключения плюсового зажима источника питания, выход первого компаратора соединен с управляющим входом пятого ключа, выход инвертора соединен с

управляю1 1им входом шестого к.азча, вход первого расширителя импульсов соединен через третий формирователь импульсов управления с управляющим входом третьей запоминающей ячейки и через второй расширитель импульсов с управляющим входом четвертого ключа, выход второго согласующего усилителя соединен с информационным входом третьей запоминающей ячейки и с одним из входов третьего компаратора, одни из входов которого через шестой резистор соединен с выходом третьей запоминающей ячейки и через седьмой резистор с общим выводом устройства, выход третьего компаратора через четвертый формирователь импульсов управления соеинен с управляющим входом четвертой запоминающей ячейки, информационный вход которой соединен с информационнь1м входом первой запоминаюей ячейки, сумматор, первый вход которого через восьмой резистор соеинен с выходом первой запоминающей чейки и через девятый резистор с общим выводом устройства, второй вход сумматора через десятый резистор соединен с выходом четвертой запоминающей ячейки и через одиннадцатый резистор с общим выводом устройства, выход сумматора соединен с выводом, являющимся выходом устройства и предназначенным для подключения измерительного, прибора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ измерения амплитуды синусоидального напряжения инфранизкой частоты | 1977 |

|

SU658486A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1388987A1 |

| Способ определения входного сопротивления усилителя заряда и устройство для его осуществления | 1984 |

|

SU1205060A1 |

| Электрометрический преобразователь заряда | 1986 |

|

SU1420537A1 |

| Преобразователь разности фаз в напряжение | 1985 |

|

SU1273836A2 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1042036A1 |

| Преобразователь частоты | 1986 |

|

SU1403287A2 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| Однофазный двухполупериодный преобразователь переменного напряжения в постоянное | 1988 |

|

SU1541732A1 |

| Амплитудный детектор | 1983 |

|

SU1150563A1 |

1. Способ измерения амплитуды синусоидального напряжения инфранизкой частоты, основанный на заряде накопительной емкости измеряемым напряжением и вьщелении временного интервала, соответствующего положительному полупериоду измеряемого напряжения, преобразовании: его линейно нарастающего напряжения, запоминании его максимальной амплитуды, уменьшении запомненного напряжения в два раза, сравнении полученного в результате уменьшения сигнала с линейно нарастающим напряжением, запоминании амплитуды измеренного напряжения в момент равенства отмеченных напряжений, отличающийс я тем, что, с целью повьш1ения точности измерения, одновременно с вьаделением временного интервала, соответствующего положительному полупериоду, вьщеляют отрицательный полупериод измеряемого напряжения, затем запоминают его максимальную амплитуду, уменьшают ее в два раза, полученное в результате уменьшения напряжение суммируют с уменьшенной в два раза максимальной амплитудой положительного полупериода. 2. Устройство для измерения амплитуды синусоидального напряжения, инфранизкой частоты, содержащее первый компаратор, первый вход которого соединен с общим выводом устройства и с одним из выводов, ЯВЛЯЮ1ЦИМСЯ первым входом устройства, второй вход соединен с одним из вьшодов, являющимся вторым входом устройства, и с информационным входом первой запоминающей ячейки, а выход соединен с управляющим входом первого ключа, с входом инвертора и через первый конденсатор -с входом первого расширителя импульсов и с входом пер ,вого формирователя импульсов управле-f иия,выход которого соединен с управ- ляющим входом второй запоминающей ячейки, а вход через первый резистор-:-с общим выводом устройства, nepBbdt согласующий усилитель, первый вход 00 которого соединен с первой обкладкой ю второго конденсатора, с общим выво1C 4 Ю дом устройства и через последовательно соединенные второй и третий клю чи - с вторым входом первого соглйсукицегоусилителя, с второй обкладкой второго конденсатора, которая .через последовательно соединенные второй резистор и первый ключ соединена с выводом для подключения плюсового зажима источника питания, выходы первого расширителя импульсов и инвертора соединены соответственно с управляюшими входами второго и третьего ключей, выход первого согласующего усилителя соединен с информаци онным входом второй запоминающей

f

Изобретение относится к электроизмерительной технике и может быть использовано в радиоэлектронике и приборостроении при создании устройства для измерения амплитуды синусоидального напряжения инфранизкой частоты.

Известен способ измерения амплитуды синусоидального напряжения, заключающийся в измерении мгновенного значения напряжения в момент времени, отстоящий на 3/4 периода от начала измерения . 1J.

Недостатком данного способа является низкая точность измерения амплитуды синусоидального напряжения в случае, когда в измеряемом сигнале имеется постоянная составляющая. Это обусловлено тем, что при наличии

постоянной составляющей длительность положительного полупериода, фиксируемого по моментам перехода через нуль измеряемого напряжения, оказывается не равной длительности отрицательного полупериода. В этом случае момент измерения оказьшается смещенным относительно максимального значения измеряемого сигнала, что и определяет появление погрешности

при измерении. Наиболее близким к предлагаемому по. технической сущности является способ измерения амплитуды синусоидального напряжения инфранизкой частоты, основанньш на заряде накопительной емкости измеряемым напряжением, вьщелении временного интервала соответствующего полупериоду измеряемого напряжения, преобразовании его линейно нарастающего напряжения и запоминании его максимальной амплитуды, делении запомненного напряжения на два, сравнении полученного в результате деления сигнала с линейно нарастающим напряжением и запоминании в момент равенства указанных напряЛсений амплитуды измеряемого напряжения 2. Недостатком этого способа являетс низкая точность измерения .амплитуды синусоидального напряжения, если в измеряемом сигнале содержится постоянная составляющая. Указанный недостаток обусловлен тем, что при наличии постоянной составляющей амплитуда положительного полупериода, фикси руемого в момент максимального значения измеряемого сигнала, оказывает ся не равной амплитуде отрицательного полупериода на величину этой соетавляющей, что и определяет появлени погрешности измерения. IЦель изобретения - повьппение точности измерения. Поставленная цель достигается тем., что согласно способу измерения амплитуды синусоидального напряжения инфранизкой частоты, основанному на заряде накопительной емкости измеряе мым напряжением и вьщелении временно го интервала, соответствующего положительному полупериоду измеряемого напряжения, преобразовании его линей но нарастающего напряжения, запомина нии его максимальной амплитуды,умень шении запомненного напряжения в два раза, сравнении полученного в резуль тате уменьшения -сигнала с линейно нарастающим напряжением, запоминании амплитуды измеренного напряжения в момент равенства отмеченных напряжений, одновременно с вьщелением временного интервала, соответствующего положительному полупериоду, выделяют отрицательный полупериод измеряемого напряжения, затем запоминают его мак симальную амплитуду уменьшают ее в два раза, полученное в результате уменьшения напряжение суммируют с уменьшенной в два раза максимальной амплитудой положительного полупериоа.. . . . Известно устройство для осуществления известного способа измерения амплитуды синусоидального напряжения инфранизкой частоты, содержащее формирователь линейно нарастающего напряжения, включающий первый компаратор, первый и второй резисторы, первый, второй и третий ключи, расширитель импульсов, первый и второй конденсатор, согласующий усилитель. Устройство содержит также первую и вторую запоминающие ячейки, первый и второй формирователи импульсов управления, четвертый и третий резисторы, второй компаратор. При этом первый вход первого компаратора соединен с общим выводом устройства и с одним из выводов, являющимся первым входом устройства, второй вход соединен с информационным входом первой запоминающей ячейки, а выход соединен с управляющим входом первого ключа, с входом инвертора и через первый конденсатор - с входом первого расширителя импульсов и с входом первого формирователя импульсов управления, выход которого соединен с управляющим входом второй запоминающей ячейки, а вход через первый резистор - с общим выводом устройства, первый согласующей усипитель, первый вход которого соединен с первой обкладкой второго конденсатора, с общим выводом устройства и через после- , довательно соединенные второй, и третий ключи - с вторым входом первого согласующего усилителя, с второй обкладкой второго конденсатора, которая через последовательно соединенные второй резистор и первый ключ соединена с выводом для подключения плюсового зажима источника питания, выходы расширителя импульсов и инвертора соеди«ены соответственно с управляющими входами второго и третьего ключей, выход согласующего усилителя соединен с информационным входом второй запоминакнцей ячейки и с одним из.входов второго компаратора, другой вход которого через третий резистор соединен с выходом второй запоминающей ячейки и черьз четвертый резистор с общим вьгоодом устройства, выход второго компаратора через второй формирователь импульсов управления соединен с управляющим входом первой запоминающей ячейки, выход которой соединен с выводом, являющимся выходом устройства и предназначенным для подключения измерительного пр ибора. Недостатком ,э.того устройства является низкая точность измерения амплитуды синусоидального напряжения при наличии в измеряемом сигнале постоянной составляющей. : Цель изобретения - повышение точ ности измерения. Поставленная цель достигается тем, что в устройство для измерения амплитуды синусоидального напряжения инфранизкой частоты, содержащее первый компаратор, первый вход которого соединен с общим выводом устройства с одним из выводов,являющимся первым входом устройства, второй вход соеди нен с одним из выводов, являющимся вторым входом устройства, с информационным входом первой запоминающей ячейки, а выход соединен с управляющим входом первого ключа, с входом инвертора и через первый конденсатор с входом первого расширителя импульсов и с входом первого формирователя импульсов управления, выход которого соединен с управляющим входом второй запоминающей ячейки, а вход через первый резистор - с общим выводом устройства, первьй согласующий усилитель, первьй вход которого соединен с первой обкладкой второго конденсатора, с общим вьшодом устройства и через последовательно соединенные второй и третий ключи - с вторым входом первого согласующего усилителя, с второй обкладкой второго конденсатора, которая через последовательно соединенные второй резистор и первьй ключ соединена с выводом для подключения плюсового зажима источника питания, выходы первого расширителя импульсов и инвертора соединены соответственно с управляющими входами второго и третьего ключей, выход первого согласующего усилителя соединен с информационным :входом второй запоминающей ячейки и с одним из входов второго компаратора, другой вход которого через третий резистор соединен с выходом второй запоминающей ячейки и через четвертьй резистор с общим выводом устройства, выход второго компаратора , через второй формирователь импульсов управления соединен с уп|)авляющим входом первой запоминаюпгей ячейки, введены пятый, шестой,, седьмой, восьмой, девятый, десятый, одинннадцатый резисторы, второй расщиритель импульсов, третья и четвертая запоминающие ячейки, третий компаратор, третий и четвертьй формирователи импульсов управления, второй согласующий усилитель, сумматор, третий конденсатор, четвертый, пятый и шестой ключи, причем первый вход второго согласующего усилителя соединен с первой обкладкой треть его конденсатора, с общим выводом устройства и через последовательно соединенные .четвертьй и пятьй ключи с вторым входом второго согласующего усилителя, с второй обкладкой третьего конденсатора, которая через пос ледовательно соединенные пятьй резистор и шестой ключ соединена с выводом для подключения плюсового зажима источника питания, выход первого компаратора соединен с управляющим входом пятого ключа, выход инвертора соединен с управляющим входом шестого ключа, вход первого расширителя импульсов соединен через третий формирователь импульсов управления с управляющим входом третьей запоминающей ячейки и через второй расширитель импульсов с управляющим входом четвертого ключа, вьссод второго согласующего усилителя соединен с информационным входом третьей запоминающей ячейки и с одним из входов третьего компаратора, один из входов которого через шестой везисторсоединен с выходом третьей зап6минаюп(ей ячейки и через седьмой резистор с общим выводом устройства, выход третьего компаратора через четвертьй управляющий формирователь импульсов управления соединен с управляющим входом четвертой запоминающей ячейки, информационньй вход которой соединен с информационным входом первой запоминающей чейки, сумматор, первьй вход котоого через восьмой резистор соединен выходом первой запоминающей ячейки через девятый резистор с общим ыводом устройства, второй вход умматора через десятьй резистор оединен с выходом четвертой запомиающей ячейки и через одиннадцатьй езистор с обтдим вьгоодом устройства.

выход сумматора соединен с выводом, являющимся выходом устройства.и предназначенным для подключения измерительного прибора.

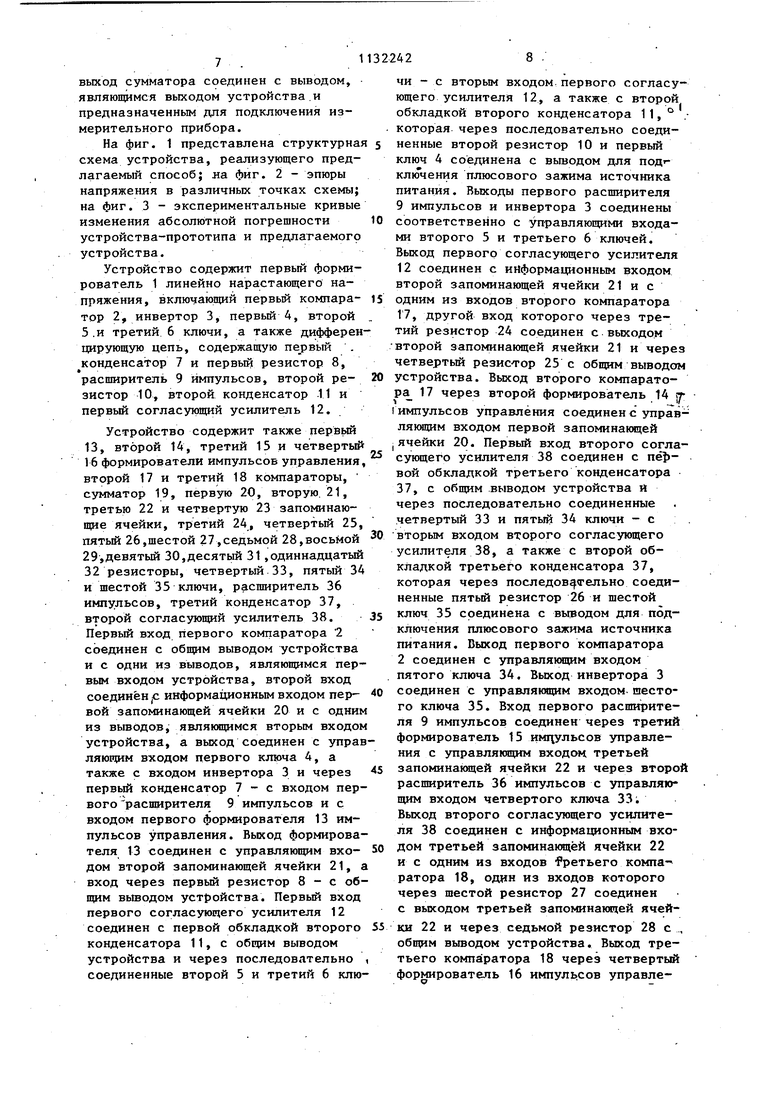

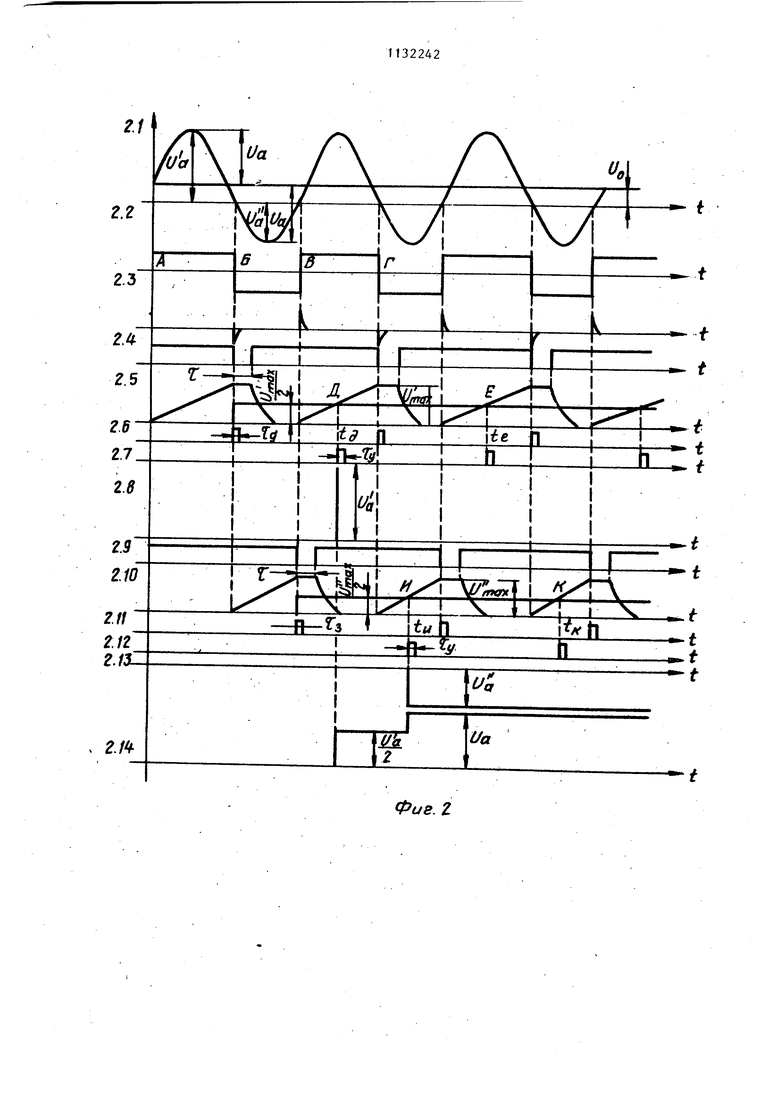

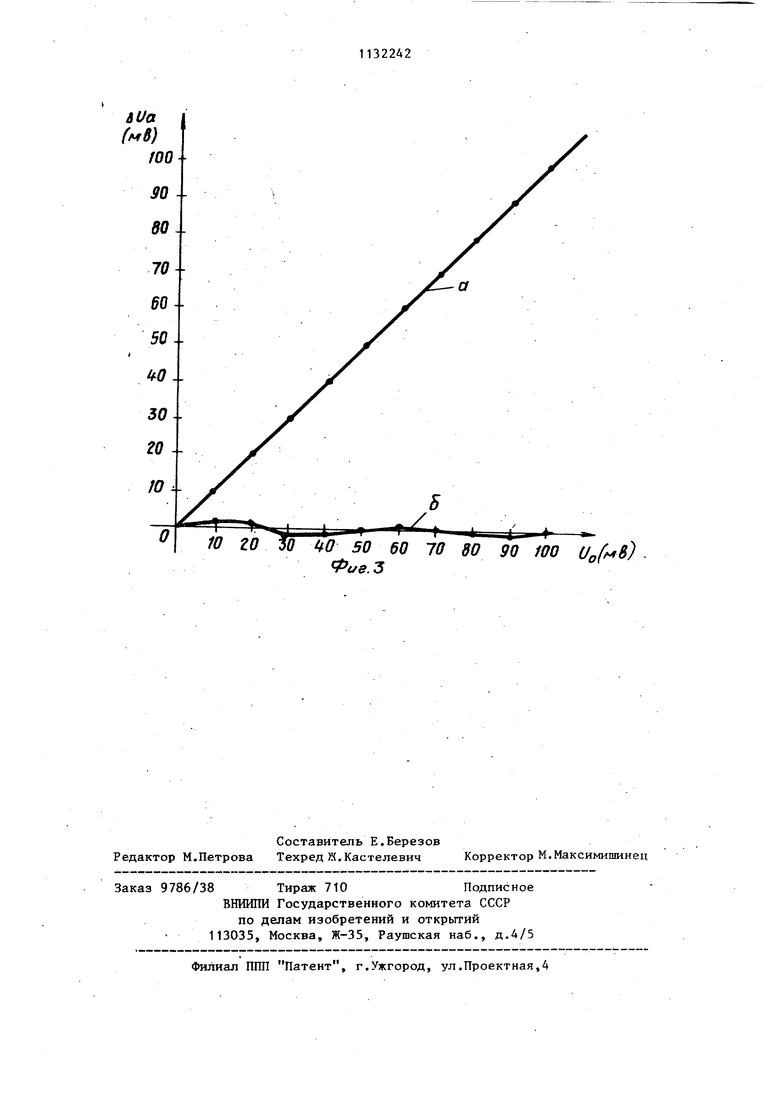

На фиг. 1 представлена структурная схема устройства, реализующего предлагаемый способ; на фиг. 2 - эпюры напряжения в различных точках схемы; на фиг. 3 - экспериментальные кривые изменения абсолютной погрешности устройства-прототипа и предлагаемого устройства.

Устройство содержит первый формирователь 1 линейно нарастающего напряжения, включающий первый компаратор 2, инвертор 3, первый 4, второй 5 .и третий 6 ключи, а также дифференцирующую цепь, содержащую конденсатор 7 и первый резистор 8, расширитель 9 импульсов, второй резистор 10, второй конденсатор 11 и первый согласующий усилитель 12.

Устройство содержит также первый 13, второй 14, третий 15 и четвертый 16 формирователи импульсов управления, второй 17 и третий 18 компараторы, сумматор 19, первую 20, вторую. 21, третью 22 и четвертую 23 запоминающие ячейки, третий 24, четвертый 25, пятый 26,шестой 27,седьмой 28,восьмой 29,девятый 30,десятый 31,одиннадцатый 32 резисторы, четвертый 33, пятый 34 и шестой 35 ключи, расширитель 36 импульсов, третий конденсатор 37, второй согласующий усилитель 38. Первый вход первого компаратора 2 соединен с общим выводом устройства и с одни из выводов, являющимся первым входом устройства, второй вход соединён jC информационным входом первой запоминающей ячейки 20 и с одним из вывсэдов, являющимся вторым входом устройства, а выход соединен с управляющим входом первого ключа 4, а также с входом инвертора 3 и через первый конденсатор 7 - с входом первого расширителя 9 импульсов и с входом первого формирователя 13 импульсов управления. Выход формирователя 13 соединен с управляющим входом второй запоминающей ячейки 21, а вход через первый резистор 8 - с общим выводом уст1)ойства. Первый вход первого согласующего усилителя 12 соединен с первой обкладкой второго конденсатора 11, с общим выводом устройства и через последовательно i соединенные второй 5 и трети7Ч 6 ключи - с вторым входом,первого согласующего усилителя 12, а также с второй обкладкой второго конденсатора 11, которая через последовательно соединенные второй резистор 10 и первый ключ 4 соединена с вьшодом для под-ключения плюсового зажима источника питания. Выходы первого расширителя 9 импульсов и инвертора 3 соединены соответственно с управляющими входами второго 5 и третьего 6 ключей. Выход первого согласующего усилителя 12 соединен с информационным входом второй запоминающей ячейки 21 и с одним из входов второго компаратора 17, другой вход которого через третий резистор 24 соединен с выходом

второй запоминающей ячейки 21 и через четвертый резистор 25 с общим выводом устройства. Выход второго компаратора 17 через второй формирователь 14 гг

I импульсов управления соединен с управлякнцим входом первой запоминающей

I ячейки 20. Первый вход второго согласующего усилителя 38 соединен с первой обкладкой третьего конденсатора 37, с общим выводом устройства и через последовательно соединенные .четвертый 33 и пятый 34 ключи - с : вторым входом второго согласующего усилителя 38, а также с второй обкладкой третьего конденсатора 37, которая через последовательно соединенные пятый резистор 26 и шестой ключ 35 соединена с выводом для подключения плюсового зажима источника питания. Быход первого компаратора 2 соединен с управляющим входом пятого ключа 34. Выход инвертора 3 соединен с управлякицим входом шестого ключа 35. Вход первого расширителя 9 импульсов соединен через третий формирователь 15 имдульсов управления с управлякицим входом третьей запоминакщей ячейки 22 и через второй расширитель 36 импульсов с управляющим входом четвертого ключа 33; Выход второго согласующего усилителя 38 соединен с информационным входом третьей запоминающей ячейки 22 и с одним из входов fpeTbero компаратора 18, один из входов которого через шестой резистор 27 соединен с выходом третьей запоминающей ячейки 22 и через седьмой резистор 28 с , общим выводом устройства. Выход третьего компаратора 18 через четвертый формироватапь 16 импульсов управлеиия соединен с управляющим входим четвертой запоминающей ячейки 23, информационный вход которой соединен с информационным входом первой запоминающей ячейки. Первый вход . сумматора 19 через восьмой резистор 29 соединен с выходом первой запоминающей ячейки 20 и через девятьй резистор 30 с общим вьгоодом устройства. Второй вход сумматора 19 через десятьй резистор 31 соединен с выходом четвертой запоминающей ячейки 23 и через одиннадцатый резистор 32 с общим выводом устройства. Выход сумматора 19 соединен с выводом, являющимся выходом устройства и предназначенным для подключения измерительного прибора. При этом второй расширитель 36 импульсов, третий конденсатор 37, второй согласующий усилитель 38, пятьй резистор 26, четвертый 33, пятый 34 и шестой 35 ключи образуют второй формирователь 39 линейно нарастающего напряжения.

Устройство работает следующим образом.

При включении к входным выводам синусоидального напряжения инфранизкой частоты (фиг. 2.1) на выходе компаратора 2 формируются прямоугольные импульсы (фиг. 2.2). Положительным импульсом с выхода компаратора 2 замыкается ключ Д, а ключ 6 запирается импульсом с вькода инвертора 3. 35 Вследствие этого на участке А-Б (фиг. 2.2) конденсатор 11 линейно заряжается через резистор 10 (фиг. 2.5). На резисторе.8 вьщеляются дифференциальные импульсы фиг. 2.31,40 соответствующие моментам перехода . входным сигналом через нулевое значение. На каждьй отрицательньй импульс расширителем 9 формируется управляющий импульс длительностью t 45 (фиг. 2.4), под действием которого кшюч 5 размыкается, предотвращая разряд конденсатора 11. После окончания управляющего импульса конденсатор 11 быстро разряжается через замкну- 50 тые ключи 5 и 6. В результате этого на выходе усилителя 12 формируется линейно нарастающее напряжение (фиг. 2.5), амплитуда которого Umox пропорциональна длительности поло- 55 жительного полупериода входного сигнала. Формирователем 13 на каждый отрицательньй импульс с выхода дифференцирующей цепи формируется импульс записи (фиг. 2.6), которым на время задержки t за р 1кается входной ключ запоминающей ячейки 21. Параметры формирователя 13 выбраны так, чтобы выполнялось условие Т . В этом случае в ячейке 21 записывается напряжение Uitnu равное мак$симальному значению линейно нарастающего напряжения. Напряжение Umax , деленное резисторами 24 и 25 пополам, поступает на первый вход компаратора 17, на второй вход которого поступает линейно нарастающее напряжение с выхода усилителя 12. В момент равенства напряжений на входах компаратора 17 на его выходе возникают перепады напряжения. По положительным перепадам напряжений в моменты времени t3,te (точки Л, Е на фиг. 2.5) формирователем 14 формируются управляющие импульсы длительностью Ту (фиг. 2.7), временное положение которых соответствует моментам про-, хождения входным сигналом через максимум амплитуды напряжения UA положительного полупериода. На время t ij замыкается входной ключ запоминающей ячейки 20. В результате этого на выходе ячейки 20, начиная с момента времени 73 (фиг. 2.5), устанавливается постоянное напряжение (фиг. 2.8), равное амплитуде положительной полуволны входного сигнала

,

где УЙ - истинное значение амплитуды синусоидального напряжения инфранизкой частоты; UQ - величина постоянной составляющей напряжения.

Напряжение Ud , уменьшенное на резисторах 29 и 30 пополам, поступает на неинвертирующий вход сумматора 19. Отрицательным импульсом с вькода компаратора 2 запирается ключ 34, а ключ 35 замыкается импульсом с выхода |1нвертора 3. На участке Б-В (фиг. 2.2) конденсатор 37 линейно заряжается через резистор 26. (фиг. 2.10). На каждьй положительный мпульс с выхода дифференцирующейцепи (фиг. 2.3) расширителем 36 имульсов формируется управляющий импульс длительностью Т (фиг. 2.9), под действием которого ключ 33 разыкается, предотвращая разряд кондр сатора 37. После окончания управляющего импульса конденсатор 37 быстро разряжается через замкнутые ключи 33 и 34. В результате на выходе усилителя 38 формируется линейно нарастающее напряжение (фиг. 2.10), амплиту да которого и ttia« пропорциональна длительности отрицательного полупериода входного сигнала. Формирователем 15 каждый положительный импульс с выхода дифференцирующей цепи формируется импульс записи (фиг. 2.11), которым на время L 5 замыкается входной ключ запоминающей ячейки 22. Параметры формирователя 15 выбраны так, чтобы вьтолнялось условие .в этом случае в ячейке 22 записывается напряжение Umax равное максимальному значению линейно нарастающего напряжения. Напряжение U тлх, деленное на резисторах 27 и 28 пополам, поступает на первый вход компаратора 18, на второй вход которого поступает линейно нарастающее напряжение с выхода усилителя 38. В моменты равенства напряжений на входах компара тора 18 на его выходе возникают пере пады напряжений.. По положительным перепадам напряжений в моменты времени tu , tie (точки И, К, на фиг.а.ю формирователем 16 формируются управляющие импульсы длительностью tvj (фиг. 2.12), временное положение которых соответствует моментам прохождения входным сигналом через максимум амплитуды напряжения U отрицательного полупериода. На время Li замыкается входной ключ запоминающей ячейки 23. В результате на выходе ячейки 23, начиная с момента времени ty (точка И на фиг. 2.10), устанавливается постоянное напряжени (фиг. 2.13), равное амплитуде напряжения отрицательной полуволны входного сигнала UQ-UCI-UOЭто напряжение, деленное резисторами 31 и 32 пополам, поступает на втсТрой вход (инвертирующий) сумматора 19. На выходе сумматора устанавливается напряжение, равное Uk / UA 1- { Uft-Uo . I г. / - Uu Jbro-bUa-iTn ,1, т.е. истинной амплитуде синусоидального напряжения инфранизкой частоты (фиг. 2.13). Это напряжение на выходе устройства может быть измерено любым вольтметром постоянного тока. На фиг, 3 приведены экспериментальные кривые изменения абсолютной погрешности прототипа (кривая Л ) и предлагаемого изобретения (кривая 5 ) в зависимости от величины постоянной составляющей в измеряемом сигнале. Из анализа графиков следу-, ет, что погрешность прототипа растет пропорционально величине постоянной составляющей, а то время как погрешность предлагаемого изобретения практически не зависит от величины постоянной составляющей и приблизительно равна нулю. Данное устройство, реализующее предлагаемый способ, позволяет измерять амплитуду синусоидального напряжения инфранизкой частоты с более высокой точностью, чем устройство-прототип.

Фиг.г

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-12-30—Публикация

1983-09-30—Подача