со 1C

dt&

со

05

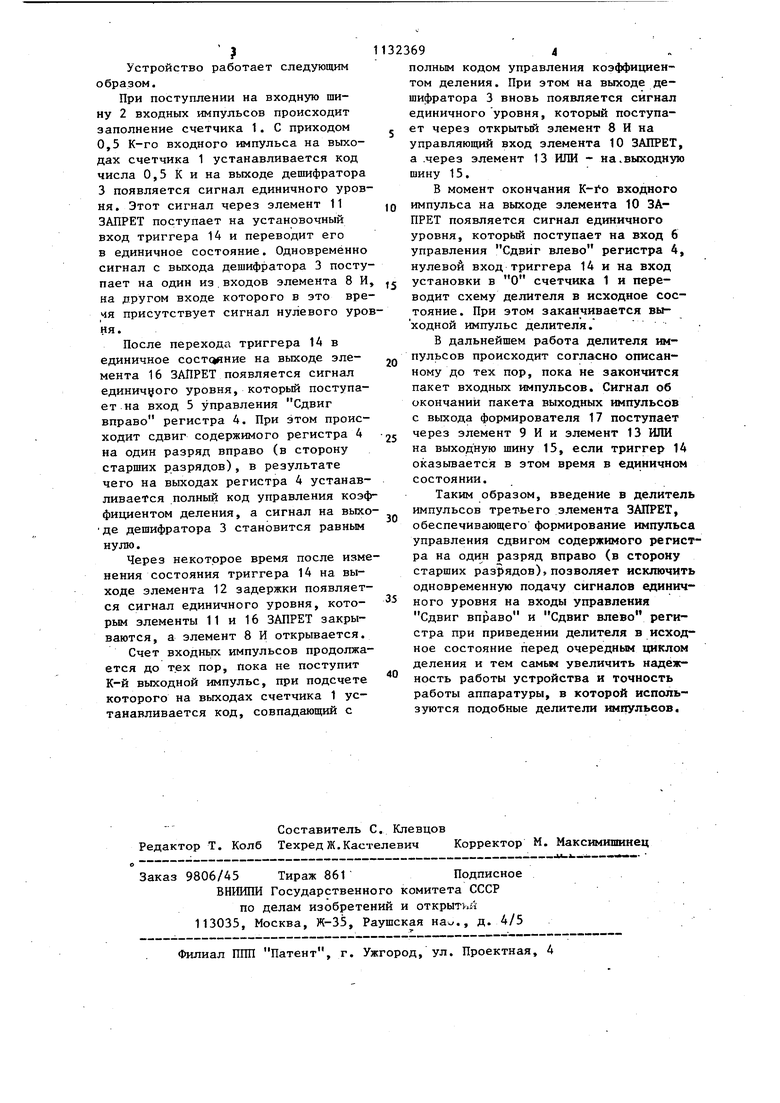

со Изобретение относится к импульсной технике и может быть использова но для деления импульсов, сгруппиро ванных в пакеты импульсов. По основному авт. св. № 913601 известен делитель импульсов, содержащий п-разрядный счетчик с входом установки в О, счетньш вход которого соединен с входной шиной, деши ратор, первая группа входов которого соединена с выходами счетчика, сдвиговый регистр с входами управления Сдвиг вправо и Сдвиг влево входы которого соединены с шинами кода управления 5 а выходы подключены к второй группе входов дешифратора, первый и второй элементы И, первый и второй элементы ЗАПРЕТ, элемент задержки, элемент ИЛИ и триггер, выход которого соединен с первым входом второго элемента И и входом элемента задержки, выход которого соединен с первым входом первого элемента И и запрещающим входом второго элемента ЗАПРЕТ, управляющий вход которого соединен со вторым входом первого элемента И и выходом дешифратора, а выход второго элемента ЗАПРЕТ соединен с установочным входом триггера, вход сбро са которого соединен со входом управления Сдвиг влево регистра, входом установки в О счетчика и выходом первого элемента ЗАПРЕТ, запрещающий вход которого соединен с входной шиной, а управляющий - с выходо| 1 первого элемента И и первым входом элемента ИЛИ, второй вход которО|ю соединен с выходом второго элемента И, а выход элемента ИЛИ соединен с выходной шиной CU. Недостаток такого делителя импульсов заключается в том, что в пр ,цессе приведения его в исходное с.остояние перед очередным циклом де ления на входы Сдвиг вправо и : Сдвиг влево регистра в течение не которого промежутка времени одновременно поступают управляющие сигналы. Это может привести к искажени информации, записанной в регистре и как следствие этого, к нарушению работы делителя. Цель изобретения - повьш1ение надежности работы делителя импульсов. Поставленная цель достигается те что в делитель импульсов введен тре тий элемент ЗАПРЕТ, выход которого соединен с входом управления Сдвиг 69 вправо регистра, запрещающий вход соединен с выходом элемента задержки, а управляющий - с выходом триггера. На чертеже представлена схема делителя импульсов. Делитель импульсов содержит п-разрядный счетчик 1 с входом установки в О, счетньй вход которого соединен с входной шиной 2, дешифратор 3, первая группа входов которого соединена с выходами счетчика 1, сдвиговьй регистр входами . управления Сдвиг рправо 5 и Сдвиг влево 6, входы которого соединены с шинами 7 кода уп(Равления, а выходы подклк чены к второй группе входов дешифратора 3, первый и второй элементы 8 и 9 И, первый и второй элементы 10 и 11 ЗАПРЕТ, элемент 12 задержки, элемент 13 ИЛИ и триггер 14, выход которого соединен с первым входом второго элемента 9 И и входом элемента 12 задержки, выход которого соединен с первым входом первого элемента 8 И и запрещающим входом второго элемента 11 ЗАПРЕТ, управляющий вход которого соединен со вторым входом первого элемента 8 И и с выходом дешифратора 3, а выход второго элемен,та 11 ЗАПРЕТ соединен с установочным входом триггера 14, вход сброса которого соединен со входом 6 управ-, ления Сдвиг влево регистра, входом установки в О счетчика 1 и выходом первого элемента 10 ЗАПРЕТ, запрещающий вход которого соединен с входной шиной 2, а управляющий - с выходом первого элемента 8 И и первьм входом элемента 13 ИЛИ, второй вход которого соединен с выходом второго элемента 9 И, а выход элемента 13 ИЛИ соединен с выходной шиной 15, третий элемент 16 ЗАПРЕТ, выход которого соединен с входом 5 управления Сдвиг вправо регистра 4,запрещающий вход соединен свыходом элемента задержки 12, а управляющий вход - с выходом триггера 14. В исходном положении двоичный счетчик 1 и триггер J4 установлены нулевые состояния. Код управления оэффициентом деления К записан в оответствующие ячейки памяти региста 4. При этом на вторзто группу вхоов дешифратора 3 поступает код полоинного коэффициента деления. Устройство работает следующим образом. При поступлении на входную шину 2 входных импульсов происходит заполнение счетчика 1. С приходом 0,5 К-го входного импульса на выходах счетчика 1 устанавливается код числа 0,5 К и на выходе дешифратора 3 появляется сигнал единичного уров ня. Этот сигнал через элемент 11 ЗАПРЕТ поступает на установочный вход триггера 14 и переводит его в единичное состояние. Одновременно сигнал с выхода дешифратора 3 посту пает на один из входов элемента 8 И на другом входе которого в это вре чя присутствует сигнал нулевого уро ня. После перехода триггера 1А в единичное состояние на выходе элемента 16 ЗАПРЕТ появляется сигнал единичного уровня, который поступает на вход 5 управления Сдвиг вправо регистра 4. При этом происходит сдвиг содержимого регистра 4 на один разряд вправо (в сторону старших разрядов), в результате чего на выходах регистра 4 устанавливается полный код управления коэф фициентом деления, а сигнал на выхо де дешифратора 3 становится равным нулю. Через некоторое время после изме нения состояния триггера 14 на выходе элемента 12 задержки появляется сигнал единичного уровня, кото рым элементы 11 и 16 ЗАПРЕТ закрываются, а элемент 8 И открывается. Счет входных импульсов продолжа ется до тех пор, пока не поступит К-й выходной импульс, при подсчете которого на выходах счетчика 1 устанавливается код, совпадающий с 694. полным кодом управления коэффициентом деления. При этом на выходе дешифратора 3 вновь появляется сигнал единичного уровня, который поступает через открытый элемент 8 И на управляющий вход элемента 10 ЗАПРЕТ, а .через элемент 13 ИЛИ - на выходную шину 15. В момент окончания K-fo входного импульса на выходе элемента 10 ЗАПРЕТ появляется сигнал единичного уровня, который поступает на вход 6 управления Сдвиг влево регистра А, нулевой вход триггера 14 и на вход установки в О счетчика 1 и переводит схему делителя в исходное состояние. При этом заканчивается выходной импульс делителя. В дальнейшем работа делителя импульсов происходит согласно описанному до тех пор, пока не закончится пакет входных импульсов. Сигнал об окончаний пакета выходных импульсов с выхода формирователя 17 поступает через элемент 9 И и элемент 13 ИЛИ на выходную шину 15, если триггер 14 оказывается в этом время в единичном состоянии. Таким образом, введение в делитель импульсов третьего элемента ЗАПРЕТ, обеспечивающего формирование импульса управления сдвигом содержимого регистра на один разряд вправо (в сторону старших разрядов), позволяет исключить одновременную подачу сигналов единичного уровня на входы управления Сдвиг вправо и Сдвиг влево регистра при приведении делителя в исходное состояние перед очередным циклом деления и тем самьм увеличить надежность работы устройства и точность работы аппаратуры, в которой используются подобные делители импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Симметричный делитель частоты импульсов | 1982 |

|

SU1089763A2 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1307587A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1547057A2 |

| Устройство для измерения времени установления выходного сигнала цифроаналогового преобразователя | 1990 |

|

SU1716601A2 |

| Устройство для преобразования частоты следования импульсов | 1978 |

|

SU764114A1 |

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

| Устройство для регистрации однократныхпРОцЕССОВ | 1978 |

|

SU842936A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОГО КОДИРОВАНИЯ | 1972 |

|

SU354409A1 |

| Умножитель частоты следования импульсов | 1982 |

|

SU1038943A1 |

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

ДЕЛИТЕЛЬ ИМПУЛЬСОВ по авт. св. № 913601, отличающийся тем, что, с целью повьппения надежности работы, в него введен третий элемент ЗАПРЕТ, выход которого соединен со входом управления , Сдвиг вправо регистра, запрещающий вход соединен с выходом элемента задержки, а управляющий вход - с выходом триггера.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № 913601, кл | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

Авторы

Даты

1984-12-30—Публикация

1983-09-23—Подача