12

%

О СЛ

sl

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники, а также в синтезаторах частот.

Цель изобретения - уменьшение побочных составляющих в спектре выходного сигнала.

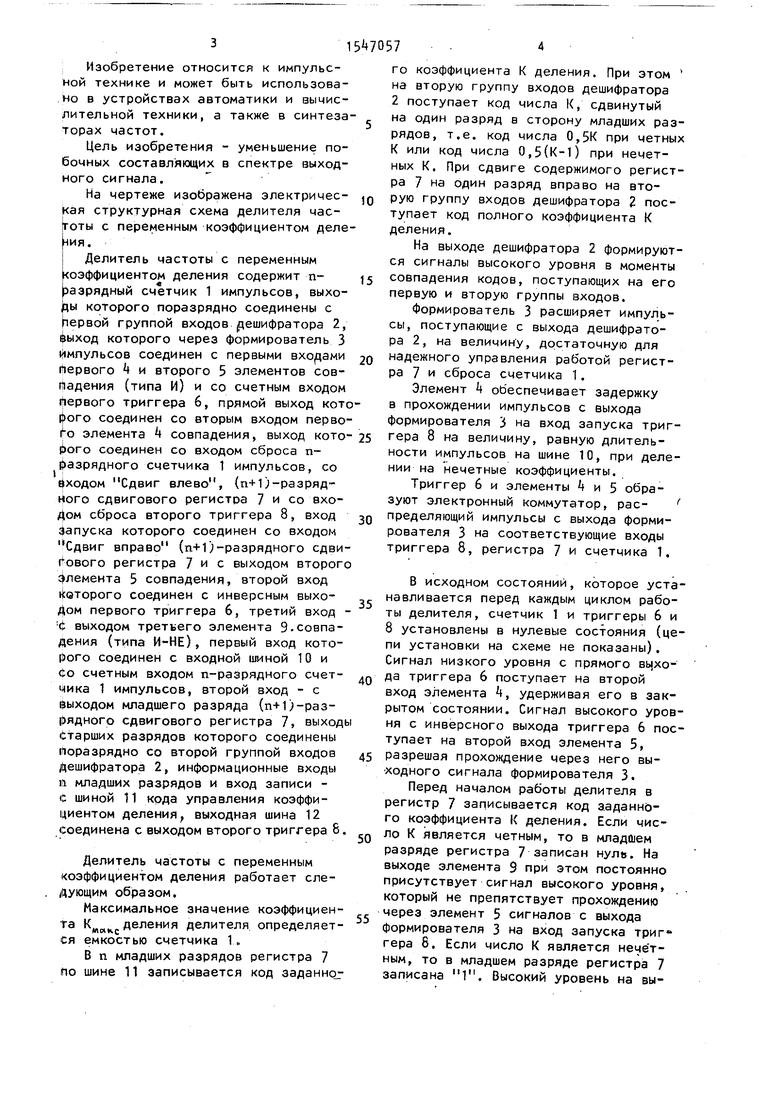

На чертеже изображена электричес- Кая структурная схема делителя частоты с переменным коэффициентом деления.

Делитель частоты с переменным коэффициентом деления содержит п- разрядный счетчик 1 импульсов, выходы которого поразрядно соединены с Первой группой входов дешифратора 2, фыход которого через формирователь 3 импульсов соединен с первыми входами Первого и второго 5 элементов совпадения (типа И) и со счетным входом первого триггера 6, прямой выход которого соединен со вторым входом первого элемента совпадения, выход кото- рого соединен со входом сброса п- разрядного счетчика 1 импульсов, со йходом Сдвиг влево, (п-М)-разрядного сдвигового регистра 7 и со входом сброса второго триггера 8, вход Запуска которого соединен со входом Сдвиг вправо (п+1)-разрядного сдвигового регистра 7 и с выходом второго Элемента 5 совпадения, второй вход Которого соединен с инверсным выходом первого триггера 6, третий вход - и выходом третьего элемента 9.совпадения (типа И-НЕ), первый вход которого соединен с входной шиной 10 и Со счетным входом n-разрядного счет- чика 1 импульсов, второй вход - с йыходом младшего разряда (п+1)-разрядного сдвигового регистра 7, выходы Старших разрядов которого соединены поразрядно со второй группой входов дешифратора 2, информационные входы п младших разрядов и вход записи - С шиной 11 кода управления коэффициентом деления, выходная шина 12 соединена с выходом второго триггера 8.

Делитель частоты с переменным коэффициентом деления работает следующим образом.

Максимальное значение коэффициента Кмик деления делителя определяется емкостью счетчика 1.

В п младших разрядов регистра 7 Гю шине 11 записывается код заданно

5 0 5 0 „ 5

5

0

5

го коэффициента К деления. При этом на вторую группу входов дешифратора 2 поступает код числа К, сдвинутый на один разряд в сторону младших разрядов, т.е. код числа 0,5К при четных К или код числа 0,5(К-1) при нечетных К. При сдвиге содержимого регистра 7 на один разряд вправо на вторую группу входов дешифратора 2 поступает код полного коэффициента К деления.

На выходе дешифратора 2 формируются сигналы высокого уровня в моменты совпадения кодов, поступающих на его первую и вторую группы входов.

Формирователь 3 расширяет импульсы, поступающие с выхода дешифратора 2, на величину, достаточную для надежного управления работой регистра 7 и сброса счетчика 1.

Элемент k обеспечивает задержку в прохождении импульсов с выхода формирователя 3 на вход запуска триггера 8 на величину, равную длительности импульсов на шине 10, при делении на нечетные коэффициенты.

Триггер 6 и элементы Ь и 5 образуют электронный коммутатор, рас- пределяющий импульсы с выхода формирователя 3 на соответствующие входы триггера 8, регистра 7 и счетчика 1.

В исходном состоянии, которое устанавливается перед каждым циклом работы делителя, счетчик 1 и триггеры 6 и 8 установлены в нулевые состояния (цепи установки на схеме не показаны). Сигнал низкого уровня с прямого вцхо- да триггера 6 поступает на второй вход элемента А, удерживая его в закрытом состоянии. Сигнал высокого уровня с инверсного выхода триггера 6 поступает на второй вход элемента 5, разрешая прохождение через него выходного сигнала формирователя 3.

Перед началом работы делителя в регистр 7 записывается код заданного коэффициента К деления. Если число К является четным, то в младшем разряде регистра 7 записан нуль. На выходе элемента 9 при этом постоянно присутствует сигнал высокого уровня, который не препятствует прохождению через элемент 5 сигналов с выхода формирователя 3 на вход запуска триггера 8. Если число К является нече т- ным, то в младшем разряде регистра 7 записана 1. Высокий уровень на вы

ходе элемента У, разрешающий прохождение сигналов с выхода формировател 3 через элемент 5, появляется в этом случае только в паузах между входными импульсами на шине 10.

При делении на четные коэффициент делитель работает следующим образом.

С приходом 0,5К-го входного импулса на выходе дешифратора 2 появляется сигнал высокого уровня, который через формирователь 3 и элемент 5 поступает на вход запуска триггера 8 и на вход Сдвиг вправо регистра 7. Триггер 8 при этом переходит в еди ничное состояние, в результате чего на шине 12 начинает формироваться вы ходной импульс, а содержимое регистр

7сдвигается на один разряд вправо. При этом уровень на выходе дешифратора 2 изменяется на низкий. Через некоторое время, определяемое параметрами формирователя 3, уровень на его выходе также становится низким.

8момент окончания выходного импульса формирователя 3 триггер 6 переходит в единичное состояние. При этом элемент 4 открывается, а элемент 5 закрывается.

С приходом К-го входного импульса на выходе дешифратора 2 вновь появляется сигнал высокого уровня, который через формирователь 3 и элемент k поступает на вход сброса триггера 8, на вход сброса сметчика 1 и на вход Сдвиг влево, регистра 7. Триггер 8 при этом переходит в нулевое состоние, в результате чего заканчивается формирование импульса на шине 12. Триггеры счетчика 1 также переходят в нулевые состояния, а содержимое регистра 7 сдвигается на один разряд влево. Уровень на выходе дешифратора 2 становится низким. Через некоторое время становится низким и уровень на выходе формирователя 3, в результате чего триггер 6 переходит в нулевое состояние, закрывая элемент А и открывая элемент 5.

В дальнейшем циклы работы делителя повторяются.

При делении на нечетные коэффициенты делитель работает следующим образом.

С приходом 0,5(К-1)-го входного импульса на выходе дешифратора 2 появляется сигнал высокого уровня, который через формирователь 3 поступает на первый вход элемента 5.

ю

20

25

яы

ь-г а

30

35

40

45

50

55

В момент окончания 0,5(К-1)-го входного импульса на выходе элемента 9 появляется сигнал высокого уровня, в результате чего на выходе элемента 5 также появляется сигнал высокого уровня. При этом триггер 8 переходит в единичное состояние, в ре- . зультате чего осуществляется сдвиг содержимого регистра 7 на один разряд вправо, а уровень на выходе дешифратора 2 становится низким. В момент окончания выходного импульса формирователя 3 триггер 6 переходит в единичное состояние, открывая элемент k и закрывая элемент 5.

С приходом К-го входного импульса срабатывает дешифратор 2 и на выходе формирователя 3 появляется сигнал высокого уровня, в результате чего триггер 8 переключается в нулевое состояние, счетчик 1 устанавливается в состояние нуля и осуществляется сдвиг содержимого регистра 7 на один разряд влево. В момент окончания выходного импульса формирователя 3 триггер 6 переходит в нулевое состояние, закрывая элемент А и открывая элемент 5.

В дальнейшем циклы работы делителя повторяются.

Таким образом, на выходе триггера 8 формируются симметричные выходные импульсы даже при нечетном коэффициенте деления (при условии, что скважность входных импульсов на шине 10 равна двум), а на выходах дешифратора 2 и формирователя 3 - импульсы удвоенной частоты (по отношению к импульсам на шине 12). Формула изобретения Делитель частоты с переменным ко эффициентом деления по авт.св. N° 1307587, отличающийся тем, что, с целью уменьшения побочных составляющих в спектре выходного сигнала, в него введены третий элемент совпадения и триггер, вход сброса которого соединен с выходом первого элемента совпадения, вход запуска - с выходом второго элемента совпадения, третий вход которого соединен с выходом третьего элемента совпадения, первый и второй входы которого соединены соответственно с входной шиной и с выходом младшего разряда сдвигового регистра, который выполнен увеличенным на один разряд.

| название | год | авторы | номер документа |

|---|---|---|---|

| Симметричный делитель частоты импульсов | 1982 |

|

SU1089763A2 |

| Делитель частоты следования импульсов | 1985 |

|

SU1265996A1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1307587A1 |

| Делитель частоты следования импульсов | 1982 |

|

SU1045400A1 |

| Делитель частоты следования импульсов | 1988 |

|

SU1596453A1 |

| Устройство для деления число-импульсного кода на константу | 1981 |

|

SU1012443A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1252939A1 |

| Устройство для цифрового функционального преобразования | 1981 |

|

SU985792A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Делитель импульсов | 1983 |

|

SU1132369A2 |

Изобретение относится к импульсной технике и может использоваться в устройствах автоматики и вычислительной техники, в синтезаторах частот. Цель изобретения - уменьшение побочных составляющих в спектре выходного сигнала - достигается введением элемента 9 совпадения и триггера 8 с организацией новых функциональных связей и выполнением увеличенным на один разряд сдвигового регистра 7. устройство также содержит счетчик 1 импульсов, дешифратор 2, формирователь 3 импульсов, элементы 4 и 5 совпадения, триггер 6, входную и выходную шины 10 и 12 и шину 11 кода управления коэффициентом деления. Выходной сигнал устройства при четных и нечетных коэффициентах деления имеет скважность, равную двум. 1 ил.

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1307587A1 |

Авторы

Даты

1990-02-28—Публикация

1988-05-12—Подача