ei

kn с

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель импульсов | 1983 |

|

SU1132369A2 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1307587A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1547057A2 |

| Устройство для преобразования частоты следования импульсов | 1978 |

|

SU764114A1 |

| Цифровая электронная вычислительная машина последовательного действия | 1976 |

|

SU658564A2 |

| Устройство для деления двоичных чисел | 1982 |

|

SU1103224A1 |

| Устройство для формирования знаков на экране телевизионного индикатора | 1989 |

|

SU1679536A1 |

| Число-импульсное арифметическое устройство | 1980 |

|

SU951303A1 |

| Преобразователь частоты в код | 1985 |

|

SU1356207A1 |

| Арифметическое устройство по модулю | 1991 |

|

SU1809437A1 |

СИММЕТРИЧНЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ HMnyJibCOB по авт.ев К 913601, о тлнчающнй.ся тем, что, с целью увеличения точности симметрирования выходных сигналов делителя при нечетных коэффициентах деления и повышения надежности в работе, в него введены элемент К-НЕ и второй триггер, выход которого сое;: Ш1ен с входом управления регистра Сдвиг вправо и выходной шиной, R -вход подключен к выходу элемента И, а 5 вход - к выходу второго элемента ЗАПРЕТ, второй управляющий вход которого соедш1ен с выходом элемента И-НЕ, первый вход которого соединен с выходом младшего разряда регистра,а второй - с входной шиной.

00

;о

О5

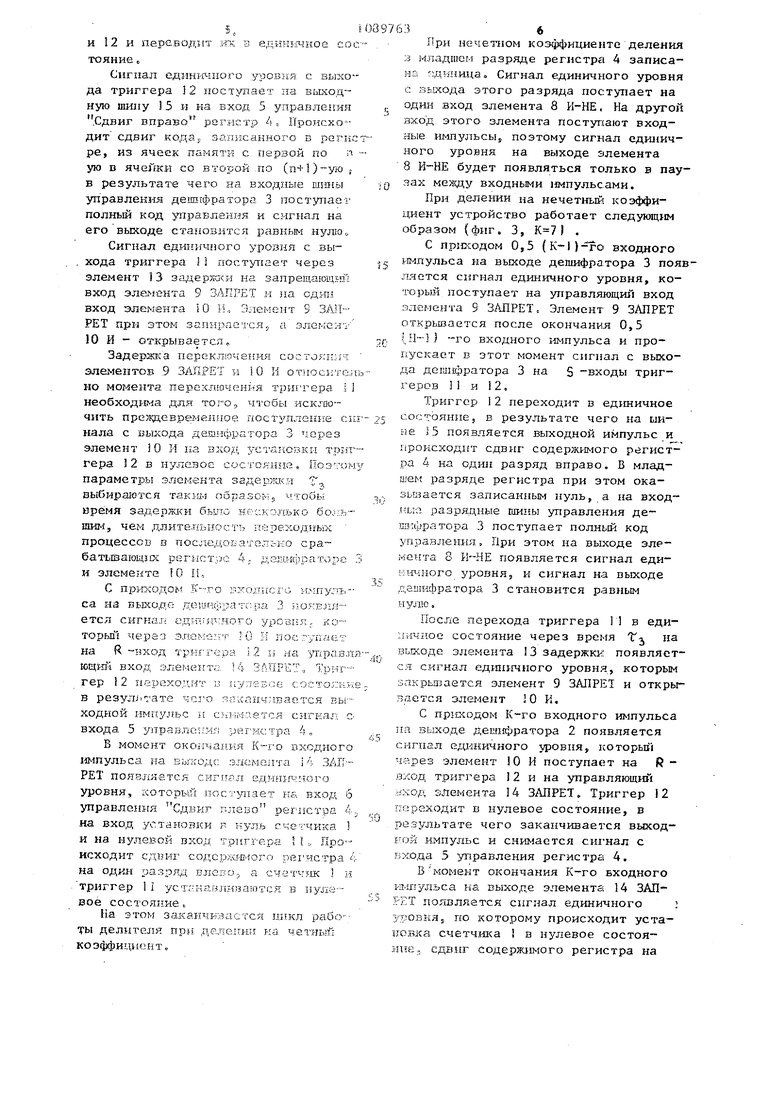

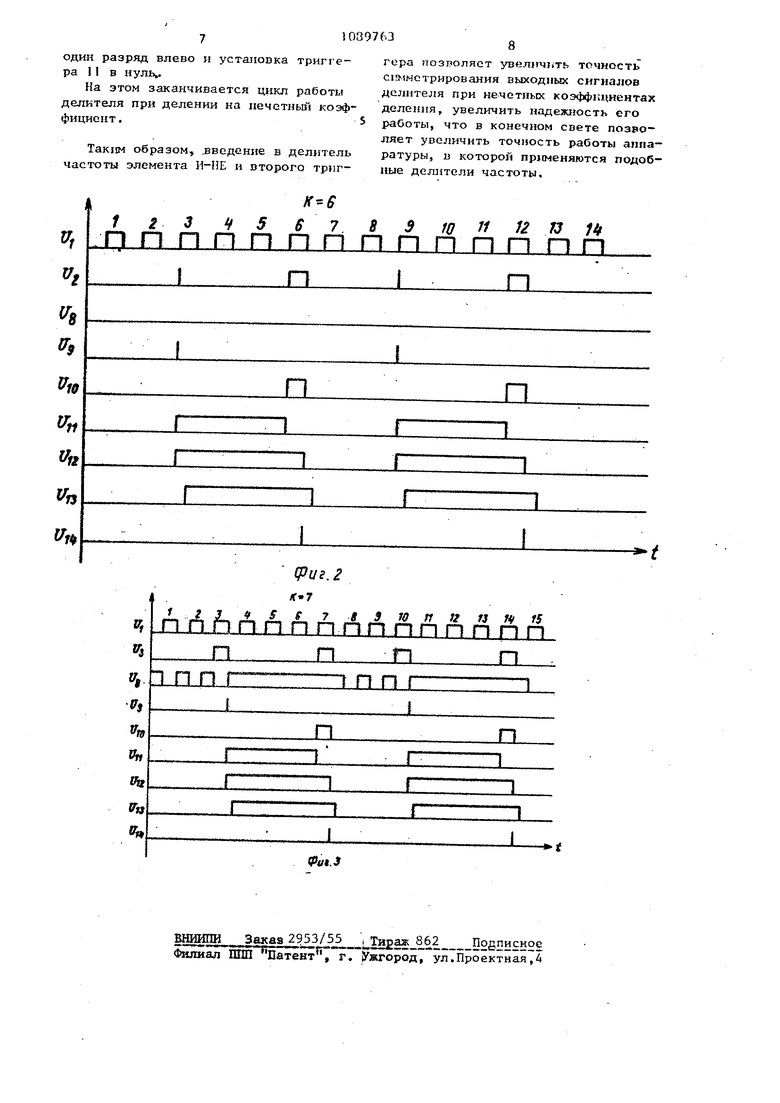

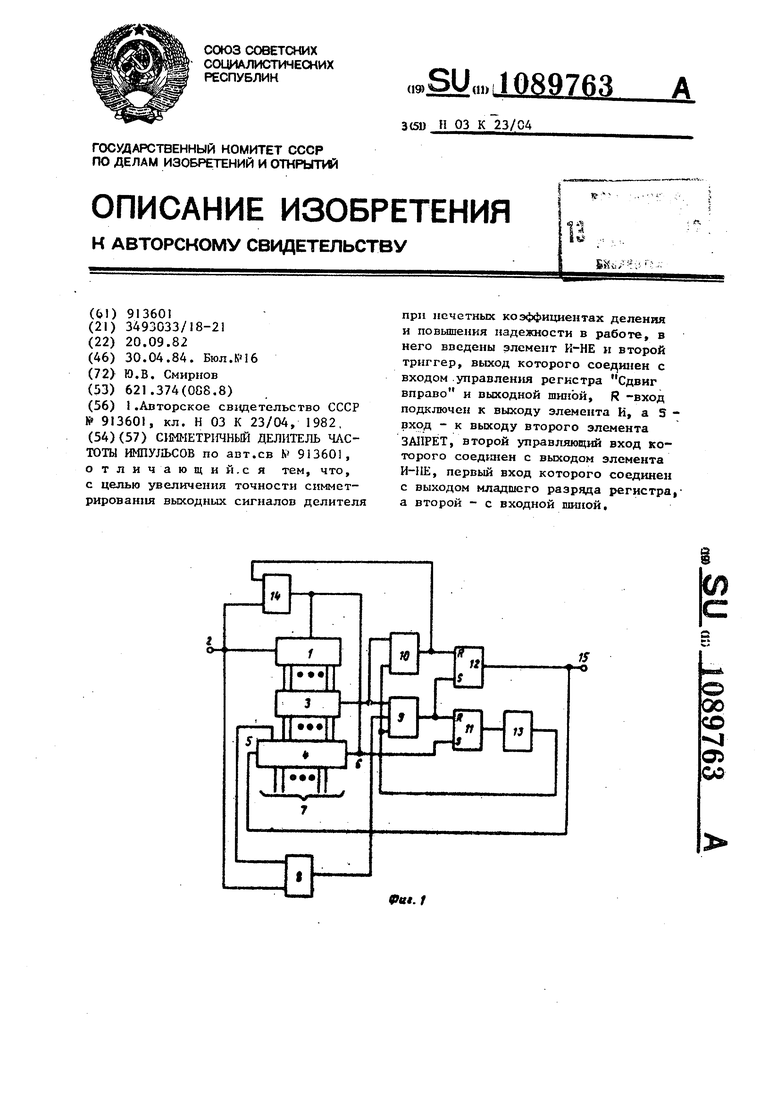

Изобретение относится к импульсной технике и может быть использова но в измерительной аппаратуре, а также в устройствах автоматики и телемеханики. По основному авт.св. 1 913601 известен делитель импульсов, содержащий п -разрядный счетчик с входом установки в нуль, счетный, вход которого соединен с входной шиной, дешифратор, первая группа входов которого соед1мена с выходами счетчика, сдвпгакяций регистр с входами управления соединен с выходами счетчика, сдвигакнций регистр с входами управления Сдвиг вправо и Сдвиг влево,входы которого соединены с кода управления, а выходы подключены к второй группе входов дет18фратора, нервьй н второй элементы И, первый и второй эле менты ЗАПРЁТ, триггер, элемент задержки и элемент ШШ, один вход которого соединен с выходом второго элемента И, од1Ш вход которого соединен с выходом формирователя, а другой - с входом управления регист ра Сдвиг вправо, с выходом триггера и с входом элемента задержки, выход которого соед1шен с одним входом первого элемента И и запрещаклдим входом второго элемента ЗАПРЕТ, управляющий вход которого соединен с пь1ходом дешифратора и однгш входом первого элемента И, а выходс входом установки триггера в единичное состояние, вход установки в нулевое состояние которого соед1П1ен с входом управлениярегистра Сдвиг Влево, входом установки на нуль счетчика импульсов и выходом первого SJKMeHTa ЗАПРЕТ, запрещающий вхо которого соединен с входной шиной, а улравляюций - с выходом первого э мента И и другим входом элемента lUU выход которого соединен с выходной шшюйГи При работе такого делителя на вы ходе триггера с раздельньми входами возникают импульсы симметричной фор мы, однако точность симметрирования импульсов оказьшается недостаточной если коэффициент деления является нечетным числом. Кроме того, в тако делителе импульсов возможно появлен ошибок деления, так как при привед НИИ делителя в исходное состояние п ред очередным циклом деления на вх управления регистра Сдвиг вправо и Сдвиг влево в течение некоторого промежутка времени одновременно поступают сигналы едга1ичного уровня, что может привести к искаженло информации, записанной в регистре. Цель изобретения - увеличение точности и надежности работы делителя импульсов, Поставленная цель достигается тем, что в делитель импульсов, содержащий п -разрядный счетчик с входом установки в нуль, счетный вход которого соединен с входной шиной, дешифратор, первая группа входов которого соединена с выходами счетчика, сдвигающий регистр с входами управления Сдвиг вправо и Сдвиг влево, входы которого соединены с шинами кода управления, а выходы подключены к второй группе входов дешифратора, первый и второй элементы ЗАПРЕТ, элемент И, элемент зад,ержки и первьв триггер, выход которого соед1шен с входом элемента задержка, R -вход соединен с входом управления регистра Сдвиг влево, входом установки счетчика в нуль и выходом первого элемента ЗАПРЕТ, эапрещакщий вход которого соед1шен с входной , а управляющий - с выходом элемента И, один вход которого соединен с выходом элемента задержки и запрещакнцим входом второго элемента. ЗАПРЕТ, выход которого соединен с 5 -входом первого триггера, а первый управляющие вход - с выходом дешифратора н вторым входом элемента И, введены элемент И-НЕ и второй триггер, выход которого соед1шен с входом управления регистра Сдвиг вправо и выХОД110Й шиной, R -вход подключен к выходу элемента Н, а S -вход к выходу второго элемента ЗАПРЕТ, второй управляющий вход которого соединен с выходом элемента И-НЕ, первый вход которого соединен с выходом младшего разряда регистра, а второй - с входной шиной. На фиг,1 представлена схема симметричного делителя частоты импульсов;, на фиг,2 и 3 импульсные диаграммы работы устройства при четном () и нечетном () коэффициенттах деления. Устройство содержит h -разрядный счетчик 1 импульсов, счетный вход которого соединен с входной шиной 2, a выходные шины - с входным разрядньмн шинами дешифратора 3, являющегося, по-сутцеству, компара:тором кодов, сдвигающий регистр 4 с входами управления Сдвиг вправо и Сдвиг влево 6, выходные шины ко торого, за исключением шинц младшег разряда, соединены с : входными тинами управления дешифратора 3, а входные кодовые шины - с шинами 7 кода управления, элемент 8 И-НЕ, эл мент 9 ЗАПРЕТ, элемент 10 И, триггеры 11 и 12, элемент 13 задержки, элемент 14 ЗАПРЕТ и выходную шину 1 Симметричный делитель частоты импульсов содержит п -разрядный сче чик 1 с входом установки в нуль, счетный вход которого соединен с . входной Ы1ШОЙ 2 , дешифратор 3, первая группа входов которого соединена с выходами счетчика, сдвигающий регистр 4 с входами 5 и 6 управления Сдвиг вправо и Сдвиг влево, входы которого соединены с пинами 7 кода управления, а выходы подключены к второй группе входов дешифратора, первый и второй элементы ЗАПРЕТ, элемент И, элемент задер ки и первый триггер, выход которого соединен со входом элемента I3 задержки, R -вход соединен с входом управления регистра Сдвиг вправо, входом установки счетчика в нуль и выходом элемента 14 ЗАПРЕТ, запреща щий вход которого соединен с входной шиной, а управляющий - с выходом элемента задержки и входом второго элемента ЗАПРЕТ, выход которого соединен с S -входом первого триггера, а первый управлякиций вход с выходом дешифратора 3 и BTOprtiW входом элемента 10 И, элемент 8 И-Н и второй триггер 12, выход которого соединен с входом 5 управления реги стра Сдвиг вправо и выходной шиной 15, R -вход подключен к выходу элемента 10 И, а 3 -вход - к выходу элемента ЗАПРЕТ, второй ynpaieляющий вход которого соединен с выходом элемента 8 И-НЕ,перши вход которого соединен с выходом младиего разряда регистра 4, а второй с выходной шиной 15. Максимальное значение коэффициента деления делителя определяется емкостью счетчика 1 и сдвигающего регистра 4, причем регистр должен иметь на одну ячейку памяти больше, чем количество разрядов счетчика 1. Входшде кодовые шины регистра 4 подключаются к входам ячеек памяти с первой по , а ВЫХОДНЬБ кодовые Ш1шы соединены с выходами ячеек памяти с первой по (п+1)-ую, причем выходная кодовая шина первой ячейки памяти (выход младшего разряда) подключена к одному входу элемента 8 И-НЕ,а остальные - к второй группе входов дешифратора 3. Устройство работает следующим образом. В исходном положении, которое устанавл1шается перед -каждым циклом деления на заданный коэффициент, счетчик I и триггеры 11 и 12 установлены Б нулевое состояние. На запрещающий вход элемента 9 ЗАПРЕТ и на один вход элемента 10 И поступают сигналы нулевого уровня, В результате этого элемент 9 ЗАПРЕТ оказывается подготовленным к приему сигналов, поступающих наего управляющие входы, а элемент 10 И закрыт. Код управления коэффициентом деления К записан в ячейке памяти с первого по п-ук, в результате чего на входные разрядные щшсы управления дешифратора 3 поступает код управлсння, сдвинутый на один разряд влево (в сторону| младших разрядов), т.е код числа 0,5 К при четном и К и 0,5 (К-1) - при нечетном К, При четном коэффициенте деления в младшем разряде регистра 4 записан нуль, Сигнал нулевого уровня с выхода этого разряда поступает на один вход элемента 8 К-НЕ, в результате чего на выходе этого элемента при делении на четный коэффициент постоянно присутствует сигнал единичг ного уровня. Этот сигнал поступает на один управляющий вход элемента 9 ЗАПРЕТ, При делении на четный коэффициент устройство работает следующим образом () для обозначения сигналов, возникающих па выходах отдельных элементов и узлов делителя при его работе, использованы буквы U , цифровые индексы которых (i) соответствуют номерам этих элементов и узлов, пргшеденных на схеме делителя (рис. U. С приходом 0,5 К-ого входного импульса на выходе дешифратора 3 появляется сигнал единичного уровня, который через элемент ЗАПРЕТ поступает на ед1шичные входы триггеров 11

и 12 и Переводит Е тояние.

Сигнал един№П1ого уровня с выхода триггера 12 поступает па выходную шину 15 и на вход 5 управления Сдвиг вправо регистр 4 Происходит сдвиг кода,: зап.15санного в регистре, из ячеек памяти с первой по п

ую в ячейки со второй по ()-ую ; в результате чего на входные шш1Ы управления дешифратора 3 поступает полный код управления и сигнал на его выходе становится равным нулЮг.

Сигнал единкчис го уровня с выхода триггера I1 поступает через элемент 13 зэ деряа«)- на sanpemasoiujai вход эле-мскта 9 ЗАЛРЕТ .и па одии вход элемента Ш И, 2)лемент 3 ЗАПРЕТ при этом зап11рается,, а элексн 10 И - открывается с,

BaAepatfia переклочепня состою: :;.- элемептоЕ 9 ЗАПРЕТ и 10 Н относительно момента переключения тригтера i i нео6ход№1а для того, чтобы исключить презщевремелное поступление cui-нала с выхода дешифратора 3 .ерез элемент 10 И па зхоц устагтевки тглп -гера 32 в нулевое состоянне, Поэ.ому параметры элемента задерзжи Т, выбираются такш- oopasoi-ij чтобы время задержки было несколько большим, чем длительность п:;;реходиых процессов в последоБательЕО сра батываюцзк регистре 4; деп№1фратире 3 и элементе 10 li,

С пpi. 1С-ГО зходисго 11л;пу,гп:. са на выходе декалфуа-тсра 3 ПОКЕЛЯ-етсл сигнал ед;-пгк;ного уровня,- который через элеМЗНр 50 И лосгупает на R -вход триггера 12 н на управля юций вход элемеггта 14 ЗАПРЕТ Триггер 12 перехо,-гит и кулезсе состо;:кне. в результате чего закапчивается вьгходкой импу.цьс и сьнмается сягкал с,входа 5 управле:;и;1 рег истра 4,

В момент окончания К-то входного импульса на ЕЪГКОДС злемеита 14 ЗАПРЕТ появляется сигнал едш-нгчного уровня, KOTOpbvfi поступает на вход б управлезигя Сдвиг плево periscTpa 4j на вход установки в куль счетчика 1 и на нулевой вход триг:гера I I ,. Про-исходит сдвш содсрлц-шого рехистра 4 на один разред влево, а счетчик н триггер 1 i устакавливаттся в нуле-вое состояние

tia этом заканчкзгются никл р-або-ы делителя при делепнн на четный оэффициент.

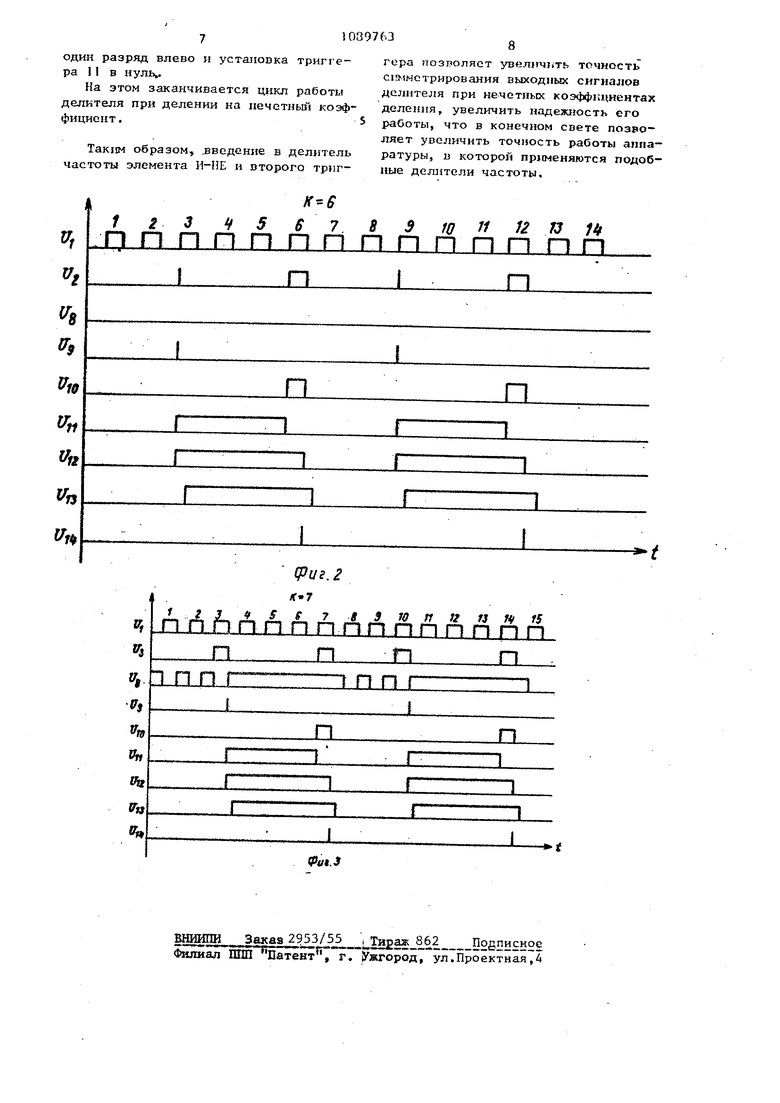

При нечетном коэффициенте деления 3 младшем разряде регистра 4 записана Щ.-шица, Сигнал единичного уровня с вьскода этого разряда поступает на один вход элемента 8 И-НЕ, На другой вход этого элемента поступают входные импульсы поэтому сигнал единичного уровня на выходе элемента 8 И-НЕ будет появляться только в пауэах между входными импульсами.

При делении на нечетный коэффициент устройство работает следующим образом (фиг. 3, ) .

С приходом 0,5 {К-1)о входного импульса на выходе депшфратора 3 пояллется сигнал единичного уровня, которьв поступает на управляющий вход элемента 9 ЗАПРЕТ. Элемент 9 ЗАПРЕТ открывается после окончания 0,5 ll-l I -го входного импульса и пропускает в этот момент сигнал с выхода дешифратора 3 на S -входы триггеров 1i и 2,

Триггер 12 переходит в ед1шичное состояние, в результате чего на ыине 15 появляется выходной импульс и происходит сдвиг содержимого регистра 4 на один разряд вправо. В младu.ieM разряде регистра при этом оказьгаается записанным нуль, а на вход.u-a разрядные шиз.ы управления дешифратора 3 поступает полньш код управления. При этом на выходе элемента 8 И--НЕ появляется сигнал един:1теного уровня, и сигнал на выходе дешифратора 3 становится равным н улта,

После перехода триггера 11 в единичное состояние через время Тj на выходе элемента 13 задержки; появляется сигнал едшигчного уровня, которым закрьшается элемент 9 ЗАПРЕТ и открывается эле1-1еят 0 И,

С ПР1ЕХОДОМ входного импульса на выходе дешифратора 2 появляется сигнал единичного уровня, которьп через элемент 0 И поступает на R вход триггера 12 и на управляющий иход элемента 14 ЗАПРЕТ. Триггер 12 переходит в нулевое состояние, в результате чего заканчивается выходной импульс и снимается сигнал с входа 5 управления регистра 4.

Вмомент окончания К-го входного га-гпульса на выходе элемента 14 ЗАПРЕТ появляется сигнал единичного ypoBKHs по которому происходит установ.ка счетчика 1 в нулевое состоя™ зпш, сдвлг содерлипЮго регистра на

один разряд влево и установка триггера 1 1 в Hyniv

На этом заканчивается ЦИРСЛ работы делителя при делении на нечетньв коэффициент.

Таким образом, .введение в делитель частоты элемента И-ПЕ и второго триггера позволяет увелич 1ть точность С1ячмстрирования выходных сигналов делителя при нечетньсх коэффициентах деления, увеличить надежность его работы, что в конечном свете позволяет увеличить точность работы аппаратуры, в KOTopoii применяются подобные делители частоты.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-04-30—Публикация

1982-09-20—Подача