переключаквцие четвертого и пятого ключей, являются шиной нулевого потенциала устройства, контакты первый и второй переключающие перво«о, переключающий второго, размыкающие и замыкающие четвертого и пятого, размыкакхций и замыкающий. третьего ключей являются выходами блока с первого по седьмой соответственно.

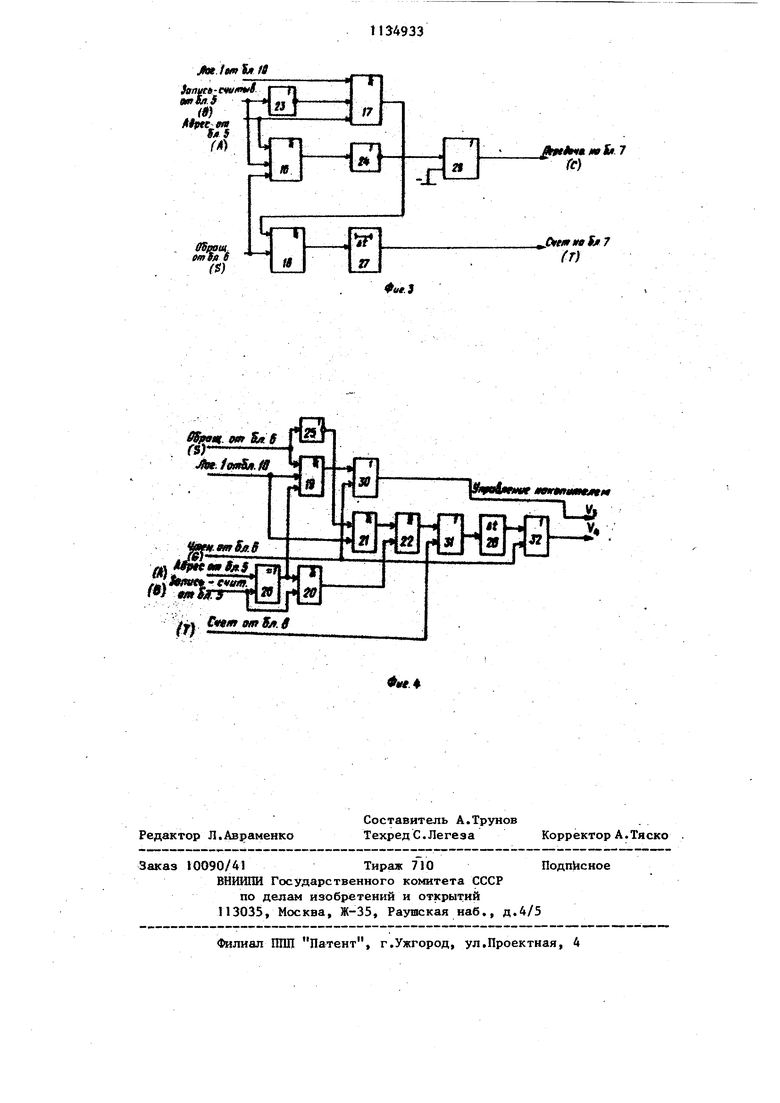

3. Устройство по п.1, о тличающееся тем, что фop шpoвa .тель команд содержит второй и третий инверторы, первый элемент ИЛИ, пер1аый элемент задержки, первый, второй и третий элементы И, первый, второй и третий входы первого элемента И соответственно объединены с первыми :входами второго, третьего элементов И и с входов второго инвертора и ярляются с первого пО третий входами формирователя соответственно, выход второго инвертора соединен с вторым входом второго элемента И, третий вход которого является четвертым входом формирователя, выход подключен к второму входу третьего элемента И, выход .которого через первый элемент задержки соединен с вторым выходом формирователя, выход первого элемента И через третий инвертор подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с шиной.нулевого потенциала устройства, а выход является первым выходом формирователя.

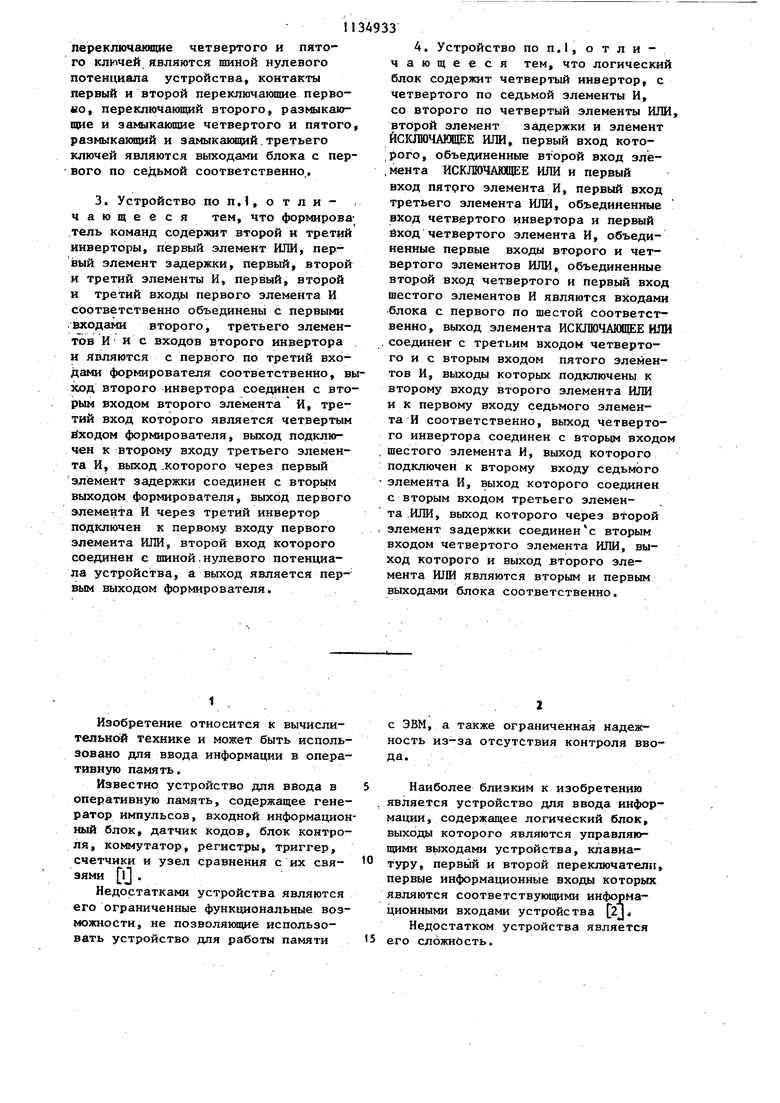

4. Устройство по п.1, о т л и чающееся тем, что логический блок содержит четвертый инвертор, с четвертого по седьмой элементы И, со второго по четвертый элементы ИЛИ, втЬрой элемент задержки и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого, объединенные второй вход злемента ИСКШЧАЮЩЕЕ ИЛИ и первый вход пятрго элемента И, первый вход третьего элемента ИЛИ, объединенные вход четвертого инвертора и первый йход четвертого элемента И, объединенные первые входы второго и четвертого элементов ИЛИ, объединенные второй вход четвертого и первый вход шестого элементов И являются входами блока с первого по шестой соответственно, выход элемента ИСКЛЮЧАКЩЕ ИШ

соединен- с третьим входом четвертого и с вторым входом пятого элементов И, выходы которых подключены к второму входу второго элемента ИЛИ и к первому входу седьмого элемента И соответственно, выход четвертого инвертора соединен с вторым входом шестого элемента И, выход которого подключен к второму входу седьмого

элемента И, выход которого соединен с вторым входом третьего элемента .ИЛИ, выход которого через второй

элемент задержки соединен с вторым входом четвертого элемента ИЛИ, выход которого и выход второго элемента ИЛИ являются вторым и первым выходами блока соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вывода информации | 1983 |

|

SU1137475A1 |

| Устройство для передачи информации | 1981 |

|

SU1012311A1 |

| Устройство для графического отображения синтезируемой устной речи | 1986 |

|

SU1411802A1 |

| Устройство для измерения временных параметров программ | 1982 |

|

SU1136109A1 |

| Устройство для воспроизведения видеосигнала | 1987 |

|

SU1555918A1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1989 |

|

RU2028731C1 |

| Адаптивное устройство для обучения языкам | 1987 |

|

SU1441445A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Измерительная система с автоматическим контролем аналого-цифрового преобразования и блок задания нечувствительности | 1991 |

|

SU1837261A1 |

| Микропрограммное устройство формирования тестовой последовательности | 1984 |

|

SU1267425A1 |

1. УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ, содержащее логический блок, выходы которого являются управляющими выходами устройства, клавиатуру первый и второй переключатели, первые информационные входы которых являются соответствующими информационными входами устройства, отличающееся тем, что, с целью упрощения устройства, в него введены, первый инвертор, третий переключатель, формирователь импульсов, счетчик-регистр, формирователь команд и блок ключей, первый выход которого соединен с перьым управляющим входом третьего переключателя, второй выход - с вторым управляющим входом третьего пе еключатепя и с первыми входами логического блока, и формирователя команд, третий выход - с вторыми входами логического блока и формирователя команд, четвертый и пятый выходы - с соответствующими входами формирователя импульсов, и седьмой выходы - с соответствующими Управляющими входами первого и второго пере.ключателей, щина нулевого потенциала блока ключей является шиной нулевого потенциала устройства, вторые информационные входы первого и второго переключателей подключены соответст выходу третьевенно к первому и к .выходу го переключателя выход клавиасчетчика-регистра, информационным туры соединен с переключателя, входом третьего второй выход которого подключен к информационному входу счетчика-регистра, управляющий вход которого соединен с первым выходом формирователя команд, счетный вход счетчикарегистра соединен с третьим входом логического блока и вторым выходом i формирователя команд, первый выход формирователя импульсов подключен (Л к третьему входу формирователя команд и к четвертому входу логичесС кого блока, пятый вход кот-, рого соединен с вторым выходом формирователя импульсов, вход первого инвертора соединен с шиной нулевого потенциала, выход - с четвертым входом формирователя команд и с шестым вхо00 4 дом логического блока, выходы первого и второго переключателей являют:о ся выходами данных и адреса устройстDO 00 ва соответственно, первые информационные входы которых являются соответствукяцнми входами устройства. 2. Устройство по П.1, о т л н ч а ю щ ее с я тем, что блок ключей содержит с первого по пятый ключи, контакты первый замыкающий и второй размикакшщй первого, -размыкающие второго и третьего ключей являются шиной положительного потенциала блока, контакты первый размыкающий, второй замыкающий первого, за(« 1кающий второго.

i ,

Изобретение относится к вычислительной технике и может быть использовано для ввода информации в оперативную память.

Известно устройство для ввода в оперативную память, содержащее генератор импульсов, входной информационш 1й блок, датчик кодов, блок контроля, коммутатор, регистры, триггер, счетчики и узел сравнения с их связями .

Недостатками устройства являются его ограниченные функциональные возможности, не позволякяцие использовать устройство для работы памяти

с ЭВМ, а также ограниченная надежность из-за отсутствия контроля ввода.

Наиболее близким к изобретению является устройство дпя ввода информации , содержащее логический блок, выходы которого являются управляющими выходами устройства, клавиатуру, первый и второй переключатели, первые информационные которых являются соответствующими информационными входами устройства Pj Недостатком устройства является

его сложность. Цель изобретения - упрощение уст ройства. Указанная цель достигается тем, что в устройство для ввода информации, содержащее логический блок, выходы которого являются соответствующими управля мцими выходами устройства, клавиатуру, первый и второй переключатели, первые информационные входы которых являются COOT ветствугацими информационными входа ми устройства, дополнительно введены первый инвертор, третий переклю чатель, формирователь импульсов, счетчик-регистр, формирователь ко.манд и блок ключей, первый выход ко рого соединен с первым управляющим входом третьего переключателя, вто,рой выход - с вторым .управляющие входом третьего переключателя, и с первыми входами логического блока и формирователя команд, третий выход - с вторыми входами , логического блока и формирователя команд, четвертый и пятый выходы - с соответствующими входами фориирователя импульсов, шестой и седьмой выходыс соответствующими управлякицими входами первого и второго переключателей, шина нулевого потенциала блока ключей является шиной нулевого потенциала устройства, вторые информационные входе 1 первого и второго переключателей подключены соот ветственно к первому выходу третьег пере1слючателя и к выходу счетчикарегистра, выход клавиатуры соединен с информационным входом третьего переключателя, второй выход которого подключен к информационному вход счетчика-регистра, управляюцщй вход которого соединен с первым выходом формирователя команд, счетный вход счетчика-регистра соединёнс третьи входом логического блока и вторым выходом формирователя команд, первый выход формирователя импульсов подключен к третьему входу формиров теля команд и к четвертому входу логического блока, пятый вход которого соединен с вторым выходом форгфирователя импульсов, вход первого инвертора соединен с шиной нулевого по тенциала ,выход - четвертым входом фор «шровдтеля команд и с шестым входом noiTi4ecKoro блока, выходы первого И второго переключателей являются выходами данных и адреса устройства соответственно, первые инфop aциoнные входы которых являются соответст-. вующими входами устройства. Блок ключей содержит с первого по пятый ключи, контакты первый замыкающий и второй размыкающий первого, размыканядие второго и третьего ключей являются шиной положительного потенциала блока, контакты первый размыкающий, второй замыкающий первого, замыкающий второго, переключающие четвертого и пятого ключей являются шиной нулевого потенциала устройства, контакты первый и второй переключающие первого, переключающий второго, размы:.-а(яцие и за1« 1каю- щие четвертого и пятого, размыкающий и замыканнций третьего ключей являются выходами блока с первого по седьмой соответственно. Формирователь команд содержит второй и третий инверторы, элемент ИЛИ, первый элемент задержки, первый, второй и третий элементы И, первый, второй и третий входы первого элемента И соответственно объединены с первыми входами второго, третьего элементов И и с входом второго инвертора и являются с первого по третий входами формирователя соответственно, выход второго инвертора соединен с вторым входом второго элемента И, третий вход которого является четвертым входом формирователя, выход подключен ко второму входу третьего элемента И, выход которого через первый элемент задержки соединен с вторым выходом формирователя, выход первого элемента И через третий инвертор подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с шиной нулевого потенциала устройства, а выход является первым выходом формирователя. Логический блок содержит четвертый инвертор, с четвертого по седьмой элементы И, со второго по чет вертый элементы ИЛИ, второй элемент задержки и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ первый вход которого, объединенные второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и первый вход пятого эле-мента И, первый вход третьего элемента ИЛИ, объединенные вход четвертого инвертора и первый вход четвертого элемента И, объединенные:nepi вые входы второго и четвертого элементов ИЛИ объединенные второй вход четвертого и первый вход шестого элементов И являются входами блока $1 с первого по шестой соответственно, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соеди ней с третьим входом четвертого и со вторым входом пятого элементов И, дыходы которых подключены к второму входу элемента ИЛИ и к первому входу седьмого элемента И соответственно, выход четвертого инвертора соединен со вторым входом шесто го элемента И, выход которого подклк чен к второму входу седьмого элемента И, выход которого соединен со вторым входом третьего элемента ИЛИ, выход которого через второй элемент задержки соединен с вторым входом четвертого элемента ИЛИ, . выход которого и выход второго элемента ИЛИ являются вторым и первым выходами блока соответственно. На фиг.1 изображена схема устройства; на фиг, 2 - схема блока ключей; на фиг. 3 - схема формирователя команд; .на фиг. А - схема логи ческого блока. На схемах с первого по третий переключатели 1-3, клавиатура 4, блок .ключей 5, формирователь импульсов 6, счетчик-регистр 7, форми рователь команд 8, логический блок инвертор первый 10, ключи с первого по пятый П-15, логические переменные, сопоставленные сигналам Адрес Запись-считывание,Обращение, Счет Чтение, Передача , Счет, перво му и второму управления накопителем jA,B, S,G,C,T,V, ,V с первого по третий элементы И 16-18, первый эле.мент задержки 19, второй и третий инверторы 20 и 21, с первого по чет вертый элементы ИЛИ 22-25, четверты инвертор 26, второй элемент задержки 27, с четвертого по седьмой элементы И 28-31, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 32. Устройство работает следующим об разом. Возможны три режима работы: загру ка информации в накопитель,считывание информации в порядке возрастаний адресор, считывание по произвольному адресу Загрузка информации в накопитель. На блоке 5 (фиг.2) оператор устанавливает ключи 1 1,1 2 и 1 3 в исходные по ложения, при этом на выходах блока появляются сигналы, согласно табл, 1 . Счетчик-регистр 7 может-быть реализован, например, на микросхеме серии КГ55ИЕ7. 3 Сигналы Адрес и Данные производят установку переключателя 3, который подключает клавиатуру к входам счетчика-регистра 7. Сигнал Адрес поступает на формирователь 8 и блок 9. Запись-считывание также поступает на блок И 9 и на формирователь 8. Сигнал Загрузка устанавливает переключатели I и 2 в положение, при котором данные и адрес в накопитель вводятся от устройства (с его клавиатуры). Нулевой уровень сигналов Чтение и Обращение обеспечивает Лог.О на выходах формирователя 6. Затем на клавиатуре 4 набирается адрес ячейки накопителя, в которую должна быть произведена запись. По нажатию и отпусканию ключа 15 блока 5 обеспечивается кратковременная подача Лог.1 на вход формирователя 6, который формирует сигнал Обращение, поступающий затем на блок 9 и формирователь 8. При этом формирователь 8, реализующий на своем первом выходе сигнал С, описываемый логической функцией С 3 (А Б S) переключит уровень этого сигнала с Лог.1 на Лог.О, так как А В 1, а S изменяется от О к 1, создавая отрицательный фронт сигнала на входе счетчика-регистра 7. Сигнал на выходе Т, форми- . рователя 8 описываемый , логической функцией Т А В S будет равен О так как А В S 1). Таким образом, при проведении описанных операций адрес, набранный на клавиатуре А, поступит через переключатель 3 на входы счетчика-регистра 7, наличие сигнала Т 0 иотрицательного фронта сигнала С (изменение от } к о) создает условия для занесения адреса в счетчик-регистр 7, с которого он через переключатель 2 поступит на выхода устройства, соединенные с адресньчми входами накопителя. Затем производится переключение ключа 11 блока 5 в положение Данные. При этом на выходах блока 5 появятся сигналы, со гласно табл. 2. На клавиатуре 4 набирается код данных, который через переключатель 3, установившийся при изменении уровней сигналов Адрес и Данные в другое положение и через переклю- чатель I поступит на выходы устройства, соединенные с входами данных накопителя. Затем производится нажатие и отп кание ключа 15 блока 5, который сфо мирует на выходе формирователя 6 положительный импульс сигнала Обра щение , поступающий на блок 9 и фор мирователь 8. Описанным способом бу дут сформированы сигналы С и Т. При чем, сигнал Т с выхода формировател постулит на блок 9, на входах которого в момент нажатия ключа 15 появятся сигналы, представленные в табл, 3. Блок 9 по выходам управления накопителем реализует следукицие логи.ческие функции: Vi АВ + V| ABS + . При создавшейся на входах блока совокупности сигналов Va If V, 0. Таким образом, при осуществлени Перечисленных операций управления На входах счетчика-регистра 7 сиг;напы Т О и отрицательный фронт сигнала С (изменение от I к О), на входах накопителя V 1, V О, При этом счетчик-регистр 7 через пе реключатель 2 передает сигнал адреса с клавиатуры 4 на адресные входы накопителя, код данных через перекл чатель I поступает на вход данных накопителя, а совокупность управляю щих сигналов V-j 1 , Vi f О обеспечивает запись данных по установленно му адресу в накопитель. Считывание информации в йорядке возрастания адресов. Предположим,из накопителя необходимо считать данные, записанные в порядке возрастания адресов с шагом ., до адреса Ау(Аjj. А; с адреса А коды адресов). Для этого двоичные необходимо установить на клавиатуре 4 адрес (А - 1) и ввести его в счетчик-регистр 7 описанным образом. Затем устанавливается ключ 12 блока 5 в положение Считывание. При этом в табл. 1 изменится значе ние сигнала Запись-считывание, В О (фиг.2). Состояние переключа телей 1 и 2 не изменится и цепь передачи кодов адреса и данных через них сохранится. Затем производится нажатие ключа 15 блока 5, по которому формиров тель 6 сформирует положительный импульс сигнала Обращение. В момент нажатия ключа 15 на входлх формирователя 8 имеются сигналы А 1, В О, S I. Формирователь 8 формирует сигналы С I и Т I, что соответствует его работе в режиме счетчика, который при каждом нажатии ключа 15 будет прибавлять к своему содержимому I и выставлять это число на своих выходах, с которых оно поступит через переключатель 2 на адресные входы накопителя. По нажатию ключа 15 на входе блока 9 появляются сигналы А S Т 1, В G О, что приводит к появлению на его выходах сигналов V.- 1 , Vi I . Это соответст-,Г вует рехсиму считывания содержимого накопителя по заданному адресу. Поскольку в счетчик-регистр 7 был введен адрес () и по нажатию ключа 15 к нему добавилась 1, то . из накопителя будет считана информация по адресу . При последующих отпусканиях и нажатиях ключа 15 I аналогично производится считывание содержимого.накопителя по адресам (А;+ 1) (А-;+ 2) и т.д. Считывание информации по произвольному адресу. Для осуществления этого режима при считывании адреса А; необходимо ввести адрес j Счетчик-регистр 7, также, как это производится при загрузке информации в накопитель. Затем нужно включить ключ 14 иа блоке 5 (фиг.2). Сигнал Чтение уровнем ЛОг.О подается на входы формирователя 6, где он формируется и поступает на вход блока 9, при этом логическая переменная, сопоставленная этому сигналу, принимает значение I, G f. На выходах блока 9 появляются сигналы v I, осуществлянщие считывание информации из накопителя по адресу Аj. На фиг. 3 приведена возможная реализация формирователя 8 в соответствии с логическими функциями для его выходов. Введение элемента 19 обусловлено необходимостью обеспечения запаздывания сигнала Т по отношению к сигналу С для обеспечения нормальной работы счетчика-регистра 7, реаизуемого на ИС К155ИЕ7.

На фиг.A приведена возможная реализация блока 9 в соответствии с логическими функщ{ями для его выходов.

(А| + AB)S-«-G

+ Т + G

Обращение

Введеиие элемента задержки 27 обусловлено необходимостью запаздывания сигнала V/j Чтение-запись по отношению к сигналу VA выбор кристалла.

Т а б л и ц а 1

Т а б л и ц а 2

Т а б лица 3

113493312

n

- cvutntio:

жпмо

lt9lHlipWb

vWffMF Pff

9§Ч

Mftee вт

Фиг 2

Продолжение табл.3

ь5

9oSpau(.

.

HOMMIMtM

4мег/

Jtat tembtt

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для записи информации в оперативную память | 1974 |

|

SU482805A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для управления оперативным накопителей | 1972 |

|

SU463145A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-01-15—Публикация

1983-08-04—Подача