Ю

О5

li to сд

Изобретение относится к вычислиельной технике, а именно к устрой-, твам автоматического синтеза тестов ля контроля работоспособностги и диагностики неисправностей сложных цифровых объектов,

Целью изобретения является повыение коэффициента использования обоудования.

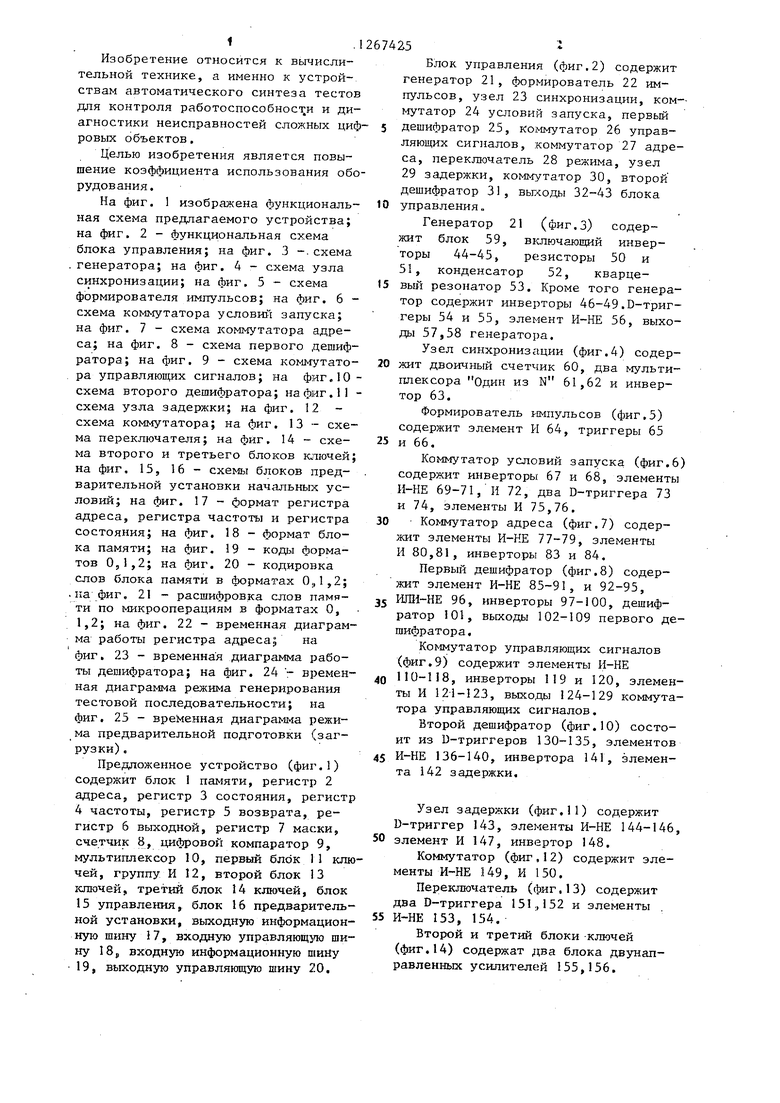

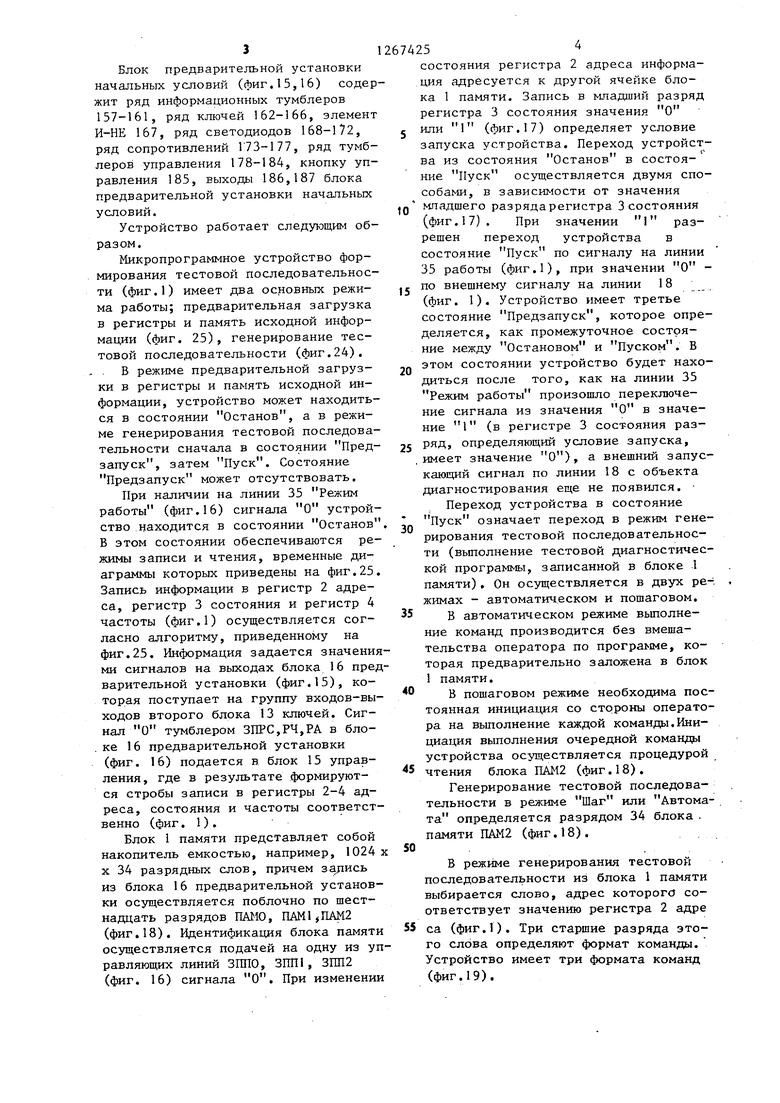

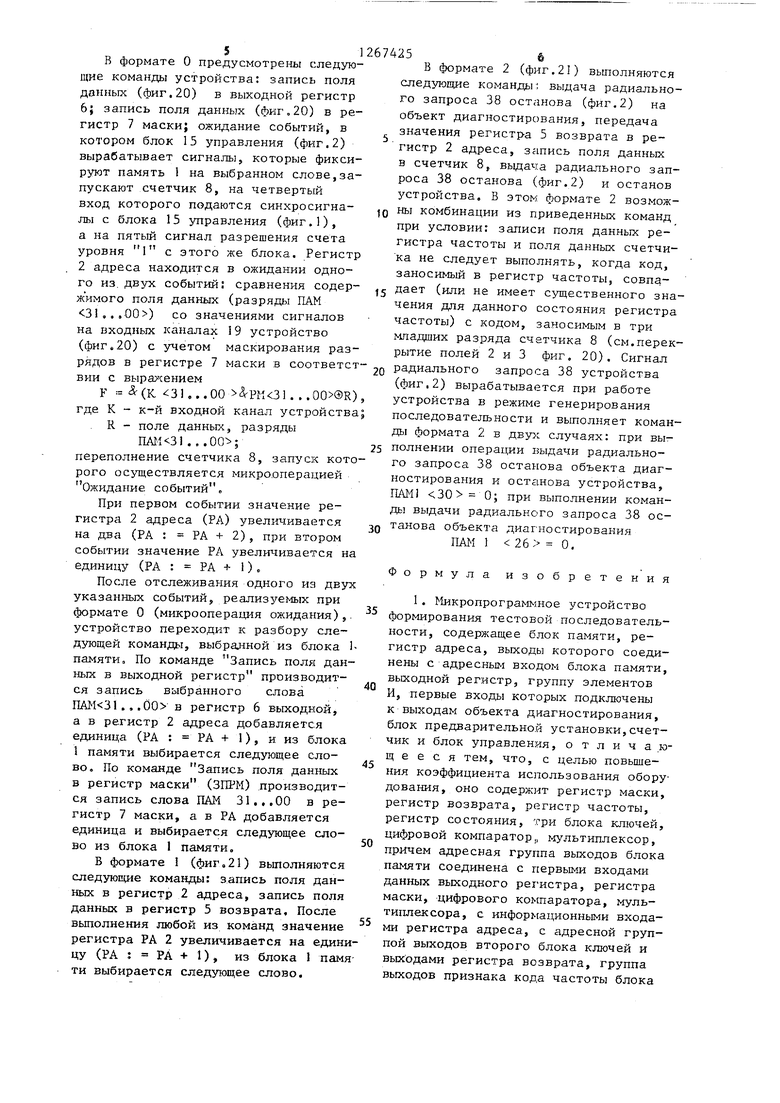

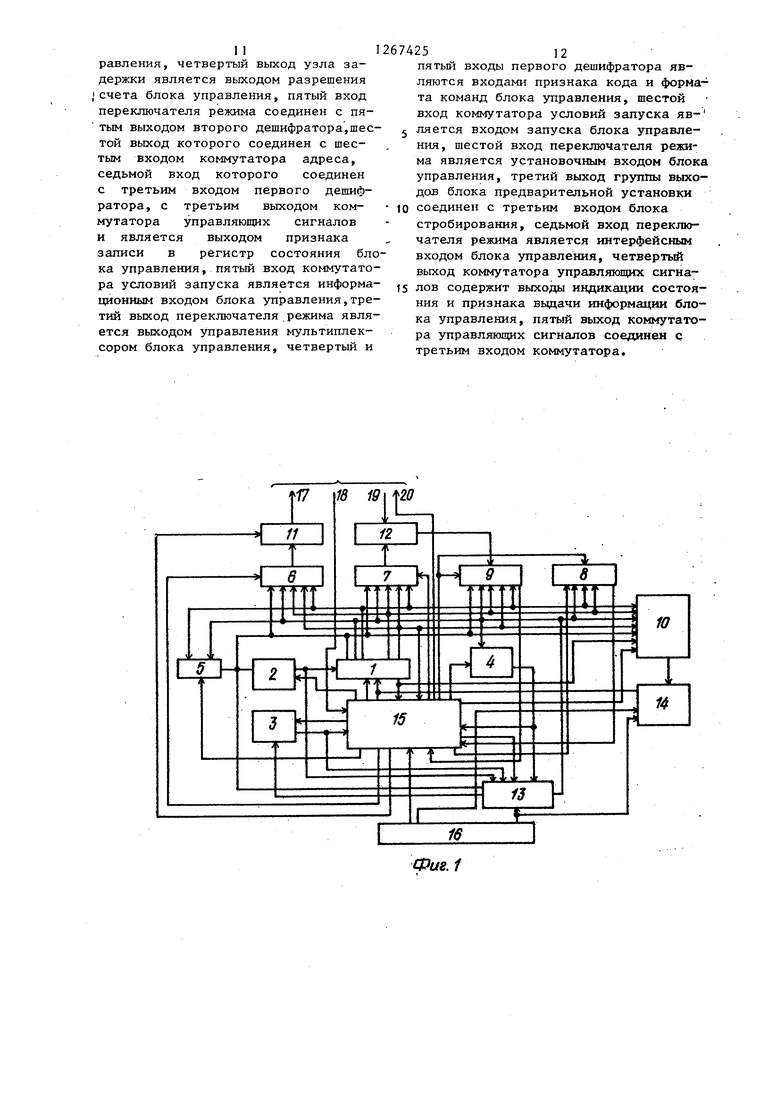

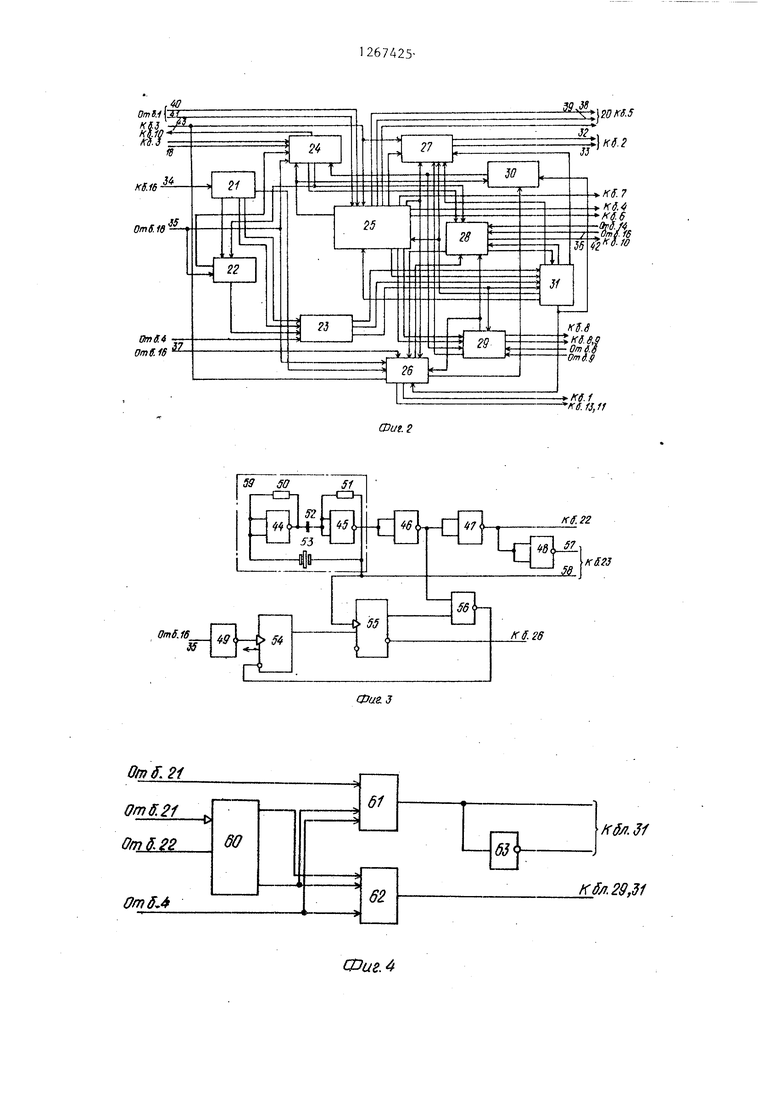

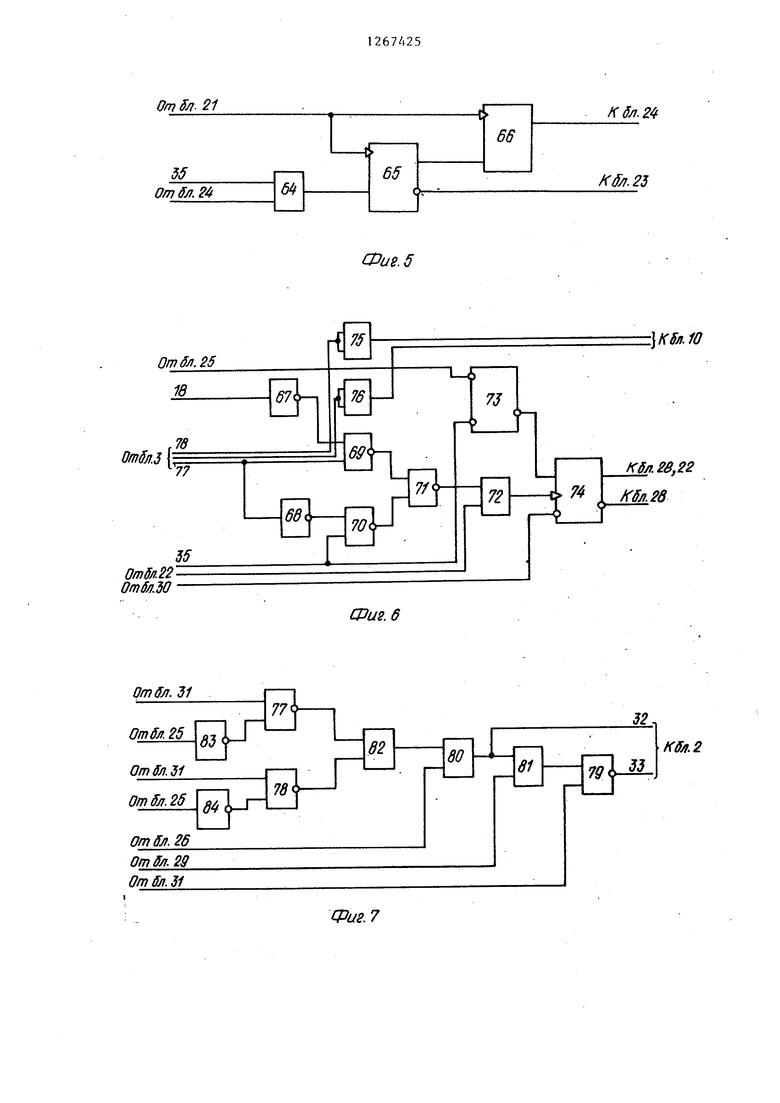

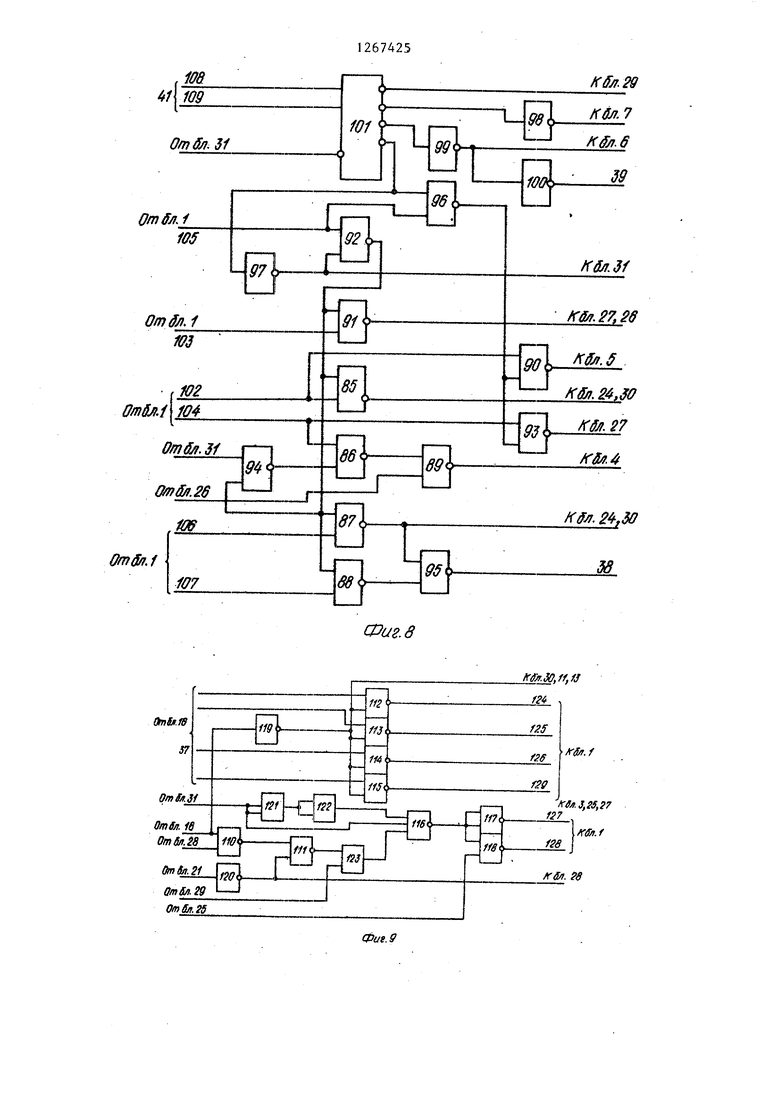

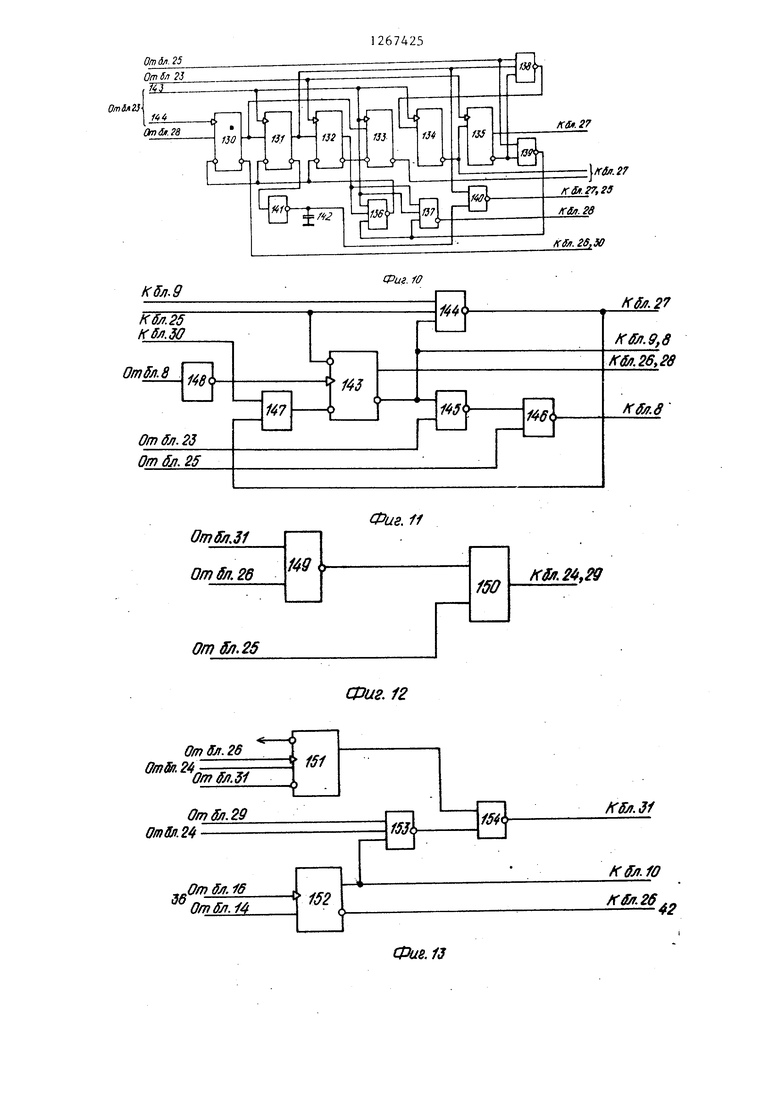

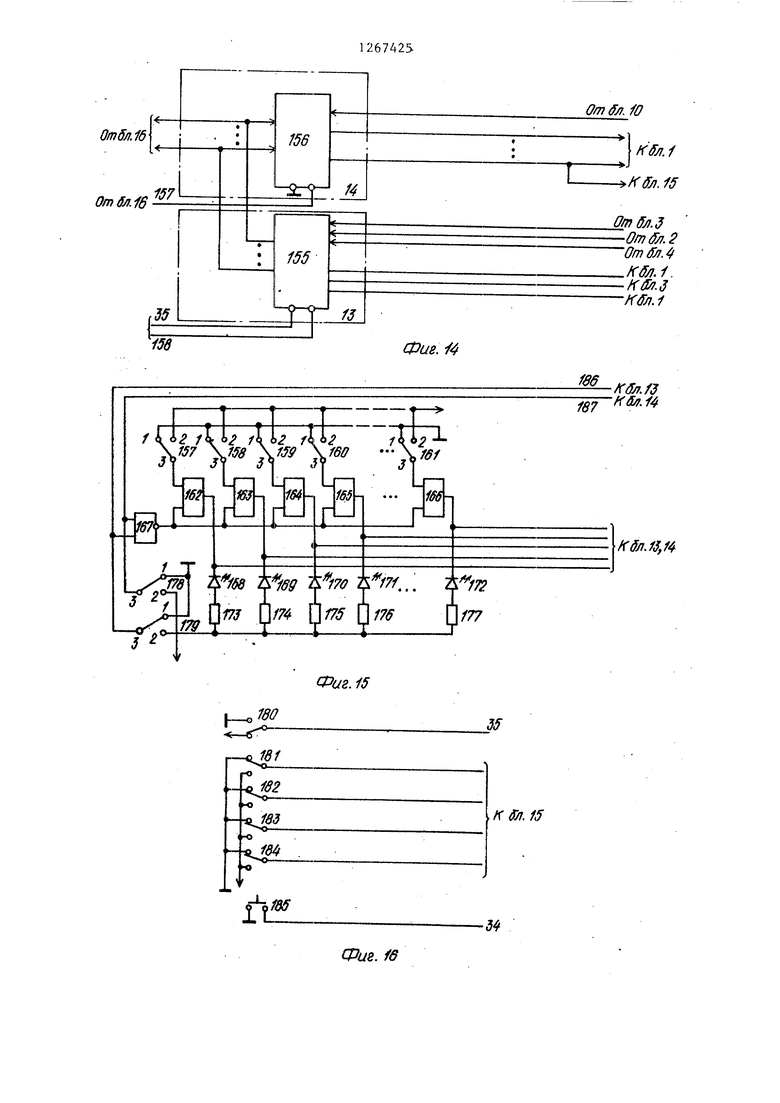

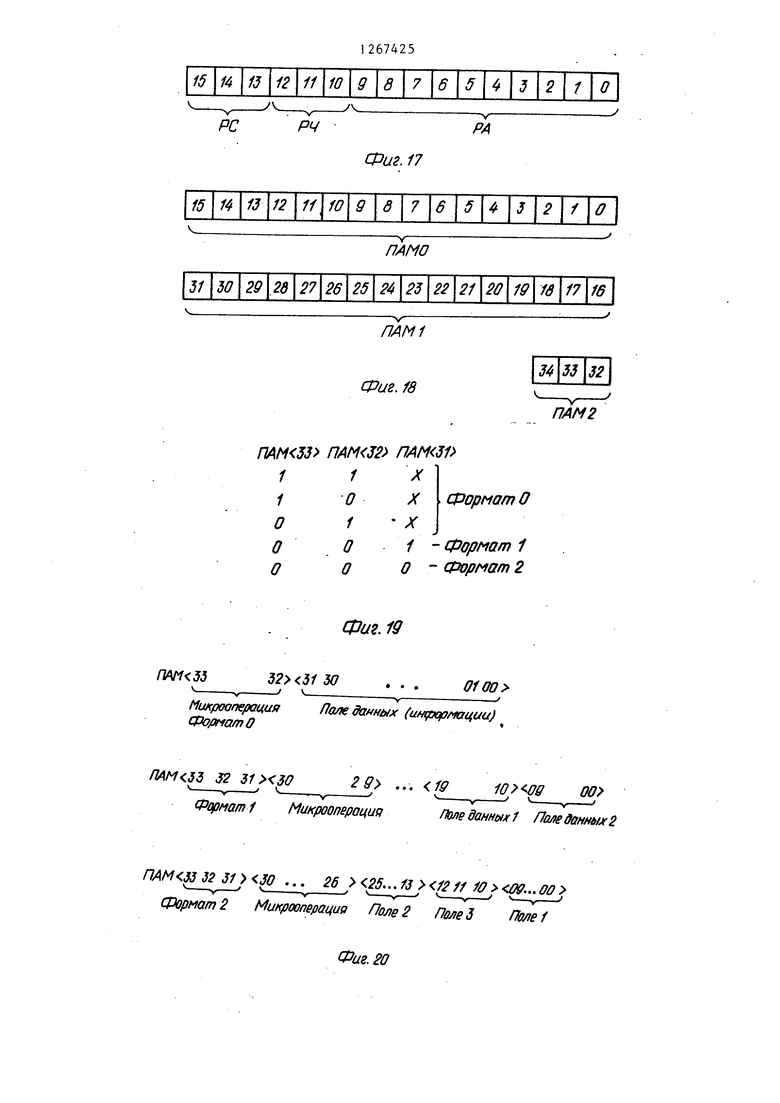

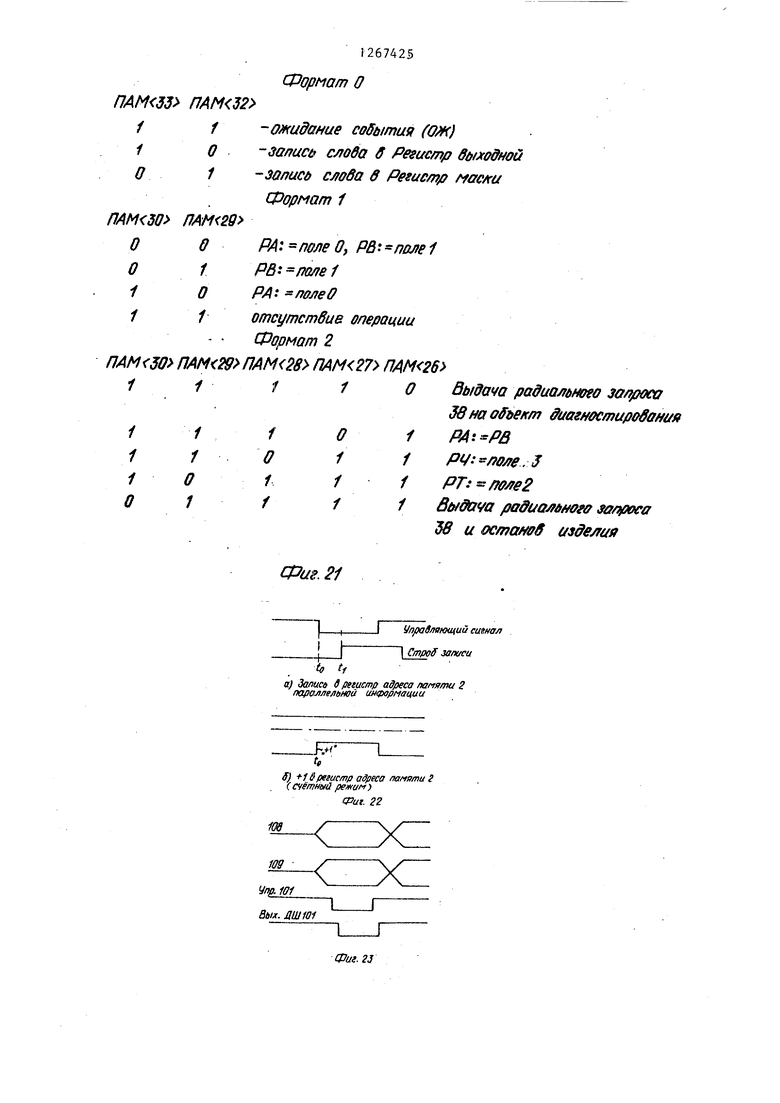

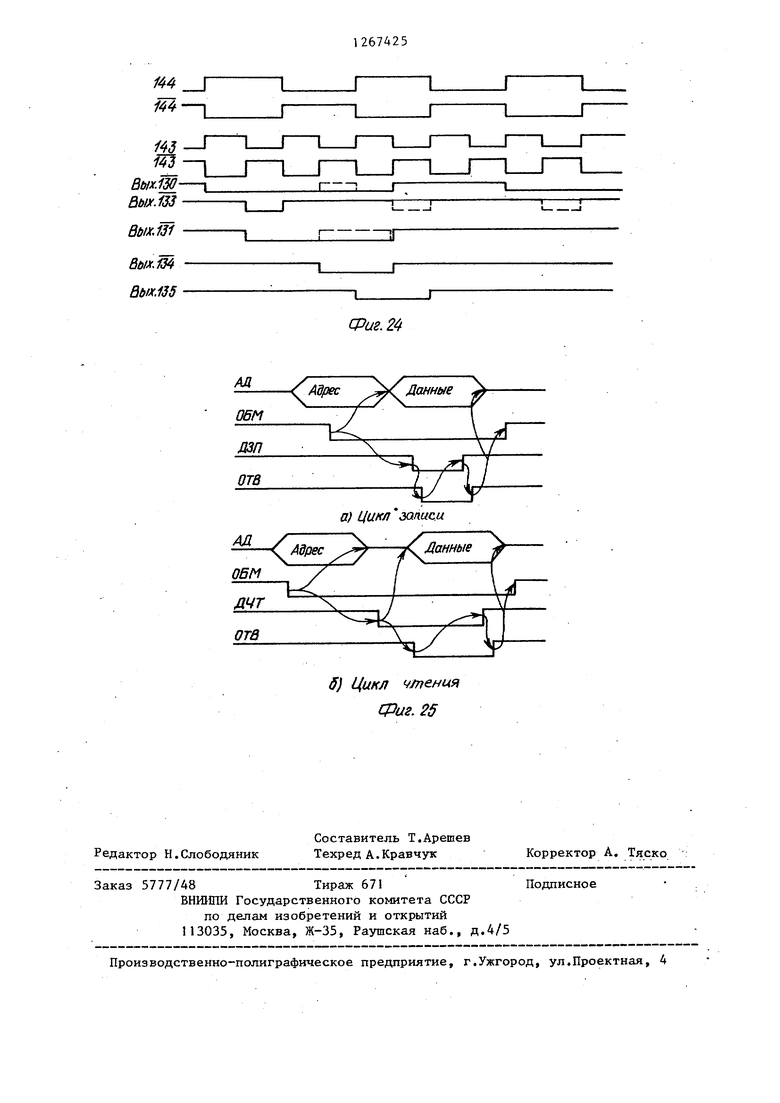

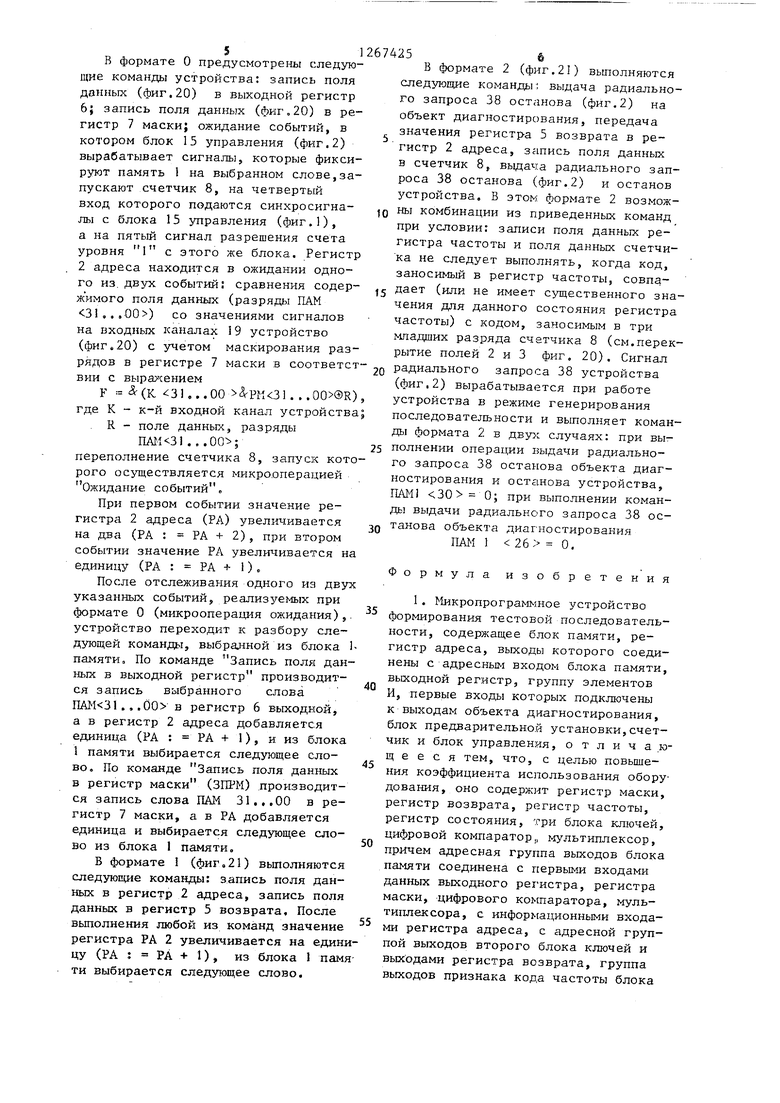

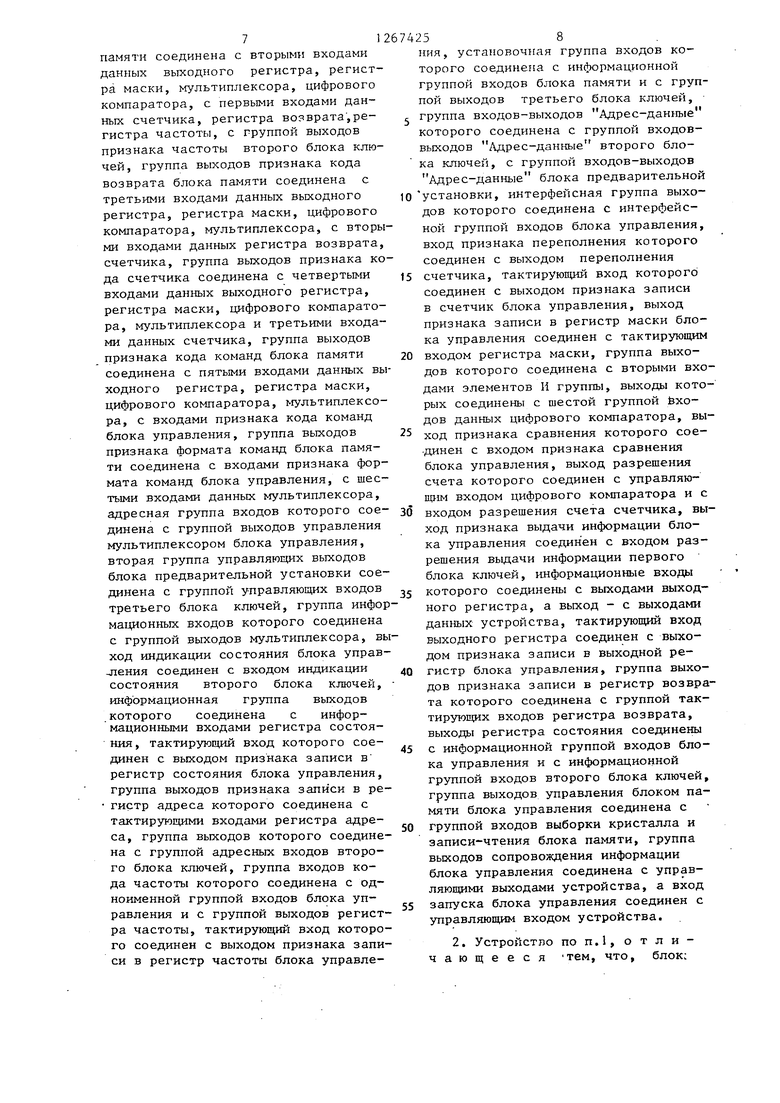

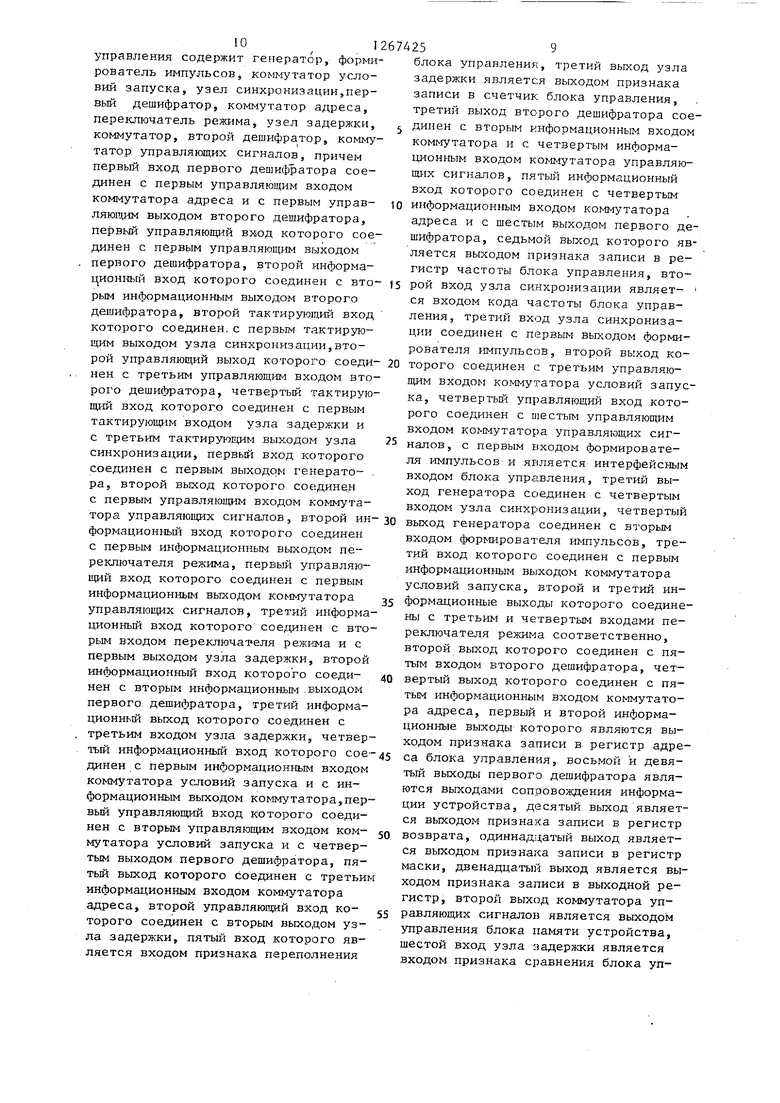

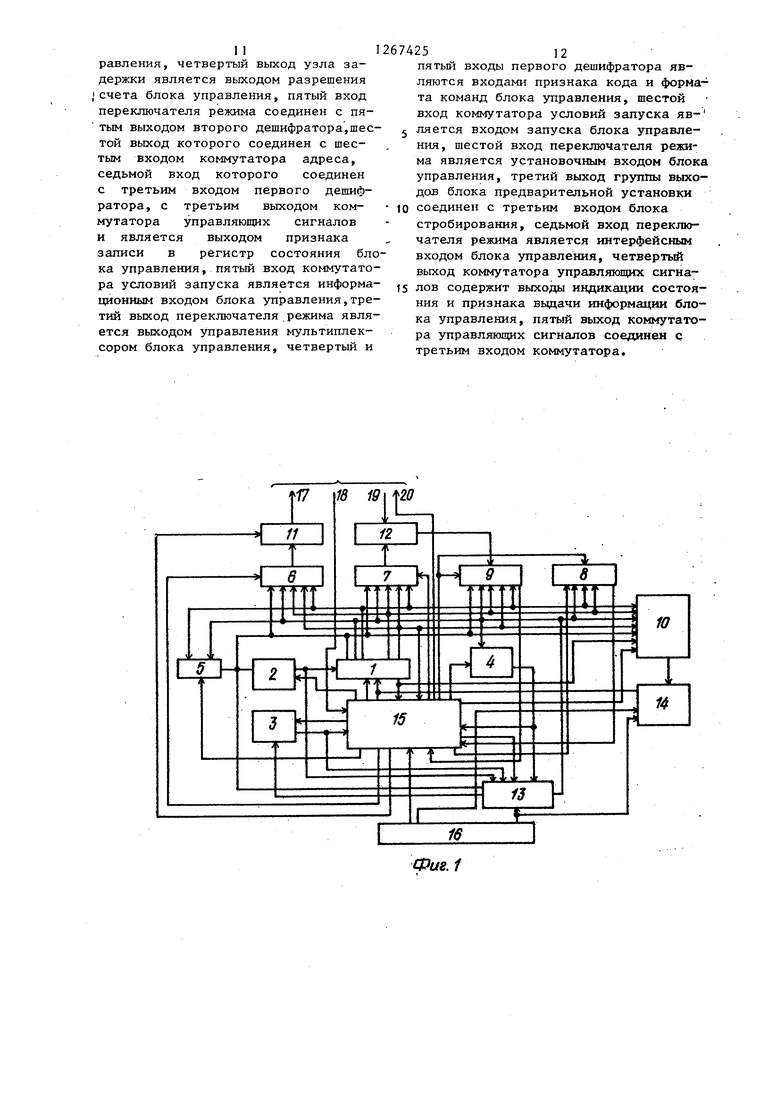

На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг. 2 - функциональная схема блока управления; на фиг. 3 -.схема генератора; на фиг. А - схема узла синхронизации; на фиг. 5 - схема формирователя импульсов; на фиг. 6 схема коммутатора условий запуска; на фиг. 7 - схема коммутатора адреса; на фиг. 8 - схема первого дешифратора ; на фиг. 9 - схема комкутатора управляющих сигналов; на фиг.10 схема второго дешифратора; на фиг.11 схема узла задержки; на фиг. 12 схема коммутатора; на фиг. 13 - схема переключателя; на фИг. 14 - схема второго и третьего блоков тстючей; на фиг. 15, 16 - схемы блоков пред- . варительной установки начальных условий; на фиг. 17 - формат регистра адреса, регистра частоты и регистра состояния; на фиг. 18 - формат блока памяти; на фиг. 19 - форматов 0,1,2; на фиг. 20 - кодировка слов блока памяти в форматах О,, 1,2; на фиг.21- расшифровка слов памяти по микрооперациям в форматах О, 1,2; на фиг. 22 - временная диаграмма работы регистра адреса; на фиг. 23 - временная диаграмма работы дешифратора; на фиг. 24 - временная диаграмма режима генерирования тестовой последовательности; на фиг. 25 - временная диаграмма режима предварительной подготовки (загрузки) .

Предпоженное устройство (фиг.1) содержит блок 1 памяти, регистр 2 адреса, регистр 3 состояния, регистр 4 частоты, регистр 5 возврата, регистр 6 выходной, регистр 7 маски, счетчик 8, цифровой компаратор 9, мультиплексор 10, первый блок 11 ключей, группу И 12, второй блок 13 ключей, третий блок 14 ключей, блок 15 управления, блок 16 предварительной установки, выходную информационную шину 17, входную управляющею шину 18, входную информационную шийу 19, выходную управляющую шину 20,

Блок управления (фиг.2) содержит генератор 21, формирователь 22 импульсов, узел 23 синхронизации, ком-мутатор 24 условий запуска, первый

дешифратор 25, кохммутатор 26 управляющих сигналов, коммутатор 27 адреса, переключатель 28 режима, узел 29 задержки, коммутатор 30, второй дешифратор 31, вькоды 32-43 блока

управления,.

Генератор 21 (фиг.З) содержит блок 59, включаюш 1й инверторы 44-45, резисторы 50 и 5, конденсатор 52, кварцевьш резонатор 53. Кроме того генератор содержит инверторы 46-49.D-триггеры 54 и 55, элемент И-НЕ 56, выходы 57,58 генератора.

Узел синхронизации (фиг.4) содержит двоичный счетчик 60, два мультиплексора Один из N 61,62 и инвертор 63.

Формирователь смпульсов (фиг.5) содержит элемент И 64, триггеры 65

и 66.

Коммутатор условий запуска (фиг.6) содержит инверторы 67 и 68, элементы И-НЕ 69-71,и 72, два D-триггера 73 и 74, элементы И 75,76.

Коммутатор адреса (фиг.7) содержит элементы И-НЕ 77-79, элементы И 80,81, инверторы 83 и 84.

Первый дешифратор (фиг.8) содер- жит элемент И-НЕ 85-91, и 92-95,

ИПИ-НЕ 96, инверторы 97-100, дешифратор 101, вькоды 102-109 первого дешифратора.

Коммутатор управляющих сигналов (фиг.9) содержит элементы И-НЕ

110-118, инверторы 119 и 120, элементы И 12-1-123, выходы 124-129 коммутатора управляющих сигналов.

Второй дешифратор (фиг.10) состоит из D-триггеров 130-135, элементов

И-НЕ 136-140, инвертора 141, элемента 142 задержки.

Узел задержки (фиг.11) содержит D-триггер 143, элементы И-НЕ 144-146, элемент И 147, инвертор 148.

Коммутатор (фиг,12) содержит элементы И-НЕ 149, И 150.

Переключатель (фиг,13) содержит два D-триггера 151., 152 и элементы И-НЕ 153, 154.

Второй и третий блоки -ключей (фиг.14) содержат два блока двзгааправленных усилителей 155,156. 3 Блок предварительной установки начальных условий (фиг.15,16) содер жит ряд информационных тумблеров 157-161, ряд ключей 162-166, элемент И-НЕ 167, ряд светодиодов 168-172, ряд сопротивлений Г73-177, ряд тумблеров управления 178-184, кнопку управления 185, выходы 186,187 блока предварительной установки начальных условий. Устройство работает следующим образом. Микропрограммное устройство формирования тестовой последовательности (фиг.1) имеет два основных режима работы; предварительная загрузка в регистры и память исходной информации (фиг. 25), генерирование тестовой последовательности (фиг.24). . . В режиме предварительной загрузки в регистры и память исходной информации, устройство может находиться в состоянии Останов, а в режиме генерирования тестовой последовательности сначала в состоянии Предзапуск, затем Пуск. Состояние Предзапуск может отсутствовать. При наличии на линии 35 Режим работы (фиг.16) сигнала О устройство находится в состоянии Останов В этом состоянии обеспечиваются режимы записи и чтения, временные диаграммы которых приведены на фиг.25. Запись информации в регистр 2 адреса, регистр 3 состояния и регистр 4 частоты (фиг.1) осуществляется согласно алгоритму, приведенному на фиг.25. Информация задается значения ми сигналов на выходах блока 16 пред варительной установки (фиг.15), которая поступает на группу входов-выходов второго блока 13 ключей. Сигнал О тумблером ЗПРС,РЧ,РА в бло. ке 16 предварительной установки (фиг. 16) подается в блок 15 управления, где в результате формируются стробы записи в регистры 2-4 адреса, состояния и частоты соответственно (фиг. 1) . Блок 1 памяти представляет собой накопитель емкостью, например, 1024 к X 34 разрядных слов, причем зачтись из блока 16 предварительной установки осуществляется поблочно по шестнадцать разрядов ПАМО, ПАМ1}ПАМ2 (фиг.18). Идентификация блока памяти осуществляется подачей на одну из уп равляющих линий ЗППО, ЗШП , ЗПП2 (фиг. 16) сигнала О. При изменении 25 состояния регистра 2 адреса информация адресуется к другой ячейке блока 1 памяти. Запись в младший разряд регистра 3 состояния значения О или 1 (фиг.17) определяет условие запуска устройства. Переход устройства из состояния Останов в состояние Пуск осуществляется двумя способами, в зависимости от значения младшего разряда регистра 3 состояния (фиг.17). При значении 1 разрешен переход устройства в состояние Пуск по сигналу на линии 35 работы (фиг.1), при значении О по внешнему сигналу на линии 18 (фиг. 1). Устройство имеет третье состояние Предзапуск, которое определяется, как промежуточное состояние между Остановом и Пуском. В этом состоянии устройство будет находиться после того, как на линии 35 Режим работы произошло переключение сигнала из значения О в значение 1 (в регистре 3 состояния разряд, определяющий условие запуска, имеет значение О), а внешний запускающий сигнал по линии 18 с объекта диагностирования еще не появился. Переход устройства в состояние Пуск означает переход в режим генерирования тестовой последовательности (выполнение тестовой диагностической программы, записанной в блоке 1 памяти) . Он осуществляется в двух ре-. жимах - автоматическом и пошаговом. В автоматическом режиме вьшолнение команд производится без вмешательства оператора по программе, которая предварительно заложена в блок 1 памяти. В пошаговом режиме необходима постоянная инициация со стррюны оператора на выполнение каждой команда.Инициация выполнения очередной команды устройства осуществляется процедурой чтения блока ПАМ2 (фиг.18). Генерирование тестовой последовательности в режиме Шаг или Автомата определяется разрядом 34 блока . памяти ПАМ2 (фиг.18). В режиме генерирования тестовой последовательности из блока 1 памяти выбирается слово, адрес которого соответствует значению регистра 2 адре са (фиг.1). Три старшие разряда этого слова определяют формат команды. Устройство имеет три формата команд (фиг.19). в формате О предусмотрег-шг следующие команды устройства: запись поля дйнных (фиг,20) в выходной регистр 6; запись поля данных (фиг,20) в регистр 7 маски; ожидание событий, в котором блок 15 управления (фиг.2) вырабатывает сигналы, которые фиксируют память 1 на выбранном слове,запускают счетчик 8, на четвертый вход которого подаются синхросигналы с блока 15 управления (фиг.1), а на пятый сигнал разрешения счета уровня 1 с этого же блока. Регистр 2 адреса находится в ожидании одного из. двух событий: сравнения содержимого поля данных (разряды ДАМ 31,,.00) со значениями сигналов на входньгх каналах 19 устройство (фиг.20) с учетом маскирования раз7 маски в соответс рядов в регистре ВИИ с выра сением F : Х-(к 3,..00 5rPtl 31. .. где К - к-й входной канал устройств . R - поле данных, разряды ПА11 31 .. . переполнение счетчика 8, запуск кот рого осуществляется микрооперацией Ожидание событий, При первом событии значение регистра 2 адреса (РА) увеличивается на два (РА : РА + 2), при втором событии значение РА увеличивается н единицу (РА : РА + 1). После отслеживания одного из дву указанных событий, реализземых при формате О (микрооперация ожидания), устройство переходит к разбору следутощей команды, выбранной из блока памяти. По команде Запись поля дан ньи в выходной регистр производится запись выбранного слова .,.00 в регистр 6 выходной, а в регистр 2 адреса добавляется единица (РА : РА + 1), и из блока 1 памяти выбирается следующее слово. По команде Запись поля данных в регистр маски (ЗПРМ) производится запись слова ПАМ 31...00 в регистр 7 маски, а в РА добавляется единица и выбирается следующее слово из блока 1 памяти, В формате 1 (фиг.21) выполняются следующие команды: запись поля данных в регистр 2 адреса, запись поля данных в регистр 5 возврата. После выполнения любой из команд значение регистра РА 2 увеличивается на един цу (РА : РА + 1), из блока 1 пам ти выбирается следующее слово. 25 В формате 2 (фиг.21) выполняются следуюпще команды выдача радиального запроса 38 останова (фиг.2) на объект диагностирования, передача значения регистра 5 возврата в регистр 2 адреса, запись поля данных в счетчик 8, вьщача радиального запроса 38 останова (фиг.2) и останов устройства. В этом формате 2 возможны комбинации из приведенных команд при условии: записи поля данных регистра частоты и поля данных счетчика не следует выполнять, когда код, заносимый в регистр частоты, совпадает (или не имеет существенного значения для данного состояния регистра частоты) с кодом, заносимым в три младших разряда счетчика 8 (см.перекрытие полей 2 и 3 фиг, 20). Сигнал радиального запроса 38 устройства (фиг,2) вырабатывается при работе устройства в режиме генерирования последовательности и выполняет команды формата 2 в двузс случаях: при выполнении операции выдачи радиального запроса 38 останова объекта диагностирования и останова устройства, ГШИ 30 0; при выполнении команды выдачи радиального запроса 38 останова объекта диагностирования IIAM 1 26 0. Формула изобретения 1. Микропрограммное устройство формирования тестовой последовательности, содержащее блок памяти, регистр адреса, выходы которого соединены с адресным входом блока памяти, выходной регистр, группу элементов И, первые входы которых подключены к выходам объекта диагностирования, блок предварительной установки,счетчик и блок управления, отличающееся тем, что, с целью повьшения коэффициента использования оборудования, оно содержит регистр маски, регистр возврата, регистр частоты, регистр состояния, три блока ключей, цифровой компаратор,, мультиплексор, причем адресная группа выходов блока памяти соединена с первыми входами данных выходного регистра, регистра маски, цифрового компаратора, мультигшексора, с информационными входами регистра адреса, с адресной группой выходов второго блока ключей и выходами регистра возврата, группа выходов признака кода частоты блока памяти соединена с вторыми входами данных выходного регистра, регистра маски, мультиплексора, цифрового компаратора, с первыми входами данных счетчика, регистра возврата,регистра частоты, с группой выходов признака частоты второго блока ключей, группа выходов признака кода возврата блока памяти соединена с третьими входами данных выходного регистра, регистра маски, цифрового компаратора, мультиплексора, с вторы ми входами данных регистра возврата счетчика, группа выходов признака ко да счетчика соединена с четвертыми входами данных выходного регистра, регистра маски, цифрового компаратора, мультиплексора и третьими входами данных счетчика, группа выходов признака кода команд блока памяти соединена с пятыми входами данных вы ходного регистра, регистра маски, цифрового компаратора, мультиплексора, с входами признака кода команд блока управления, группа выходов признака формата команд блока памяти соединена с входами признака формата команд блока управления, с шестыми входами данных мультиплексора, адресная группа входов которого соединена с группой выходов управления мультиплексором блока управления, вторая группа управляющих выходов блока предварительной установки соединена с группой управляющих входов третьего блока ключей, группа инфор мационных входов которого соединена с группой выходов мультиплексора, вы ход индикации состояния блока управления соединен с входом индикации состояния второго блока ключей, информационная группа выходов которого соединена с информационными входами регистра состояния, тактирующий вход которого соединен с выходом признака записи в регистр состояния блока управления, группа выходов признака записи в ре гиртр адреса которого соединена с тактируюЕЩми входами регистра адреса, группа выходов которого соединена с группой адресных входов второго блока ютючей, группа входов кода частоты которого соединена с одноименной группой входов блока управления и с группой выходов регистра частоты, тактирующий вход которого соединен с выходом признака записи в регистр частоты блока управле258ния, установочная группа входов которого соединена с информационной группой входов блока памяти и с группой выходов третьего блока ключей, группа входов-выходов Адрес-данные которого соединена с группой входоввыходов Адрес-данные второго блока ключей, с группой входов-выходов Адрес-данные блока предварительной установки, интерфейсная группа выходов которого соединена с интерфейсной группой входов блока управления, вход признака переполнения которого соединен с выходом переполнения счетчика, тактирующий вход которого соединен с выходом признака записи в счетчик блока управления, выход признака записи в регистр маски блока управления соединен с тактирующим входом регистра маски, группа выходов которого соединена с вторыми входами элементов И группы, выходы которых соединены с шестой группой бходов данных цифрового компаратора, выход признака сравнения которого сое.динен с входом признака сравнения блока управления, выход разрешения счета которого соединен с управляющим входом цифрового кo mapaтopa и с входом разрешения счета счетчика, выход признака выдачи информации блока управления соединен с входом разрешения выдачи информации первого блока ключей, информационные входы которого соединены с выходами выходного регистра, а выход - с выходами данных устройства, тактирующий вход выходного регистра соединен с выходом признака записи в выходной регистр блока управления, группа выходов признака записи в регистр возврата которого соединена с группой тактирующих входов регистра возврата, выходы регистра состояния соединены с информационной группой входов блока управления и с информационной группой входов второго блока ключей, группа выходов управления блоком памяти блока управления соединена с группой входов выборки кристалла и записи-чтения блока памяти, группа выходов сопровождения информации блока управления соединена с управляюшд ми выходами устройства, а вход запуска блока управления соединен с управляющим входом устройства. 2. Устройство по п.1, отличающееся тем, что, блок; управления содержит генератор, форми рователь импульсов, ком гутатор условий запуска, узел синхронизации,первый дешифратор, коммутатор адреса, переключатель режима, узел задержки, коммутатор, второй дешифратор, комму татор управляющих сигналов, причем первый вход первого дешифратора соединен с первым управляющим входом ком1чутатора адреса и с первым управляющим выходом второго дешифратора, первый управляющий вход которого сое динен с первым управляющим выходом первого дешифратора, второй информационный вход которого соединен с вто рым информационным выходом второго дешифратора, второй тактируюищй вход которого соединен, с первым тактирующим выходом узла синхронизации,второй управляющий выход которого соеди нен с третьим управляющим входом вто рого дешифратора, четвертый тактирую щий вход которого соединен с первым тактирующим входом узла задержки и с третьим тактируюЕЦ1м выходом узла синхронизации, первьй вход которого соединен с первым выходом генератора, второй выход которого соегдинен с первым управляющим входом гсоммутатора управляющих сигналов, второй ин формационный вход которого соединен с первым информационным выходом переключателя режима, первый управляющий вход которого соединен с первым информацион1-1ым выходом коммутатора управляющих сигналов, третий информа ционный вход которого соединен с вто рым входом переключателя режима и с первым выходом узла задержки, второй информационный вход которого соединен с вторым информационным .выходом первого дешифратора, третий информационный выход которого соединен с третьим входом узла задержки, четвер тый информационный вход которого сое динен с первым информационньм входом коммутатора условий запуска и с информационным выходом коммутатора,пер вьш управляющий вход которого соединен с вторым управляющим входом коммутатора условий запуска и с четвертым выходом первого дешифратора, пятый выход которого соединен с третьи информационным входом коммутатора адреса, второй управляющий вход которого соединен с вторым выходом узла задержки, пятый вход которого является входом признака переполнения блока управления, третий выход узла задержки является выходом признака записи в счетчик блока управления, третий выход второго дешифратора соединен с вторым информационным входом коммутатора и с четвертым информационным входом коммутатора управляющих сигналов, пятый информационный вход которого соединен с четвертым информационным входом коммутатора адреса и с шестым выходом первого дешифратора, седьмой выход которого является выходом признака записи в регистр частоты блока управления, второй вход узла синхронизации является входом кода частоты блока управления, третий вход узла синхронизации соединен с первым выходом формирователя импульсов, второй выход которого соединен с третьим управляющим входом коммутатора условий запуска, четвертый управляющий вход которого соединен с шестым управляющим входом коммутатора управляющих сигналов, с первым входом формирователя импульсов и является интерфейсным входом блока управления, третий выход генератора соединен с четвертым входом узла синхронизации, четвертый выход генератора соединен с вторым входом формирователя импульсов, третий вход которого соединен с первым информационным выходом коммутатора условий запуска, второй и третий информационные выходы которого соединены с третьим и четвертым входами переключателя режима соответственно, второй выход которого соединен с пятым входом второго дешифратора, четвертый выход которого соединен с пятым информационным входом коммутатора адреса, первый и второй информационные выходы которого являются выходом признака записи в регистр адреса блока управления, восьмой и девятый выходы первого дешифратора являются выходами сопровождения информации устройства, десятый выход является выходом признака записи в регистр возврата, одиннадгдатый выход является выходом признака записи в регистр маски, двенадцатый выход является выходом признака записи в выходной регистр, второй выход коммутатора управляющих сигналов является выходом управления блока памяти устройства, шестой вход узла задержки является входом признака сравнения блока уп11равления, четвертый выход узла задержки является выходом разрешения I счета блока управления, пятый вход переключателя режима соединен с пятым выходом второго дешифратора,шес той выход которого соединен с шестым входом коммутатора адреса, седьмой вход которого соединен с третьим входом первого дешифратора, с третьим выходом коммутатора управляющих сигналов и является выходом признака записи в регистр состояния бл ка управления, пятый вход коммутато ра условий запуска является информа ционным входом блока управления,тре тий выход переключателя режима явля ется выходом управления мультиплексором блока управления, четвертый и 2512 пятый входы первого дешифратора являются входами признака кода и формата команд блока управления, шестой вход коммутатора условий запуска ляется входом запуска блока управления, шестой вход переключателя режима является установочным входом блока управления, третий выход группы выходов блока предварительной установки соединен с третьим входом блока стробирования, седьмой вход переключателя режима является интерфейсным входом блока управления, четвертый выход коммутатора управляющих сигналов содержит выходы индикации состояния и признака выдачи информации блока управления, пятый выход комчутатора управляющих сигналов соединен с третьим входом коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Мультимикропрограммное устройство управления с контролем | 1985 |

|

SU1272333A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для программного управления | 1989 |

|

SU1656498A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1282121A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

| Устройство для обмена информацией | 1983 |

|

SU1149239A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

Изобретение относится к вьтислительной технике. Целью изобретения является повьппение коэффициента использования оборудования. Изобретение содержит блок памяти, регистры адреса, состояния, частоты, возврата, выходной, маски, блок управления, счетчик, компаратор, мультиплексор, блоки ключей, группу элементов И. Устройство осуществляет автоматическое формирование тестовых последовательностей для различных типов про9 веряемых блоков. 1 з.п. ф-лы, 25 ил. (Л

Фиг. 1

go5i

г

2

« i- «TL-j «Л

«

55

Фаг. 4

Фае. б

CPus.6

Omff/r. 31

TT

OmSfi.25

Л-Г

OmSff.26

32

ffff.2

JJ

79

0/nS/T.2S

От 5л. 31

Фиг. 7 Щ109

OmSa.l

eel

т

опИя.гз

Фиг. 8

ffMO,ff,fJ

3,15,27 /Cffjf.29

Фиг, il

Фиг. 12

Фив. 13

От5л.16

От Ил. i6

Фи8. f6

РЧPA

PC

Фиг. 17

ПАМО

ПАМ1

Фиг. f8

11

1 X

о/ - 1

оо - Формат 2

32x51 30

ч

/ V

Микрооперация Пале данных (uMOcpfiaaua) Фо/зматО

... igюход 00

Формата МикрооперацияПш,еданнш1 Пш еданнш2

nAM 3j2jn JO ... 26 25..f2// ...OO Формат 2 Микроопдрация Поле 2 ПвлеЗ fToflef

Формат О

Фи2.19

0100

Фиг. 20 i1 1О О1 ОО 01 1О I1 II 11 11 10 01

а) Записи 9 petucmp адреса папяти 2 псцголлельной информации

J Управланщий симал

CmpoS записи Формат О -о кидание св5ытия (ОЖ) -sanuctf слова б Pesttcmp вд(ходной -залисб слова в Регистр Формат 1 РА: поле Of РВ- поле1 РА- лолеО отсутствие операции Формат 2 11О Выдача радиаль ео sofyjoco 1О1 РА-.РВ 011 pi/:«/to/re.J 111 РТ: /юле2 111 Btfdava fladuaMMfff Фаё.21 38 на объект диагностирования Ъ8 и ocmof e аздмий

S) -t-lS регист/} адреса памяти г (счётный pe/ttu/ )

144 144

-(Мрес (данные

й

лзп

773

Фиг. 24

А

5

-- Адрес

Xх /

ОБМ/

ДЧТ

X

ОГВ

5} Цикл tneнu$ Фиг. 25

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для тестового диагностирования | 1982 |

|

SU1045230A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-30—Публикация

1984-06-25—Подача