является первым входом устройства, четвертый вход третьего элемен- та И-ИЛИ является вторым входом устройства,. 5ЫХОД дешифратора соединен с вторым входом блока индуктивнЕ 1Х датчиков, выход накопителя соединено пятым входом второго элемента И-ИЛИ, выходы второго и третьего элементов И-ИЛИ соединен с входами блока сравнения.

2, Устройство по п. 1, от тем, что . упс я

ч а ю щ е

равления содержит мультивибратор, регистр, формирователь импульсов, распределитель и формирователь командных импульсов, первый вход которого соединен с выходом распределителя, вход распределителя соединен .с первым вых-одом формирователя импульсов, первый вход которого соединен с выходом мультивибратора, второй выход и второй вход формирователя импульсов соединены соответственно с входом и выходом регистра, выход распределителя является первым выходом блока управления, второй, третий, четвертый, пятый,шестой, седьмой и восьмой входы формирователя командных импульсов являются первым, вторым, третьи, четвертым, пятым, шестым и с ;дьмым входами блока управления, первый, второй, третий, четвертый, пятый, шестой.и седьмой выxoд J формирователя командных импульсов являются вторым, третьим, четвертым, пятым, шестым, седьглым и восьмым выходами блока управления,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля постоянной памяти | 1987 |

|

SU1411838A2 |

| Устройство для контроля постоянной памяти | 1984 |

|

SU1191944A1 |

| Устройство для контроля постоянных запоминающих устройств | 1976 |

|

SU563697A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1151991A1 |

| Устройство для контроля постоянных запоминающих устройств | 1976 |

|

SU622175A2 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU886059A1 |

| Устройство для контроля электрического монтажа | 1985 |

|

SU1390616A1 |

| Устройство для контроля электрического монтажа | 1987 |

|

SU1455347A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1138809A1 |

| Устройство для контроля электрического монтажа | 1985 |

|

SU1345212A1 |

1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ПОСТОЯННОЙ ПАМЯТИ, содержащее блок ввода информации, вход которого соединен с первым выходом блока управления, накопитель, первыйвход которого соединен с вторым выходом блока управления, формирователь информационных сигналов, вход которого соединен с выходом блока индуктивных датчиков, генератор тока, выход которого соединен с первым входом блока индуктивных датчиков, блок сравнения, первый выход которого соединен с первым входом блока управления, блок ввода контрольных сигналов, вход которого и второй вход блока управления соединены с первым выходом блока ввода информации, блок регистрации ошибок, первый вход которого и третий вход блока управления соединены с вторым выходом блока ввода информации, второй и третий входы блока регистрации ошибок соединены соответственно с вторым и третьим выходами блока сравнения и блока управления, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены счетчик, дешифратор, формирователь адресных сигналов, элементы И-ИЛИ, элемент задержки и формирователь управляющих сигналов, первый и второй входы которого соответственно соединены с первым и четвертым выходами блока управления, четвертый вход блока управления соединен с первым выходом блока ввода контрольных сигналов, вход которого и первый вход первого элемента И-ИЛИ соединены с первым выходом блока ввода информации, третий выход которого соединен с вто рым входом первого элемента , третиП вход которого соединен с пятым выходом блока управления, второй выход блока ввода контрольных сигналов соединен с четвертым входом первого элемента И-ИЛИ, BTOPI IM входом накопителя и первым входом второго элемента И-ИЛИ, второй вход которого соединен с шестым выходом блоi ка управления, седьмой выход которого соединен с первым входом счетчика, второй вход которого соединен с выходом первого элемента И-ИЛИ, первый выход счетчика соединен с пятым входом блока управления, второй выход счетчика - с первым входом фop lиpoвaтeля адресных сигналов, пер-вым входом дешифратора, третьим входом накопителя и четвертым входом блока регистрации ошибок, выход коГО торого соединен с шестым входом блока управления, восьмой выход блока 01 управления соединен с вторым входом дешифратора и входоп элемента задержки, выход которого соединен с первь входом третьего элемента И-ИЛИ второй вход которого соединен с выходом формирователя информационных сигналов, первый выход формирователя управлякадих сигналов соединен с седьмым входом блока управления, а второй выход - с вторым входом формирователя адресных сигналов, третьими входами второго и третьего элементов И-ИЛИ и является первым выходом устройства, первый и второй выходы формирователя адресных сигналов являются соответственно вторым и третьим выходами устройства, ;четвертый вход второго элемента И-ИЛИ

Изобретение относится к вычислительной технике, в частности к запоминающим устрой,ствам, и может быть использовано для контроля блоков постоянной памяти и кодовых жгутов.

Известно устройство для контроля постоянных запоминающих устройств, содержащее блок считывания информации, соединенный с регистром определения приор-итета, адресным счетчиком и блоком управления. Регистр определения приоритета соединен с блоком анализа ошибок- и блоком ключей. Адресный счетчик, соединен с дополнительнытГ адресным счетчиком, комз гугатором, дешифратором адреса, дешифратором определения приоритета, блоком управления и блоком анализа опл-гэок. Блок управления связан с блоком анализа ошибок ,дополнительньгм адресным счетчиком,дешифратором определе1ИЯ приоритета ,-распределителем, блоко зыборки адресов приоритета и генерато1ЭОМ синхроимпульсов. Блок анализа ошибок подключен к-Дополнительному адресному счетчику, коммутатору и блоку выборки адресов приоритета. Коммутатор подключен к дешифратору адреса и генератору синхроимпульсов. Дешифратор определения приоритета с.оёдинен с распределителем, который соединен с блоком выборки адресов г:риоритета l.

Недостатком устройства является fc:eBHCOKOe быстродействие, так как косителем контрольной инфомации яв j:HeTCH перфокарта, считывание с которой имеет небольшую скорость, а также постоянная разрядность эталонного слова, что снижает номенклатуру проверяемых изделий,

2

Наиболее близким к изобретению по технической сущности является усройство для контроля блоков постоян ной памяти, содержащее блок ввода контрольных сигналов, блок управления, накопитель, группу генераторов токовых импульсовр первый блок местного управления, формирователь контрольных сигналов, распределитель синалов, схему сравнения, группу индуктивных датчиков, второй блок месного управления и Формирователь информационных сигналов, причем выход блока ввода информационных сигналов подключен к первому входу формирователя адресных сигналов, а первый вход - к первому выходу блок управления. Второй вход блока управления соединен с вторым входом формирователя адресных сигналов, третий выход и первый вход. - соотвётственно с первыми входами и выходом первого блока местного управления, а четвертый выход и второй вход - соответственно с первым Е:ходом и выходом схемы сравнения. Первый и второй входы накопителя подключены соответственно к пятому выходу блока управления и первому выходу формирователя адресных сигналов,, .

Первый вход формирователя контрольных сигналов подключен к первому выходу распределителя сигналов, второй вход - к шестому входу блока управления, а выход - к третьему входу накопителя. Первый, второй и третий входы распределителя сигналов соединены соответственно с выходом блока ввода контрольных сигналов,, выходом накопителя и седьмым входом блока управления. Выход распределителя сигналов подключен к второму входу схемы сравнения. Одни из входов генератора токовых импульсов соединены с вторым выходом первого блока местного управления, другие входы - с вторым входом формирователя адресных сигналов, а выходы - с одними из входов индуктивных датчиков, другие входы которых подключены к выходу второго блока Iместного управления. Первый и второй входы второго блока местного управления соединены соответственно с третьим выходом формирователя адресных сигналов и восьмым выходом блока управления.. ходы индуктивных датчиков подключе к входам формирователя информацион ных сигналов, выход которого соеди нен с третьим входом схемы сравнени Второй вход блока ввода контрольных сигналов является входом устройства 2. Недостатком известного устройств является то, что его быстродействие ограничено скоростью работы блока ввода контрольных сигналов, который является электромеханическим считывателем информации с программоносителя со скоростью считывания неско ких перфокарт в секунду.В режиме сравнения,когда контрольная информ ция хранится в накопителе устройст быстродействие контроля также огра чено скоростью выбора контрольных чисел из накопителя ЗУ. Кроме того, для обеспечения процесса контроля необходимо иметь рабочие программы, составление которых требует дополнительной затраты рабочего времени высококвалифицированного обслуживающего персонала. Цель изобретения - повышение быс родействия устройства путем обеспечения режима, позволяющего проводить контроль блоков памяти и кодовых жгутов методом сравнения с устройствами, хранящими аналогичную числовую программу, со скоростью контроля, близкой к режиму работы в реальном масштабе времени, а также снижение трудоемкости процесса контроля за счет того, что при изготовлении приборов большой серии не требуется составление рабочих программ. Поставленная, цель достигается тем, что в устройство для контроля блоков постоянной памяти, содержащее блок ввода информации, вход которого соединен с первым выходом блока управления, накопитель, первый вход которого соединен с вторым выходом блока упр авления, формирователь информационных сигнаиюв, вход которого соединен с выходом блока индуктивных датчиков, генератор тока, выход которого соединен с первым входом блока индуктивных датчиков, блок сравнения, первый выход которого соединен с первым входом блока управления, блок ввода контрольных сигналов, вход которого и второй вход блока управления соединены с первым выходом блока ввода информации, блок регистрации ошибок, первый вход которого и третий вход блока управления соединены с вторым выходом блока ввода информации, второй и третий входы блока регистрации ошибок соединены соответственно- с вторым и третьим выходами блока сравнения и блока управления, введены счетчик, дешифратор, формирователь адресных сигналов, элементы И-ИЛИ, элемент задержки и формирователь управляющих сигналов, первый и второй входы которого соответственно соединены с первым и четвертым выходами блока управления, четвертый вход блока управления соединен с первым выходом блока ввода контрольных сигналов, вход которого и первый вход первого элемента И-ИЛИ соединены с первым выходом блока ввода информации, третий выход которого соединен с вторым входом первого элемента И-ИЛИ, третий вход которого соединен с пятым выходом блока управления, второй выход блока. ввода контрольных сигналов соединен с четвертым входом первого элемента И-ИЛИ, вторым входом накопителя и первым входом второго элемента И-ИЛИ, второй вход которого соединен с шестым В1ЛХОДОМ блока управления, седьмой выход которого соединен с первым входом счетчика, второй вход которого соединен с выходом первого элемента И-ИЛИ, первый выход счетчика соединен с пятым входом блока управления, второй вы ход счетчика - с первым входом формирователя адресных сигналов, первым входом дешифратора, третьим входом накопителя и четвертым входом блока регистрации ошибок, выход которого соединен с шестым входом блока управления, восьмой выход блока управления соединен с вторым входом дешифратора и входом элемента задержки, выход которого соединен с первым входом третьего элемента И-ИЛИ, второй вход которого соединен с выходом формирователя информационных, сигналов, первый выход формирователя управляющих сигналов соединен с седьмым входом блока управления, а второй выход - с вторым входом формирователя адресных сигналов, третьими входами второго и третьего элементов И-ИЛИ и является первым выходом устройства, первый и второй выходы формирователя адресных- сигналов являются соответственно вторым и третьим выходами устройства, четвертый вход второго элемента И-ИЛИ является первым входом устройства, четвертый вход третьего элемента И--ИЛИ является вторым входом устройства, выход дешифратора соединен с вторым входом блока индуктивных датчиков, выход накопителя соединен с пятым входом второго эле.лента И-ИЛИ, выходы второго и третьего элементов И-ИЛИ соединены с входами блока сравнения.

Кроме того, блок управления содержит мультивибратор, регистр, форр ирователь имлульсов, распределител и формирователь командных импульсов первый вход которого соединен с выходом распределителя, вход распределителя соединен с первым выходом формирователя импульсов, первый вход которого соединен с выходом мультивибратора, второй выход и второй вход формирователя импульсов соединены соответственно с входом и выходом регистра, выход распределителя является первым выходом блока управленияр второй, третий, четвертый, пятый, ше.стой, седьмой и восьмой вхо,ды формирователя командных импульсов являются первым, вторым, третьимt четвертым, пятым, шестым и седьмым входами блока управления, первый, второй, третий, четвертьлй , пятый, шестой . и. седьмой выходы формирователя командных импульсов являются вторым, третьи у1, четвертыги, пятым, шестым, седьмым и вось№о1м выходами блока управления.

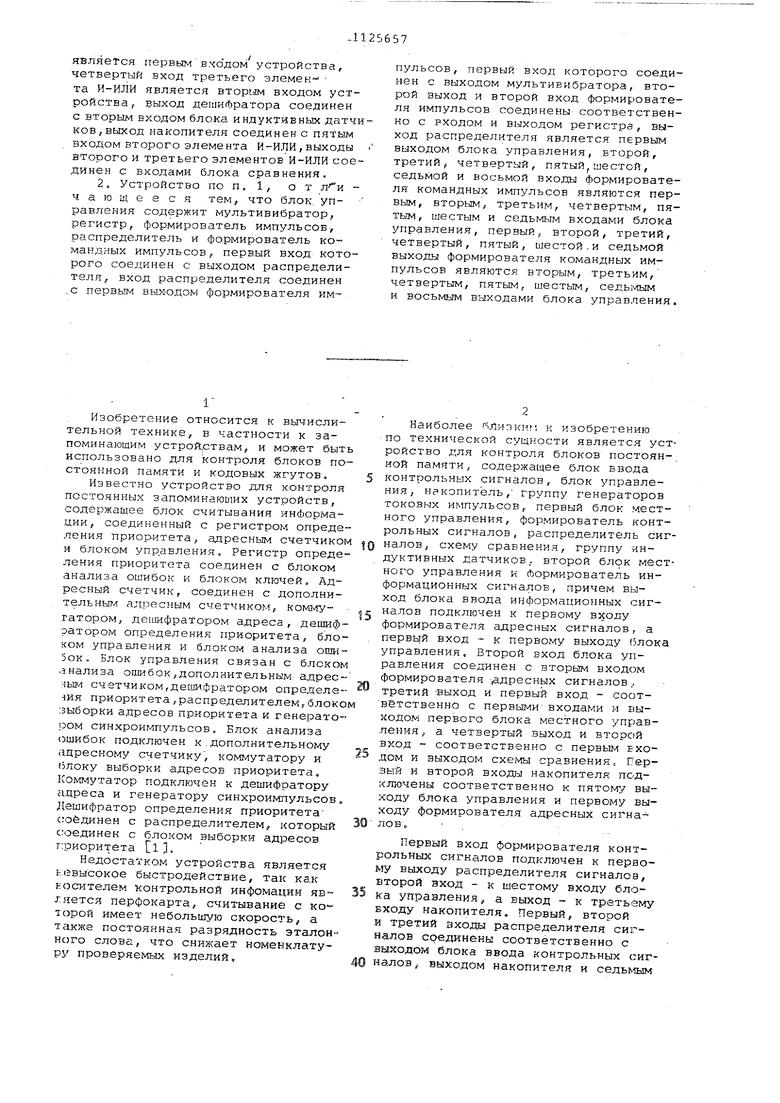

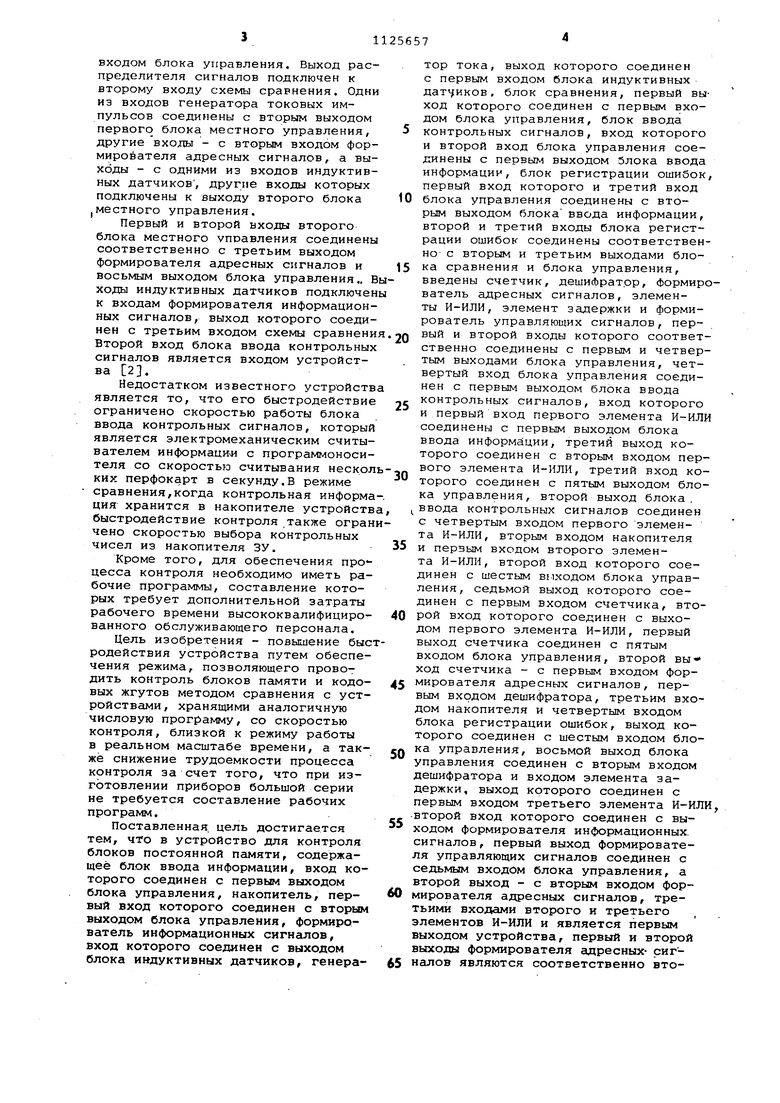

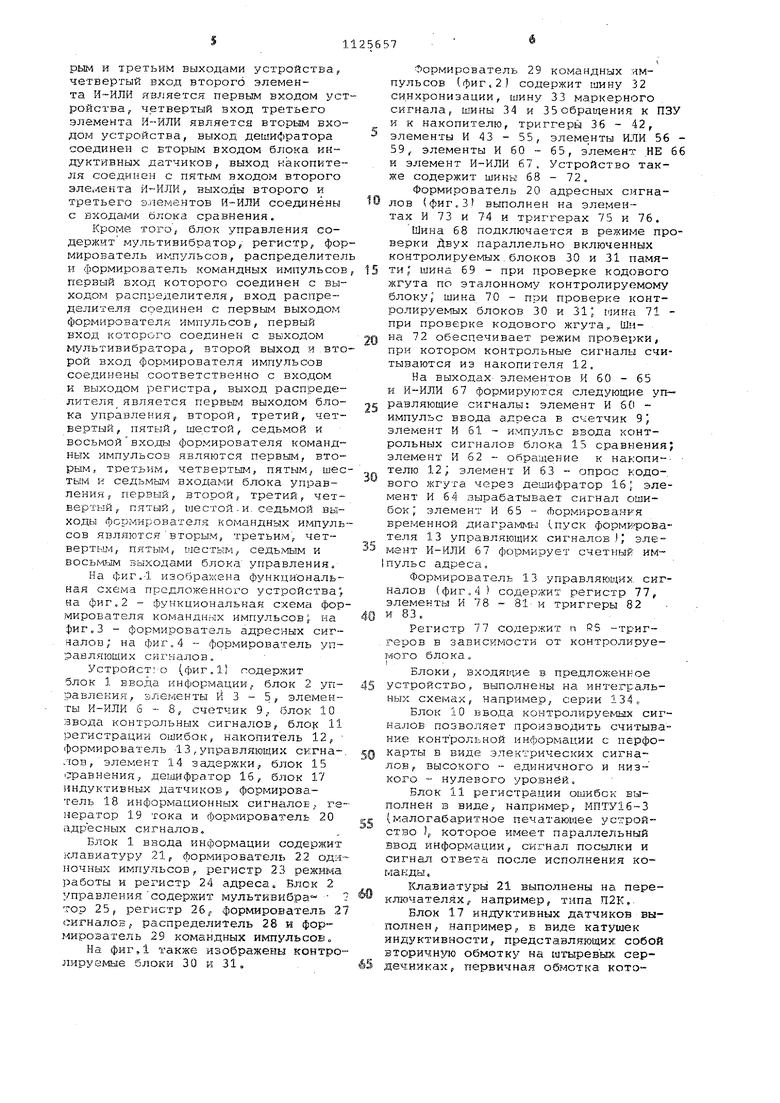

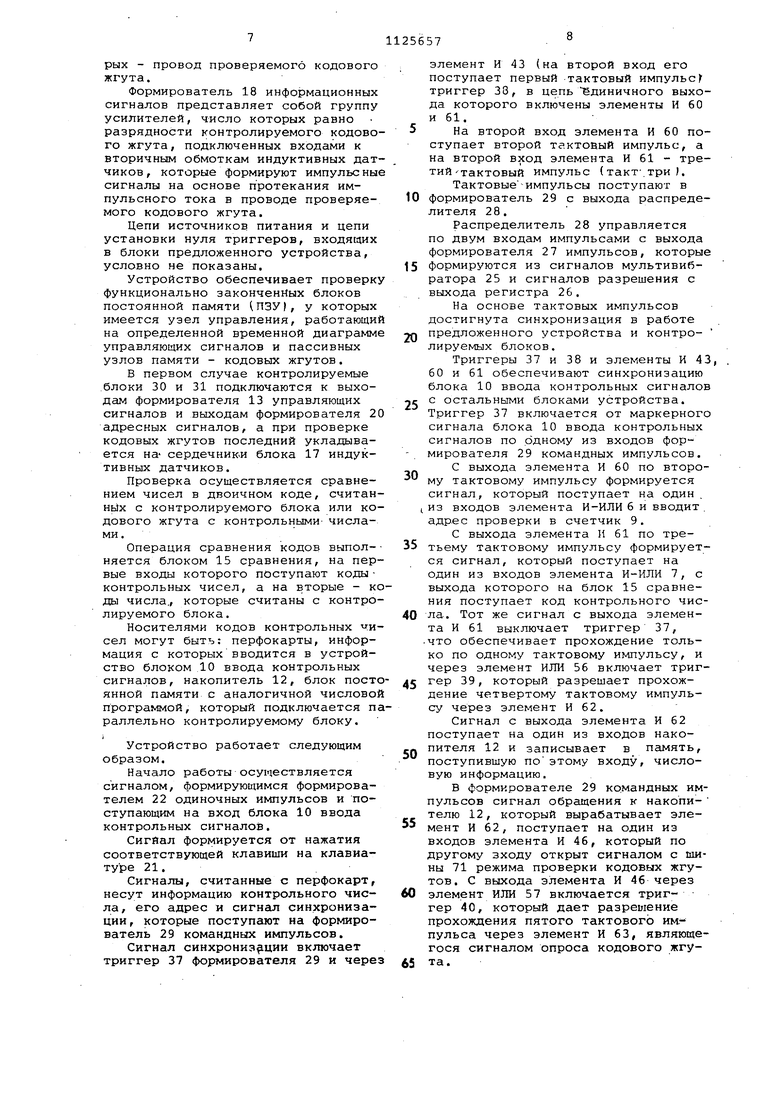

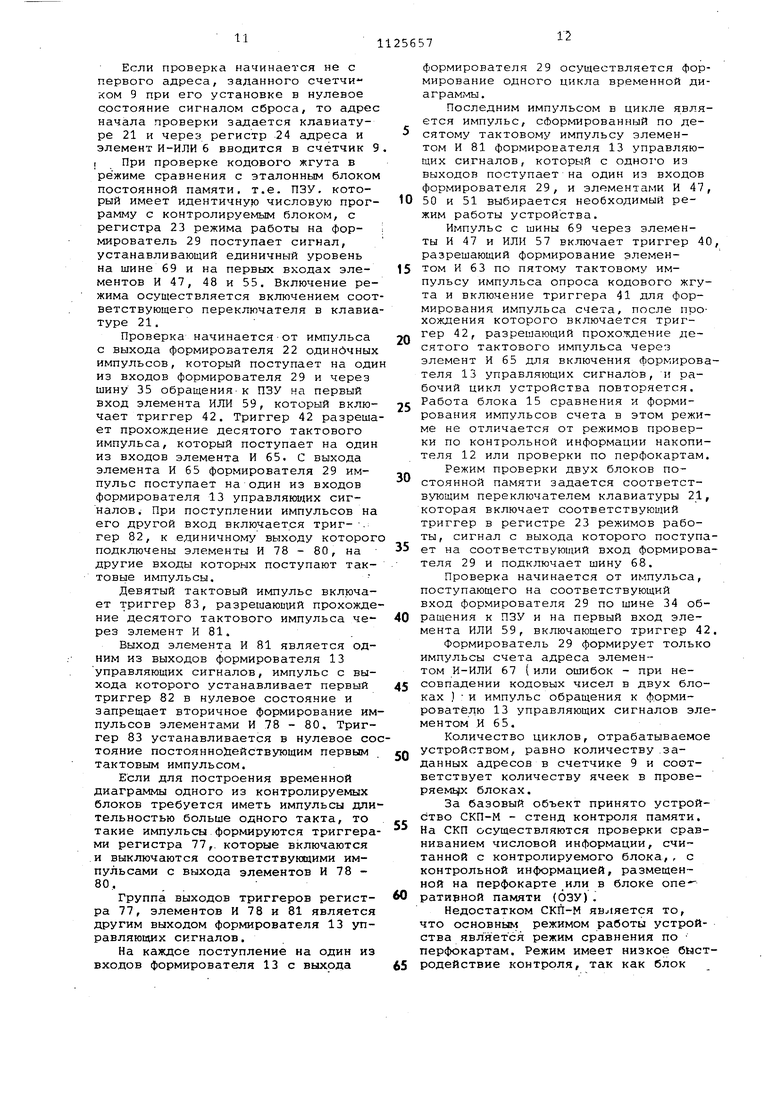

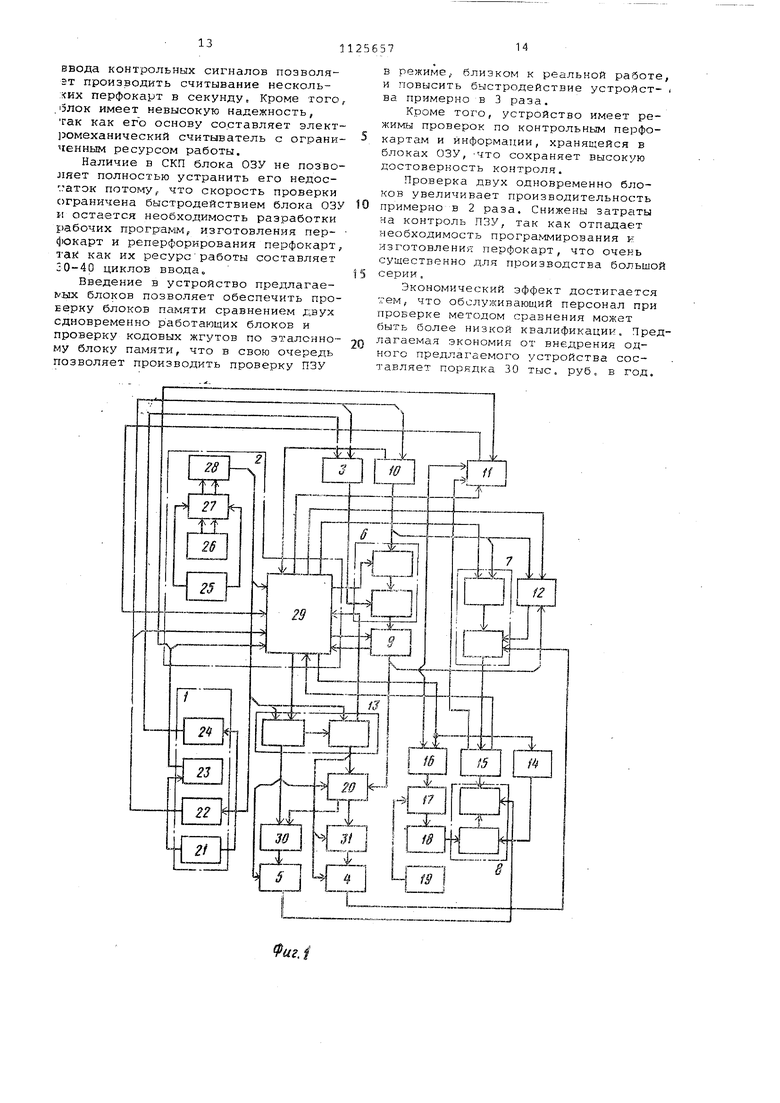

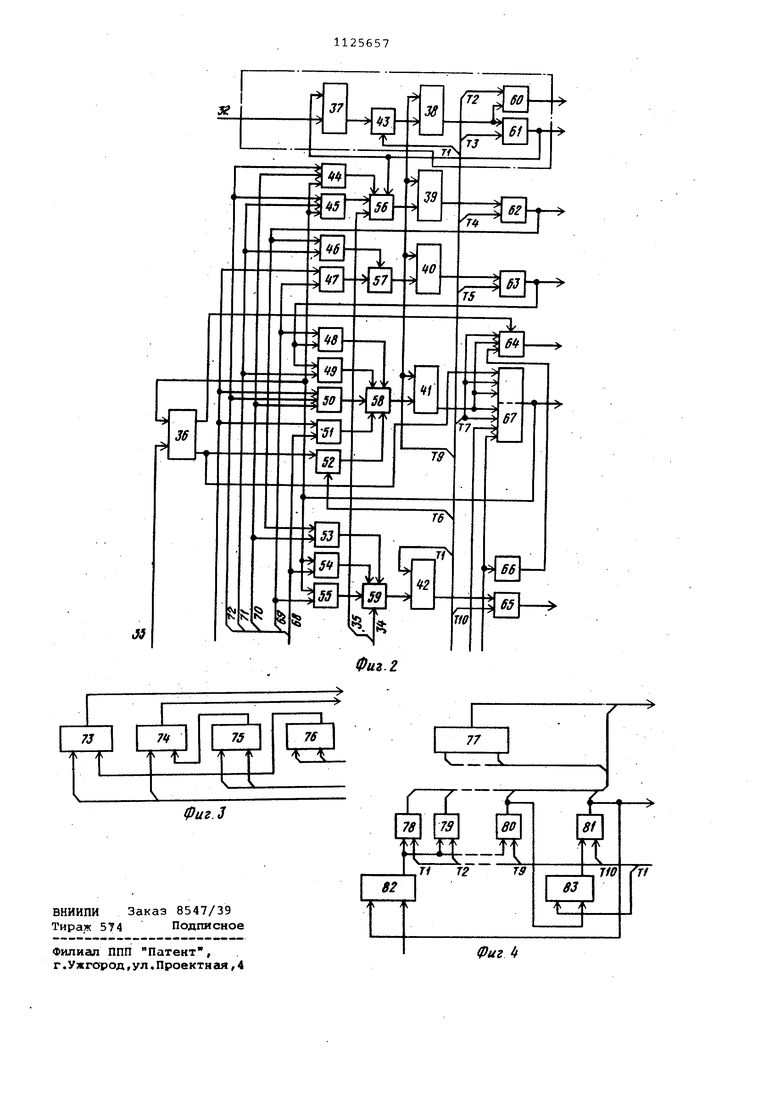

На фиг.1 изображена функциональная схема предложенного устройства; на фиг.2 - функциональная схема формирователя командных импульсов;, на фиг.З - формирователь адресных сигналов; на фиг.4 - формирователь управляющих сигналов.

Устройство (фиг,и подержит блок 1 ввода информации,, блок 2 управления, элементы И 3 - 5, элементы И-ИЛИ 6-8, счетчик 9, блок 10 звода контрольных сигналов, блок 11 регистрации ошибок, накопитель 12, формирователь 13,управляющих скгналов, элемент 14 задержки, блок 15 гравнения, дешифратор 16, блок 17 индуктивных датчиков, формирователь 18 информационных сигналов- генератор 19 тока и формирователь 20 адресных сигналов,

Блок 1 ввода информации содержит клавиатуру 21, формирователь 22 одиночных импульсов, регистр 23 режима работы и регистр 24 адреса. Влек 2 управления содержит мультивибра™ тор 25, регистр 26 формирователь 27 сигналов,, распределитель 28 и формирователь 29 командных импульсов

На фиг,1 также изображены контролируемые блоки 30 и 31.

Формирователь 29 командных импульсов (фиг,2) содержит шину 32 синхронизации, шину 33 маркерного сигнала, шины 34 и 35 обращения к ПЗ и к накопителю, триггеры 36 - 42, элементы И 43 - 55, элементы ИЛИ 56 59, элементы И 60 - 65, элемент НЕ и элемент И-ИЛИ 67. Устройство также содержит шины 68 - 72.

Формирователь 20 адресных сигналов (фиг.З выполнен на элементах И 73 и 74 и триггерах 75 и 76,

Шина 68 подключается в режиме прверки Двух параллельно включенных контролируемых.блоков 30 и 31 памяти, шина 69 - при проверке кодового жгута по эталонному контролируемоглу блоку; шина 70 - при проверке контpoлиpye 1ыx блоков 30 и 31; 1аина 71 при проверке кодового жгута,, Шина 72 обеспечивает режим проверки, при котором контрольные сигналы считываются из накопителя 12.

На выходах элементов И 60 - 65 и И-ИЛИ 67 формируются следующие управляющие сигналы: элемент И 60 импулХ)С ввода адреса в счетчик 9J элемент И 61 - импульс ввода контрольных сигналов блока 15 сравнения элемент И 62 - обращение к накопителю 12; элемент И 63 - опрос кодового жгута через дешифратор 16 элемент И 64 вырабатывает сигнал ошибок J элемент И 65 - Лормирования временной диагра (пуск формирователя 13 управляющих сигналов}; элемент И-ИЛИ 67 формирует счетный им1 пульс адреса.

Формирователь 13 управляющих сигналов (фиг,4 ) содержит регистр 77, элементы И 78 - 81 и триггеры 82 и 83.

Регистр 77 содержит п RS -триггеров в зависимости от контролируемого блока.

Блоки, входящие в предложенное устройство, выполнены на интегральных схемах, например, серии 134„

Блок 10 ввода контролируемых сигналов позволяет производить считывание контрольной информации с перфокарты в виде электрических сигналов высокого - единичного и низкого нулевого уровней.

Блок 11 регистрации ошибок выполнен в виде, например, МПТУ16-3 (малогабаритное печатающее устройство If которое имеет параллельный ввод информации, сигнал посылки и сигнал ответа после исполнения команды

Клавиатуры 21 выполнены на переключателях , например, типа П2К,

Блок 17 индуктивных датчиков выполнен, например, в виде катушек индуктивности, представляющих собой вторичн /ю обмотку на штыревых серяечникак, первичная обмотка которых - провод проверяемого кодового жгута.

Формирователь 18 информационных сигналов представляет собой группу усилителей, число которых равно разрядности контролируемого кодового жгута, подключенных входами к вторичным обмоткам индуктивных датчиков, которые формируют импульсные сигналы на основе протекания импульсного тока в проводе проверяемого кодового жгута.

Цепи источников питания и цепи установки нуля триггеров, входящих в блоки предложенного устройства, условно не показаны.

Устройство обеспечивает проверку функционально законченных блоков постоянной памяти (ПЗУ}, у которых имеется узел управления, работающий на определенной временной диаграмме управляющих сигналов и пассивных узлов памяти - кодовых жгутов.

В первом случае контролируемые блоки 30 и 31 подключаются к выходам формирователя 13 управляющих сигналов и выходам формирователя 20 адресных сигналов, а при проверке кодовых жгутов последний укладывается на- сердечники блока 17 индуктивных датчиков.

Проверка осуществляется сравнением чисел в двоичном коде, считанHbJx с контролируемого блока или кодового жгута с контрольными- числами.

Операция сравнения кодов выполняется блоком 15 сравнения, на первые входы которого поступают коды контрольных чисел, а на вторые - коды числа,, которые считаны с контролируемого блока.

Носителями кодов контрольных чисел могут быть: перфокарты, информация с которых вводится в устройство блоком 10 ввода контрольных сигналов, накопитель 12, блок постоянной памяти с аналогичной числовой программой, который подключается параллельно контролируемому блоку.

Устройство работает следующим Образом.

Начало работы осуществляется сигналом, формирующимся формирователем 22 одиночных импульсов и поступающим на вход блока 10 ввода контрольных сигналов.

Сигйал формируется от нажатия соответствующей клавиши на клавиатуре 21,

Сигналы, считанные с перфокарт, несут информацию контрольного числа, его адрес и сигнгш синхронизации, которые поступают на формирователь 29 командных импульсов.

Сигнал синхронизации включает триггер 37 формирователя 29 и через

элемент И 43 (на второй вход его поступает первый тактовый импульс триггер 33, в цепь единичного выхода которого включены элементы И 60 и 61.

На второй вход элемента И 60 поступает второй тактовый импульс, а на второй вход элемента И 61 - третийтактовый импульс (такт.три).

Тактовые-импульсы поступают в

0 формирователь 29 с выхода распределителя 28.

Распределитель 28 управляется по двум входам импульсами с выхода формирователя 27 импульсов, которые формируются из сигналов мультивиб5ратора 25 и сигналов разрешения с выхода регистра 26.

На основе тактовых импульсов достигнута синхронизация в работе предложенного устройства и контро0лируемых блоков.

Триггеры 37 и 38 и элементы И 43, 60 и 61 обеспечивают синхронизацию блока 10 ввода контрольных сигналов с остальными блоками устройства.

5 Триггер 37 включается от маркерного сигнала блока 10 ввода контрольных сигналов по одному из входов формирователя 29 командных импульсов.

С выхода элемента И 60 по второ0му тактовому импульсу формируется сигнал, который поступает на один из входов элемента И-ИЛИ 6 и вводит. адрес проверки в счетчик 9.

С выхода элемента Н 61 по тре5тьему тактовому импульсу формируется сигнал, который поступает на один из входов элемента И-ИЛИ 7, с выхода которого на блок 15 сравнения поступает код контрольного чис0ла. Тот же сигнал с выхода элемента И 61 выключает триггер 37, что обеспечивает прохождение только по одному тактовому иг шульсу, и через элемент ИЛИ 56 включает триггер 39, который разрешает прохож5дение четвертому тактовому импульсу через элемент И 62.

Сигнал с выхода элемента И 62 поступает на один из входов накопителя 12 и записывает в память,

0 поступившую поэтому входу, числовую информацию,

В формирователе 29 командных импульсов сигнал обращения к накопителю 12, который вырабатывает эле5мент И 62, поступает на один из входов элемента И 46, который по другому зходу открыт сигналом с шины 71 режима проверки кодовых жгутов. С выхода элемента И 46 через

0 элемент ИЛИ 57 включается триггер 40, который дает разрешение прохождения пятого тактового импульса через элемент И 63, являющегося сигналом опроса кодового жгу5та. Сигнал опроса поступает на вход элемента 14 задержки и на один из входов дешифратора 16, который производит селекцию провода кодового жгута по адресу, выработанному- счет чиком 9 и поступающему на другой вход дешифратора 16. От протекания импульса тока в проводе кодового жгута, уровень которого определяет генератор 19 тока, блок 17 индуктивных датчиков и связанный с ним формирователь 18 информационных сигналов формируют число, состоящее из единичных и нулевых уровней сигналов, код которых соответствует кодовой раскладке жгута Сигналы поступают на один из вхо цов элемента И-ИЛЙ 8,другой вход ко горого стробирован импульсом с выхо элемента 14 задержки. Задержка подЗирается из расчета прохождения сиг опроса кодового жгута и формирования импульсов в блоке 17 индуктивных датчиков и формирователе 18 информационных сигналов. Подбор величины задержки определяет достовер ность проверки кодового жгута, при опросе которого создается высокий уровень помех. С выхода элемента И-ИЛИ 8 код контролируемого кодового жгута пос;тупает на второй вход блока 15 сравнения, где сравнивается с ранее 1 веденным в него кодом контрольного сисла. При сравнении кодов на втором вы :оде блока 15 сравнения присутстнует сигнал единичного значения, при несравнении - нулевого, т.е. низкий уровень сигнала. Если на выходе блока 15 сравнения установлен единичный сигнал, то Е формирователе 29 (на элемент ИИЛИ 67 ) поступает сигнал разрешения формирования импульса счета по седь мому тактовому Импульсу. Другие вхо ды элемента И-ИЛИ 67 управляются си налом конечного адреса, задаваемым счетчиком 9 и триггером 41, который включается через элементы ИЛИ 58 и И 48 импульсом опроса кодового жг та с выхода элемента И 63 пятым так товым импульсом. При совпадении на всех входах единичных сигналов на в:аходе элемента И-ИЛИ 67 формируется счетный импульс, который поступа ет на второй вход счетчика 9 и увел;- чивает адрес на единицу. Установ:-1вшийся адрес соответствует подклю Ч1гнию следующей по номеру ячейки в накопителе 12 и через дешифратор 16 выбирает следующий провод в кодовом . Проверка продолжается до последнего адреса и определяется ко|личеством перфокарт в блоке 10 ввода контрольных сигналов, В случае несоответствия кодов, поступающих в блок 15 сравнения, на его втором входе присутствует сигнал противоположного значенияя - нулевой уровень. При этом в формирователе 29 элемент И-ИЛИ 67 закрыт и открывается элемент И 64, подключенный через элемент НЕ 66. На выходе элемента И 64 по седьмому тактовому импульсу формируется сигнал ошибки. Сигнал ошибки поступает на один из входов в блок 11 регистрации ошибок, на другие входы которого поступают адрес ошибки с выхода счетчика 9 и код чисел с первого выхода блока 15 сравнения. По сигналу конца печати, который поступает с выхода блока 11 регистрации ошибок, включается триггер 36 в формирователе 29, который запрещает повторное прохождение импульса сигнала ошибки и дает разрешение на прохождение счетного импульса через элемент И-ИЛИ 67. Счетный импульс поступает на второй вход счетчика 9 - адрес увеличивается на единицу -и цикл работы продолжается. (Перфокарта несет адресную информацию только на первой строке )., Для повторных проверок кодового жгута (после исправления ошибок) переключают, работу- устройства в режим повышенного быстродействия, при котором контрольные числа вводятся в блок 15 сравнения через элемент ИИЛИ 8 и в накопитель 12. Режим работы устройства задается включением соответствующего переключателя в блоке 1, и через регистр 23 режима работы в формирователе вклю- чается пятая шина 72. Проверка начинается нажатием соответствующей клавиши в блоке 1, при этом импульс с выхода формирователя 22 одиночных импульсов поступает на один из входов формирователя 29 и через шину 35 обращения к накопителю и элемент ИЛИ 56 включает триггер 39, который разрешает прохождение через элемент И 62 четвертого тактового импульса, формирующего сигнал обращения к накопителю 12. Далее через элементы И 46 и ИЛИ 57 включается триггер 40, разрешающий формирование элементом И 63 по пятому тактовому импульсу сигнал опроса кодового жгута и включение триггера 41 через элементы И 49 и ИЛИ 58. Триггер 41 разрешает формирование импульсов счета элементом И-ИЛИ 67 или ошибки элементом И 64. После формирования импульса счета через элементы И 45 и ИЛИ 56 включается триггер 39 и цикл повторяется. Работа продолжается до заданного адреса в счетчике 9.

Если проверка начинается не с первого адреса, заданного счетчиком 9 при его установке в нулевое состояние сигналом сброса, то адрес начала проверки задается клавиатуре 21 и через регистр 24 адреса и элемент И-ИЛИ 6 вводится в счетчик 9 I При проверке кодового жгута в режиме сравнения с эталонным блоком постоянной памяти, т.е. ПЗУ. который имеет идентичную числовую программу с контролируемым блоком, с регистра 23 режима работы на формирователь 29 поступает сигнал, устанавливающий единичный уровень на шине 69 и на первых входах элементов И 47, 48 и 55. Включение режима осуществляется включением соответствующего переключателя в клавиатуре 21.

Проверка начинаетсяот импульса с выхода формирователя 22 одинйчных импульсов, который поступает на оди из входов формирователя 29 и через шину 35 обращения-к ПЗУ на первый вход элемента ИЛИ 59, который включает триггер 42. Триггер 42 разрешает прохождение десятого тактового импульса, который поступает на один из входов элемента И 65. С выхода элемента И 65 формирователя 29 импульс поступает на один из входов формирователя 13 управляющих сигналов. При поступлении импульсов на его другой вход включается триг--. гер 82, к единичному выходу которог подключены элементы И 78 - 80, на другие входы которых поступают тактовые импульсы.

Девятый тактовый импульс включает триггер 83, разрешающий прохождение десятого тактового импульса через элемент И 81.

Выход элемента И 81 является одним из выходов формирователя 13 управляющих сигналов, импульс с выхода которого устанавливает первый триггер 82 в нулевое состояние и запрещает вторичное формирование импульсов элементами И 78 - 80, Триггер 83 устанавливается в нулевое сотояние постояннойействующим первым тактовым импульсом.

Если для построения временной диаграммы одного из контролируемых блоков требуется иметь импульсы длительностью больше одного такта, то такие импульсы формируются триггерами регистра 77,. которые включаются и выключаются соответствующими импульсами с выхода элементов И 78 80,

Группа выходов триггеров регистра 77, элементов И 78 и 81 является другим выходом формирователя 13 управляющих сигналов.

На каждое поступление на один из входов формирователя 13 с выхода

формирователя 29 осуществляется формирование одного цикла временной диаграммы.

Последним импульсом в цикле является импульс, сформированный по десятому тактовому импульсу элементом И 81 формирователя 13 управляющих сигналов, который с одното из выходов поступает на один из входов формирователя 29, и элементами И 47,

0 50 и 51 выбирается необходимый режим работы устройства.

Импульс с шины 69 через элементы И 47 и ИЛИ 57 вк.тючает триггер 40, разрешающий формирование элементом И 63 по пятому тактовому им5пульсу импульса опроса кодового жгута и включение триггера 41 для формирования импульса счета, после прохождения которого включается триггер 42, разрешающий прохождение де0сятого тактового импульса через элемент И 65 для включения формирователя 13 управляющих сигналов, и рабочий цикл устройства повторяется. Работа блока 15 сравнения и форми5рования импульсов счета в этом режиме не отличается от режимов проверки по контрольной информации накопителя 12 или проверки по перфокартам.

Режим проверки двух блоков по0стоянной памяти задается соответствующим переключателем клавиатуры 21, которая включает соответствующий триггер в регистре 23 режимов работы, сигнал с выхода которого поступа5ет на соответствующий вход формирователя 29 и подключает шину 68.

Проверка начинается от импульса, поступающего на соответствующий вход формирователя 29 по шине 34 об0ращения к ПЗУ и на первый вход элемента ИЛИ 59, включающего триггер 42.

Формирователь 29 формирует только импульсы счета адреса элементом И-ИЛИ 67 (или ошибок - при несовпадении кодовых чисел в двух блоках ) и импульс обращения к ф.ормироватёлю 13 управляющих сигналов элементом И 65.

Количество циклов, отрабатываемое устройством, равно количеству .за0данных адресов в счетчике 9 и соответствует количеству ячеек в проверяемьрс блоках.

За базовый объект принято устройство СКП-М - стенд контроля памяти. На СКП осуществляются проверки сравниванием числовой информации, считанной с контролируемого блока,, с контрольной информацией, размещенной на перфокарте или в блоке one- ратирной памяти (ОЗУ).

Недостатком CKrt-M яв 1яется то, что основныь5 режимом работы устройства является режим сравнения по перфокартам. Режим имеет низкое быстродействие контроля, так как блок

ввода контрольных сигналов поэволя5т производить считывание несколь. перфокарт в секунду, Кроме того . |5лок имеет невысокую надежность, гак как его основу составляет элект эомеханический считыватель с ограниченным ресурсом работы.

Наличие в СКП блока ОЗУ не позволяет полностью устранить его недос аток потому, что скорость проверки ограничена быстродействием блока ОЗУ и остается необходимость разработки рабочих программ, изготовления пер(юкарт и реперфорирования перфокарт, так как их ресурсработы составляет 30-40 циклов ввода.

Введение в устройство предлагаеfi/Hx блоков позволяет обеспечить проЕврку блоков памяти сравнением двух сдновременно работающих блоков и проверку кодовых жгутов по эталонному блоку памяти, что в свою очередь позволяет производить проверку ПЗУ

в режиме, блиэкоги к реальной работе и повысить быстродействие устройства примерно в 3 раза.

Кроме того, устройство имеет режимы проверок по контрольным перфокартам и Информации, хранящейся в блоках ОЗУ, -что сохраняет высокую достоверность контроля.

Проверка двух одновременно блоков увеличивает производительность примерно в 2 раза. Снижены затраты на контроль ПЗУ, так как отпадает необходимость программирования и изготовленик перфокарт, что очень существенно для производства большо серии.

Экономический эффект достигается тем,- что обслуживающий персонал при проверке методом сравнения может быть более низкой квалификации. Прелагаемая экономия от внедрения одного предлагаемого устройства составляет порядка 30 тыс. руб, в год.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU886059A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-11-23—Публикация

1983-04-29—Подача