ключа и первым входом седьмого клю- ча Bl-opoft выход синхронизатора соединен с пятым входом блока памяти, вторым входом седьмого ключа и вторым входом пятого ключа, выход которого соединен с вторым входом третьего счетчика, выходы шестого

и седьмого ключей соединены с входами второго элемента ИЛИ, выход которого соединен с входом второго счетчика, шестой вход блока памяти и второй вход шестого ключа объединены и подключены к второму выходу формирователя существенных отсчетов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи измерительной информации | 1982 |

|

SU1062753A1 |

| Адаптивное устройство для сбора и обработки информации | 1976 |

|

SU595725A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ И ОЦЕНКИ ИХ ПЕРИОДА | 1990 |

|

RU2033617C1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для передачи телеметрической информации | 1981 |

|

SU1005147A2 |

| Устройство для передачи телеизмерений с адаптивной коммутацией | 1984 |

|

SU1267459A1 |

| Адаптивная многоканальная системапЕРЕдАчи дАННыХ | 1979 |

|

SU815935A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| Телеметрическое устройство | 1979 |

|

SU858061A1 |

УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ, содержащее синхронизатор, первый выход которого соединен с первым входом коммутатора, вторые входы которого соединены с входами устройства, выход коммутатора соединен с первым входом формирователя существенных отсчетов, первый выход которого соединен с первым входом блока буферной памяти второй выход, формирователя существенных отсчетов соединен непосредственно с входбм формирователя импульсов записи и первым управляющим входом переключателя адреса и через первый счетчик с первым входом блока чычитания и первым информационным входом переключателя адреса, выход которого соединен с вторым входом блока буферной памяти, второй счетчик, выход которого соединен с вторым входом блока вычитания и вторым информационным входом переключателя адреса, второй выход синхронизатора соединен с вторым управляющим входом пе.реключателя адреса и входом формирователя импульсов считывания, выход которого соединен с первьви входом формирователя кадра, выход которого соединен с выходом устрой- ства, отличающееся тем, что, с целью повышения информацион,ной гибкости, в него введены блок памяти, регистр адреса и инфоЕяиации, третий счетчик, элементы ИЛИ, элемент ИЛИ-НЕ, ключи, инвертор, .элементы задержки и шина управления, выход блока буферной памяти соединен с первым входом первого ключа и информационным входом регистра адреса и информации, адресный и информационный выходы которого соединены с первым и вторым входами блока памяти, выход которого соединен с первым входом второго ключа, выходил первого и второго ключей, соединены с входами первого элемента ИЛИ, выход которого соединен с вторым входом формирователя кадра, выход формирователя импульсов.записи соединен с первым входом второго элемента ИЛИ, управляющим входом регистра адреса и информации (Л и через первый элемент .задержки с третьим входом блока буферной памяти , выход формирователя импульсов считывания соединен с третьим о входом блока памяти и вторым входом е второго элемента ИЛИ выход которого соединен с четвертым входом блока буферной памяти, первый и второй выходы блока вычитания соединены с первыми входами соответственно третьего и четвертого ключей, выход . IS9 четвертого ключа соединен с вторым СО входом формирователя существенных отсчетов, второй вход Объединен с первым входом элемента ИЛИ-НЕ и подг ключен к шине управления, выход элемента ИЛИ-НЕ соединен с вторым входом третьего ключа, выход которого соединен с первым входом третьего . счетчика, первый выход которого соединен с, четвертым входом блока памяти, второй выход третьего счетчика соединен непосредственно с первыми входами пятого и шестого ключей и вторым входом второго ключа, через второй элемент задержки с вто- рым входом элемента ИЛИ-НЕ и через инвертор с вторым входом первого

Изобретение Относится к измерительной информационной технике и может быть использовано в измерительных информационных системах с сокращением избыточности информации.

Известно устройство для передачи информации, содержащее синхронизатор, решак|щий блок, включающие блоки управления записью и считывани ем, блок вычитания, блок накопителя буферной памяти. Устройство производит сокращение избыточности и выделяет существенные сигналы, по которым можно с требуемой точностью восстановить измеряемые процессы и передат| их с дополнительной служебной информацией на приемную сторону 11.

Однако в указанном устройстве не обеспечивается равенство средней частоты записи слов с существенны7 ми сигналами и частоты считывания. Не обеспечивается также точного восстановления измеряемых процессов в режиме ускоренного воспроиэведенкя в промежутки времени от момента на чала цикла считывания до появления первого существенного сигнала рассматриваемого датчика. Последний недостаток делает практически невозможным применение устройства в режиме ускоренного воспроизведения.

Наиболее близким к предлаг11емому является устройство для передачи информации, содержащее синхронизатор, первый выход.которого подключен к первому входу коммутатора, вторые входы которого являются входами устройства, а выхбд соединен с первым входом решающего блока, первый выход которого подключен к первому входу блока накопителя буферной памяти, а второй выход соединен со входом включающе.го блока управления записью, со входом формирователя импульсов запиЬи и с первым входом переключателя адреса, выход ко- . торого подключен ко второму входу блока накопителя буферной памяти, а второй вход соединен с выходом включающего блока управления записью и с пёрвым входом блока вычитаНИН, второй вход которого подключен к выходу включающего блока управления считыванием и к третьему входу переключателя адреса, четвертый вход которого соединен со вторым выходом синхронизатора и со входом формирователя импульсов считывания, выход которого подключен к первому входу блока формирования выходного кода, выход которого является выходом устройства.

В описанном устройстве устанавливается код максимально возможной ошибки, обеспечивающий среднюю частоту записи слов с существенными ;сигналами,равной частоте считыва ния, устанавливаемой синхронизатором C2J

Однако область применения данного устройства является узкой. Оно не может обеспечить ускоренной выдачи запомненной информации с частотой, существенно превышающей частоту записи, так как максимально возможная частота считывания равна частоте переключения коммутатора. Между тем режим ускоренного воспроиведения необходим для ряда объектов измерения, в которых сокращение избыточности необходимо для сокращения времени сеанса свдзи, во время каждого из которых необходимо надежно принять всю накопленного между сеансами связи инфррмацию (и. даже возможно принять несколько раз).

Цель изобретения - расширение области припенения устройства за счет обеспечения возможности функциони|рования его в режиме ускоренного воспроизведения.

Поставленная цель достигается тем, что в устройство для передачи информации, содержащее синхронизатор, первый выход которого соединен с первым входом коммутатора, вторые входы которого соединены с входами устройства, выход коммутатора соединен с первым входом формирователя существенных отсчетов, первый выход которого соединен с первым входом блока буферной памяти, второй выход форгдарователя существенных отсчетов соединен непосредственно с входом

ормирователя импульсов записи и первым управляющим входом переключателя адреса и через первый счётик с первым входом блока вычитания и первым информационным входом переключателя адреса, выход которого Соединен с вторым входом блока буферной памяти, второй счетчик, выход которого соединен с вторым входом блока вычитания и вторым нформационным входом переключателя адреса, второй выход синхронизатора соединен с вторым управляющим входом переключателя адреса и вхо- ом формирователя импульсов считывания, выход которого соединен с первым входом формирователя кадра, выходКоторого соединен с выходом устройства, введены блок памяти, регистр адреса и информации, третий счетчик, элементы ИЛИ, элемент ИЛИЛИ-НЕ, ключи, инвертор, элементы задержки и шина управления, выход блока буферной памяти соединён с первым входом первого ключа и информационным входом регистра адреса и . информации, адресный и информационный выходы которого соединены с первым и вторым входами блока памяти, выход которого соединен с первым входом второго ключа, выходу первого. и второго ключей соединены с входами Первого элемента ИЛИ, выход которого соединен с вторым вхЬдомформирователя кадра,.выход формирователя импульсов записи соединен с первым входом второго элемента ИЛИ, управ-ляющим входом регистра адреса и информации и через первый элемент задержки с третьим входом блока буферной .памяти, выход формирователя импульсов считывания соединен с третьим входом блока памяти и вторым входом второго элемента ИЛИ,:выход которого соединен с четвертым входом блока буферной памяти, .первый и второй выходы блока вычитания соединены с первыми входами соответственно третьего и четвертого ключей, выход четвертого ключа соединен с вторым вхоом формирователя существенных отсетов, второй вход объединен с первым входом элемента ИЛИ-НЕ и подклюен к шине управления, выход элемента ИЛИ-НЕ соединен с вторым входом третьего ключа, выход которого соединен с первым входом третьего счетчика, первый выход которого соединен с четвертым входом блока памяти, второй выход третьего счетчика соединен непосредственно с первыми входами пятого и шестого ключей и вторым входом второго ключа, через второй элемент задержки с вторым входом элемента ИЛИ-НЕ и через инвертор с вторым входом первого ключа и первым входом, седьмого ключа, второй выход синхрониза тора соединен с пятым входом

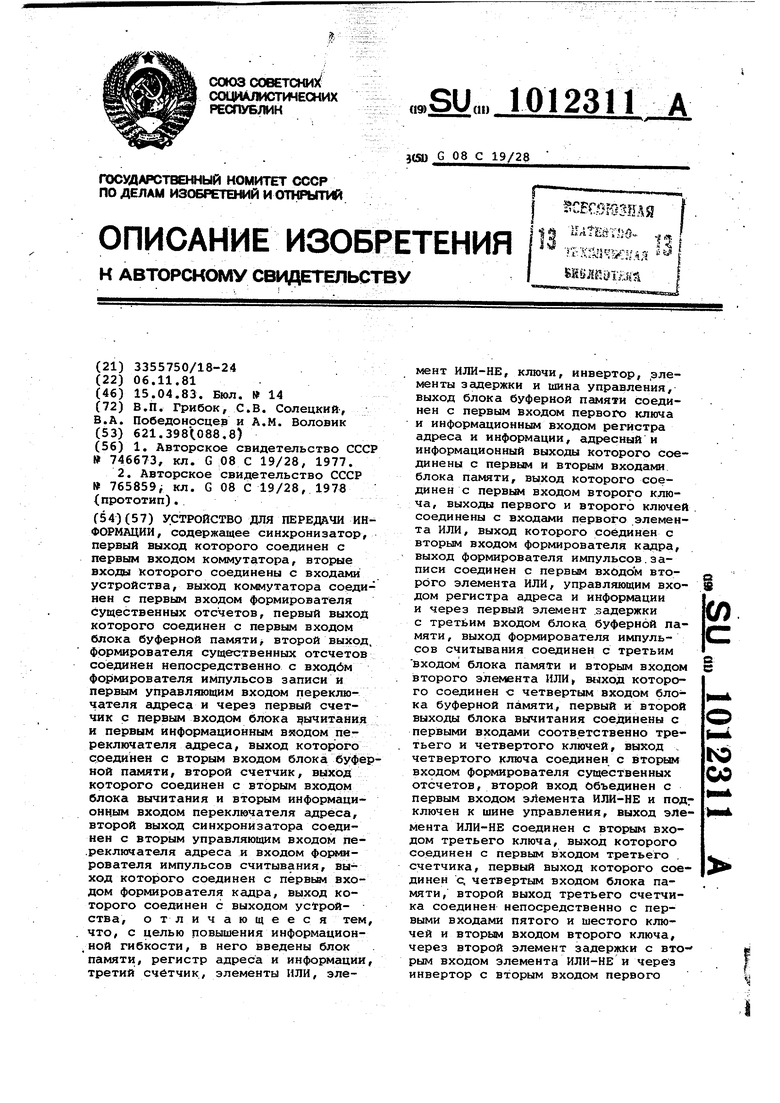

блока памяти , вторым входом седьмого ключа и вторым входом пятого ключа, . выход которого Соединен с вторым входом третьего счетчика, выходы шестого и седьмого ключей соединены с входами второго элемента ИЛИ, выход .которого соединен с входом второго счетчика, ше.стой вход блока памяти и второй вход шестого ключа объединены и подключены к в.торому выхот0ДУ формирователя существенных отсчетов . На чертеже представлена стуктурная схема предлагаемого устройства для передачи информации.

Устройство содержит шину 1 управления, ключ 2, элемент ИЛИ-НЕ 3, ключ 4, коммутатор 5,. синхронизатор 6, формирователь 7 существенных отсчетов, блок 8 буферной пг1мяти, первый счетчик 9 (включающий блок управления записью), переключатель 10 адреса, формирователь 11 импульсов записи, элемент ИЛИ 12, регистр 13 адреса и информации, элёмен.т 14 задержки, блок 15 памяти, элемент 16.

5 задержки, счетчик 17, ключи 18, 19,и 20, инвертор} 21, ключи 22 и 23, элемент ИЛИ 24, счетчик 25 (включающий блок управления считыванием, формирователь 26 импульсов считыва0ния, формирователь 27 кадра, элемент ИЛИ 28 и блок 29 вычи-уания.

1

Схема формирователя 7 существенных отсчетов определяется методом

5 выделения существенных отсчетов. В простейшем случае выделения сущест- . венных отсчетов по способу предсказания нулевого порядка формирователь 7 включает (на чертеже не показаны) приемный регистр, на который посту0пает код величины сигнала соответствующего датчика из коммутатора, блок оперативной памяти, в котором хранятся коды существенных :игналов для каждого датчика, и вычитатель, на

5 входы которого поступают значения кода величины сигнала датчика и код величины существенного сигнала из ячейки оперативной памяти, адрес которой, определяется номером датчи0ка, Вычитатель находит величину модуля разности и сравнивает ее с до-, пустимой, хранящейся в специальном регистре, входящим та-кже в формирователь 7, Если модуль разности боль5ше допустимой величины, выделяется импульс, по которому в ячейку оперативной памяти с номером датчика записывается код величины сигнала. Первым выходом формирователя 7 яв0ляется выход параллельного кода из приемного регистра, а вторым выходом - выход вычитателя, на котором . формируется импульс для изменения

содержимого яч.ейки оперативной памяти. Кроме входа, на который посту пает код величины сигнала и номера датчика, формирователь 7 имеет вход на который поступает код- допустимой величины максимальной ошибки и сигнал требования на ее замену в указанном выше специальном регистре. При поступлении такого сигнгша иа первом выходе формирователя формируется код величины допустимой максимальной ошибки, снабженный осо бым (например нулевым) номером дат чика, а на втором выходе появляется импульс требования на запись. Коммутатор 5 включает (на чертеж не показаны), например, счетчик до величины общего числа датчиков, высокоточные аналоговые переключатели упрсшляемые сигналами счетчика и вы деляющие сигнал датчика, имеющего номер, сформированный в счетчике, аналого-цифровой преобразователь, определяющий код величины сигнала датчика. На выходе коммутатора 5 формируется код номера датчика (из счетчика) и код величины сигнала да чика (из аналого-цифрового преобразователя) . Ключи, например, выполнены, как комплекс элементов И, один из входо которых подключен к общей шине, на которую заведен вход управления. На второй вход элементов И заводятся коммутируекые коды. Формирователь 27 кг1дра выполнен, например, в виде сдвигового регистра. На первый вход его подается импульс, по которому в сдвиговый регистр заносится кол, сформированный на втором входе формирователя 27. 8дальнейшем при сдвиге этот код пре образуется из параллельного в последовательный и подается в передатчик из которого сигналы следуют непосред ственно в канал связи. Элемент 14 задержки заднего фронта выполнен , например, на одновибраторе. Элемент 16 задержки выполнен например, в виде комбинации двух одновибраторов: одиндля сдвига заднего фронта входного импульса, другой дпя сдвига переднего фронта. Переключатель 10 гщреса выполнен, например, в виде ряда схем , у которых к одному из элементов И подключен определенный разряд счетчика 9и сигнсш-управления подключением адреса записи, а ко второму элементу И подклю,чен тот же разряд счетчика 25 и сигнал управления подключением адреса считывания. Формироват-ели. 11 и 26 импульсов записи и считывания вьшолнены, напри мер, в виде одновибратора, уменьшающего длительность входного импульса. Одновибратор подключен к дифференцирующему элементу, выделяющему сигнал, синфазйый заднему фронту ,сигнала одновибратора. Дифференцирующий элемент подключен к усилителю-формирователю, который выдает импульс с параметрами, необходимыми для обеспечения нормальной работы устройства. Блок 8 буферной памяти выполнен .на стандартных микросхемах К565РУЗА (аналогичным таким микросхемам, как К565РУ1А или К507РУ1А/. Блок 15 памяти представляет собой накопитель памяти на стандартных миксхемах, снабженный переключателем адреса и усилителями-формирователями импульсов. Остальные элементы и блоки, входя,щие в состав устройства, являются стандартными и не требуют особых пояснений. Работа устройства для передачи информации происходит в двух основных режимах. Первый из режимов - обеспечиваю.щий среднюю частоту записи слов с существенными сигналами равной частоте считывания - характеризуется наличием потенциала логической 1 на шине 1 управления. Этот потенциёш открывает ключ 2 и попадает на вход элемента ИЛИ-НЕ 3. Таким образом, на выходе этого элемента формируется потенцисш логического О, закрывающий ключ 4. Рассмотрим процесс записи слов с существенными отсчётами. Входными сигналами устройства являются выходные сигналы датчиков, из которых для обеспечения временной привязки параметров хотя бы один должен быть датчиком времени (таймером). Сигналы с датчиков..поступают на коммутатор 5, переключающий по сигналам с общего синхронизатора 6. После каждого переключения сигналы с очередного датчи.ка поступёиот на формирователь 7, где происходит выделение существенных отсчетов, по которым на приемной стороне можно с требуемой точностью, восстановись все измеряемое процессы. Кгикдый из существенных отсчетоб снабжен в формирователе 7 кодом номера датчика. Для обеспечения временной привязки используются сигналы таймера, записываемые с определенными группами существенных отсчетов (или даже с каждьм существенным отсчетом). Таким образом, на выходе формирователя 7 образуются слова с существенными отсчетами, поступающие на информационные входы блока 8 буферной памяти. Если формирователь 7 выделил слово с существенным отсчетом, на втором (служебном) выходе формирователе 7 формируется импульс требования на запись, который подается на вход счетЧика 9, содержимое которого после поступления импульса требования на . запись увеличивается на единицу. Импульс требования на запись, кроме того, поступает на первый управляющий вход переключателя 10 адреса, в результате чего на его выходе, подключенном к адрес ному входу блока 8. буферной памяти, формируется код адреса записи из счетчика 9. Далее импульс требования на запись подается ца формирователь 11 импульсов записи, в котором из переднего фронта поступившеего импульса, задержанного на определенное время, формируется узкий (по сравнению с импульсом требования на запись) импульс, поступающий на элемент ИЛИ 12 и на управляющий вход регистра 13. После прохождения элемента ИЛИ 12 импульс по падает на вход управления считывани блока 8 буферной памяти. -При этом происходит считывание существенного отсчёта из блока В буферной памяти в регистр 13 адреса и информации (в регистр адреса подается номер да чика, а все остальные разряды слова , с существенными сигналами поступают в регистр информации). Выходы разря дов регистра 13 адреса и информации подключены соответственно с адресным входам записи и информационным входом блока 15 памяти. Из импульса требования на запись и сигнала, выданного формирователем 11 импульсов записи, формируется управляющий сиг нал, по котброму код из регистра 13 запоминается в ячейке блока 15 памяти, код номера которой также хранится в регистре 13. Импульс с выхода формирователя 11 импульсов записи проходит элемент задержки на время, достаточное для считав§ния в регистр 13, и поступает на вход управления записью блока 8 буферной памяти. При этом происходит запись слова в ячейку блока 8 буфер ной Пс1мяти, номер которой определяется содержимым счетчика 9, т. е. имен но в ту ячейку, предыдущее содержимое которой было считано непосредственно перед этим в регистр 13. Таким образом, в ячейки с последовательно увеличивающимися нсмерами Слока 8 буферной памяти заносятс все слова с существенными отсчета,ми. Перед каждой записью содержимое ячейки, в которую должно быть записано слово с существенным отсчетом, переносится в блок 15 памятй. При этом запись производится .в йчейку с номером, соответствующим номеру датчика, а сам этот номер может не запомниться. Т.е. для каждбго датчика в блоке 15 памяти запо минается код последнего из сущестпаяных отсчетов, исчезнувшего из блока 8 буферной памяти вследствие обновления содержимого соответствующей ячейки. Для анализа процесса считывания из блока памяти и формирователя выходного кода необходимо установить, какие из ключей открываются в режиме, обеспечивающем среднюю частоту записи существенных отсчетов, равной частоте считывання, а таКже в чем состоят условия открывания каждого ключа. В рассматриваемом режиме ключ 2, как указывалось выше, открыт, а ключ 4 - закрыт. Выход ключа 4 под ключей ко входу иачгшьной установки счетчика 17, т.е. поскольку ключ 4 закрыт, на счетчик 17 начальная установка не подается. У счетчика 17 имеется два выхода: на nefpBO из них формируется двоичный код числа импульсов, подаваеьшх на его счетный вход, а на втором (управляющем) выходе сигнёш логического О появляется после поступления на счетный вход количества .импульсов, равного числу датчиков. При любом другом содержимом на этом выходе оказывается сигнал логической 1. Такой выход у счетчика 17организуется очевидным образом: достаточно соединить .прямые (или инверсные) выходы его триггеров через наборное поле (или кроссиррвку) со входами элемента И-НЕ. Тогда на выходе этого элемента будет присутствовать необходимый управляющий сигнал. Этот второй (управляющий) сигнал подключается, в частности, ко входам управления ключей 18, 19 и 20 и ко входу инвертора 21, выходной сигнал которого подается на входы управления-ключей 22 и 23. Через ключ 18 на счетный вход счетчика 17 поступают импульсы синхронизатора б, частота которых определяет частоту считывания существенных отсчетов для передачи на приемную сторону. Каково бы не было первоначальное (после включения) содержимое счетчика 17, после поступления определенного числа импульсов, синхронизатора б в счетчике 17 установится содержимое, при которрм на его вто:ром выходе появляется запрещающий нулевой потенцигш. После этого ключ 18закрывается, и дгшьнейшее прохождение импульсов на счетный вход счетчика 17 прекращается, а на его втором выходе оказывается неизменный нулевой потенциал. Этот потенциал закрывает ключи 18, 19 и 29 и вызы вает формирование единичного раэрешакйпего сигнала на выходе инвертора 21. Этот сигнал, в свою очередь, открывает ключи 22 и 23. Таким образом,, в рабочем состоянии дЛя режима, обеспечиваквдего равенство средней частоты записи су-« щественных отсчетов с частотой счит вания-, открыты ключи 2, 22 и 23 и закрыты ключи 4,18, 19 и 20. Рассмотрим процесс считывания в данном режиме. Как указывалось выше, синхрониза тор 6 выдает с постоянной частотой импульсы требования на считывание. Каждый такой импульс поступает на вход блока 15 памяти, где по нему производится выбор .ячейки для считы вания, код номера которой определяется содержимым счетчика 17 (в данном режиме - постоянным). Импульс требования на считывание происходит через открытый ключ 22 и элемент ИЛИ 24 на вход счета счетчика 25, после чего содержимое этого счетчик увеличивается на единицу. Кроме того, импульс требования на считывани подается на второй управляющий вход переключателя 10 адреса, в результа те- чего на адресный вход блока 8 бу ферной памяти подается содержимое счетчика 25. Также импульс требовакия на считывание поступает на вход формирователя 26 импульсов считывания, в котором из переднего фронта импульса, задержанного на определен ное время, формируется узкий импуль подаваемый на блок 8 буферной памяти, на блок 15 памяти и на формирователь выходного кода. При этом на выходах блоков 8 и 15 памяти появляется код считанных слов. Однако, поскольку ключ 19 закрыт, а ключ 23 открыт, на информационный вход формирователя 27 кадра всегда поступает существенный отсчет с выхода бло ка 8 буферной памяти. Это слово пер дается в формирователь 27 через отк рытый ключ 23 и через элемент ИЛИ 2 Таким образом, стробом с выхода формирователя 26 импульсов считывания в формирователь 27 выходного кода переписывается слойо с существенным отсчетом, хранящееся в ячейке блока 8 буферной памяти по адресу, код ко торого установлен счетчиком 25. Из формирователя 27. кадра информация поступает непосредственно в канал связи с приемной стороной. Содержимое счетчиков 9 и 25 поступает в блок 29 вычитания, где опре деляется число запомненных и не считанных из блока 8 буферной памяти слов, содержащих существенные отсчеты. В зависимости от этого числа, называемого заполнением, блок 29 вычитания устанавливает допустимое значение максимально возможной ошибки для формирователя 7. Это значение передаемся в .формирователь 7 через открытый ключ 2. При этом при заполнении, равном общему числу ячеек блока 8 буферной памяти, значение максимально возможной ошибки должно определяться областью допустимых значений паре метров, а при нулевом заполнении (для обеспечения принудительной существенности) максимально возможная ошибка должна быть отрицательной величи-, ной. При изменениях величины максимально возможной ошибки в устройстве может быть предусмотрено формирование специального служебного слова, содержащего код величины максимально возможной ошибки, полученный в результате данного изменения. Такое служебное слово запоминается в блоках 8 и 15 полностью- аналогично слову с существенными отсчетами. На приемной стороне служебные слова можHQ выделить по их адресной части, которая не должна совпадать ни с одним из номеров датчиков. Блок 29 вычитания имеет второй выход, на котором формируется высокий управляющий сигнал при равенстве содержимого счетчиков 9 и 25, однако этот сигнал попадает только на закрытый ключ 4 и не может оказать воздействия на работу устройства. Таким образом, в рассматриваемом режиме всегда устанавливается (и может передаваться) код максимально возможной ошибки, обеспечивающий равенство средней частоты записи слов с существенными отсчетами и частоты считывания, устанавливае-. мой синхронизатором 6. Однако, кроме данного режима, предлагаемое устройство д;1Я передачи информации может обеспечивать ускоренную выдачу запомненной информации с частотой, существенно превышающей частоту -записи. Режим ускоренной выдачи запомненной информации характеризуется тем, что час-, тота импульсов, вьц аваемая синхронизатором б на переключение коммутатора 5, оказывается меньше, чем частота импульсов на другом выходе синхронизатора 6 (частота импульсов требования на считывание). В указанном режиме на шине 1 управления присутствует потенциал логического О, Он может формироваться по внешней команде или же с помощью какого-либо дополнительного блока сравнения частот на выходах синхронизатора 6. Потенциал логического О на шине 1 закрывает ключ 2, что означает постоянство максимально возможной ошибки, устанавливаемой для формирователя 7. Таким образом, в данном режиме не могут формироваться служебные слова, свидетельствующие об изменении величины максимальной ошибки. Поэтому в режиме ускоренной выдачи процесс записи слов с. существенными отсчетами полностью аналогичен рассмотренному выше процессу в режиме, обеспечивающем равенство частот записи и считывания, а значит повторно процесс записи не рассматривается, В результате этого процесса в ячейки блока 8 буферной памяти заносятся : все существенные отсчеты, причем при каждой новой записи обновляется содержимое той ячейки, в которую запись существенныхотсчетов производилась раньше всего. Перед каждой записью содержикюе ячейки, в которую должна быть проведена указанная запись, считывается и переносится в блок 15 памяти в ячейку, соответствующую номеру датчика, выдавшего существенный сигнал (код номера датчика при этом может не за поминаться), т.е. для каяодого датчика в блоке 15 памяти запоминается код последнего из существенных отсчетов, изчезнувшего из блока 8 буферной памяти вследствие обновления содержимого соответствующей ячейки.

Рассмотрение процесса считывания из блоков памяти и формирователя выходного кода начинают с момента начала цикла считывания, когда в реэхльтате ускоренного (по сравнению с записью), считывания содержимое счетчика 25 .делается равным содержимому счетчика 9. При этом на выходе блока 29 вычитания, подключенном через открытый ключ 4 ко входу начальной установки счетчика 17, формируется сигнал, обнуляющий счетчик 17. При этом на первом выходе счетчика 17 появляется код, определяющий номер первого из датчиков (например таймера), а. на втором выходе формируется единичный разрешающий сигнал открывающий ключи 18, 19 и 20 и формирующий на выходе инвертора 21 нулевой потенциал. Этот потенциал с выхода инвертора 21 закрывает ключи 22 и 23. Сформированный на втором выходе счетчика 17 передний фронт положительного импульса вызывает появление единичного сигнала на выходе элемента 14 задержки заднего фронта, который может быть выполнен, например, по схеме одновибратора. Положительный сигнал с выхода элемента 14 формирует нулевой потенциал на выходе элемента ИЛИ-НЕ 3. Данный нулевой потенциал закрывает ключ 4.

Синхронизатор 6 выдает с постоянной частотой импульсы требования на считывание. Каждый такой импульс поступает на вход блока 15 памяти, где по нему производится выбор ячейки для считывания, код номера которой определяется содержимым счетчика 17. На счетный вход счетчика 17 через ключ 18 поступают импульсы требования на считывание, т.е. в бло-ке 15 памяти последовательно (с каждым импульсом требования на считывание) осуществляется опрос содержи.мого его ячеек. Как уже указывалось, в ячейках блока 15 памяти запоминается для каждого из датчиков код последнего из существенных сигнгшов

исчезнувших из блока В буферной па-, мяти вследствие обновления содержимого соответствующей ячейки. Импульег требования на считывание поступает на вход формирователя 26 импульсов

5 считывания, в котором из переднего фронта импульса, задержанного на определенное время, формируется узкий импульс, подаваемой на блок 8 буферной памяти, на блок 15 памяти и на

0 формирователь 27 кадра. .При этом на выходах блоков 8 и 15 памяти появля. ется код считанных слов (дополненный для блока 15 кодом адреса считывания, отражающий номер соответствующего датчика). Однако, поскольку ключ 19 открыт, а ключ 23 закрыт, на информационный вход формирователя 27 кадра поступает слово, считанное из блока 15, дополненное кодом

Q адреса считывания (номером датчика). Это слово передается в формирователь 27 через открытый ключ 19 и через элемент ИЛИ 28.

Таким образом, после начала цик, ла считывания ь форлшрователь 27 кадра (и из него S канал связи JEртя передачи на приемную сторону) передаются значения кодов последнего из существенных отсчетов для каждого из датчиков, исчезнувшие из блока 8 буферной памяти вследствие обновления содержимого его ячеек. По этим данным на приемной стороне можно обеспечить восстановление участка процессов изменения выходных сигналов

5 датчиков, начиная с момента начала цикла считывания вплоть до появления первого из существенныхотсчетов каждого датчика.

п Если до окончания передачи содержимого блока 15 памяти произойдет формирование и запоминание нового . существенного отсчета (или несколь-. ких сигналов), то импульс требования на запись вызовет не только увеличение на единицу содержимого счетчика 9, но и, пройдя через открытый ключ 20 и элемент ИЛИ 24, увеличит на единицу содержимое счетчика 25. .Поскольку ключ 22 при этом закрыт,

0 и другим путем содержимое счетчика 25 измениться не может, на вторрм выходе блока 29 вычитания сохраняется высокий потенциал, свидетельст-. вующий о равенстве содержимого счетчиков 9 и 25. Однако этот потенциал

подается на закрытый ключ 4 и не вляет ни работу устройства.

После окончания передачи содержимого блока 15 памяти на втором выходе счетчика 17 устанавливается сигнал логического О, закрывающий ключи 18, 19 и 20 и устанавливающий единичный потенциал на выходе инвертора 21. Потенциал с выхода инвертора 21 открывает ключи 22 и 23. Как уже указывалось (при анализе режима, обеспечивающего равенство средней частоты записи слов с существенными сигналами с частотой счтывания), при таком наборе открытых и закрытых ключевых схем происходит считывание в формирователь 27 кадра для передачи на приемную стррону содержимого ячеек с последовательно увеличивающимися номерами блока 8 буферной памяти, а номера этих ячеек определяются содержимым счетчика 25.

Дпя .того, чтобы сразу по окончании передачи содержимого блока 15 памяти не произошло начальной установки счетчика 17, Элемент 14 задержки заднего фронта обеспечивает (через элемент ИЛИ-НЕ 3) запирание ключа 4 до момента прохожжения нескольких импульсов требования на считывание. Поэтому до окончания нового цикла считывания не может

возникнуть равенства содержимого счетчиков 9 и 25.

Таким Образом, по окончании передачи содержимого блока 15 памяти в формирователь 27 кадра поступают слова с существенными отсчетами из блока 8 буферной памяти, начиная с тех, которые раньше всего были записаны в этот блок (т.е. для каждого из датчиков по окончании передачи содержимого блока 15 на приемную сторону будет передан существенный сигнал непосредственно следующий за тем, который был передан на блок 15). Такая организация передачи позволяет обеспечить восстано.вление с необходимой точностью всех процессов, измеряеьшх датчиками в течение всего промежутка времени, соответствующего циклу считывания.

Применение предлагаемого изобретения позволяет повысить информационную гибкость устройства, что

позволяет существенно расширить область применения устройства для передачи информации за счет обеспеения возможности функционирования в режиме ускоренного воспроизведения. При этом полностью исключаются ограничения на задаваемую частоту импульсов требования на считывание.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для передачи данных с сокращением избыточности информации | 1978 |

|

SU746673A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для передачи информации | 1978 |

|

SU765859A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1983-04-15—Публикация

1981-11-06—Подача