СО СП

а 00

2.Устройство поп. 1,отличающееся тем, что дешифратор вьтолнен в виде параллельных сумматоров или вычитателей, первые группы входов которых включены параллельно,

а вторые гр,зт1пы входов подключены к шинам кодовых чисел..

3.Устройство по п. 1, отличающееся тем, что блок управле1 ня содержит триггер, одновибратор, вход которого соединен с единичным

входом триггера, и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с выходом одновибратора, второй вход - с инверсным выходом триггера, причем единичный и нулевой входы триггера являются соответственно первым и вторым входами, а прямой выход триггера,- выход одновибратора и выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ являются соответственно первым, вторым и третьим выходами блока управления,

| название | год | авторы | номер документа |

|---|---|---|---|

| Емкостно-электронный преобразователь перемещения | 1989 |

|

SU1721434A1 |

| Устройство для измерения скорости телеграфирования | 1982 |

|

SU1059691A1 |

| Цифровой частотный детектор | 1983 |

|

SU1193765A1 |

| Устройство для цифрового измерения частоты | 1989 |

|

SU1666965A2 |

| Устройство для контроля амплитудно-частотных характеристик четырехполюсников | 1980 |

|

SU946003A1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1983 |

|

SU1129625A1 |

| Устройство для многоканальной магнитной записи и воспроизведения сигналов с коррекцией временных искажений | 1990 |

|

SU1777178A1 |

| Устройство для распознавания образов | 1986 |

|

SU1361589A1 |

| Устройство для измерения скорости телеграфирования | 1974 |

|

SU547042A1 |

| Матричный осциллограф | 1981 |

|

SU1018021A1 |

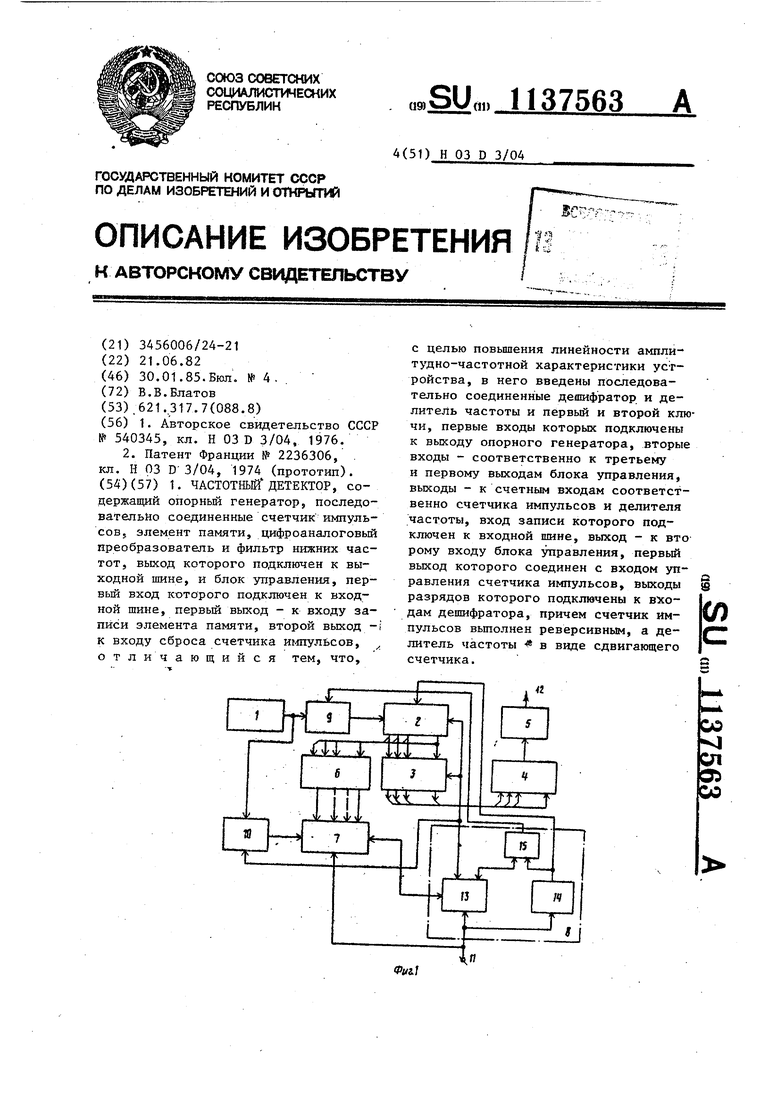

1. ЧАСТОТНЫЙДЕТЕКТОР, содержащий опорньй генератор, последовательно соединенные счетчик импульcoBf элемент памяти, цифроаналоговый преобразователь и фильтр нижних частот, выход которого подключен к выходной шине, и блок управления, первый вход которого подключен к входной шине, первый выход - к входу записи элемента памяти, второй выход -i к входу сброса счетчика импульсов, отличающийся тем, что. с целью повьшения линейности амплитудно-частотной характеристики устройства, в него введены последовательно соединенные дешифратор и делитель частоты и первый и второй ключи, первые входы которых подключены к выходу опорного генератора, вторые входы - соответственно к третьему и первому выходам блока управления, выходы - к счетным входам соответственно счетчика импульсов и делителя частоты, вход записи которого подключен к входной шине, выход - к вто рому входу блока управления, первый выход которого соединен с входом управления счетчика импульсов, выходы разрядов которого подключены к входам дешифратора, причем счетчик импульсов выполнен реверсивным, а делитель частоты в виде сдвигающего счетчика.

Изобретение относится к радиотехнике и может использоваться для демодуляции частотно-манипулированных и частотно-модулированных сигналов.

Известен многочастотньй дискрими : натор частотно-модулированных сигналов j содержа дай опорньй генератор; .счетчик нмпульсов, дешифратор, формирователь, преобразователь, элементы И и ИЛИ

.OAHaKo известное устройство харак теризуется нелинейностью амплитудночастотной характеристики.

Наиболее близким по технической сущности к изобретению является йемо-{5 дулдтор (детектор.) частотно-модули- рованных сигналов, содержащий блок управления и счетчик, первые входы ; . которых подключены к источнику тактовых импульсов (опорному генератору), 20 Первый и.второй выходы блока управления соед,инены с входами счетчика . а второй вход подключен к выходу усилителя-ограничителя (формирователя), соединенного с входной ииной. Выход- 25 ные шикы счетчика подключены к входам запоминающего устройства (элемент памяти)э вход записи которого соединен с третьим вьпсодом блока упра.вле- ния„ Выходы элемента памяти поДклю- зо чены к входам цифроаналогового преобразователя (ЦАП)f выход которого через фильтр нижних частот (ФНЧ) соединей с выходной шиной 2 ,

Недостаток данного устройства заг ключается в большой нелинейности a fflлитyднo чacтoтнoй характеристики, обусловленной тем, что выходной сигнал пропорционален не частоте входного сигнала, а периоду его повторения.

Цель изобретения - повьшение линейности амплитудно-частотной характеристики устройства.

Поставленная.цель достигается тем, что в частотный детектор, содержащий опорный генераторэ последовательно соединенные счетчик импульсов, элемент памяти, цифроаналоговый преобразователь и фильтр нижних частот, выход которого подключен к выходной шине, и блок управления первый вход которого подключен к входной шине, первый выход - к входу записи элемента памяти, второй выход - к входу сброса счетчика импульсов, введены последовательно соединенные дешифратор- и делитель частоты и первый и второй ключи, первые входы которых подключены к выходу опорного генератора, вторые входы - соответственно к третьему и первому выходам блока управления, выходы - к счетным входам соответственно счетчика импульсов Я делителя частоты, вход записи которого подключен к .входной шине, выход - к второму входу блока управления, первый выход которого соединен с входом управления счетчика импульсов, выходы разрядов которого подключены к входам дешифратора, причем счетчик импульсов выполнен реверсивным, а делитель частоты - в виде сдвигающего счетчика.

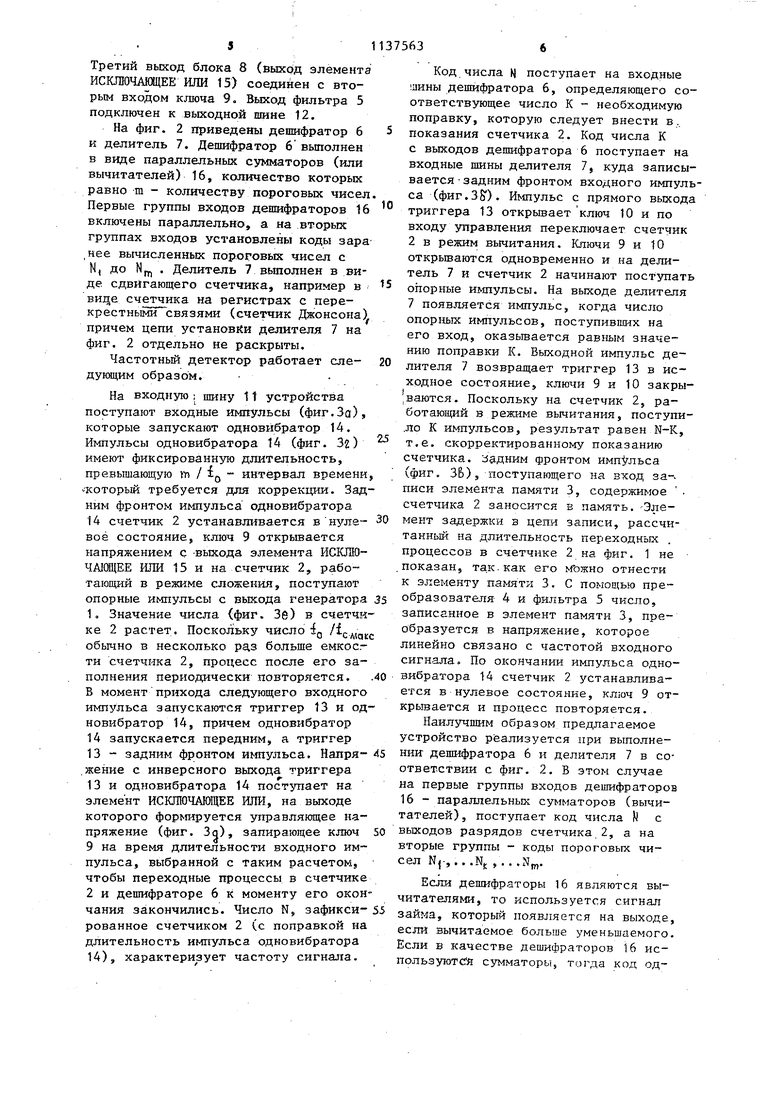

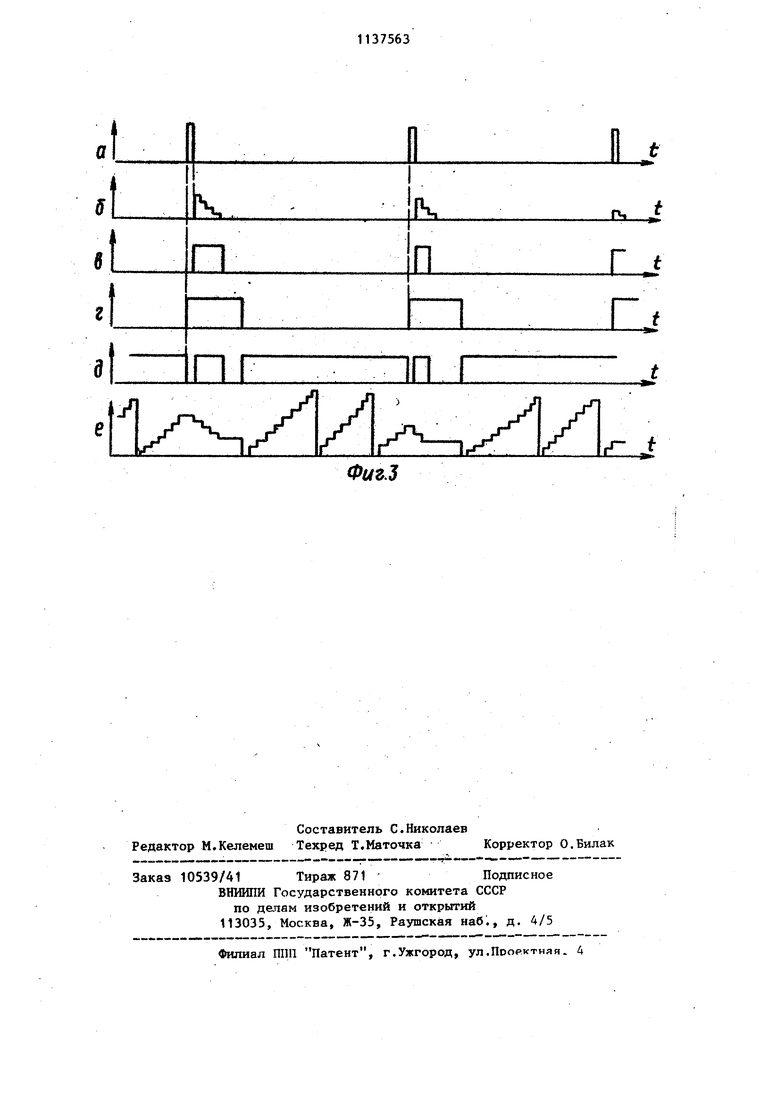

При этом дешифратор выполнен в виде параллельных сум.маторов или вычитателей, первые группы входов которых включены параллельно, а вторые группы входов подключены к пшнам ко дов кодовых чисел. Кроме того, блок управления соде жит триггер, .одновибратор, вход которого соединен с единичным входом триггера, и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ первьй вход которого соединен с выходом одновибратора, второй вход с инверсным Ёыходом триггера, приче единичный и нулевой входы триггера являются соответственно первым и вт рым входами, апрямой выход триггер выход одновибратора и выход элемент ИСКЛЮЧАЮЩЕЕ ИЛИ являются соответствеино первьм, вторым и третьим выхо дами блока управления. Принцип работы, устройства основа на измерении периода сигнала. Кажды период сигнала заполняется имйул са ми опорной частоты, следующими с ча тотой f., которая значительно выше частоты сигнала f . При этом счетчи регистрирует число j, io До io-ii .&iU, смаке смакс - - смакс - максимальная частота сиг .смаке с Это число однозначно связано с по казанием частотного детектора. Разложим N по степеням if и, ограничив шись первыми двумя члeнa ш, запишем о-Н2 к, °KJ/S, , ,.,, г, Отсюда следует, что показания уст ройства не пропорциональны ii. причем второе слагаемое характеризует -отклонение 8К показаний детектора от линейной зависимости. Отклонение равное погрешности дискретносЕи, получается при значении Af I -4 fcMoicc /fT. При находим-Л f,. макс/ о наибольшее значение ;макс определяется соотношением смахсгде.л,1смакс- смин)смин минимальная частота сиг кала. 634 Таким образом, при ut-zL&t счетчик регистрирует число Н , которое отклоняется от линейного- значения на К. Поэтому для коррекции нелинейности характеристики детектора предварительно вычисляются все пороговые числа от К, до Кm , а затем после каждого цикла измерения в зависимости от величины полученного числа N в счет- i чик вносится поправка. Если N tN Nпоказания счетчика уменьшаются на единицу, при уменьшаются на К и т.д. В результате, отклонение выходного напряжения частотного детектора от линейного закона не превьшает погрешности дискретности. На фиг. 1 представлена структурная электрическая схема частотного детектора; на фиг. 2 - вариант вьптолнения дешифратора и делителя частоты; на фиг. 3 - временные диаграммы, иллюстрируюпще работу устройства. Частотный детектор содержит опорньй генератор 1, последовательно соединенные реверсивный счетчик 2 импульсов , элемент памяти 3, цифроаналогоБый преобразователь 4 и фильтр нижних частот 5, последовательно соединенные дешифратор 6 и делитель 7 частоты (с переменным коэффициентом деления), а также, блок 8 управления, первый и второй ключи 9 и 10, входную 11, и выходную 12 шины. Блок управлен11Я 8 содержит триггер 13, одновибратор 14, вход которого соединен с единичным входом триггера 13, и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 15. Первый вход последнего соединен с выходом одновибратора 14, вто- рой вход - с иньерсным выходом триггера 13. Первые входы ключей 9 и 10 подключены к вькоду генератора 1, выходы к счетным входам соответственно счетчика 2 и делителя 7. Входы дешифратора 6 подключены к выходам разрядов счетчика 2. Вход записи делителя 7 первый вход блока 8 (единичный ход триггера 13) подключены к входной шине 11. Второй вход блока 8 (нуевой вход триггера 13) подключен к ыходу делителя 7. Первый выход блоа 8 (прямой выход триггера 13) соеинен с входом записи элемента памяи 3, входом управления счетчика 2 BTopbiM входом ключа 10. Второй выод блока 8 -(выход одновибратора 1.4) оединен с входом сброса счетчика 2.

Третий выход блока 8 (выход элемента ИСКгаОЧАЩЕЕ ИЛИ 15) соединен с вторым входом ключа 9, Выход фильтра 5 подключен к выходной шине 12.

На фиг. 2 приведены дешифратор 6 и делитель 7. Дешифратор 6 вьтолнен в виде параллельных сумматоров (или вычитателей) 16, капичество которых равно m - количеству пороговых чисел Первые группы входов дешифраторов 16 включены параллельно, а на вторых группах входов установлены коды зара ,нее вычисленных пороговых чисел с N, до N . Делитель 7 вьшолнен в виде сдвигающего счетчика, например в счетч11ка на регистрах с перекрестными связями (счетчик Джонсона) причем цепи установки делителя 7 на фиг. 2 отдельно не раскрыты.

Частотный детектор работает еледующим образом.

На входную ; шину 11 устройства поступают входные импульсы (фиг.Зд), которые запускают одновйбратор 14. Импульсы одновибратора 14 (фиг. Зг) имеют фиксированнздо длительность, превышающую m / ig - интервал времени, который требуется для коррекции. Задним фронтом импульса одновибратора 14 счетчик 2 устанавливается внулевое состояние, ключ 9 открывается напряжением с -выхода элемента ИСКЛЮЧАКЩЕЕ ИЛИ 15 и на счетчик 2, работающий в режиме сложения, поступают опорные импульсы с выхода генератора 1. Значение числа (фиг. Зб) в счетчике 2 растет. Поскольку число i обычно в несколько рдз больше емкос.ти счетчика 2, процесс после его заполнения периодически повторяется.

8момент прихода следующего входного импульса запускаются триггер 13 и одновйбратор 14, причем одновйбратор

14 запускается передним, а триггер 13 - задним фронтом импульса. Напря.женив с инверсного выхода триггера 13 и одновибратора 14 поступает на элемент ИСЮТЮЧАЮЩЕЕ ИЛИ, на выходе которого формируется управляющее напряжение (фиг. 3q), запирающее ключ

9на время длительности входного импульса, выбранной с таким расчетом, чтобы переходные процессы в счетчике 2 и дешифраторе 6 к моменту его окончания закончились. Число N, зафиксированное счетчиком 2 (с поправкой на длительность импульса одновибратора 14), характеризует частоту сигнала.

Код числа Ц поступает на входные шины дешифратора 6, определяющего соответствующее число К - необходимую поправку, которую следует внести в.. показания счетчика 2, Код числа К с выходов дешифратора 6 поступает на входные шины делителя 7, куда записывается задним фронтом входного импулса (фиг.ЗЮ, Импульс с прямого выход триггера 13 открывает ключ 10 и по входу управления переключает счетчик 2 в режим вычитания. Ключи 9 и tO открьшаются одновременно и на делитель 7 и счетчик 2 начинают поступат опорные импульсы. На выходе делителя 7 появляется импульс, когда число опорных импульсов, поступивших на его вход, оказьгоается равным значению поправки К. Выходной импульс делителя 7 возвращает триггер 13 в исходное состояние, ключи 9 и 10 закры.ваются. Поскольку на счетчик 2, работающий в режиме вычитания, поступило К импульсов, результат равен N-K, т.е. скорректированному показанию счетчика, задним фронтом (фиг. ЗЬ), поступающего на вход за- писи элемента памяти 3, содержимое . счетчика 2 заносится в память, -Элемент задержки в цепи записи, рассчитанный на длительность переходных , процессов в счетчике 2 на фиг, 1 не .показан, та.к.как его foжнo отнести к элементу памяти 3. С помощью преобразователя- 4 и фильтра 5 число, записанное в элемент памяти 3, преобразуется в напряжение, которое линейно связано с частотой входного сигнала. По окончании импульса одновибратора 14 счетчик 2 устанавливается в нулевое состояние, ключ 9 открывается и процесс повторяется.

Наилучшим образом предлагаемое устройство р1еализуется при выполнении дешифратора 6 и делителя 7 в соответствии с фиг, 2, В этом случае на первые группы входов дешифраторов 16 - параллельных сумматоров (вычитателей) , поступает код числа ) с выходов разрядов счетчика 2, а на вторые группы - коды пороговых чисел N|-,...Nj /. ..N.

Если дешифраторы 16 являются вычитателями, то используется сигнал , который появляется на выходе, если вычитаемое больше уменьшаемого. Если в качестве дешифраторов 16 используютсй сумматоры, тогда код одного из чисел на входах каждого сумматора 16 представляется в инверсном виде (например число И снимается с инверсных выходов счетчика 2), при этом используется сигнал переноса, квторый появляется при . В результате на выходах сумматоров (вычитателей) 16, для которых число N больше пороговых чисел, появляются,, например, логические единицы, а на выходах дешифратора 16, для которых N меньше или равно пороговым значениям, появляются логические нули. Следовательно, число К равно количеству логических единиц на выходах сумматоров (вычитателей). Код числа К подается на установочные шины делителя 7, в качестве которого используется сдвигакяций счетчик. Установка первого (девого) регистра производится дешифратором 16 ) следующего - с Nm- и -Я- Последний (выходной) регистр устанавливаI ГГГТ

ФаюиввЯ

ется дешифратором с , .В результате число К записьгеается в сдвигающий счетчик в виде нулевого состояния К правых регистров, остальные

регистры устанавливаются в единичное состояние. При поступлении на вход сдвигающего счетчика опорных импульсов единицы начинают .сдвигаться вправо. Через К импульсов первая единица

поступает на выход сдвигающего регист ра, т.е. делителя 7, я используется как выходной сигнал дпя установки триггера 13 в начальное состояние. Таким образом, выполнение часготного детектора по. изобретению существенно повышает линейность его амплитудно-частотной характеристики, которая практически в результате кор.рекции не отлич;ается от линейной,

поскольку отклонение от линейного закона не превышает погрешности . дискретности, т.е. одной ступеньки (шага) преобразователя 4.

Н от счевпикаг

у у у у

j

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Многочастотный дискриминатор частотно-модулированных сигналов | 1976 |

|

SU540345A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| УСТРОЙСТВО ДЛЯ АЭРАЦИИ ЖИДКОСТИ | 2003 |

|

RU2236306C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-01-30—Публикация

1982-06-21—Подача