2.Детектор по п.1, о т л и ч а ющ и и -с я тем, что блок управления выполнен в виде первого одновибратора, вход и выход которого подключены соответственно к первому входу

и второму выходу блока управления, элемента И, инверсный вход которого соединен с выходом первого одновибратора, прямой вход элемента И подключен к второму входу блока управления, первый выход которого соединен с выходом элемента И, и второго одновибратора, вход и выход которого подключены соответственно к первому входу и третьему выходу блока управления .

3.Детектор по п.1, о т л ичающийся тем, что блок передачи кода выполнен в виде группы параллельных цепочек, каждая из которых содержит последовательно соединенные элемент ИЛИ и элемент И, причем первые входы всех элементов ИЛИ и все выходы элементов И образуют соответственно входные и выходные разрядные шины блока передачи кода, а все вторые входы элементов ИЛИ

и все вторые входы элементов И подключены соответственн-л к первому и второму управляющим входам блока передачи кода.

4, Детектор по п.1, отличающийся тем, что блок управления передачей выполнен в виде счетчика, цепь сброса и счетный вход которого подключены соответственно к цепи сброса и информационному входу блока управления передачей, первого RS-триггера, S-вход которого подключен к выходу счетчик элемента И, первый вход которого подключен, к прямому выходу первого RS-триггера и второму выходу блока управления передачей, и второго RS-триггера, S-вход которого соединен с выходом элемента И, а выход подключен к первому выходу блока управления передачей, при этом R-входы обоих RS-триггеров соединены с цепью сброса блока управления передачей, к информационному входу которого подключен второй вход элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Позиционный дискретный электропривод | 1985 |

|

SU1352474A1 |

| Частотный детектор | 1982 |

|

SU1137563A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СРЕДНЕКВАДРАТИЧЕСКОГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ | 1987 |

|

SU1438439A1 |

| Быстродействующий селективный измеритель амплитуды ВЧ-сигнала | 1990 |

|

SU1780029A1 |

| Программное временное устройство | 1988 |

|

SU1647517A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННЫМИ ЗАМКАМИ | 2001 |

|

RU2198276C1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1762280A2 |

| Цифровой регистратор | 1984 |

|

SU1164549A1 |

| ЦИФРОВОЙ ЧАСТОТОМЕР | 1996 |

|

RU2097774C1 |

1. ЦИФРОВОЙ ЧАСТОТНЫЙ ДЕТЕ ТОР, содержащий формирователь импульсов , блок управления, счетчик, опорный генератор и последовательно соединенные элемент памяти, цифроаналоговый преобразователь и фильтр нижних частот, выход которого является выходом устройства, вход которого соединен с входом формирователя импульсов, выход которого подключен к первому входу блока управления, второй вход которого соедине с выходом опорного генератора, первый и второй выходы блока управлени .. .., ... --(ЛЯ соединены соответственно со счетньм входом и цепью сброса счетчика, а третий выход блока управления соединен с цепью записи элемента памяти, отличающийся тем, что, с целью уменьшения погрешности измерения путем устранения неоднозначности показаний, в устройство введены блок передачи кода, входные разрядные шины которого соединены с соответствукядими выходными разрядными шинами счетчика, а выходные разрядные шины - с соответствующими входными разрядньми шинами элемента памяти, и блок управления передачей, первый и второй выхода 1 которого подключены соответственно к первому и второму управляющим входам блока передачи кода, при этом цепь сброса блока управления передачей соединена с вторым входом блока управления, а информационный вход блока управления передачей подключен к выходу старшего разряда счетчика.

Изобретение относится к области радиотехники и может использоваться для демодуляции частотно-модулированных и частотно-манипулированных сигналов.

Цельи изобретения является уменьшение погрешности измерения путем устранения неоднозначности показаний.

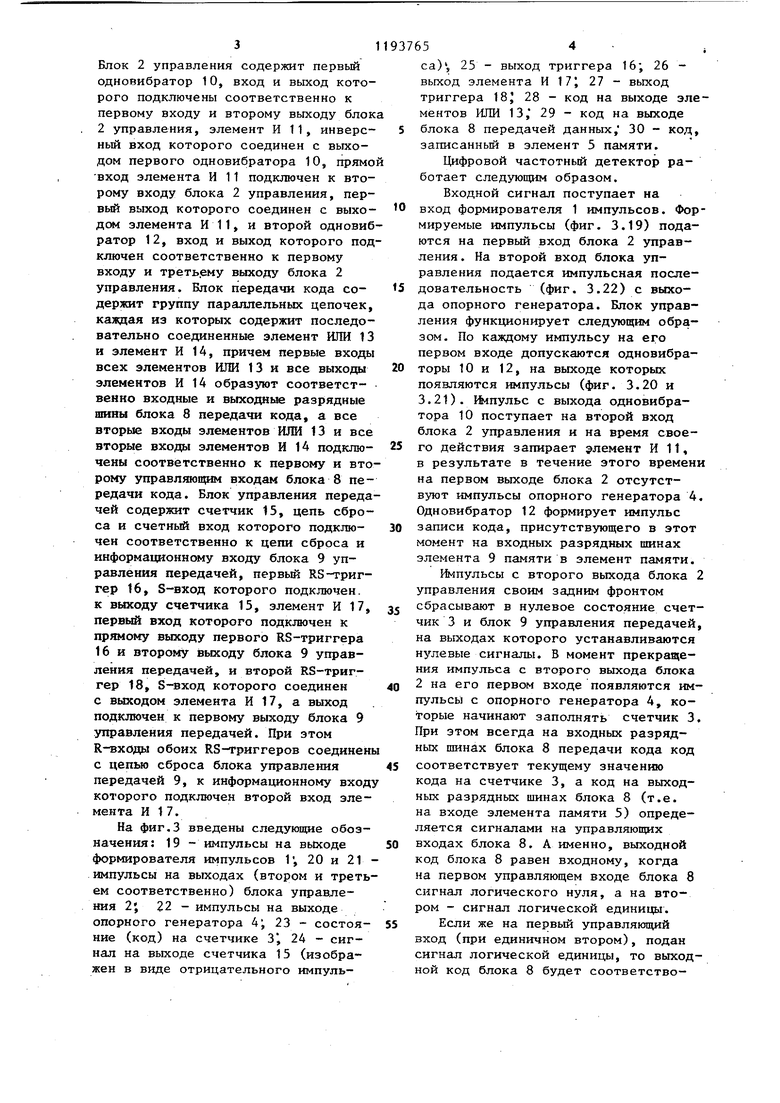

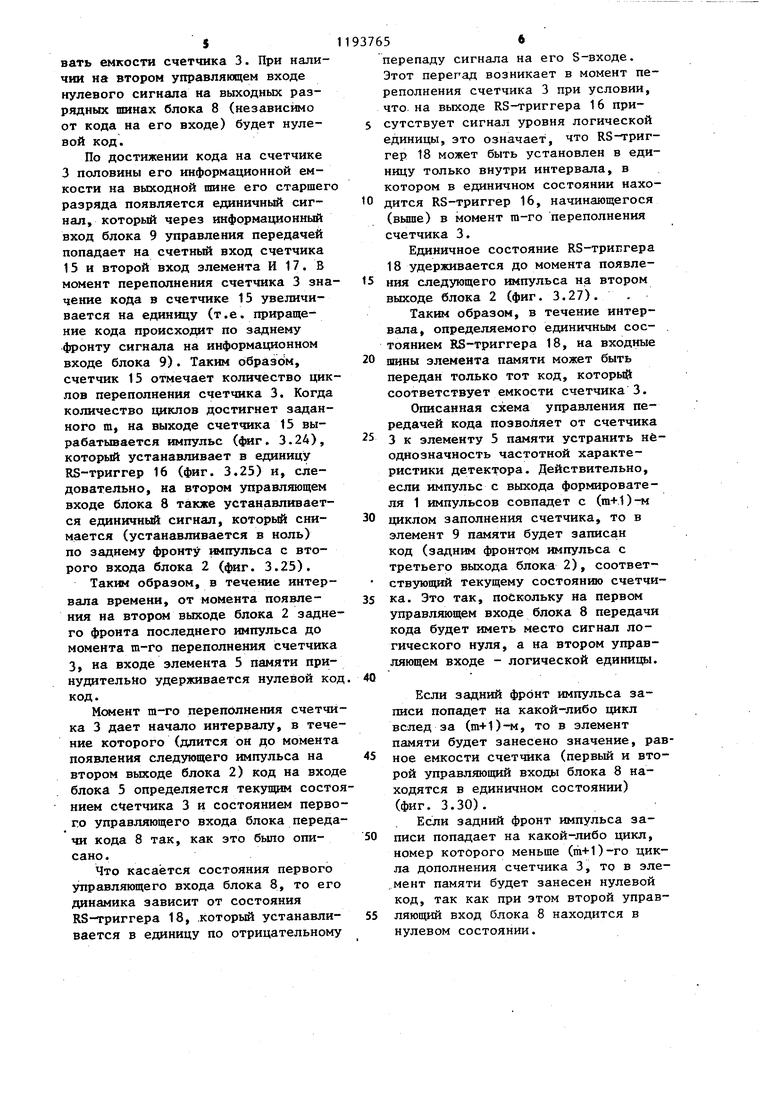

На фиг,1 представлена схема предлагаемого цифрового частотного детектора на фиг.2 - частотная характеристика детектора на фиг.З - временные, диаграммы работы блоков устройства.

Частотный детектор содержит формирователь 1 импульсов, блок 2 управления, счетчик 3, опорный генератор 4, последовательно соединенные элемент 5 памяти, цифроаналоговый преобразователь 6, фильтр 7 нижних частот, выход которого является выходом устройства, вход которого соединен с выходом формирователя 1 импульсов, выход которого подключен

к первому входу блока 2 управления, второй вход которого соединен с выходом опорного генератора 4, первый и второй выходы блока 2 управлен1«1 соединены соответственно со счетным входом и цепью сброса счетчика 3, а третий выход блока 2 управления соединен с цепью записи элемента 5 памяти, блок 8 передачи кода, входные разрядные шины которого соединены с соответствующими выходньки разрядными шинами счетчика 3, а выходаые разрядные шины с соответствующими входными разрядньЕми пшнами элемента 5 памяти,и

блок 9 управления передачей, первый и второй выходы которого подключены соответственно к первому и второму управляющим входам блока 8 передачи кода, при этом цепь сброса

блока управления передачей 9 соединена с вторым выходом блока 2 управления, а информационный вход блока 9 управления передачей подключен к выходу старшего разряда счетчика 3,

31

Блок 2 управления содержит первый одновибратор 10, вход и выход которого подключены соответственно к первому входу и второму выходу блока 2 управления, элемент И 11, инверсный вход которого соединен с выходом первого одновибратора 10, прямой ВХОД элемента И 11 подключен к второму входу блока 2 управления, первый выход которого соединен с выходом элемента И 11, и второй одновибратор 12, вход и выход которого подключен соответственно к первому входу и третьему выходу блока 2 управления. Блок передачи кода содержит группу параллельных цепочек, каждая из которых содержит последовательно соединенные элемент ИЛИ 13 и элемент И 14, причем первые входы всех элементов ИЛИ 13 и все выходы элементов И 14 образуют соответственно входные и выходные разрядные шины блока 8 передачи кода, а все вторые входы элементов ИЛИ 13 и все вторые входы элементов И 14 подключены соответственно к первому и второму управляюпщм входам блока 8 передачи кода. Блок управления передачей содержит счетчик 15, цепь сброса и счетный вход которого подключен соответственно к цепи сброса и информационному входу блока 9 управления передачей, первый RS-триггер 16, S-вход которого подключен, к выходу счетчика 15, элемент И 17, первый вход которого подклочен к прямому выходу первого RS-триггера 16 и второму выходу блока 9 управления передачей, и второй RS-триггер 18, S-вход которого соединен с выходом элемента И 17, а выход подключен к первому выходу блока 9 управления передачей. При этом обоих RS-триггеров соединены с цепью сброса блока управления передачей 9, к информационному входу которого подключен второй вход элемента И 1 7.

На фиг.З введены следующие обоэначения: 19 - импульсы на выходе формирователя импульсов 1, 20 и 21 импульсы на выходах (втором и третьем соответственно) блока управ1ления 2j 22 - импульсы на выходе опорного генератора 4j 23 - состояние (код) на счетчике 3, 24 - сигнал на выходе счетчика 15 (изображен в виде отрицательного импуль654 i

ca)j 25 - выход триггера 16; 26 - выход элемента И 17 27 - выход триггера 18J 28 - код на выходе элементов ИЛИ 13; 29 - код на выходе блока 8 передачей данных, 30 - код, записанный в элемент 5 памяти.

Цифровой частотный детектор работает следующим образом.

Входной сигнал поступает на

вход формирователя 1 импульсов. Формируемые импульсы (фиг. 3.19) подаются на первый вход блока 2 управления . На второй вход блока управления подается импульсная последовательность (фиг. 3.22) с выхода опорного генератора. Блок управления функционирует следующим образом. По каждому импульсу на его первом входе допускаются одновибраторы 10 и 12, на выходе которых появляются импульсы (фиг. 3.20 и 3.21). Шпульс с выхода одновибратора 10 поступает на второй вход блока 2 управления и на время своего действия запирает элемент И 11, в результате в течение этого времени на первом выходе блока 2 отсутствуют импульсы опорного генератора 4. Одновибратор 12 формирует импульс

записи кода, присутствующего в этот момент на входных разрядных шинах элемента 9 памяти в элемент памяти.

{ пульсы с второго выхода блока 2 управления своим задним фронтом

сбрасывают в нулевое состояние счетчик 3 и блок 9 управления передачей, на выходах которого устанавливаются нулевые сигналы. Б момент прекращения импульса с второго выхода блока

2 на его первом входе появляются импульсы с опорного генератора 4, которые начинают заполнять счетчик 3. При этом всегда на входных разрядных шинах блока 8 передачи кода код

соответствует текущему значению

кода на счетчике 3, а код на выходных разрядных шинах блока 8 (т.е. на входе элемента памяти 5) определяется сигналами на управляющих

входах блока 8. А именно, выходной код блока 8 равен входному, когда на первом управляющем входе блока 8 сигнал логического нуля, а на втором - сигнал логической единицы.

Если же на первый управляющий вход (при единичном втором), подан сигнал логической единицы, то выходной код блока 8 будет соответство-

S

вать емкости счетчика 3. При наличии на втором управляющем входе нулевого сигнала на выходных разР51ДНЫХ шинах блока 8 (независимо от кода на его входе) будет нулевой код.

По достижении кода на счетчике 3 половины его информационной емкости на выходной шине его старшего разряда появляется единичный сигнал, который через информационный вход блока 9 управления передачей попадает на счетный вход счетчика 15 и второй вход элемента И 17. В момент переполнения счетчика 3 значение кода в счетчике 15 увеличивается на единицу (т.е. приращение кода происходит по заднему фронту сигнала на информационном входе блока 9). Таким образом, счетчик 15 отмечает количество циклов переполнения счетчика 3. Когда количество 1щклов достигнет заданного т, на выходе счетчика 15 вырабатывается импульс (фиг. 3.24), который устанавливает в единицу RS-триггер 16 (фиг. 3.25) и, следовательно, на втором управляющем входе блока 8 также устанавливается единичный сигнал, который снимается (устанавливается в ноль) по заднему фронту импульса с второго входа блока 2 (фиг. 3.25).

Таким образом, в течение интервала времени, от момента появления на вторсм выходе блока 2 заднего фронта последнего импульса до момента т-го переполнения счетчика 3, на входе элемента 5 памяти принудительно удерживается нулевой код код.

т-го переполнения счетчика 3 дает начало интервалу, в течение которого (длится он до момента появления следующего импульса на втором выходе блока 2) код на вход блока 5 определяется текущим состонием счетчика 3 и состоянием первого управляющего входа блока передачи кода 8 так, как это было описано .

Что касается состояния первого управляющего входа блока 8, то его динамика зависит от состояния RS-триггера 18, .который устанавливается в единицу по отрицательному

937656

перепаду сигнала на его S-входе. Этот перегад возникает в момент переполнения счетчика 3 при условии, что на выходе RS-триггера 16 присутствует сигнал уровня логической единицы, это означает, что RS-триггер 18 может быть установлен в единицу только внутри интервала, в котором в единичном состоянии нахо-

10 дится RS-триггер 16, начинающегося (выше) в момент т-го переполнения счетчика 3.

Единичное состояние RS-трИЕгера 18 удерживается до момента появления следующего импульса на втором выходе блока 2 (фиг. 3.27). .

Таким образом, в течение интервала, определяемого единичным сое- . тоянием RS-триггера 18, на входные

20 шины элемента памяти может быть передан только тот код, который соответствует емкости счетчика 3.

Описанная схема управления передачей кода позволяет от счетчика

25 3 к элементу 5 памяти устранить неоднозначность частотной характеристики детектора. Действительно, если импульс с выхода формирователя 1 импульсов совпадет с (т+1)-м

30 циклом заполнения счетчика, то в элемент 9 памяти будет записан код (задним фронтом импульса с третьего выхода блока 2), соответствующий текущему состоянию счетчика. Это так, поскольку на первом управляющем входе блока 8 передачи кода будет иметь место сигнал логического нуля, а на втором управляющем входе - логической единицы.

Если задний фронт импульса записи попадет на какой-либо цикл вслед за (ш+1)-м, то в элемент памяти будет занесено значение, равное емкости счетчика (первый и второй управляющий входы блока 8 находятся в единичном состоянии) (фиг. 3.30).

Если задний фронт импульса записи попадает на какой-либо цикл, номер которого меньше (т+1)-го цикла дополнения счетчика 3, то в эле.мент памяти будет занесен нулевой код, так как при этом второй управляющий вход блока 8 находится в нулевом состоянии.

| Многочастотный дискриминатор частотно-модулированных сигналов | 1976 |

|

SU540345A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-11-23—Публикация

1983-04-25—Подача