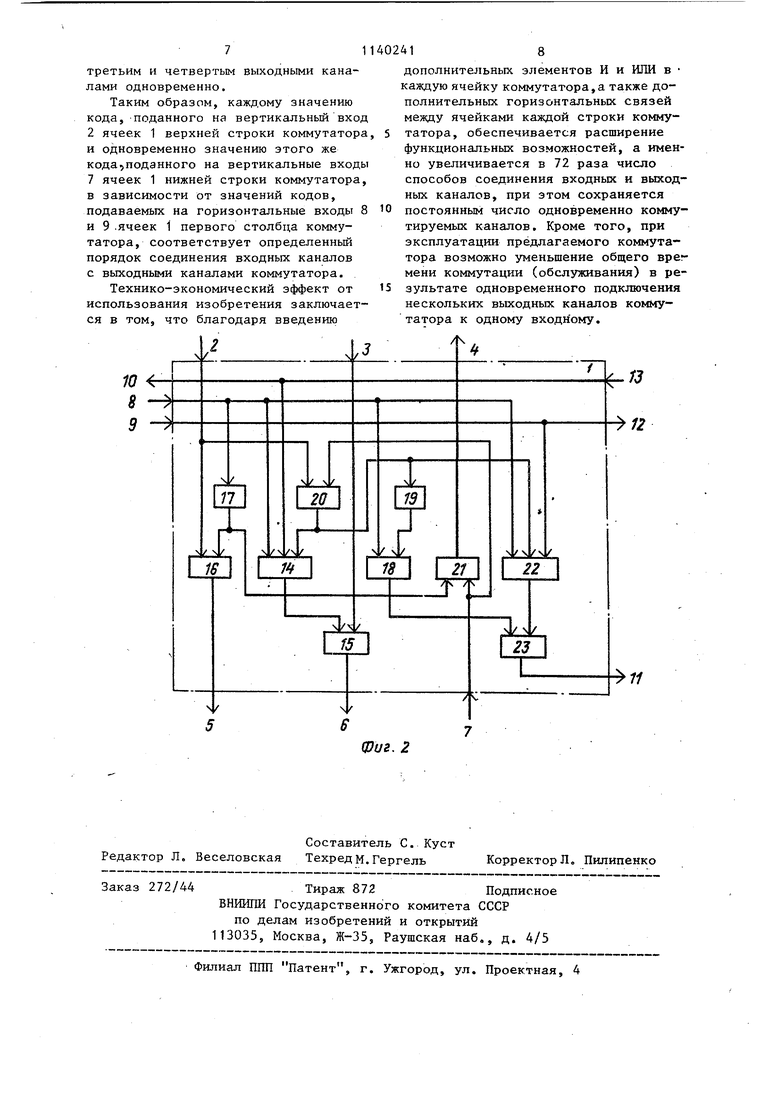

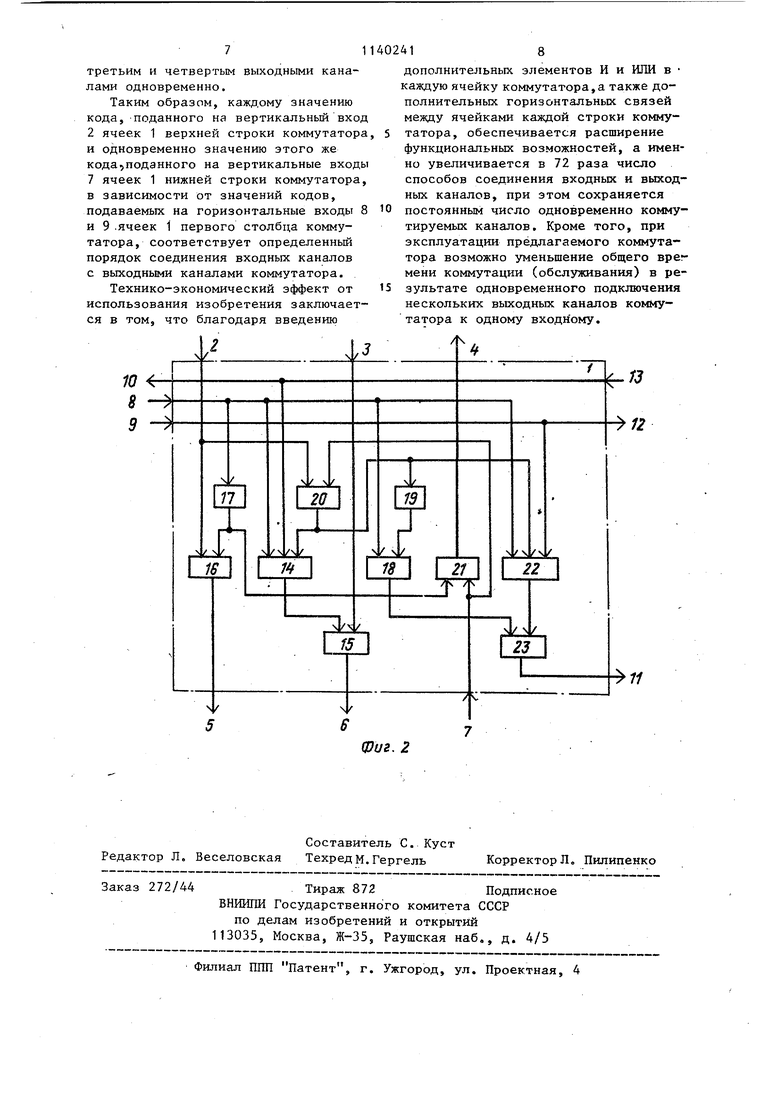

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для коммутадаи каналов ввода - вывода информации цифровых устройств. По основному авт. св. № 1.003336 извecтq коммутатор, сйдержащий идентичные ячейки, распрложенные в узлах двумерной решетки, каждая из которых содержит- элементы И, ИЛИ,НЕ причем в каждой ячейке ее горизонтальные входы соединены с входами первого элемента И, выход которого подключен к одному из входов первого элемента ИЛИ, другой вход которого соединен с вторым вертикальным входом ячейки, а выход - с вторьм вертикальным выходом ячейки, первьй вертикальный вход которой подключен к одному из входов второго элемента Н, другой вход которого через первый элемент НЕ соединен с первым горизон тальным входом ячейки и одним из входов четвертого элемента И, а выход - с первым вертикальным выходом ячейки, первый горизонтальный вход ячейки соединен с одним из входов третьего элемента И, другой вход которого через второй элемент НЕ подключен к третьему входу первого элемента И и выходу второго элемента ИЛИ, другой вход которого соединен с третьим вертикальным входом ячейки и подключен к другому входу четверто го элемента И, а выход - с третьим вертикальным выходом ячейки, причем первый, второй вертикальные входы и третий вертикальный выход ячейки с координатами (, ) соединены с первым, вторым вертикальными выходами и третьим вертикальным входом ячейки с координатами («,) +1) соответственно, первый, второй вертикальные выходы и третий вертикальный вход - с первым, вторым вертикальным входами и третьим вертикальным выходом ячейки с координатами (i,j -1) соответственно, первые горизонтальные вход и выход - с вторыми горизон тальными выходом и входом ячейки с координатами (l-1, ), а вторые гориз.онталькые вход и выход - с первым горизонтальным выходом и входом ячейки с координатами (i + 1,4 ) Dj Однако этот коммутатор имеет огра ничейные функциональные возможности так как не позволяет осуществлять работу одного входного канала на не111 сколько выходных одновременнб в различных комбинациях. Цель изобретения - расширение функциональных возможностей коммутатора. Поставленная цель достигается тем, что в коммутатор в кажр,ую из идентичных ячеек введены третий элемент ИЛИ и пятый элемент И, первый вход которого подключен к первому горизонтальному входу ячейки, второй вход - к выходу второго элемента ИЛИ, а третий вход является третьим горизонтальным входом ячейки и соединен с третьим горизонтальным выходом ячейдов третьего элемента ШШ, другой вход которого соединен с выходом третьего элемента И, а выход - с вторым горизонтальным выходом ячейки, причем третьи горизонтальные вход и выход ячейки с координатами (1.,j ) соединены с третьими горизонтальными выходом и входом ячеек с координатами (-1,j ) и (i + 1,j ) хсоответственно, На фиг. 1 представлена функциональная схема коммутатора; на фиг. 2 - структурная схема ячейки коммутатора. Коммутатор содержит ячейку 1, первый 2 и второй 3 вертикальные входы и третий вертикальный выход 4 которой с координатами (1,J ) соединены с первым 5 и вторым 6 вертикальными выходами и третьим вертикальным входом -7 ячейки 1 с координатами (l,j +1) соответственно, первый и второй вертикальные выходы 5 и 6 и третий вертикальный вход 7 с первым 2 и вторым 3 вертикальными входами и третьим вертикальным выходом 4 ячейки 1 с координатами (i, j -1) соответственно, первый 8 и третий 9 горизонтальные входы и . первый горизонтальный выход 10 - с вторым 11 и третьим 12 горизонтальными выходами и вторым горизонтальным входом 13 ячейки 1 с координатами (l-1,j ) соответственно, а второй 11 и третий .12 горизонтальные выходы и второй горизонтальный вход 13 - с первым 8 и третьим 9 горизонтальными входами и первьм горизонтальным выходом 10 ячейки 1 с координатами (i+1, j) соответственно. Ячейка 1 коммутатора содержит первый элемент 14 И, входы которого соединены с горизонтальными входами 8 и 13 ячейки 1, g выход - с одним из входов первого элемента 15 ИЛИ, другой вход которого подключен к вертикальному входу 3 ячейки 1, а выход - к вертикальному выходу 6 ячейки 1, вертикальный вход 2 которой подключен к одному из входов второго элемента 16 И, другой вход которого через первый элемент 17 НЕ соединен с горизонтальным входом 8 ячейки 1, а выход - с вертикальным выходом 5 ячейки 1, горизонтальный вход 8 ячейки 1 соединен с одним из входов третьего элемента 18 И, другой вход которого через второй элемент 19 НЕ подключен к третьему вхо ду первого элемента 14 И и вьгходу второго элемента 20 ИЛИ, один из входов которого соединен с вертикал ным входом 2 ячейки 1, а другой вход - с вертикальным входом 7 ячей ки 1 и одним из входов четвертого элемента 21 И, другой вход которого соединен с другим входом второго элемента 16 И, соединенного с входо первого элемента 17 НЕ, а выход - с вертикальным выходом 4 ячейки 1, горизонтальный вход 8 которой подкл чен к первому входу пятого элемента 22 И, второй вход которого соединен с выходом второго элемента 20 ИЛИ, третий вход является горизонтальным входом.9 ячейки 1 и соединен с горизонтальным выходом 12 ячейки 1, а выход подключен к одному из входов третьего элемента 23 ИЛИ, другой вход которого соединен с выходом третьего элемента. 18 И, а выход - с горизонтальным выходом 11 ячейки 1, входными каналами коммутатора являются горизонтальные входы 13 ячеек 1 правого столбца коммутатора, а вы ходными каналами - вертикальные выходы 6 ячеек 1 нижней строки коммутатора. Коммутатор работает следующим об разом. Пусть коммутатор содержит восемь входных и четьфе вькодных канала и требуется соединение второго вход ного канала с первым выходным каналом, третьего - с вторым, пятого с третьим, седьмого - с четвертым. На вертикальные входы 2 ячеек t верхней строки коммутатора подаются единичные логические уровни, а на вертикальные входы 3 этих же ячеек 1 и на вертикальные входы 7 ячеек 1 нижней строки коммутатора - нулевые логические уровни. На горизонтальные входы 9 ячеек 1 крайнего левого столбца коммутатора подаются нулевые логические уровни, а на горизонтальные входы 8 ячеек 1 этого же столбца подается код 01101010, причем единичные логические уровни подаются на горизонтальные входы 8 ячеек 1 тех строк коммутатора, соответствующие входные каналы которых требуется коммутировать. На горизонтальный ход 8 ячейки 1,лежащей на пересечении второй строки и первого столбца коммутатора,подается единичный логиеский уровень, следовательно, на ее вертикальном выходе 5 образуется нуле- , вой логический уровень.Начиная с указанной ячейки 1 нулевой логический уровень образуется на вертикальных выходах 5 всех расположенных ниже ячеек 1 первого столбца. Так как на горизонтальный вход 8 первой ячейки 1первого столбца подан нулевой логический уровень, то разрещается прохождение единичного логического уровня с вертикального входа 2 этой ячейки 1 на вертикальный вход 2второй ячейки 1 первого столбца коммутатора. Таким образом, только в единственной ячейке 1 первого столбца имеет место одновременная подача единичных логических уровней на входы 2 и 8, поэтому именно на этой ячейке 1 осзтцествляется соединение второй строки с первым столбцом коммутатора, т.е„ второй входной канал соединяется с первым в,ькодным каналом. На горизонтальном выходе 11 этой же ячейки 1 образуется нулевой логический уровень, в результате чего на горизонтальные входы 8 ячеек 1 смежного правого (второго) столбца коммутатора подается код 00101010 с погашенной первой единицей. Аналогично получают соединение третьего входного канала с вторым выходным каналом, пятого - с третьим и седьмого - с четвертым. Наличие нулевых логических уровйей на горизонтальных входах 9 всех ячеек 1 коммутатора не. нарушает логику работы коммутатора. Если на вертикальные входы 2 и 3 ячеек 1 верхней строки коммутатора поданы нулевые логические-уровни, а на вертикальные входы 7 нижней стро ки коммутатора - единичные логические уровни, то при коде 01101010 на горизонтальных входах 8 ячеек 1 и нулевых логических уровнях на -горизонтальных входах 9 ячеек 1 этого же столбца коммутатора осуществляет ся соединение седьмого входного канала с первым выходным,пятого - с вторым, третьего - с третьим и второго - с четвертым.Работа коммутатора в этом случае происходит следующим образом На горизонтальный вход .8 ячейки 1, лежащей на пересечении седьмой строки с первым столбцом коммутатор подается единичный логический уровень, следовательно, на ее вертикальном выходе 4 образуется нулевой логический уровень. Начиная с указанной ячейки 1 нулевой логический уровень образуется на вертикальных выходяк 4 всех расположенных вьше ячеек 1 первого столбца. На горизонтальный вход 8 восьмой ячейки 1 первого столбца подается нулевой ло гический уровень,,единичный логический уровень подается на вертикальньй вход 7 седьмой ячейки 1 первого столбца. В результате, чего на входа 8 и 7 седьмой ячейки 1 первого стол ца имеет место одновременная подача единичных логических уровней, поэтому именно на этой ячейке 1 осуществляется соединение седьмой строки с первым столбцом, т.е. седьмой входной канал соединяется с первым выходным каналом. На горизонтальном в ходе 11 этой же ячейки 1 образуется нулевой логический уровень, в результате чего на горизонтальные вхо ды 8 ячеек 1 второго столбца коммутатора подается код 01101000 с погашенной седьмой единицей. Соединение последующих входных каналов коммутатора с вькодными каналами осуществляется аналогично. Наличие нулевых логический уровней на горизонтальных входах 9 всех ячеек 1 не нарушает логику работы коммутатора. Пусть, например, требуется осуществить соедине;ние второго входного канала с первым и вторым выходными каналами, а седьмого выс третьим и четходного канала каналами. вертым выходными 416 Для этого на вертикальные входы 2 и 7 ячеек 1 верхней и нижней строк коммутатора соответственно подаются коды 1100 и 0011, на вертикальные входы 3 ячеек 1 верхней строки коммутатора - код 0000. На горизонтальные входы 8 и 9 ячеек 1 крайнего левого столбца коммутатора подается код 01000010, причем единичные логические уровни на входах 8 ячеек 1 означают как и прежде, номера тех входных каналов, которые требуется соединить, а единичные логические уровни на входах 9 ячеек 1 означают, что каждый из этих входных каналов (второй и седьмой) требуется соединить с несколькими выходными каналами одновременно. Количество подключенных выходных каналов определяется количеством единиц в кодах, подаваемых соответственно на вертикальные входы 2 и 7 ячеек 1 верхней и нижней строк коммутатора. На горизонтальный вход 8 первой ячейки 1 первого столбца подаете нулевой логический уровень, который проходит на входы 8 всех ячеек 1 первой строки коммутатора, а на вертикальные входы 2 ячеек 1 верхней строки коммутатора - код 1100, в результате чего на вертикальные входы 2 ячеек 1 второй строки коммутатора поступает код 1100. Так как на горизонтальные входы 8 и 9 второй ячейки 1 первого столбца подаются единичные логические уровни, то на горизонтальных входах 8 и 9 всех ячеек 1 второй строки коммутатора образуются единичные логические уровни, а на вертикальных вьп:одах 5 всех ячеек 1 второй строки - нулевые логические уровни. Начиная с этой строки нулевые логические уровни образуются на вертикальных выходах 5 ячеек 1 всех расположенных ниже строк. Таким образом, в первых двух ячейках 1 второй строки коммутатора имеет место одновременная подача единичных логических уровней на входы 2 и 8, поэтому именно на этих ячейках осуществляется соединение второй строки с первым и вторым столбцами коммутатора, т.е. второй входной канал соединяется с первым и вторым выходными каналами одновременно. Аналогично для нижней и седьмой строк коммутатора получают соединение седьмого входного канала с

711

третьим и четвертым выходными каналами одновременно.

Таким образом, каждому значению кода, поданного на вертикальный вход 2 ячеек 1 верхней строки коммутатора, и одновременно значению этого же кода,поданного на вертикальные входы 7 ячеек 1 нижней строки коммутатора, в зависимости от значений кодов, подаваемых на горизонтальные входы 8 и 9 .ячеек 1 первого столбца коммутатора, соответствует определенный порядок соединения входных каналов с выходными каналами коммутатора.

Технико-экономический эффект от использования изобретения заключается в том, что благодаря введению

02418

дополнительных элементов И и ШШ в каждую ячейку коммутатора,а также дополнительных горизонтальных связей между ячейками каждой строки коммутатора, обеспечивается расширение функциональных возможностей, а именно увеличивается в 72 раза число способов соединения входных и выходных каналов, при этом сохраняется постоянным число одновременно коммутируемых каналов. Кроме того, при эксплуатации предлагаемого коммутатора возможно уменьшение общего врег мени коммутации (обслуживания) в результате одновременного подключения нескольких выходных канапов коммутатора к одному входному.

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутатор | 1985 |

|

SU1248045A1 |

| Коммутатор | 1981 |

|

SU1003336A1 |

| Коммутатор | 1976 |

|

SU558399A1 |

| Коммутатор | 1986 |

|

SU1314332A2 |

| Коммутатор | 1983 |

|

SU1120313A1 |

| Ячейка однородной среды | 1982 |

|

SU1013943A1 |

| КРЕМНИЕВЫЙ МУЛЬТИПЛЕКСОР | 2015 |

|

RU2602373C1 |

| Ячейка однородной структуры | 1989 |

|

SU1674104A1 |

| Матричное вычислительное устройство | 1979 |

|

SU809173A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ СРЕДЫ | 1995 |

|

RU2103724C1 |

КОММУТАТОР по авт. св. № 1003336, отличающийся тем, что, с целью расширения его функциональных возможностей, в каждую из идeнтичныx ячеек введены третий элемент ИЛИ и пятый элемент И, первый вход которого по ключен к :Ш т первому горизонтальному входу ячейки, второй вход - к выходу второго элемента ШШ, а третий вход является третьим горизонтальным входом ячейки и соединен с третьим горизонтальным выходом ячейки, а выход соединен с одним из входов третьего элемента ШШ, другой вход которого соединен с выходом третьего элемента И, а выход - со вторым горизонтальным выходом ячейки, причем третьи горизонтальные вход и ячейки с координатами (i,) соединены с третьими горизонтальными выходом и входом ячеек с координатами

Фиг. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Коммутатор | 1981 |

|

SU1003336A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-02-15—Публикация

1983-09-28—Подача