(54) МАТРИЧНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО

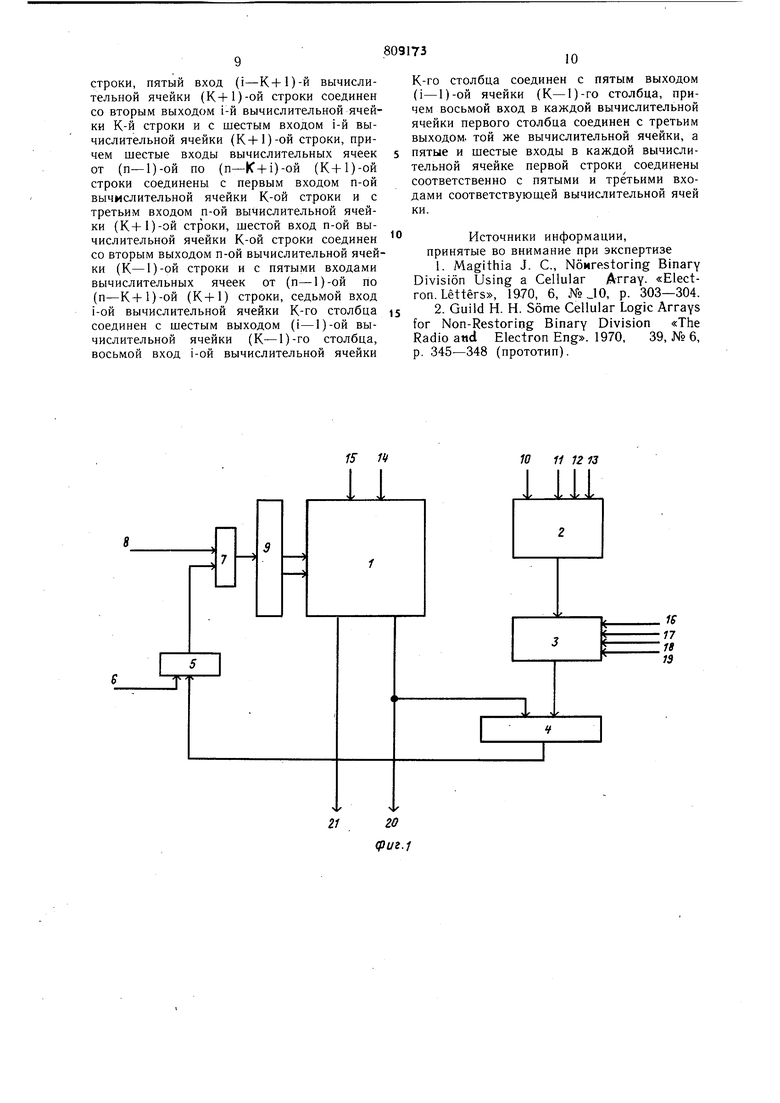

динен с первыми входами вычислительных ячеек п-го столбца, а второй выход регистра - со вторыми входами вычислительных ячеек п-го столбца, третьи и четвертые входы вычислительных ячеек цервой строки соединены соответственно с пятым и шестым входами устройства, а второй, третий, четвертый и пятый входы коммутатора соединень соответственно с седьмым, восьмым, девятым и десятым входами устройства, первые, и вторые выходы вычислительных ячеек последней строки соединены соответственно с первым и вторым выходами устройства, причем каждая вычислительная ячейка дополнительно содержит второй одноразрядный сумматор и второй сумматор по модулю два, причем выход первого сумматора по модулю два соединен с первым входом первого одноразрядного сумматора, выход второго сумматора по модулю два соединен с первым входом второго одноразрядного сумматора, первый вход первого сумматора по модулю два соединен с первым входом вычислительной ячейки, первый вход второго сумматора по модулю два соединен со вторым входом вычислительной ячейки, второй вход первого одноразрядного сумматора соединен с третьим входом вычислительной ячейки, второй вход первого сумматора по модулю два соединен с четвертым входом вычислительной ячейки, второй вход второго сумматора по модулю два соединен с пятым входом вычислительной ячейки, а второй вход второго одноразрядного сумматора соединен с шестым входом вычислительной ячейки, третий вход первого одноразрядного сумматора соединен с седьмым входом вычислительной ячейки, а третий вход второго одноразрядного сумматора соединен с восьмым входом вычислительной ячейки, первый выход первого однразрядного сумматора соединен с первым выходом вычислительной ячейки, а первый выход второго одноразрядного сумматора соединен со вторым выходом вычислительной ячейки, первый выход второго сумматора по модулю два соединен с третьим выходом вычислительной ячейки, а первый выход первого сумматора по модулю два соединен с четвертым выходом вычислительной ячейки, вторые выходы второго и первого одноразрядных сумматоров соединены соответственно с пятым и шестым выходами вычислительной ячейки, первые входы вычислительных ячеек i-ro столбца соединены с четвертыми выходами соответствуюш,их вычислительных ячеек (i-1)-го столбца, вторые входы вычислительных ячеек i-ro столбца соединены с третьими выходами соответствуюших вычислительных ячеек (i-1)-го столбца, третий вход i-ой вычислительной ячейки К-й строки соединен с первым Bjjiходом i-ой вычислительной ячейки (К-1)-ой строки и с четвертым входом ( +1)-йвычислительной ячейки К-ой строки, пятый В.ХОД (i-K-f 1)-й вычислительной ячейки (КЧ-1)-ой строки соединен с вторым выходом i-й вычислительной ячейки К-й строки и с шестым входом 1-й вычислительной ячейки (К+1)-ой строки, причем шестые входы вычислительных ячеек от (п-1)-ой по (п-К + 1)-ой (К+1)-ой строки соединены с первым входом п-ой вычислительной ячейки К-ой строки с третьим входом п-ой вычислительной ячейки (K-f 1)-ой строки, шестой вход п-ой вычислительной ячейки К-ой строки соединен со вторым выходом п-ой вычислительной ячейки (К-1)-ой строки и с пятыми входами вычислительных ячеек от (n-0-ой по (п-К+1)-ой (К+1) строки, седьмой вход i-ой вычислительной ячейки К-го столбца соединен с шестым выходом )-oй вычислительной ячейки (К-1)-го столбца, восьмой вход i-ой вычислительной ячейки К-го столбца соединен с пятым выходом ()-oй ячейки (К-1)-го столбца, причем восьмой вход в каждой вычислительной ячейки первого столбца соединен с третьим выходом той же вычислительной ячейки, а пятые и шестные входы в каждой вычислительной ячейке первой строки соединены соответственно с пятыми и третьим входами соответствующей вычислительной ячейки.

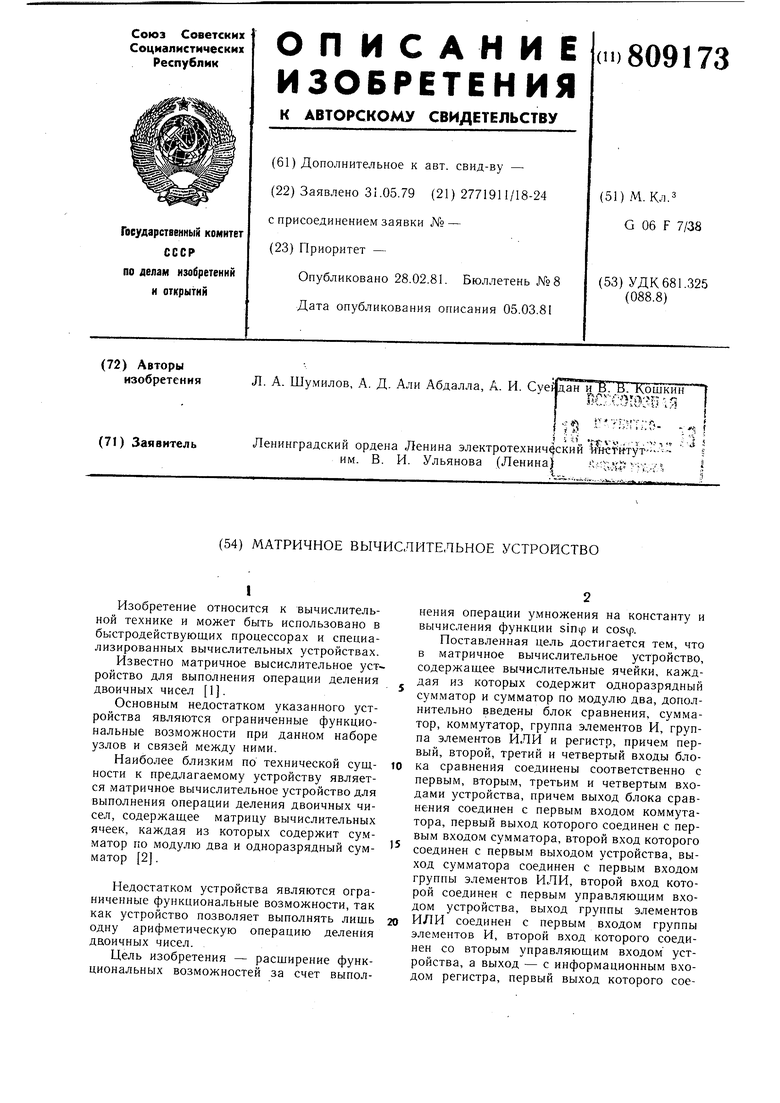

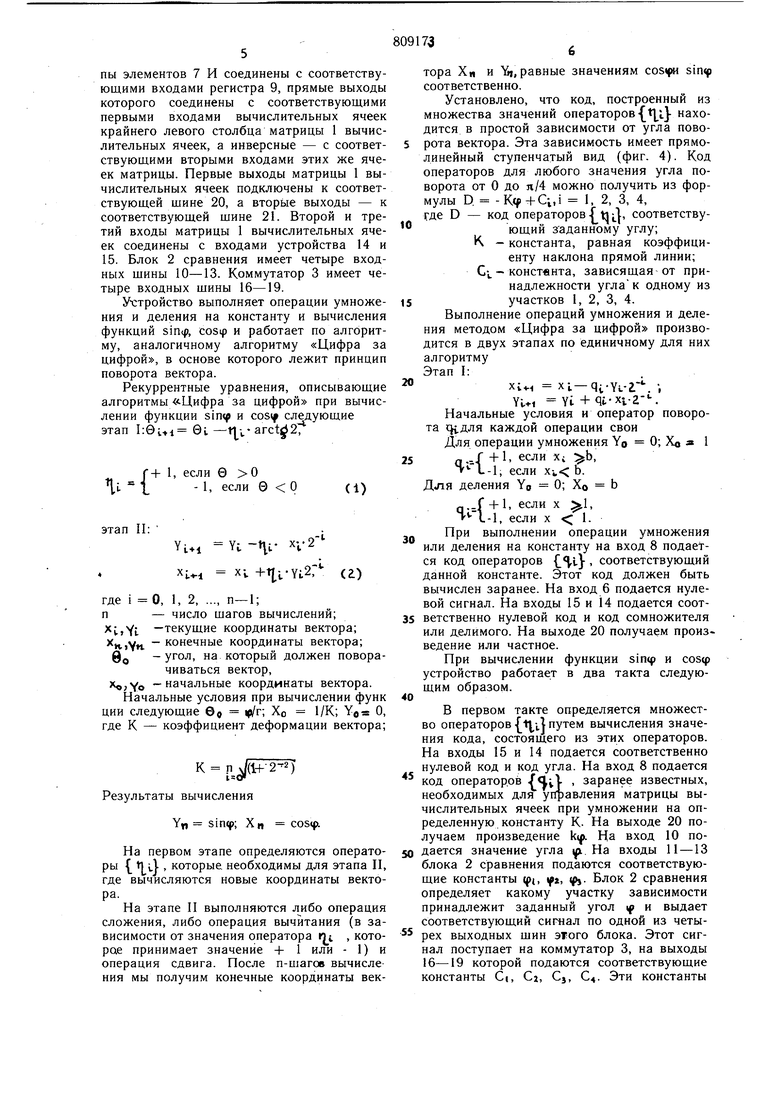

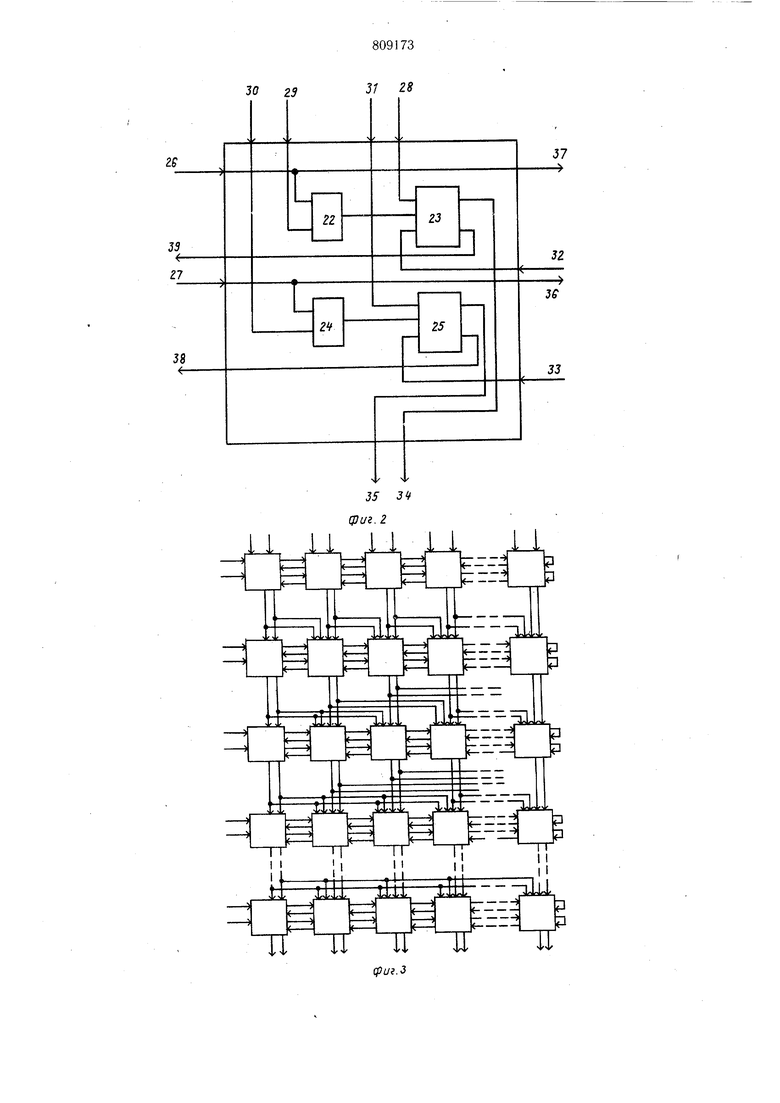

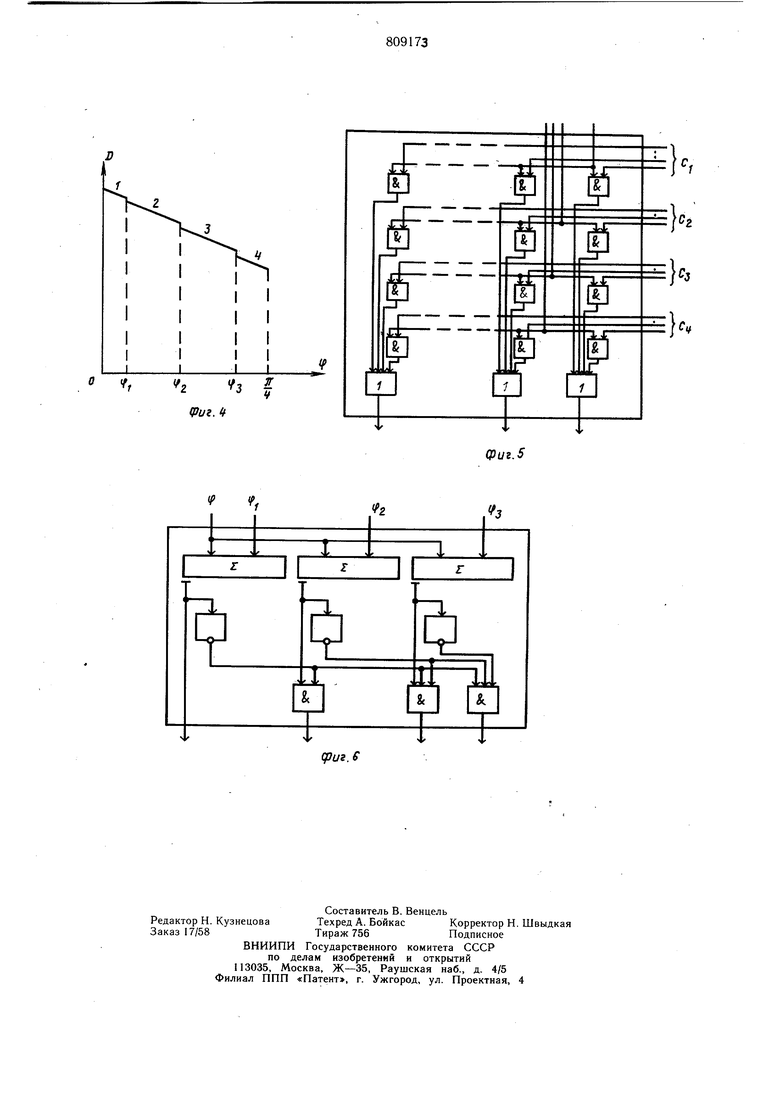

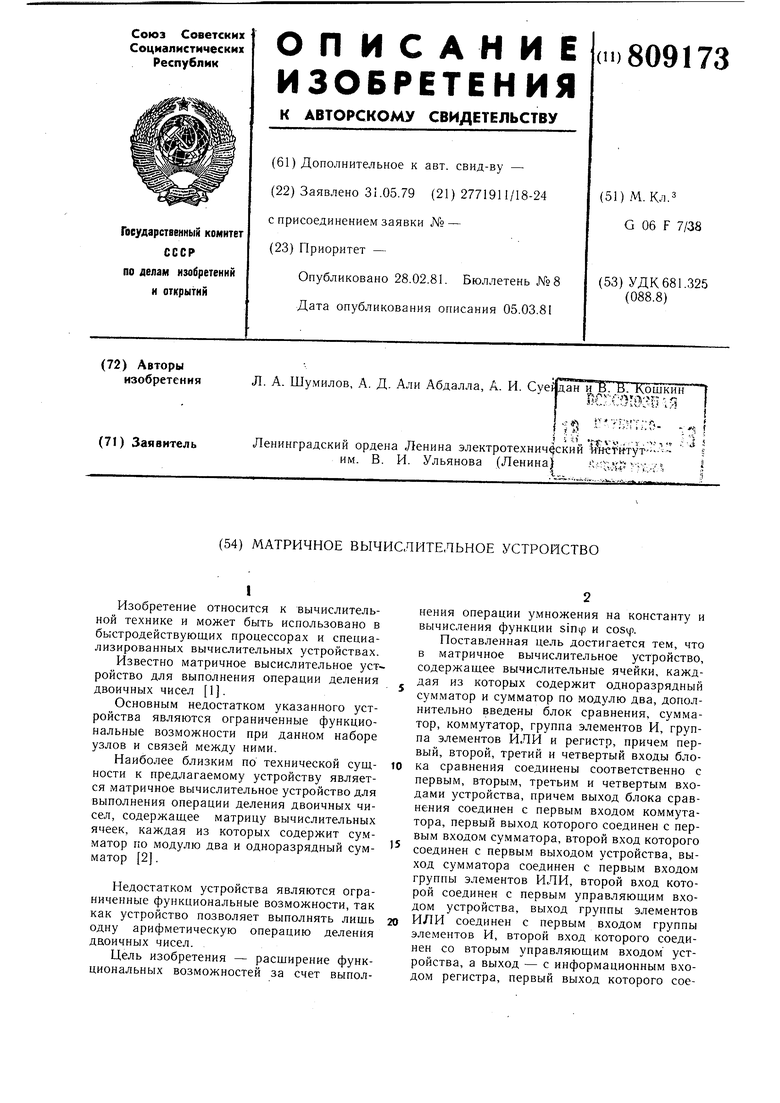

На фиг. 1 представлена структурная схема матричного вычислительного устройства; на фиг. 2-структурная схема вычислительной ячейки; на фиг. 3 - то же, матрица вычислительных ячеек; на фиг. 4 - зависимость кода D от угла р; на фиг. 5 - структурная схема коммутатора; на фиг. 6- то же, блока сравнения.

г Матричное вычислительное устройство (фиг. 1) содержит матрицу 1 вычислительных ячеек, блок 2 сравнения, коммутатор 3, сумматор 4, группу элементов 5 ИЛИ, первый управляющий вход 6 устройства, группу элементов 7 И, второй управляюший вход

8, регистр 9, с первого по десятый входы уст ройства 10-19, первый и второй выходы устройства 20 и 21.

Вычислительная ячейка содержит (фиг. 2) первый сумматор 22 по модулю два, первый одноразрядный сумматор 23, второй сум матор 24 по модулю два, второй одноразрядный сумматор 25, с первого по восьмой входы ячейки 26-33, с первого по шестой выходы ячейки 34-39.

Выходы коммутатора 3 и один из выходов матрицы соединены с первыми и вторыми входами сумматора 4. Выходы сумматора соединены с первыми входами группы элементов 5 ИЛИ, вторые входы которой соединены с шиной 6 управления. Выходы группы элементов 5 ИЛИ соединены с первыми входами группы элементов 7 И, вторые входы которой подключены к соответствующей управляюшей шине 8. Выходы группы элементов 7 И соединены с соответствующими входами регистра 9, прямые выходы которого соединены с соответствующими первыми входами вычислительных ячеек крайнего левого столбца матрицы 1 вычислительных ячеек, а инверсные - с соответствующими вторыми входами этих же ячеек матрицы. Первые выходы матрицы 1 вычислительных ячеек подключены к соответствующей шине 20, а вторьге выходы - к соответствующей щине 21. Второй и третий входы матрицы 1 вычислительных ячеек соединены с входами устройства 14 и 15. Блок 2 сравнения имеет четыре входных щины 10-13. Коммутатор 3 имеет четыре входных щины 16-19.

Устройство выполняет операции умножения и деления на константу и вычисления функций sinf, созф и работает по алгоритму, аналогичному алгоритму «Цифра за цифрой, в основе которого лежит принцип поворота вектора.

Рекуррентные уравнения, описывающие алгоритмы «Цифра за цифрой при вычислении функции и cosf следующие этап I:0Ui в1 -l varct 27

+ 1, если в 0

v-{

- 1, если 9 О(1)

этап II:

-,-t

Yi+i XV 2

xi XI -t-TJ i,-YL2r (г)

где i О, 1, 2, ..., n-1; п- число щагов вычислений;

Х.,У;. -текущие координаты вектора; конечные координаты вектора;

во -угол, на который должен поворачиваться вектор,

-начальные координаты вектора.

Начальные условия при вычислении функ ции следующие во г; Хо 1/К; YO О, где К - коэффициент деформации вектора;

К n(l-f 2-2) Результаты вычисления

Yn sintf; Хц .

На первом этапе определяются операторы ti v} которые необходимы для этапа II, где вычисляются новые координаты вектора.

На этапе II выполняются либо операция сложения, либо операция вычитания (в зависимости от значения оператора rji , которое принимает значение + 1 или - 1) и операция сдвига. После п-шагов вычисления мы получим конечные координаты вектора Хп и ii, равные значениям соответственно.

Установлено, что код, построенный из множества значений операторов находится в простой зависимости от угла поворота вектора. Эта зависимость имеет прямолинейный ступенчатый вид (фиг. 4). Код операторов для любого значения угла поворота от О до п/4 можно получить из формулы D -Ktp-f-Ci,i I, 2, 3, 4, где D - код операторов-Г ttjl, соответствующий заданному углу; К - константа, равная коэффициенту наклона прямой линии; С. - конствнта, зависящая от принадлежности угла к одному из участков 1, 2, 3, 4.

Выполнение операций умножения и деления методом «Цифра за цифрой производится в двух этапах по единичному для них алгоритму Этап I:

хи XI-qi-Yi-r -. ,

Yi., Yi + qi.-Xi-2--. Начальные условия и оператор поворота каждой операции свои

Для операции умножения YO 0; Хо 1

а--Г + L-1, если хь Ь.

Для деления YO 0; Хо b

n.-f + 1, если X vl, -l-l, е

если X 1. При выполнении операции умножения или деления на константу на вход 8 подается код операторов соответствующий данной константе. Этот код должен быть вычислен заранее. На вход 6 подается нулевой сигнал. На входы 15 и 14 подается соответственно нулевой код и код сомножителя или делимого. На выходе 20 получаем произведение или частное.

При вычислении функции sintp и устройство работает в два такта следующим образом.

В первом такте определяется множество операторов {1,1} путем вычисления значения кода, состоящего из этих операторов. На входы 15 и 14 подается соответственно нулевой код и код угла. На вход 8 подается

код операторов /4i}- . заранее известных, необходимых для управления матрицы вычислительных ячеек при умножении на определенную константу К. На выходе 20 получаем произведение ktp. На вход 10 подается значение угла . На входы 11 -13 блока 2 сравнения подаются соответствующие константы ф(, уа, (j. Блок 2 сравнения определяет какому участку зависимости принадлежит заданный угол if и выдает соответствующий сигнал по одной из четырех выходных щин эгого блока. Этот сигнал поступает на коммутатор 3, на выходы 16-19 которой подаются соответствующие константы С(, Cj, Cj, €4. Эти константы соответствуют участкам 1, 2, 3, 4 зависимбсти кода D от угла ц. По сигналу, поступающему из блока 2 сравнения, пропускается одна из констант Ci, Сг, Q, С;,, которая поступает на второй вход сумматора 4. Сумма (Кф+С), которая представляет собой код управления для второго этапа вычисления sniip и созф, поступает через группы вентилей 5 и 7 на входы регистра 9. Во втором такте выполняется непосредственное вычисление sin sp и созф. На входы 15 и 14 подаются соответственно нулевой код и код значения 1/К (К - коэффициент деформации вектора при повороте). На выходах 20 и 21 получаем соответственно значения СО5ф и 51ПЦ). Матрица 1 вычислительных ячеек выполняет вычисление по рекуррентным соотношениям (2) В каждой строке матрицы промежуточные значения координат векторга Xi. , Yi, образуются на выходах первых и вторых одноразрядных сумматоров вычислительных ячеек строк матрицы. Сдвиги промежуточных результатов на i-разрядов вправо (это равносильно их умножению на ) осуществляются внутриматричными соединениями. Вычисления B.i матрице выполняются в дополнительном жоде. Размножение знаков промежуточных результатов при сдвиге осуществляется соответствующими внутриматричными соединениями. Формула изобретения 1. Матричное вычислительное устройство, содержащее вычислительные ячейки, каждая из. которых содержит одноразрядный сумматор -и сумматор по модулю два, отли,чающееся тем, что с целью расширения функциональных возможностей, за счет выполнения дополнительных операций умножения на константу и вычисления функций и , в него дополнительно введены блок сравнения, сумматор, коммутатор, группа элементов И, группа элементов ИЛИ и регистр, причем первый, второй, третий и четвертый входы блока сравнения соединены соответственно с первым, вторым, третьим и четверть.VI входами устройства, а выход блока сравнения соединен с первым входом коммутатора, первый выход которого соединен с первым входом сумматора, второй вход которого соединен с первым выходом устройства, выход сум.матора соединен с первым входомгруппы элементов ИЛИ, второй вход которой соединен с первым управляющим входом устройства, выход группы элементов ИЛИ соединен с первым входом группы элементов И, второй вход которого соединен со вторым управляющим входом устройства, а выход - с информационным входом регистра, первый выход которого соединен с первыми входами вычислительных ячеек п-го столбца, а второй выход регистра - со вторыми входами вычислитель ных ячеек п-го столбца, третьи и четвертые входы вычислительных ячеек первой строки соединены соответственно с пятым и шестым входами устройства, а второй, третий, четвертый и пятый входы коммутатора соединены соответственно с седьмым, восьмы.м, девятым и десятым входами устройства, первые и вторые выходы вычислительных ячеек последней строки соединены соответственно с первым и вторым выходами устройства. 2. Устройство по п. 1, отличающееся тем, что каждая вычислительная ячейка дополнительно содержит второй одноразрядный сумматор и второй сумматор по модулю два, причем выход первого сумматора по модулю два соединен с первым входом первого одноразрядного су.мматора, выход второго сумматора по модулю два соединен с первым входом второго одноразрядного сумматора, первый вход первого сумматора по модулю два соединен с первым входом вычислительной ячейки, первый вход второго сумматора по модулю два соединен со вторьш входом вычислительной ячейки, второй вход первого одноразрядного сум.матора соединен с третьим входом вычислительной ячейки, второй вход первого сумматора по модулю два соединен с четверты.м входом вычислительной ячейки, второй вход второго сумматора по модулю два соединен с пятым входом вычислительной ячейки, а второй вход второго одноразрядного сумматора соединен с щестым входом вычислительной ячейки, третий вход первого одноразрядного сумматора соединен с седь.мым входом вычислительной ячейки, а третий вход второго одноразрядного сумматора соединен с восьмым входом вычислительной ячейки, первый выход первого одноразрядного сум.матора соединен с первым выходом вычислительной ячейки, а первый выход второго одноразрядного сумматора соединен со вторым выходом вычислительной ячейки, первый выход второго су.мматора по модулю два соединен с третьим выходом вычислительной ячейки, а первый выход первого сум.матора по .модулю два соединен с четвертым выходом вычислительной ячейки, вторые выходы второго и первого одноразрядных сумматоров соединены соответственно с пятым и щестым выходами вычислительной ячейки, первые входы вычислительных ячеек i-ro столбца соединены с четвертыми выходами соответствующих вычислительных ячеек (i-i)-ro столбца, вторые входы вычислительных ячеек i-ro столбца соединены с третьими выходами соответствующих вычислительных ячеек )-ro столбца, третий вход i-ой вычислительной ячейки К-йстроки соединен с первым выходом i-ой вычислительной ячейки (К-1)-ой строки и с четвертым входом (i K+0-й вычислительной ячейки К-ой строки, пятый вход (i-К+1)-й вычислительной ячейки (К+1)-ой строки соединен со вторым выходом i-й вычислительной ячейки К-й строки и с шестым входом i-й вычислительной ячейки (К-М)-ой строки, причем шестые входы вычислительных ячеек от (п-1)-ой по (п-К + 1)-ой (К+1)-ой строки соединены с первым входом п-ой вычислительной ячейки К-ой строки и с третьим входом п-ой вычислительной ячейки (К+1)-ой строки, шестой вход п-ой вычислительной ячейки К-ой строки соединен со вторым выходом п-ой вычислительной ячейки (К-1)-ой строки и с пятыми входами вычислительных ячеек от (п-1)-ой по (п-КЧ-1)-ой (К+1) строки, седьмой вход i-ой вычислительной ячейки К-го столбца соединен с шестым выходом (i-1)-ой вычислительной ячейки (К-1)-го столбца, восьмой вход i-ой вычислительной ячейки 73 К-го столбца соединен с пятым выходом (i-1)-ой ячейки (К-1)-го столбца, причем восьмой вход в каждой вычислительной ячейки первого столбца соединен с третьим выходом, той же вычислительной ячейки, а пятые и шестые входы в каждой вычислительной ячейке первой строки соединены соответственно с пятыми и третьими входами соответствуюшей вычислительной ячей ки. Источники информации, принятые во внимание при экспертизе 1. Magithia J. С., NoMrestoring В1пагу Division Using а Cellular Array. «Electron. Letters, 1970, 6, № JO, p. 303-304. 2. Guild H. H. Some Cellular Logic Arrays for Non-Restoring Binary Division «The Radio and Electron Eng. 1970, 39, № 6, p. 345-348 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное вычислительное устройство | 1979 |

|

SU824195A1 |

| Матричное вычислительное устройство | 1979 |

|

SU809174A1 |

| Вычислительное устройство | 1981 |

|

SU1032454A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1134948A1 |

| Матричное устройство для возведенияВ КВАдРАТ | 1979 |

|

SU842804A1 |

| Устройство для умножения | 1989 |

|

SU1688238A1 |

| Устройство для умножения | 1987 |

|

SU1501043A1 |

| Матричное вычислительное устройство тригонометрических функций | 1984 |

|

SU1238060A1 |

| Вычислительное устройство | 1983 |

|

SU1117635A1 |

| Вычислительное устройство | 1983 |

|

SU1164701A1 |

11 « / W b 11 1213 L 1х 4/

30 23

U TI IT U

J/ 2S

il

I I

I I

ff

JL

3 f

/,

(риг. ft

f f.

Авторы

Даты

1981-02-28—Публикация

1979-05-31—Подача