Изобретение относится к автоматике и вычислительной технике.

Известен коммутатор, содержащий идентичные ячейки, расположенные в узлах двумерной решетки и идентично соединенные между собой, каждая из которых содержит элементы И, ИЛИ

и НЕ С13.

К недостаткам известного коммутатора относятся низкое быстродействие и сложность конструкции.

Наиболее близким по технической сущности к предлагаемому является коммутатор, содержащий идентичные ячейки, расположенные в узлах двумерной решетки идентично соединенные между собой, каждая из которых содержит элементы И, ИЛИ, НЕ 2.

Недостатком этого устройства является невозможность изменения порядка соединения выходных ка.налов, что сужает его функциональные возможности.

Цель изобретения - расишрение функциональных возможностей коммутатора.

Поставленная цель достигается тем, что. в коммутатор, содержащий идентичные ячейки, расположенные в узлах двумерной решетки и идентично

соединенные между собой, каждая из которых содержит элементы И,ИЛИ и НЕ, причем в каждой ячейке ее горизонтальные входы соединены с входами первого элемента И, выход которого подключен к одному из входов элемента ИЛИ, другой вход которого соединен с вторым вертикальным входом ячейки, а выход - с вторим вертикальным вы10ходом ячейки, первый вертикальный вход ячейки, а выход - с вторым вер тикальным выходом ячейки, первый вертикальный вход ячейки подключен.к одному из входов второго элемента

15 И, другой вход которого через первый элемент НЕ соединен с первым горизонтальным входом ячейки, а выход - с первым вертикальным выходом ячейки, первый горизонтальный вход

20 ячейки соединен с одним из входов третьего элемента И, другой вход которого подключен к выходу второго элемента НЕ, а выход - к второму горизонтальному выходу ячейки, второй

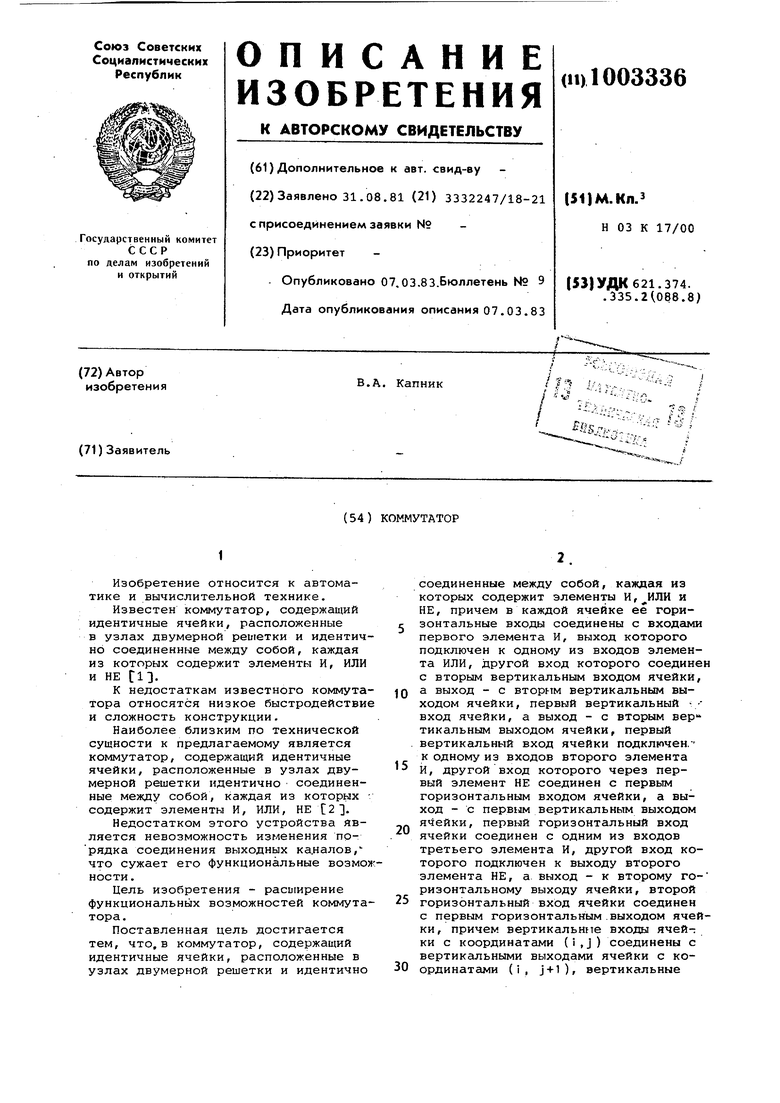

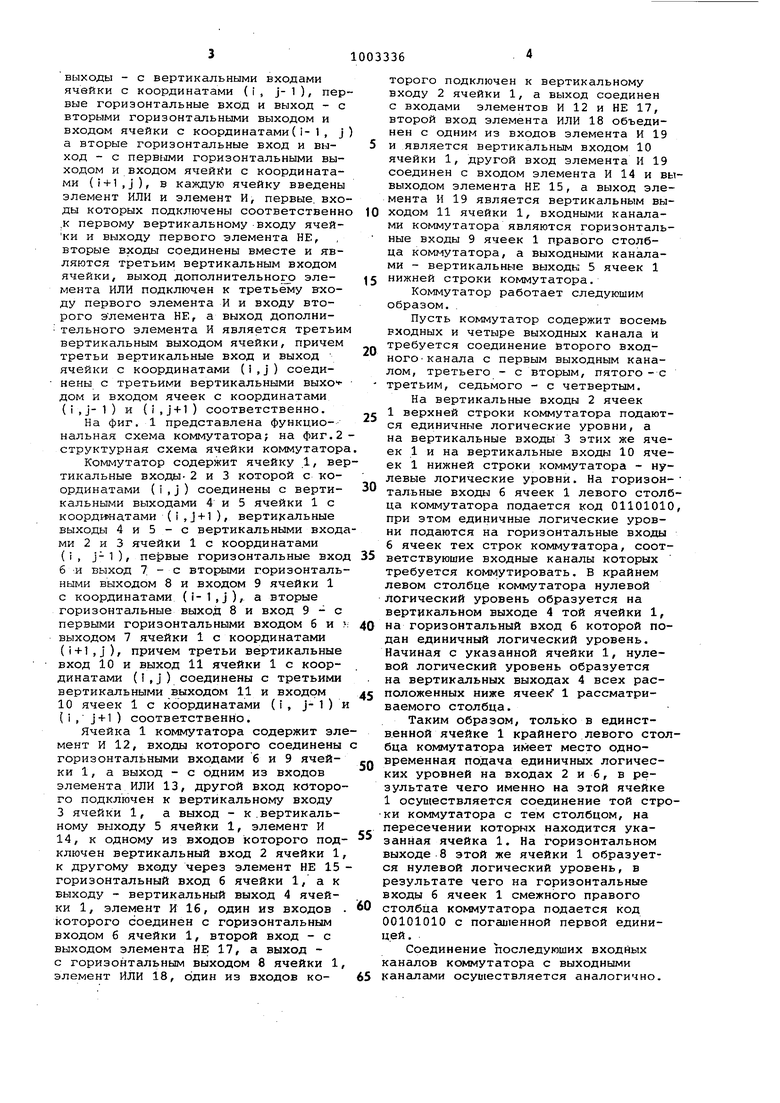

25 горизонтальный вход ячейки соединен с первым горизонтальным.выходом ячейки, причем вертикальные входы ячейки с координатами (i,j ) соединены с вертикальными выходами ячейки с ко30ординатами (i, j+1), вертикальные выходы - с вертикальными входами ячейки с координатами (i, j- 1 ), пер вые горизонтальные вход и выход - с вторыми горизонтальными выходом и входом ячейки с координатами(i- 1, j а вторые горизонтальные вход и выход - с первЕями горизонтальными выходом и входом ячейки с координатами (i+1,j), в каждую ячейку введены элемент ИЛИ и элемент И, первые, вхо ды которых подключены соответственн ,к первому вертикальному входу ячейки и выходу первого элемента НЕ, , вторые входы соединены вместе и являются третьим вертикальным входом ячейки, выход дополнительного элемента ИЛИ подключен к третьему нходу первого элемента И и входу второго элемента НЕ, а выход дополнительного элемента И является третьи вертикальным выходом ячейки, причем третьи вертикальные вход и выход ячейки с координатами (i ,j ) соединены с третьими вертикальными выхо дом и входом ячеек с координатами (i,j-1) и {i,j+1) соответственно. На фиг, 1 представлена функциональная схема коммутатора; на фиг.2 структурная схема ячейки коммутатор Коммутатор содержит ячейку 1, ве тикальные входы-2 и 3 которой с координатами (1,j) соединены с вертикальными выходами 4 и 5 ячейки 1 с коорди на,тами ( i , J + 1 ), вертикальные выходы 4 и 5 - с вертикальными вход ми 2 и 3 ячейки 1 с координатами (i, j-1), первые горизонтальные вход 6 и выход 7 - с вторыми горизонталь ными выходом 8 и входом 9 ячейки 1 с координатами ( i- 1 , j ), а вторые горизонтальные выход 8 и вход 9 - с первыми горизонтальными входом 6 и выходом 7 ячейки 1 с координатами (i+1,j), причем третьи вертикальные вход 10 и выход 11 ячейки 1 с координатами (I,j) соединены с третьими вертикальными выходом 11 и входом 10 ячеек 1 с координатами ( i , j- 1 ) и (i, j+1) соответственно. Ячейка 1 коммутатора содержит эл мент И 12, входы которого соединены горизонтальными входами б и 9 ячейки 1, а выход - с одним из входов элемента ИЛИ 13, другой вход которо го подключен к вертикальному входу 3 ячейки 1, а выход - к .вертикальному выходу 5 ячейки 1, элемент И 14, к одному из входов которого подключен вертикальный вход 2 ячейки 1 к другому входу через элемент НЕ 15 горизонтальный вход 6 ячейки 1, а к выходу - вертикальный выход 4 ячейки 1, элемент И 16, один из входов которого соединен с горизонтальным входом б ячейки 1, второй вход - с выходом элемента НЕ 17, а выход с горизонтальным выходом 8 ячейки 1 элемент ИЛИ 18, Ьдин из входов которого подключен к вертикальному входу 2 ячейки 1, а выход соединен с входами элементов И 12 и НЕ 17, второй вход элемента ИЛИ 18 объединен с одним из входов элемента И 19 и является вертикальным входом 10 ячейки 1, другой вход элемента И 19 соединен с входом элемента И 14 и вывыходом элемента НЕ 15, а выход элемента И 19 является вертикальным выходом 11 ячейки 1, входными каналами коммутатора являются горизонтальные входы 9 ячеек 1 правого столбца ком1чутатора, а выходными каналами - вертикальные выходы 5 ячеек 1 нижней строки коммутатора. Коммутатор работает следующим образом. Пусть коммутатор содержит восемь входных и четыре выходных канала и требуется соединение второго входного канала с первым выходным каналом, третьего - с вторым, пятого - с третьим, седьмого - с четвертым. На вертикальные входы 2 ячеек 1 верхней строки коммутатора подаются единичные логические уровни, а на вертикальные входы 3 этих же ячеек 1 и на вертикальные входы 10 ячеек 1 нижней строки коммутатора - нулевые логические уровни. На горизон- тальные входы б ячеек 1 левого столбца коммутатора подается код 01101010, при этом единичные логические уровни подаются на горизонтальные входы 6 ячеек тех строк коммутатора, соответствующие входные каналы которых требуется коммутировать. В крайнем левом столбце коммутатора нулевой логический уровень образуется на вертикальном выходе 4 той ячейки 1, на горизонтальный вход б которой подан единичный логический уровень. Начиная с указанной ячейки 1, нулевой логический уровень образуется на вертикальных выходах 4 всех расположенных ниже ячеекГ 1 рассматриваемого столбца. Таким образом, только в единственной ячейке 1 крайнего левого столбца коммутатора имеет место одновременная подача единичных логических уровней на входах 2 и б, в результате чего именно на этой ячейке 1 осуществляется соединение той строки коммутатора с тем столбцом, на пересечении которых находится указанная ячейка 1. На горизонтальном выходе 8 этой же ячейки 1 образуется нулевой логический уровень, в результате чего на горизонтальные входы б ячеек 1 смежного правого столбца коммутатора подается код 00101010 с погашенной первой единицей . Соединение последующих входных каналов коммутатора с выходными кансШс1ми осуществляется аналогично. Если на вертикальные входы 2 и 3 ячеек 1 вер.хней строки коммутатора Jподаны нулевые логические уровни, а на вертикальные входы 10 ячеек 1 нижней строки коммутатора - единичные логические уровни, то при коде 01101010 на горизонтальных входах б ячеек 1 крайнего левого столбца коммутатора осуществляется соединение седьмого входного канала с первым выходным, пятого - с вторым, третьего -.стретьим, второго - с четвертым. Таким образом, каждому значению кода, поданного на вертикальные входы 2 ячеек 1 верхней строки комм татора, и одновременно -поданному ин версному значению этого же кода на вертикальные входы 10 ячеек 1 нижней строки коммутатора соответствует определенный порядок коммутации входных каналов на выходные каналы коммутатора. Формула изобретения Коммутатор., содержащий идентичные ячейки, расположенныев узлах двумерной решетки и идентично соеди ненные между собой, каждйя из которых содержит элементы И, ИЛИ и НЕ, причем в каждой ячейке ее горизонталь ные входы соединены с входами перво .го элемента И, выход которого подклю чен к одному их входов элемента ИЛИ другой вход которого соединен с вто рым вертикальным входом ячейки, а выход - с вторым вертикальным выходом ячейки, первый вертикальный вход ячейки подключен к одному из входов второго элемента И, другой вход которого через первый элемент НЕ соединен с первым горизонтальньам входом ячейки, а выход - с первым вертикальным выходом ячейки, первый горизонтальный вход ячейки соедине с одним из входов третьего элемента И, другой вход которого подключен к выходу второго элемента НЕ, а выход - к второму горизонтальному выходу ячейки, второй горизонтальный Ьход ячейки соединен с первЕлм горизонтальным выходом ячейки, причем вертикальные входы ячейки с координатами (i,j) соединены с вертикальными выходами ячейки с координатами (i, j + l),. вертикальные выходы - с вертикальными входами ячейки с координатами (i, j- 1 ), первые горизонтальные вход и выход - с вторыми горизонтальными выходом и входом ячейки с координатами { i- 1 . j ) а вторые горизонтальные вход и выход с первым горизонтальным выходом и входом ячейки с координатами (1+1, ),-отлйч ающийся тем, что, с целью расширения его функциональных возможностей,.в каждую ячейку коммутатора дополнительно введены элемент ИЛИ и элемент И, первые входы которых подключены соответст- . венно к первому вертикальному входу ячейки и выходу первого эле.мента НЕ, вторые входы соединены вместе и являются третьим вертикальным входом ячейки, выход дополнительного элемента ИЛИ подключен к третьему входу первого элемента И и входу второго элемента НЕ, а выход дополнительного элемента И является третьим вертикальным выходом ячейки., причем третьи вертикальные вход -и выход ячейки с координатеиии ( i , j ) соединены с третьими вер икальными выходом и входом ячеек с координатами (i,j-1) и (i,j + 1 ) соответственно. Источники информации, принятые во внимание при экспертизе 1. Фет Я.И. Функциональные возможности простых вычислительных средств АВТ. - Зинатне, Рига, 1974, № 3, с. 48. 2. Авторское свидетельство СССР . 558399, кл. Н 03 К 17/02, 15.05.77 (прототип).

lit

liT

lit

UT

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутатор | 1983 |

|

SU1140241A2 |

| Коммутатор | 1985 |

|

SU1248045A1 |

| Коммутатор | 1976 |

|

SU558399A1 |

| Функциональный коммутатор | 1983 |

|

SU1137458A1 |

| Функциональный коммутатор | 1985 |

|

SU1320802A1 |

| Коммутатор | 1983 |

|

SU1120313A1 |

| Коммутатор | 1986 |

|

SU1314332A2 |

| Ячейка однородной среды | 1977 |

|

SU664169A1 |

| УСТРОЙСТВО ДЛЯ СОРТИРОВКИ ДВУМЕРНОГО МАССИВА ДАННЫХ | 2004 |

|

RU2279122C1 |

| Матричный коммутатор | 1987 |

|

SU1439614A1 |

Авторы

Даты

1983-03-07—Публикация

1981-08-31—Подача