Изобретение относится к автоматике и вычислительной технике и может быть использовано для коммутации каналов ввода-вьшода информации цифровых устройств.

Цель изобретения - повьппение быстродействия за счет сокращения числа последовательно соединенных элементов, через которые проходит коммутируемый сигнал, путем введения в каждую ячейку коммутатора элемента с тремя устойчивыми состояниями и третьего элем.ента НЕ.

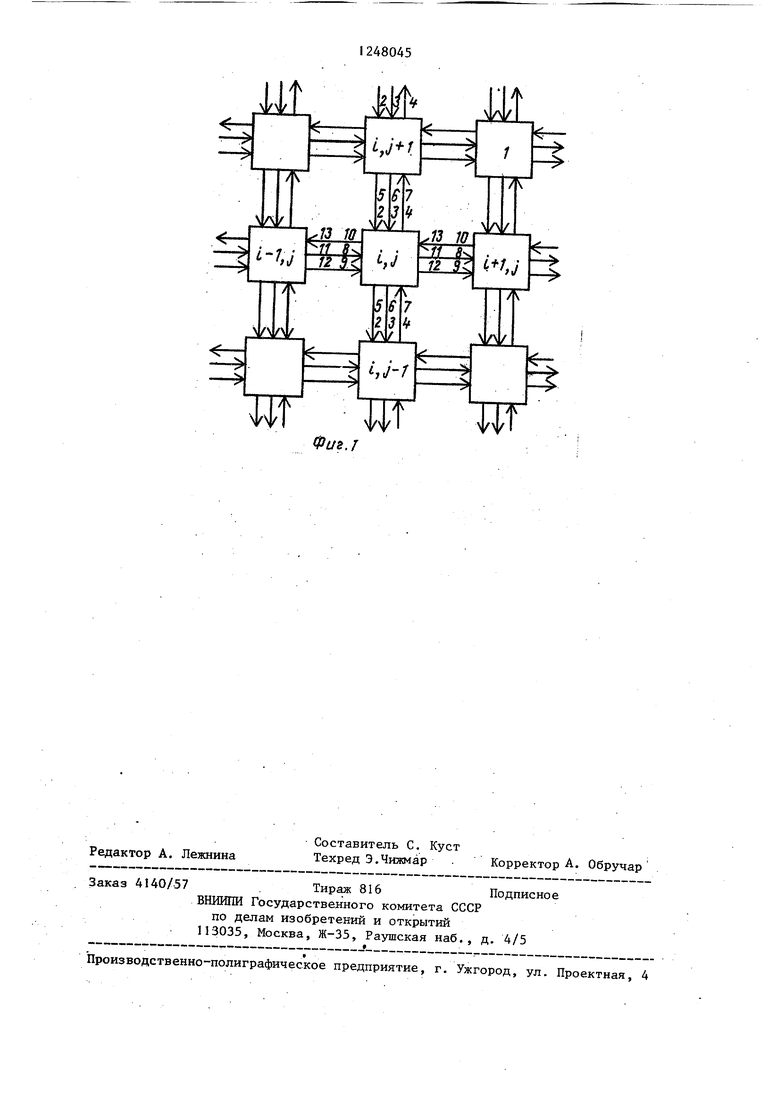

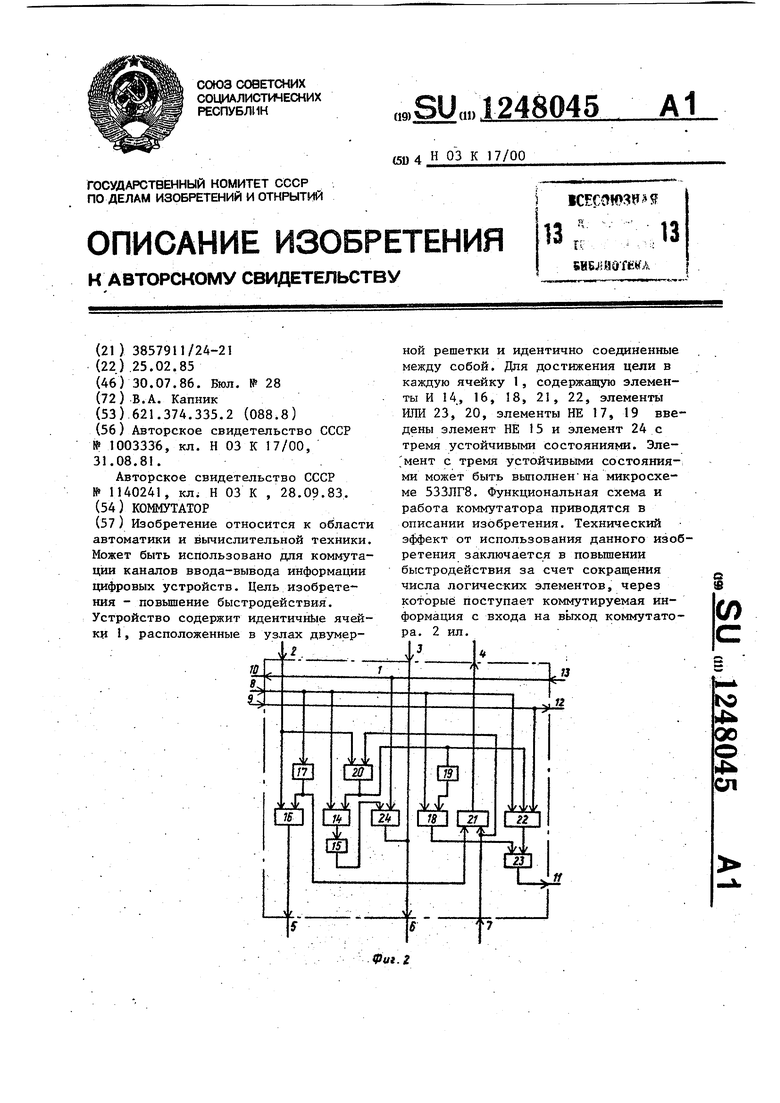

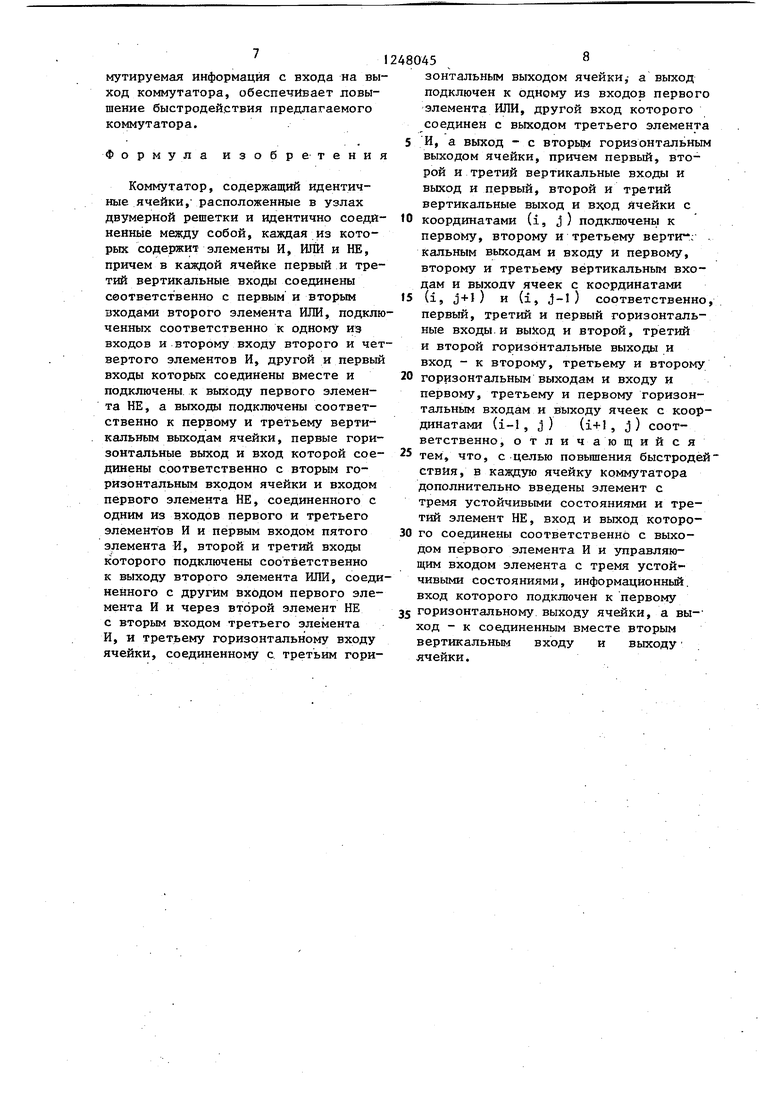

На фиг.1 приведена функциональная схема предлагаемого коммутатора; на- фиг.2 -структурная схема ячейки коммутатора.

Коммутатор содержит ячейку 1 с координатами (i, j) первьй и второй вертикальные входы 2 и 3 и третий вертикальный выход 4 которой соединены с первым и вторым вертикальными выходами 5 и 6 и третьим- вертикальным входом 7 ячейки 1 с

третьего элемента НЕ 15, выход которого соединен с управляющим входом элемента 24 с тремя устойчивыми состояниями, другой вход которого под- 5 ключен к первому горизонтальному выходу 10 ячейки 1, соединенному с вторым горизонтальным входом 13 ячей ки 1 , а выход - к соединенным вместе вторым вертикальным входу 3 и выхо- 10 ду 6 ячейки, первьш горизонтальный вход 8 которой подключен к входу первого элемента НЕ 17, соединенного с одним из входов третьего элемента И 18 и первым входом пятого элемента 5 И 22, третий вход которого подключен к соединенным вместе третьим горизонтальным входу 9 и выходу 12 ячейки 1, а выход соединен с одним из входов первого элемента ИЛИ 23, 20 другой вход которого подключен к выходу третьего элемента И 18, второй .вход которого соединен с выходом вто рого элемента НЕ 19, первый и третий вертикальные входы 2 и 7 ячейки соекоординатами (i, j + l ) соответственно, 25 динены соответственно с первьм и первьш и второй вертикальные выходы вторым входами второго элемента ИЛИ 5 и 6 и третий вертикальньй вход 7 - 20, подключенными соответственно к с первым и вторым вертикальными входа- одному из входов и второму входу

.ми 2 и 3 и третьим вертикальным выходом 4 ячейки 1 с координатами {i, j-1 ) соответственно, первый и третий горизонтальные входы 8 и 9 и первый горизонтальный вькод 10 - с вторым и третьим горизонтальными.

второго и четвертого элементов И 16 30 и 21, другой и первый входы которых соединены вместе и подключены к выходу первого элемента НЕ 17, а выходы подключены соответственно к первому и третьему вертикальным выходам

выходами 11 и 12 и вторым горизонталь-j и 4 ячейки I, второй горизонталь- Ш)1м входом 13 ячейки 1 с координатами (1-1, j) соответственно,, а второй и третий горизонтальные выходы 11 и 12 и второй горизонтальньй вход 13 - с первым и третьим горизонтальными входами 8 и 9 и первым горизонтальным выходом 10 ячейки 1 с координатами (i+1 , j) соответственно.

ный выход 11 которой соединен с вы- .ходом первого элемента ИЛИ 23, входными каналами коммутатора- являются горизонтальные входы 13 ячеек 1 40 правого стролбца коммутатора,, а .выходными каналами - вертикальные выходы 6 ячеек 1 нижней строки коммутатора.

Ячейка 1 коммутатора содержит первый элемент И 14, третий, элемент НЕ 15, второй элемент И 16, первый элемент НЕ 17, третий элемент И 18, второй элемент НЕ 19, второй элемент ИЛИ 20, четвертьй элемент И 21, пятый элемент И 22, первый элемент ИЛИ 23 и элемент 24 с тремя.устойчивыми состояниями. Входы первого элемента И 14 подключены соответственно к первому горизонтальному входу 8 ячейки I и выходу .второго элемента ИЛИ 20, соединенного с входом второго элемента НЕ 19 и вторым входом пятого элемента И 22, а выход - с входом

2480451

третьего элемента НЕ 15, выход которого соединен с управляющим входом элемента 24 с тремя устойчивыми состояниями, другой вход которого под- 5 ключен к первому горизонтальному выходу 10 ячейки 1, соединенному с вторым горизонтальным входом 13 ячейки 1 , а выход - к соединенным вместе вторым вертикальным входу 3 и выхо- 10 ду 6 ячейки, первьш горизонтальный вход 8 которой подключен к входу первого элемента НЕ 17, соединенного с одним из входов третьего элемента И 18 и первым входом пятого элемента 5 И 22, третий вход которого подключен к соединенным вместе третьим горизонтальным входу 9 и выходу 12 ячейки 1, а выход соединен с одним из входов первого элемента ИЛИ 23, 20 другой вход которого подключен к выходу третьего элемента И 18, второй .вход которого соединен с выходом второго элемента НЕ 19, первый и третий вертикальные входы 2 и 7 ячейки соевторого и четвертого элементов И 16 30 и 21, другой и первый входы которых соединены вместе и подключены к выходу первого элемента НЕ 17, а выходы подключены соответственно к первому и третьему вертикальным выходам

j и 4 ячейки I, второй горизонталь-

ный выход 11 которой соединен с вы- .ходом первого элемента ИЛИ 23, входными каналами коммутатора- являются горизонтальные входы 13 ячеек 1 40 правого стролбца коммутатора,, а .выходными каналами - вертикальные выходы 6 ячеек 1 нижней строки коммутатора.

Элемент с тремя устойчивыми сос- 45 тояниями может быть вьшолнен, например, на микросхеме 533ЛП8.

Коммутатор работает следующим образом.:

50

55

Пусть .коммутатор содержит восемь входных и четыре выходных каналд и требуется соединение второго входного канала с первым выходным каналом, третьего --с вторым, пятого - с третьим, седьмого - с четвертым.

На вертикальные входы 2 ячеек 1 верхней строки коммутатора подаются единичные логические уровни, а на вертикальные входы 7 ячеек 1 нижней

31

строки коммутатора - нулевые логические уровни. На горизонтальные входы 9 ячеек I крайнего левого столбца коммутатора подаются нулевые логические уровни, а на горизонт ль- fuie входы 8 ячеек 1 этого же столбца - код 01101010, причем единичные логические уровни подаются на горизонтальные входы 8 ячеек 1 тех строк коммутатора, соответствующие входные каналы которых требуется коммутировать. На горизонтальный вход 8 ячейки 1, лежащей на пересечении второй строки и первого столбца коммутатора, подан единичный логический уровень, следовательно, на ее вертикальном выходе 5 образуется нулевой логический уровень. Начиная с указанной ячейки 1 нулевой логический уровень образуется на вертикальных выходах 5 всех расположенных ниже ячеек 1 первого столбца. Так как на горизонтальный вход 8 первой ячейки 1 первого столбца подан нулевой логический уровень, то разрешается прохождение единичного логического уровня с вертикального входа 2 этой ячейки 1 на вертикальный вход 2 второй ячейки 1 первого столбца коммутатора. .

Таким образом, только в единственной ячейке 1 первого столбца имеет место одновременная подача единич ных логических уровней на входы 2 и 8, поэтому с выхода элемента И 14, указанной ячейки 1 на вход элемента tffi 15 поступает также единичный логический уровень, а с его выхода на управляющий вход элемента 24 с тремя устойчивыми состояниями - нулевой логический уровень, который разрешает прохрждение информации, поданной на информационный вход элемента 24. В результате информация, поступающая из второго входного канала, поступит в первый выходной канал, что и требуется. На горизонтальном выходе 1 этой же ячейки 1 образуется нулевой логический зФовень, в результате чего на горизонтальные входы 8 ячеек 1 смежного правого (второго) столбца коммутатора подается код 00101010 с погашенной первой единицей. В остальных ячейках 1 первого столбца коммутатора- на управляющие входы элементов 24 с тремя устойчивыми состояниями поступает единичный логический уровень, поэтому элементы 24 этих

480454

ячеек 1 находятся в состоялии с высоким выходным импедансом (в выключенном состоянии) и информация, поступающая из остальных входных кана- 5 лов, не проходит в выбранный ранее первый выходной канал.

Аналогично получается соединение третьего входного канала с вторым выходным каналом, пятого - с третьим

(О и седьмого - с четвертым.

Наличие нулевых логических уровней на горизонтальных входах 9 всех ячеек 1 коммутатора не нарушает логи- ку работы коммутатора.

15 Если на вертикальные входы 2 ячеек 1 верхней строки коммутатора поданы нулевые логические уровни, а на вертикальные входы 7 нижней строки коммутатора - единичные логические

20 уровни, то при коде 01101010 на горизонтальных входах 8 ячеек 1 и нулевых логических уровнях на горизонтальных входах 9 ячеек 1 этого же столбца коммутатора осуществляется

25 соединение седьмого входного канала с первым выходным, пятого - с вторым, третьего - с третьим и второго с четвертым.

Коммутатор в этом случае работает

30 следующим образом. На горизонтальный .вход 8 ячейки I, лежащей на пересечении седьмой строки с первым столбцом коммутатора, подан единичный логический уровень, следовательно, на

35 ее вертикальном выходе 4 образуется нулевой логический уровень. Начиная с указанной ячейки 1 нулевой логический уровень образуется на вертикальных вькодах 4 всех расположенных вы40 ше ячеек 1 первого столбца. На горизонтальный вход 8 восьмой ячейки 1 первого столбца подан нулевой логический уровень, поэтому разрешается прохождение единичного логического

45 уровня с вертикального входа 7 этой ячейки 1 на вертикальный вход 7 седьмой ячейки 1 первого столбца коммутатора. В результате на входах 8 и 7 седьмой ячейки 1 первого

50 столбца имеет место одновременная падача единичных логических уровней, поэтому с выхода элемента НЕ 15 на управляющий вход элемента 24 поступает нулевой логический уровень,

5 разрешающий прохождение информации, поданной на информационный вход элемента 24, т.е. информация, поступающая из седьмого входного канала.

подается через элемент 24 в первый выходной канал, что и требуется. На горизонтальном выходе 11 этой же ячейки 1 образуется нулевой логи- ческий уровень, в результате чего на горизонтальные входы 8 ячеек 1 второго столбца коммутатора подается код 01101000 с погашенной седьмой единицей. В остальных ячейках 1 первого столбца коммутатора на управляющие входы элементов 24 с тремя устойчивыми состояниями поступает единичный логический уровень, поэтому элементы. 24 этих ячеек 1 находятся в состоянии с высоким выходным инпедансом и информация, поспающая из остальных входных каналов не проходит в выбранный ранее первый выходной канал. Соединение пос- ледующих входных каналов коммутатора с выходными каналами осуществляется аналогично. Начили е нулевых логи-. ческих уровней на горизонтальных входах 9 всех ячеек 1 не нарушает логику работы коммутатора.

Пусть, например, требуется осуществить соединение второго входного канала с первым и вторым выходными каналами, а седьмого выходного ка- нала - с третьим и четвертым выходными каналами. Для этого на вертикальные входы 2 и 7 ячеек 1 верхней и нижней строк коммутатора соответственно подаются коды 1100 и 001 На горизонтальные входы 8 и 9 ячеек 1 крайнего левого столбца коммутатора подается код 01000010, причем единичные логические уровни на входах 8 ячеек 1 означают номера вход- ных каналов, соединение которых требуется, а единичные логические уровни на входах 9 ячеек 1 означают, что каждаш из этих входньк каналов (второй и седьмой) требуется соединить с несколькими выходными- каналами одновременно .

Количество подключенных выходных каналов определяется количеством единиц в кодах, подаваемых соответ- ственно на вертикальные входы 2 и 7 ячеек 1 верхней и нижней строк коммутатора.

На горизонтальный вход 8 первой ячейки 1 первого столбца подан нуле- вой логический уровень, который проходит на входы 8 всех ячеек 1 первой строки коммутатора, а на вертикальные входы 2 ячеек 1 верхней строки коммутатора - код 1100, в результате чего на вертикальные входы 2 ячеек 1 второй строки коммутатора поступает код 1100. Так как на горизонтальные входы 8 и 9 второй ячейки

1первого столбца поданы единичные логические уровни, то на горизонтальных входах 8 и 9 всех ячеек 1 второй строки коммутатора образуются единичные логические уровни, а на вертикальных выходах 5 всех ячеек 1 второй строки - нулевые логические уровни. Начиная с этой строки нулевые логические уровни образуются на вертикальных выходах 5 ячеек 1 .всех расположенных ниже строк.

В результате в первых двух ячейках 1 второй строки коммутатора имее место одновременная подача единичных логических уровней на входы 2 и 8, поэтому с выходов элементов НЕ 15 на управляющие входы элементов 24 поступают нулевые логические уровни, разрешающие прохрждение информации, поданной на информационные входы элементов 24, из второго входного канала в первый и второй выходные ка- налы. По отнощению к нижней и седьмой строкам коммутатора аналогично получается соединение седьмого входного канала с третьим и четвертым выходным каналами. В остальных ячейках 1 коммутатора на управляющие входы элементов 24 поступает единичный логический уровень, поэтому элементы 24 этих 1 находятся в третьем (выключенном) состоянии и информаци поступающая из остальных входных каналов, не проходит в выбранные ранее первьй, .второй, третий и четвертый выходные каналы соответственно.

Таким образом, каждому значению кода, поданного на вертикальный вход

2ячеек 1 верхней строки коммутатора и одновременно поданному инверсному значению этого же кода на- вертикальные входы 7 ячеек 1 нижней строки коммутатора в зависимости от значений кодов, подаваемых на горизонтальные входы 8 и 9 ячеек 1 первого столбца коммутатора, соответствует определенный порядок соединения входных каналов с выходными каналами коммутатора.

I

Сокращение числа логических эле- , ментов, через которые поступает ком

мутируемая информация с входа на выход коммутатора, обеспечивает ловы- шение быстродействия предлагаемого коммутатора.

Формула изобретения

Коммутатор, содержащий идентичные ячейки, расположенные в узлах двумерной решетки и идентично соединенные между собой, каждая из которых содержит элементы И, ШШ и НЕ, причем в каждой ячейке первый и третий вертикальные входы соединены сеответственно с первым и вторым входами второго элемента ИЛИ, подключенных соответственно к одному из входов и второму входу второго и четвертого элементов И, другой и первый входы которых соединены вместе и подключены, к выходу первого элемента НЕ, а выходы подключены соответственно к первому и третьему вертикальным выходам ячейки, первые горизонтальные выход и вход которой соединены соответственно с вторым горизонтальным входом ячейки и входом первого элемента НЕ, соединенного с одним из входов первого и третьего элементов И и первым входом пятого элемента И, второй и третий входы которого подключены соответственно к выходу второго элемента ИЛИ, соединенного с другим входом первого элемента И и через второй элемент НЕ с вторым входом третьего элемента И, и третьему горизонтальному входу ячейки, соединенному с третьим гори48045

зонтальным выходом ячейки,- а выход подключен к одному из входов первого элемента ИЛИ, другой вход которого соединен с выходом третьего элемента

5 И, а выход - с вторым горизонтальным выходом ячейки, причем первый, второй и третий вертикальные входы и выход и первый, второй и третий вертикальные выход и вход ячейки с

О координатами (1, j) подключены к

первому, второму и третьему верти ; . кальным выходам и входу и первому, второму и третьему вертикальным входам и выходу ячеек с координатами

fS (i, j + 1) и (1, j-1 ) соответственно, первый, третий и первый горизонтальные входы.и выход и второй, третий и второй горизонтальные выходы и вход - к второму, третьему и второму

20 горизонтальным выходам и входу и первому, третьему и первому горизонтальным входам и выходу ячеек с координатами (i-1, j ) (i+1 , j) соответственно, отличающийся

25 тем, что, с целью повышения быстродействия, в каждую ячейку коммутатора дополнительна введены элемент с тремя устойчивыми состояниями и третий элемент НЕ, вход и выход которо30 го соединены соответственно с выходом первого элемента И и управляющим входом элемента с тремя устойчивыми состояниями, информационный, вход которого подключен к первому

35 горизонтальному выходу ячейки, а вы- ход - к соединенным вместе вторым вертикальным входу и выходу ячейки.

ш

-

ш

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутатор | 1983 |

|

SU1140241A2 |

| Коммутатор | 1981 |

|

SU1003336A1 |

| Коммутатор | 1976 |

|

SU558399A1 |

| Коммутатор | 1986 |

|

SU1314332A2 |

| Коммутатор | 1983 |

|

SU1120313A1 |

| Ячейка однородной среды | 1982 |

|

SU1013943A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Ячейка однородной структуры | 1989 |

|

SU1674104A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU949721A1 |

| Устройство для отображения информации | 1987 |

|

SU1443024A1 |

Изобретение относится к области автоматики и вычислительной техники. Может быть использовано для коммутации каналов ввода-вывода информации цифровых устройств. Цель изобретения - повышение быстродействия. Устройство содержит идентичнЬ1е ячейки 1, расположенные в узлах двумерной решетки и идентично соединенные между собой. Для достижения цепи в каждую ячейку 1, содержащую элементы И 14, 16, 18, 21, 22, элементы РШИ 23, 20, элементы НЕ 17, 19 введены элемент НЕ 15 и элемент 24 с тремя устойчивыми состояниями. Эле- мент с тремя устойчивыми состояниями может быть выполнен на микросхеме 533ЛГ8. Функциональная схема и работа коммутатора приводятся в описании изобретения. Технический эффект от использования данного изобретения заключается в повьш1ении быстродействия за счет сокращения числа логических элементов, через которые поступает коммутируемая информация с входа на выход коммутатора. 2 ил. J i (Л

Ш W

Фиг. 7

Редактор А. Лежнина

Составитель С. Куст Техред Э.Чижмар

Заказ 4140/57 . Тираж 816Подписное

ВНШШИ Государственного ко штета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

. .

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

W

Корректор А. Обручар

| Коммутатор | 1981 |

|

SU1003336A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Коммутатор | 1983 |

|

SU1140241A2 |

Авторы

Даты

1986-07-30—Публикация

1985-02-25—Подача