MU

соединен со счетным входом четвертого счетчика, выходы разрядов первог и второго счетчиков объединены и соединены с первыми информационными входами первого и второго коммутаторов, выходы разрядов третьего и четвертого счетчиков объединены и соединены с вторьми информационными входами первого и второго коммутаторов, вход управления первого коммутатора объединен с входом инвертора и является управляющим входом блока управления адресацией запоминающих блоков, выход инвертора подключен к входу управления второго коммутатора, группа выходов второго коммутатора и группа выходов первог коммутатора являются соответственно первыми и вторыми группами выходов блока управления адресацией запо минающих блоков, счетный вход и установочный вход первого счетчика, установочный вход второго счетчика являются соответственно первым, вторым и третьим входами блока управления адресацией запоминающих

блоков, счетный вход и установочный вход четвертого счетчика, установочный вход третьего счетчика являются соответственно четвертьпу, пятым и шестым входами блока управления адресацией запоминаюпщх блоков.

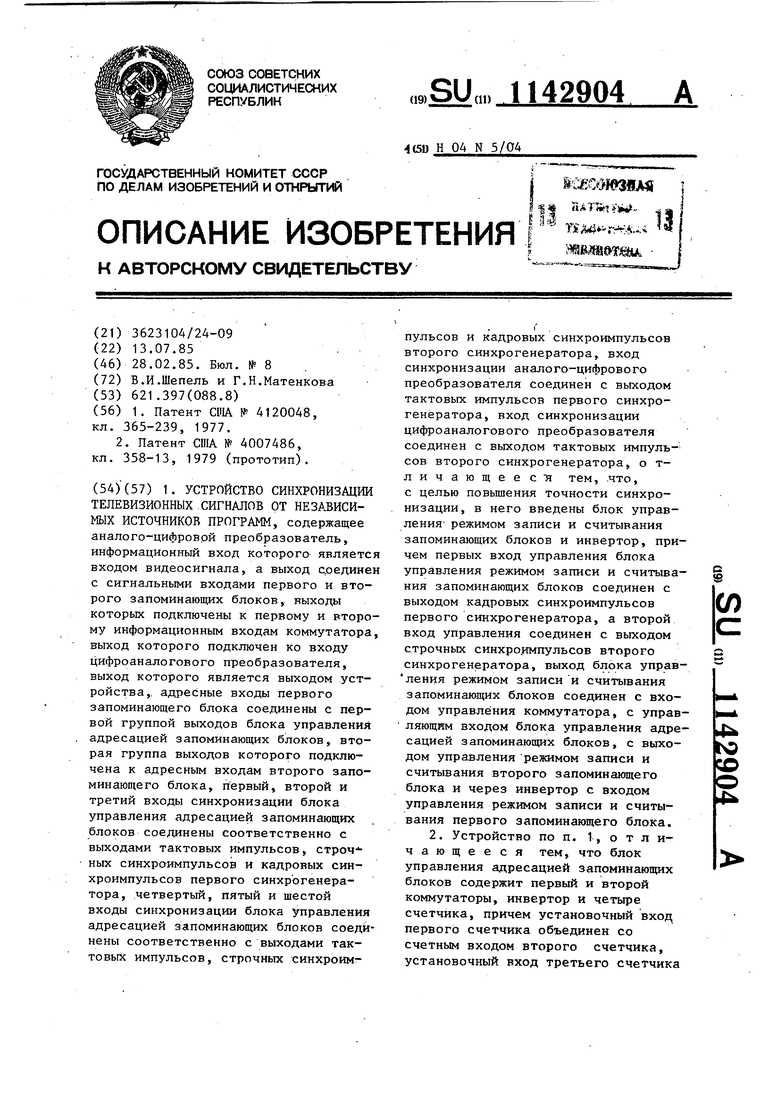

3. Устройство по п. 1, о т л ичающееся тем, что блок управления режимом записи и считывания запоминающих блоков содержит первыйи второй триггеры и элементИ первый вход элемента И, объединенный с первым установочным входом первого триггера, и второй вход элемента И являются соответственно первьм и вторым входами управления блока управления режимом записи и считывания запоминаюпщх блоков, выход элемента И соединен с вторым установочньП Г входом первого триггера, выход первого триггера соединен с входом второго триггера, выход которого является выходом блока управления режимом, записи и считывания запоминающих блоков.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для проверки электрического монтажа | 1986 |

|

SU1336035A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1987 |

|

SU1494778A1 |

| Устройство для диагностирования телевизионной аппаратуры | 1983 |

|

SU1124330A1 |

| Устройство для обработки видеоинформации | 1986 |

|

SU1322320A1 |

| Многоканальная система для морских сейсмических исследований | 1981 |

|

SU949587A2 |

| Преобразователь телевизионного стандарта | 1980 |

|

SU1238267A1 |

| УСТРОЙСТВО ДЛЯ ДИАГНОСТИРОВАНИЯ ТЕЛЕВИЗИОННОЙ АППАРАТУРЫ | 1989 |

|

RU2050700C1 |

| Устройство для отображения информации на экране телевизионного приемника | 1987 |

|

SU1522271A1 |

| Устройство для воспроизведения изображения | 1980 |

|

SU1085014A1 |

| Спироанализатор | 1986 |

|

SU1391621A1 |

1. УСТРОЙСТВО СИНХРОНИЗАЦИИ ТЕЛЕВИЗИОННЫХ СИГНАЛОВ ОТ НЕЗАВИСИМЫХ ИСТОЧНИКОВ ПРОГРАММ, содержащее аналого-цифровой преобразователь, информационный вход которого является входом видеосигнала, а выход с оединен с сигнальными входами первого и второго запоминающих блоков, выходы которых подключены к первому и второму информационным входам коммутатора, выход которого подключен ко входу цифроаналогового преобразователя, выход которого является выходом устройства,, адресные входы первого запоминающего блока соединены с первой группой выходов блока управления адресацией запоминающих блоков, вторая группа выходов которого подключена к адресным входам второго запоминающего блока, первый, второй и третий входы синхронизации блока управления адресацией запоминающих блоков соединены соответственно с выходами тактовых импульсов, строчных синхроимпульсов и кадровых синхроимпульсов первого синхрогенератора, .четвертый, пятый и шестой входы синхронизации блока управления адресацией запоминающих блоков соединены соответственно с выходами тактовых импульсов, строчных синхроимпульсов и кадровых синхроимпульсов второго синхрогенератора, вход синхронизации аналого-цифрового преобразователя соединен с выходом тактовых импульсов первого синхрогенератора, вход синхронизации цифроаналогового преобразователя соединен с выходом тактовых импульсов второго синхрогенератора, о т- личающее ся тем, .что, с целью повышения точности синхронизации, в него введены блок управления- режимом записи и считывания запоминающих блоков и инвертор, причем первых вход управления блока § управления режимом записи и считывания запоминающих блоков соединен с (Л выходом кадровых синхроимпульсов первого синхрогенератора, а второй вход управления соединен с выходом строчных синхроимпульсов второго синхрогенератора, выход блока управления режимом записи и считывания запоминающих блоков соединен с входом управления коммутатора, с управляющим входом блока управления адресацией запоминающих блоков, с выходом управления режимом записи и считывания второго запоминающего блока и через инвертор с входом управления режимом записи и считывания первого запоминающего блока. 2. Устройство по п. 1, о т л ичающееся тем, что блок управления адресацией запоминающих блоков содержит первый и второй коммутаторы, инвертор и четыре счетчика, причем установочный вход первого счетчика объединен со счетным входом второго счетчика, установочный вход третьего счетчика

Изобретение относится к промышленности средств связи и может быть использовано при построении устройст синхронизации телевизионных сигналов от независимых источников программ в системе аппаратно-студийного комплекса телевизионного центра.

Известно устройство синхронизации телевизионных сигналов от независимых источников программ, содержащее запоминающий блок, выход которого подключен к одному из входов элемента И,второй вход которого соединен с первым выходом блока управления, второй выход которого подключен к входу управления запоминающего блока, вход запоминающего блока соединен с выходом аналого-цифрового преобразователя, выход элемента И соединен с входом цифроаналогового преобразователя, входы блока управления соединены соответственно с выходами первого и второго синхрогенераторов LO.

Недостаток этого устройства низкая точность синхронизации, обусловленная тем, что в запоминающем блоке происходит задержка сигнала до тех пор, пока на его вход управления не поступит с выхода блока управления сигнал адреса считывания определяющий номер нужной ячейки запоминающего блока. Таким образом, происходит задержка на время одного периода к запоминающему |блоку, что приводит к рассогласованию фазы вЗДеосигнала на выходе устройства относительно фазы синхроимпульсов телецентра.

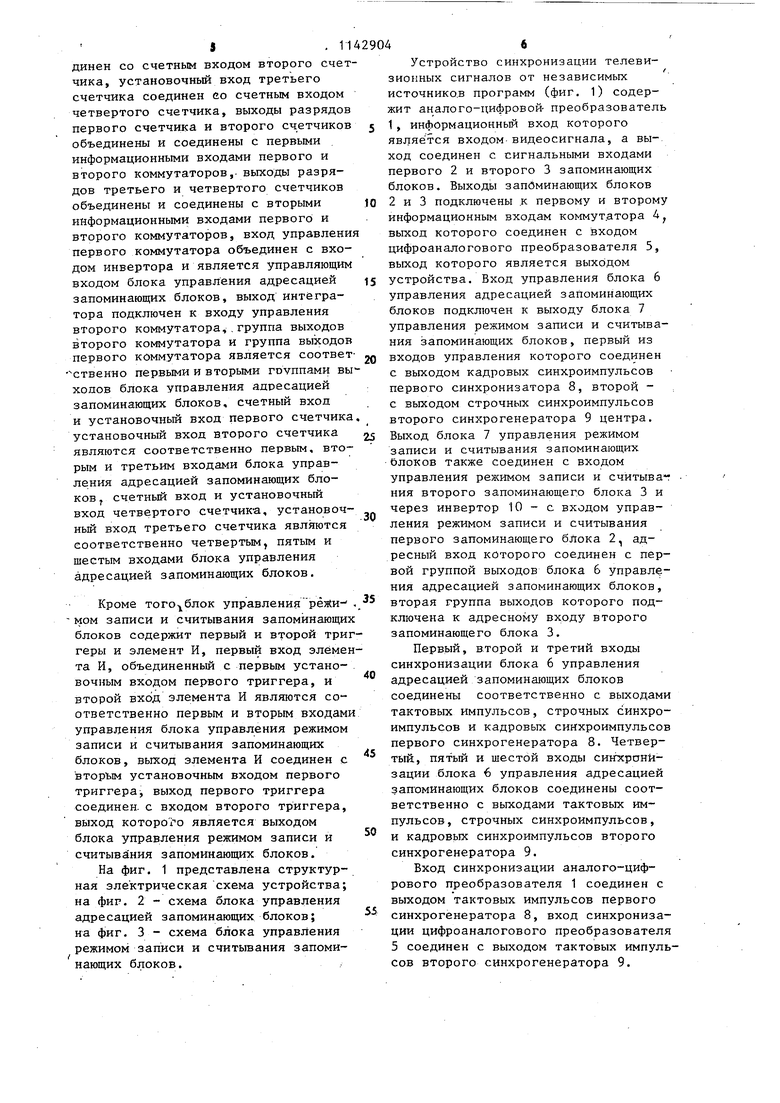

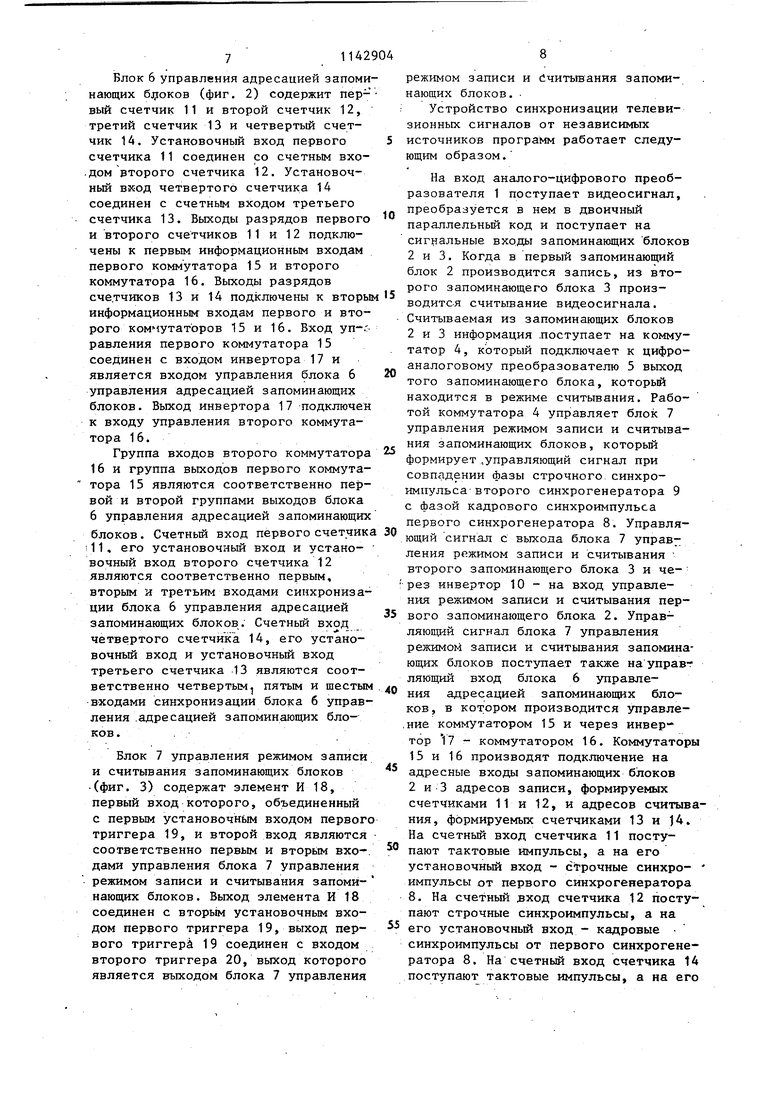

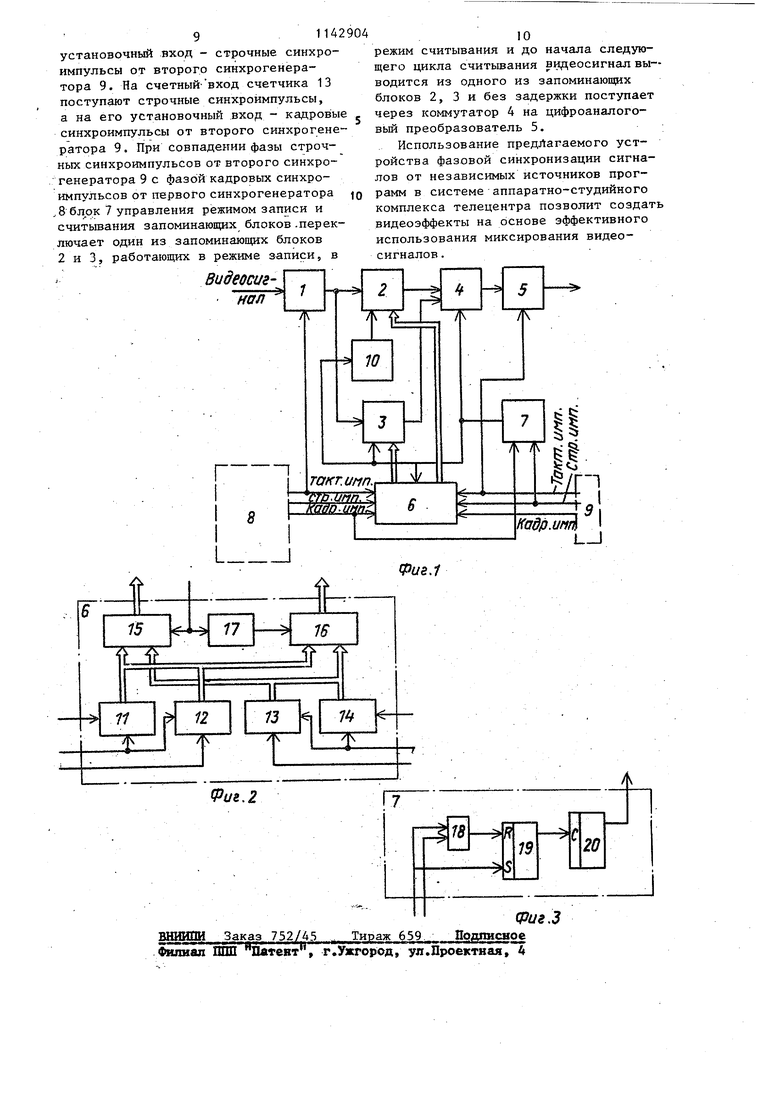

Наиболее близким по технической сущности к предлагаемому является устройство синхронизации телевизионных сигналов от независимых источников программ, содержащее запоминающие блоки, сигнальные входы которых соединены с выходами аналогоцифрового преобразователя, информа1ДИОННЫЙ вход которого является входо видеосигнала, выходы запоминающих блоков подключены к информационным входам коммутатора, выход которого подключен к входу цифроаналогового преобразователя, выход которого является выходом устройства, адресны входы запоминающих блоков соединены с соответствуюпщми группами выходов блока управления адресацией запоминающих блоков, первый, второй и третий входы синхронизации которого соединены соответственно с выходами тактовых импульсов, строчных синхроимпульсов и кадровых синхроимпульсов первого синхрогенератора, четвертый пятый и шестой.входы синхронизации блока управления адресацией запоминающих блоков соединены соответствен но с выходами тактовых импульсов, строчных синхроимпульсов и кадровых синхроимпульсов второго синхрогенератора, вход синхронизации аналогоцифрового преобразователя соединен с выходом тактовых импульсов первого синхрогенератора, вход синхронизации цифроанзЬюгового преобразователя соединен с выходом тактовых импульсов второго синхрогенератора ), Недостатком этого устройства является низкая точность синхронизации, обусловленная тем, что в зап минающих блоках происходит повторна перезапись считанного из запоминающи блоков сигнала, его хранение до сле дующего цикла считывания информации из запоминающих блоков. Таким обра- зом, происходит задержка сигнала, равная времени передачи одной телевизионной строки (64 мкс). При тако задержке считывания ввдеосигнапа и запоминающих блоков происходит задержка видеосигнала относительно фазы строчных синхроимпульсов теле1(ёнтра, а следовательно, рассогласо вание фазы видеосигнала на выходе устройства относительно синхроимпул сов телецентра, что приводит к низ|Шей точности синхронизации на выход (устройства. Цель изобретения - повышение точности синхронизации. Поставленная цель достигается тем, что в устройство синхронизации телевизионных сигналов от независимых источников программ, содержащее аналого-цифровой преобразователь, информационный вход которого является входом видеосигнала, а выход соединен с сигнальными входами первого и второго запоминающих блоков, выходы которых подключены к первому и второму информационным входам коммутатора, выход которого подключен к входу цифроаналогового преобразователя, выход которого является выходом устройства, адресные входы первого запоминающего блока соединены с первой группой выходов блока управления адресацией запоминающих блоков, вторая группа выходов которого подключена к адресным входам второго запоминающего блока, первый, второй и третий входы синхронизации блока управления адресацией запоминающих блоков соединены соответственно с выходами тактовых импульсов, строчных синхроимпульсов и кадровых синхроимпульсов первого синхрогене- ратора, четвертый, пятый и шестой входы синхронизации блока управления адресацией запоминающих блоков соединены соответственно с выходами тактовых импульсов, строчных синхроимпульсов и кадровых синхроимпульсов второго синхрогенератора,-выход синхронизации аналого-цифрового преобразователя соединен с выходом тактовых импульсов первого синхрогенератора, вход синхронизации цифроаналогового преобразователя соединен с выходом тактовых импульсов второго синхрогенератора,. введены блок управления режимом записи и считывания , запоминающих блоков и инвертор, причем вход управления блока управления режимом записи и считьшания запоминающих блоков соединен с выходом кадровых синхроимпульсов первого синхрогенератора, а второй вход управления соединен с выходом строч-ных с инхроимпульсов второго синхрогенератора, выход блока управления режимом записи и считьгоания запоминающих блоков соединен с входом управления коммутатора, с управляющим входом блока управления адресацией запоминающих блоков, с выходом управления режимом записи и считывания второго запоминающего блока и через инвертор с входом управления режимом записи и считьшания первого запоминающего блока. При этом блок управления адресацией запоминающих блоков содержит первый и второй коммутаторы, инвертор и четыре счетчика, причем установочный вход первого счетчика объеS. 11 динен со счетным входом второго счет чика, установочный вход третьего счетчика соединен со счетным входом четвертого счетчика, выходы разрядов первого счетчика и второго счетчиков объединены и соединены с первыми информационными входами первого и второго коммутаторов,, выходы разрядов третьего и четвертого счетчиков объединены и соединены с вторыми информационными входами первого и второго коммутаторов, вход управлени первого коммутатора объединен с входом инвертора и является управляющим входом блока управления адресацией запоминающих блоков, выход интегратора подключен к входу управления второго коммутатора,,группа выходов второго коммутатора и группа выходов первого коммутатора является соответ ственно первыми и вторыми гоуппами вы хопов блока управления адресацией запоминающих блоков, счетный вход и установочный вход первого счетчика установочный вход второго счетчика являются соответственно первым, вторым и третьим входами блока управления адресацией запоминающих блоков J счетный вход и установочный вход четвертого счетчика, установочный вход третьего счетчика являются соответственно четвертым, пятым и шестым входами блока управления адресацией запоминающих блоков. Кроме управления рёжи- мом записи и считывания запоминающи блоков содержит первый и второй три геры и элемент И, первый вход элеме та И, объединенный с первым установочным входом первого триггера, и второй вход элемента И являются соответственно первым и вторым входам управления блока управления режимом записи и считывания запоминающих блоков, выход элемента И соединен с вторЪм установочным входом первого триггера выход первого триггера соединен, с входом второго триггера, выход которого является выходом блока управления режимом записи и считывания запоминающих блоков. На фиг. 1 представлена структурная электрическая схема устройства; на фиг. 2 - схема блока управления адресацией запоминающих блоков; на фиг. 3 - схема блока управления режимом записи и считывания запоминающих блоков. 4 Устройство синхронизации телевизионных сигналов от независимых источнико.в программ (фиг, 1) содержит аналого-цифровой- преобразователь 1, информационный вход которого является входом-видеосигнала, а выход Соединен с сигнальными входами первого 2 и второго 3 запоминающих блоков. Выходы запоминающих блоков 2 и 3 подключены к первому и второму информационным входам коммут.атора 4 выход которого соединен с входом цифроаналогового преобразователя 5, выход которого является выходом устройства. Вход управления блока 6 управления адресацией запоминающих блоков подключен к выходу блока 7 управления режимом записи и считывания запоминающих блоков, первый из входов управления которого соединен с выходом кадровых синхроимпульсов первого синхронизатора 8, второй с выходом строчных синхроимпульсов второго синхрогенератора 9 центра. Выход блока 7 управления режимом записи и считывания запоминающих блоков также соединен с входом управления режимом записи и считывав ния второго запоминающего блока 3 и через инвертор 10 - с входом управления режимом записи и считывания первого запоминающего блока 2, адресный вход которого соединен с первой группой выходов блока 6 управл.ния адресацией запоминающих блоков. вторая группа выходов которого подключена к адресному входу второго запоминающего блока 3. Первый, второй и третий входы синхронизации блока 6 управления адресацией запоминающих блоков соединены соответственно с выходами тактовых импульсов, строчных синхроимпульсов и кадровых синхроимпульсов первого синхрогенератора 8. Четвертый, пятый и шестой входы синхронизации блока 6 управления адресацией запоминающих блоков соединены соответственно с выходами тактовых импульсов, строчных синхроимпульсов, и кадровьгх синхроимпульсов второго синхрогенератора 9. Вход синхронизации аналого-цифрового преобразователя 1 соединен с выходом тактовых импульсов первого синхрогенератора 8, вход синхронизации цифроаналогового преобразователя 5 соединен с выходом тактовых импульсов второго синхрогенератора 9.

71142

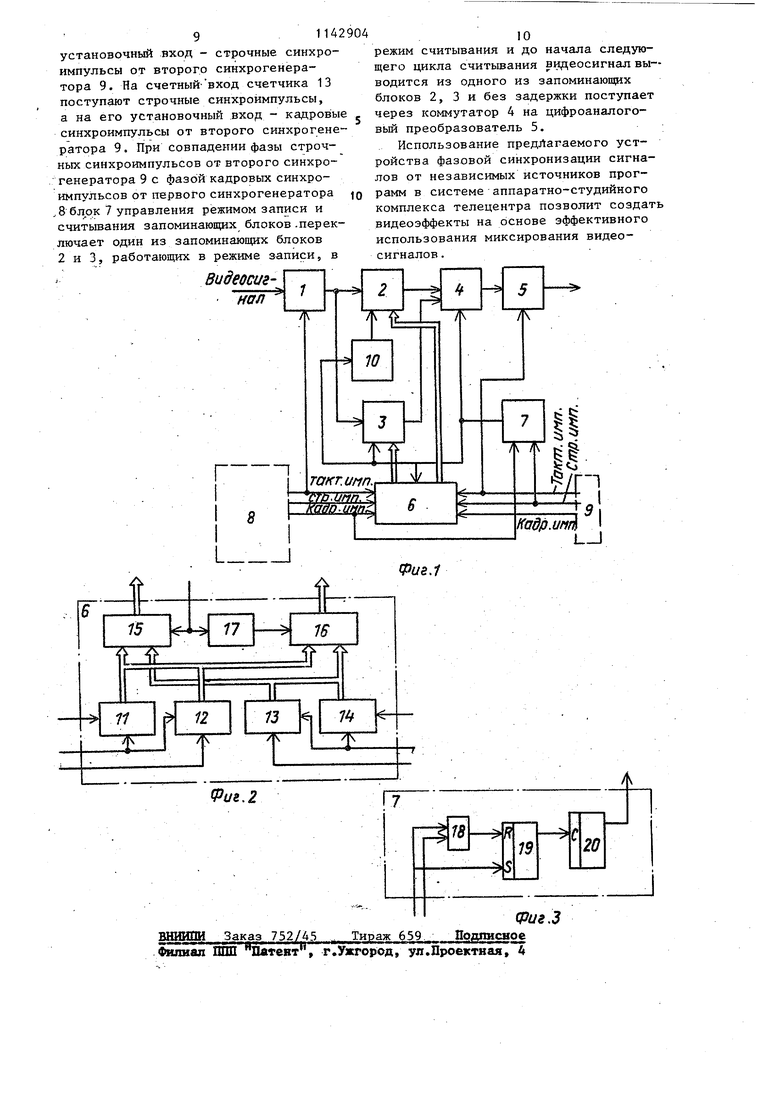

Блок 6 управления адресацией запоминающих 6jjoKOB (фиг. 2) содержит первый счетчик 11 и второй счетчик 12, третий счетчик 13 и четверть счетчик 14. Установочный вход первого счетчика 11 соединен со счетным вхо.дом второго счетчика 12. Установочный вкод четвертого счетчика 14 соединен с счетным входом третьего счетчика 13. Выходы разрядов первого и второго счетчиков 11 и 12 подключены к первым информационным входам первого коммутатора 15 и второго коммутатора 16. Выходы разрядов сче.тчиков 13 и 14 подключены к вторы информационным входам первого и второго коммутаторов 15 и 16. Вход уп-. равления первого коммутатора 15 соединен с входом инвертора 17 и является входом управления блока 6 управления адресацией запоминающих блоков. Выход инвертора 17 подключен к входу управления второго коммутатора 16.

Группа входов второго коммутатора 16 и группа выходов первого коммутатора 15 являются соответственно первой и второй группами выходов блока 6 управления адресацией запоминающих блоков. Счетный вход первого счетчик ill, его установочный вход и установочный вход второго счетчика 12 являются соответственно первым, вторым и третьим входами синхронизации блока 6 управления адресацией запоминающих блоков. Счетный вход четвертого счетчика 14, его установочный вход и установочный вход третьего счетчика 13 являются соответственно четвертым пятым и шестым входами синхронизации блока б управления .адресацией запоминающих блоков. .

Влок 7 управления режимом записи и считывания запоминающих блоков (фиг. 3) содержат элемент И 18, первый вход которого, объединенный с первым установочным входом первого триггера 19, и второй вход являются соответственно первым и вторым вхо дами управления блока 7 управления режимом записи и считывания запоминающих блоков. Выход элемента И 18 соединен с вторь1м установочным входом первого триггера 19, выход первого триггера 19 соединен с входом второго триггера 20, выход которого является выходом блока 7 управления

В

режимом записи и Считывания запоминающих блоков. .

Устройство синхронизации телевизионных сигналов от независимых источников программ работает следующим образом.

На вход аналого-цифрового преобразователя 1 поступает видеосигнал, преобразуется в нем в двоичный параллельный код и поступает на сигнальные входы запоминающих блоков 2 и 3. Когда в первый запоминающий блок 2 производится запись, из второго запоминающего блока 3 производится считывание видеосигнала. Считываемая из запоминающих блоков 2 и 3 информация .поступает на коммутатор 4, который подключает к цифроаналоговому преобразователю 5 выход того запоминающего блока, который находится в режиме считывания. Работой коммутатора 4 управляет блок 7 управления режимом записи и считывания запоминающих блоков, которьй формирует „управляющий сигнал при совпадении фазы строчного синхроимпульса второго синхрогенератора 9 с фазой кадрового синхроимпульса первого синхрогенератора 8. Управляющий сигнал с выхода блока 7 управления режимом записи и считывания второго запоминающего блока 3 и через инвертор 10 - на вход управления режимом записи и считывания первого запоминающего блока 2. Управляющий сигнал блока 7 управления регкимой записи и считывания запоминающих блоков поступает также на управг ляющий вход блока 6 управления адресацией запоминающих блоков , в котором производится управле, ние коммутатором 15 и через инвертор 17 - коммутатором 16. Коммутатор 15 и 16 производят подключение на адресные входы запоминающих блоков 2 и 3 адресов записи, формируемых счетчиками 11 и 12, и адресов считывния, формируемых счетчиками 13 и 14. На счетный вход счетчика 11 поступают тактовые импульсы, а на его установочный вход - строчные синхроимпульсы от первого синхрогенератора 8. На счетный зход счетчика 12 поступают строчные синхроимпульсы, а на его установочный вход - кадровые синхроимпульсы от первого синхрогенератора 8. На счетный вход счетчика 1 поступают тактовые импульсы, а на ег

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 4120048, кл | |||

| Станок для нарезания зубьев на гребнях | 1921 |

|

SU365A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 4007486, кл | |||

| Зажим для канатной тяги | 1919 |

|

SU358A1 |

Авторы

Даты

1985-02-28—Публикация

1983-07-13—Подача