члключается в иодготс вке информации небольшого числа элементов рязложе- ния входной развертки к записи в БП 8. При этом входной видеосигнал через АЦП i 2 поступает на блок буферной памяти (ББП) 5 и записывается в него по импульсам стробирования, поступающим с распределителя 1 временных интервалов. Сигналы адреса

Изобретение относится к телевидению и мржет быть использовано при построении устройств сопряжения скорости развертки малокадровых телевизионных (ТВ) систем с системами скорость развертки которых близка к вещательному стандарту, а также при построении устройств вывода информации для получения на экране вещательного видеоконтрольного устройства изображения объекта, исследуемого при noMODyi радиолокатора или гидроакустических устройств.

Целью .изобретения является повышение точности преобразования сигнала при произвольных соотношениях и изменении частот входной и выходной разверток.

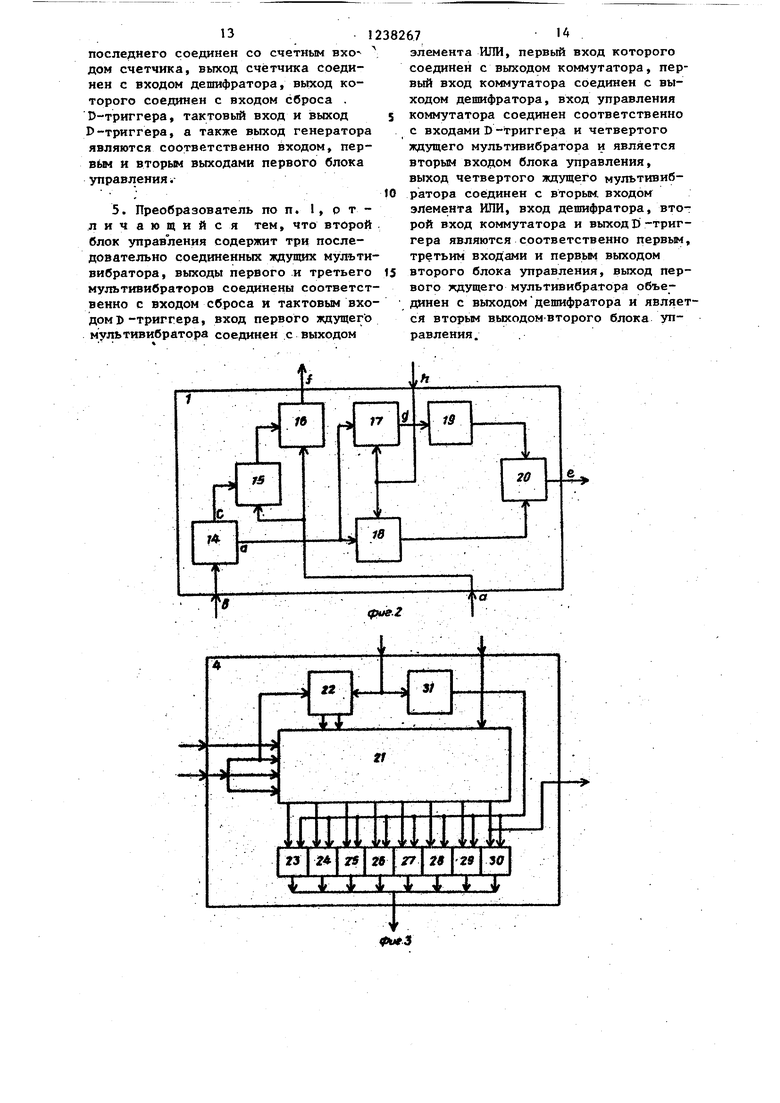

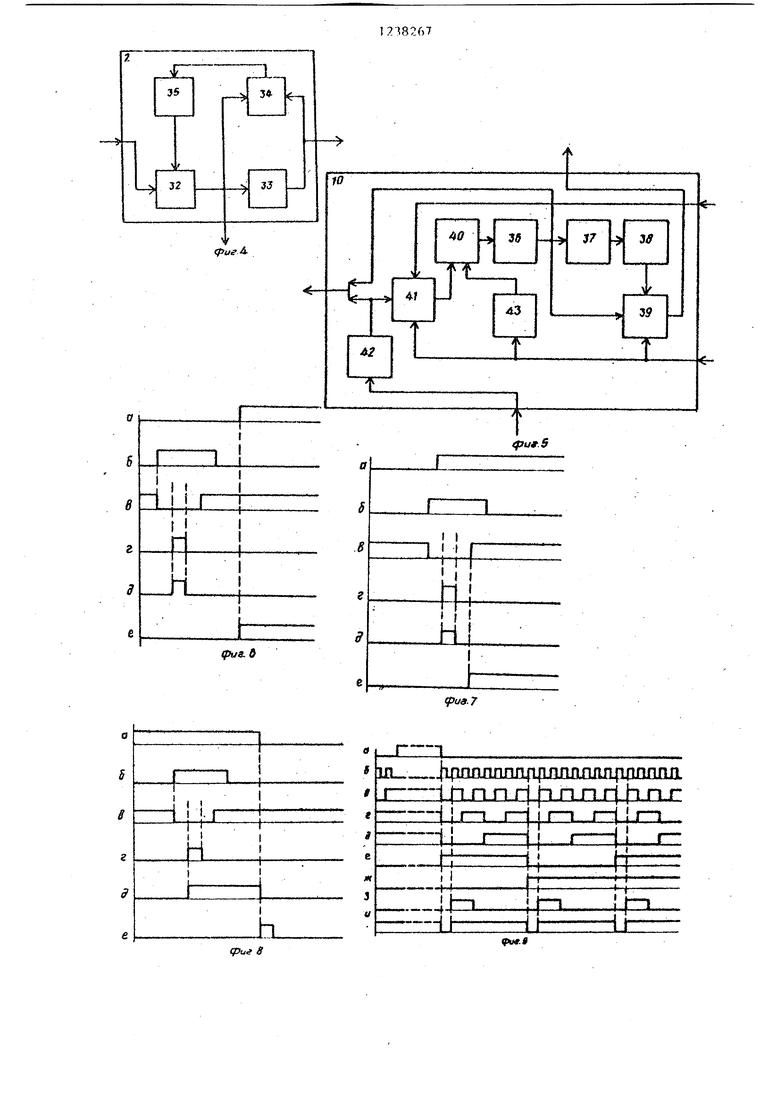

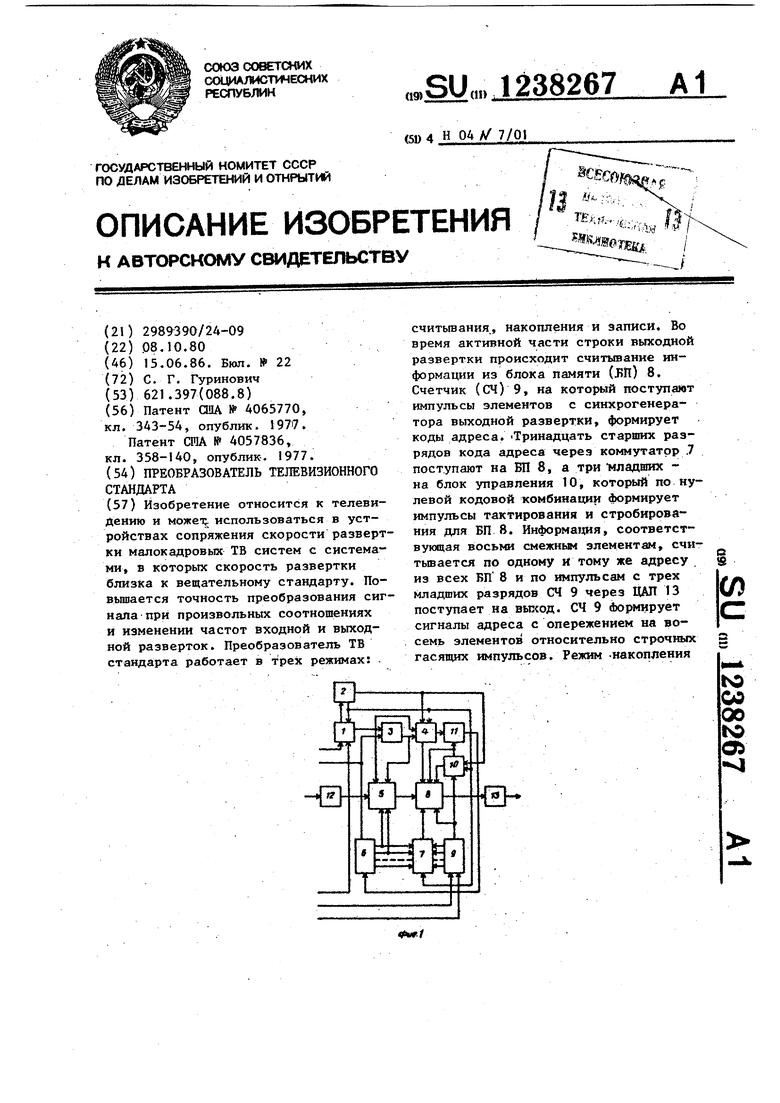

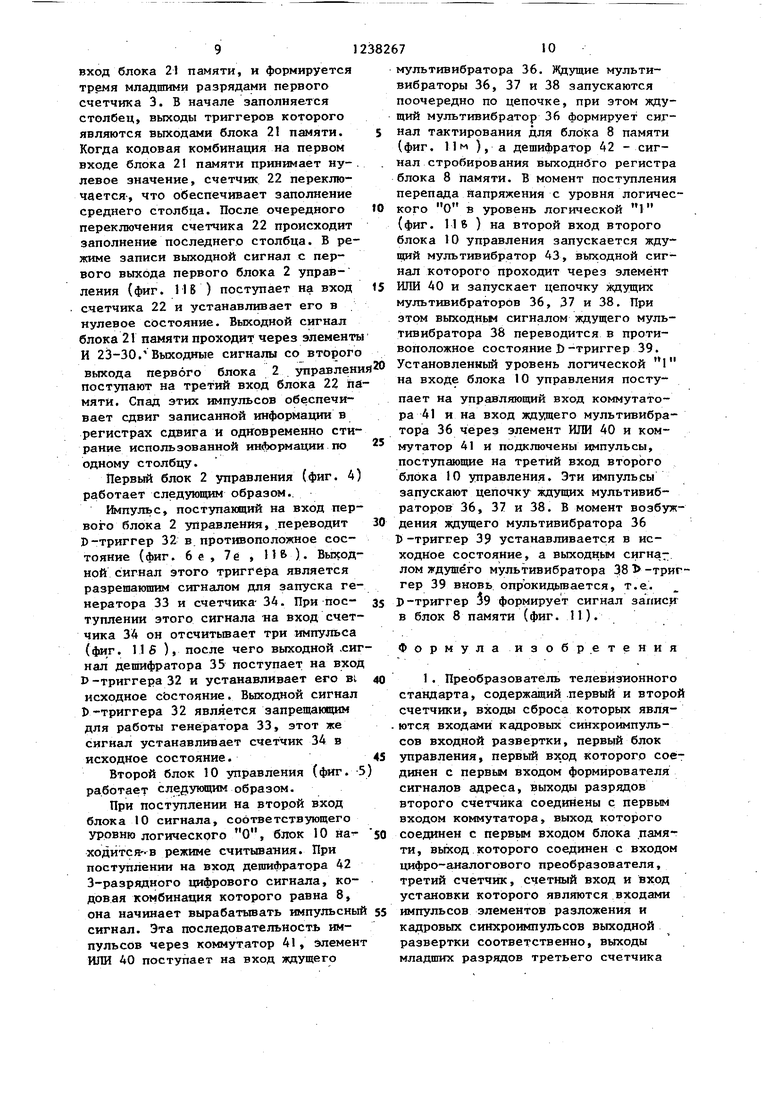

На фиг. I приведена структурная электрическая схема преобразователя ТВ стандарта; на фиг. 2 - то же, распределителя временных интервалов; на фиг. 3 - то же, формирователя сигнала адреса; на фиг. 4 - то же, первого блока управления; на фиг. 5 - то же, второго блока управления; на фиг. 6-11 - эпюры напряжений.

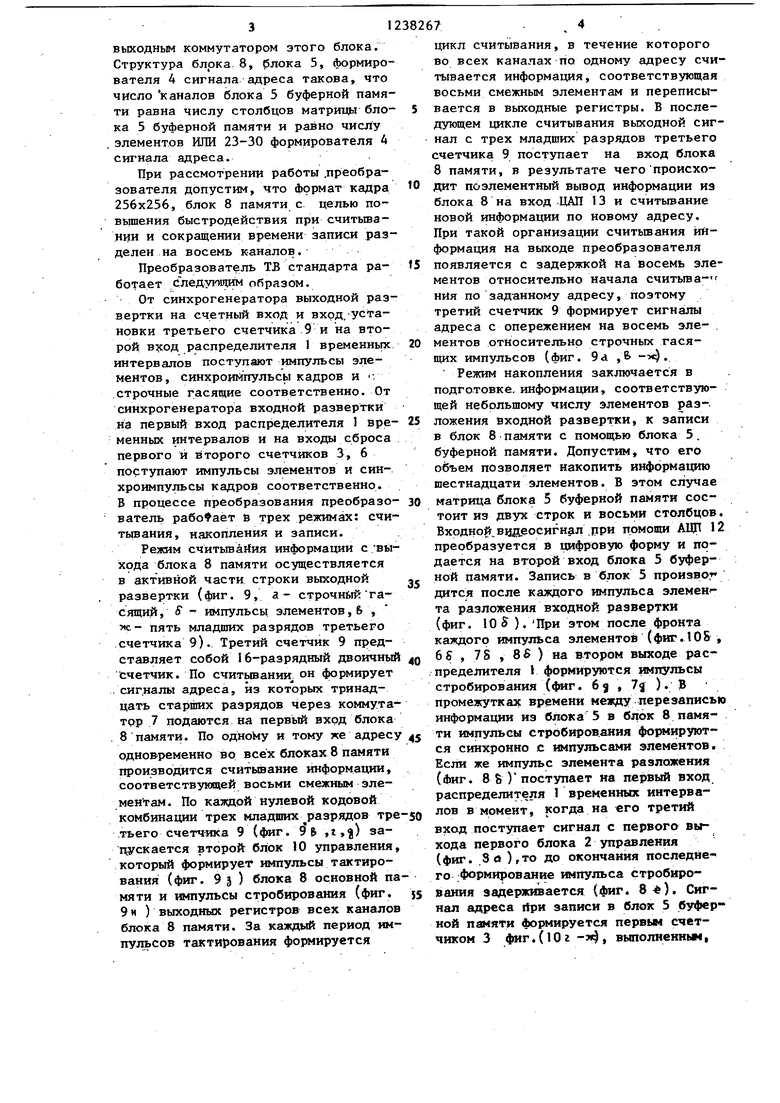

Преобразователь ТВ стандарта (фиг, 1) содержит распределитель 1 временных интервалов, первый блок 2 управления, первый счетчик 3, формирователь 4 сигнала адреса, блок 5 буферной памяти, второй счётчик 6, коммутатор 7, блок 8 памяти, третий счетчик 9, второй блок 10 управления элемент И t1, аналого-цифровой преобразователь (АЦП) 12 и цифро-аналоговый преобразователь (ЦАП) 13,

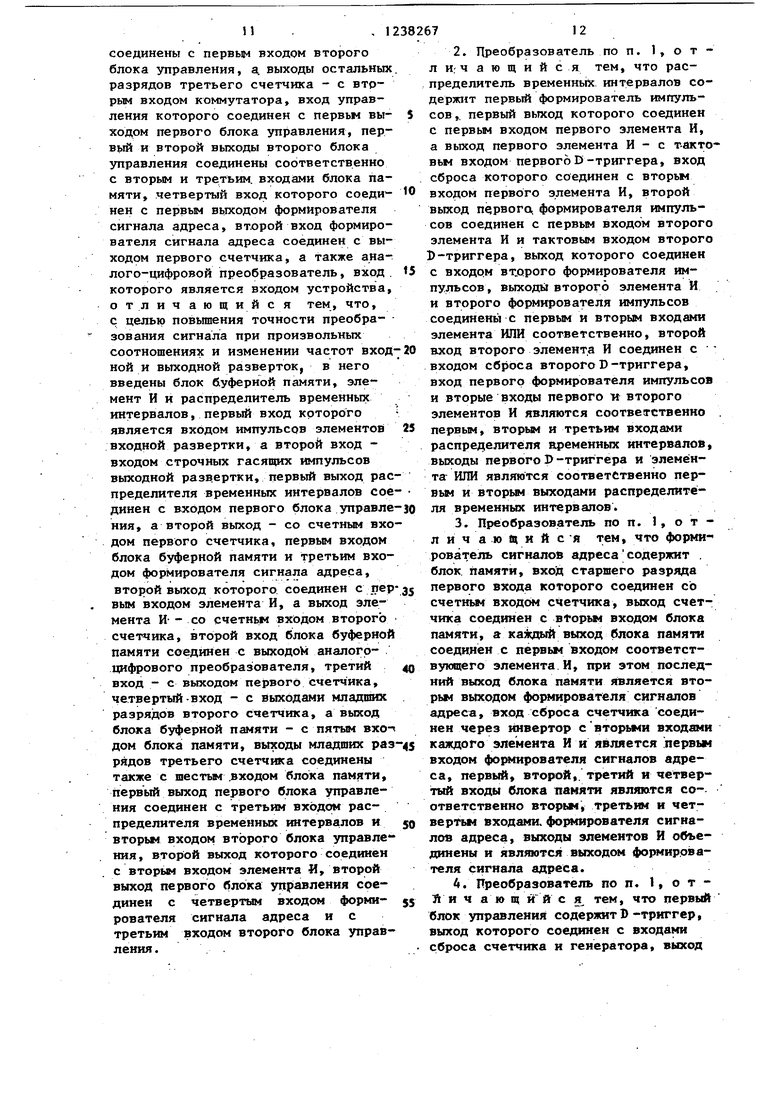

Распределитель 1 временных интервалов (фиг. 2) содержит первый формирователь 14 импульсов, первьй эледля Blin 5 формирует СЧ 3. Формирователь 4 сигнала адреса регистрирует каждый накопленный элемент и составляет программу, по которой информация распределяется в БП 8. В режиме записи накопленная информация перепи- сывается из ББП 5 в БП 8 в течение строчного гасящего импульса выходной развертки. 4 з,п. ф-ль1, 1) ил.

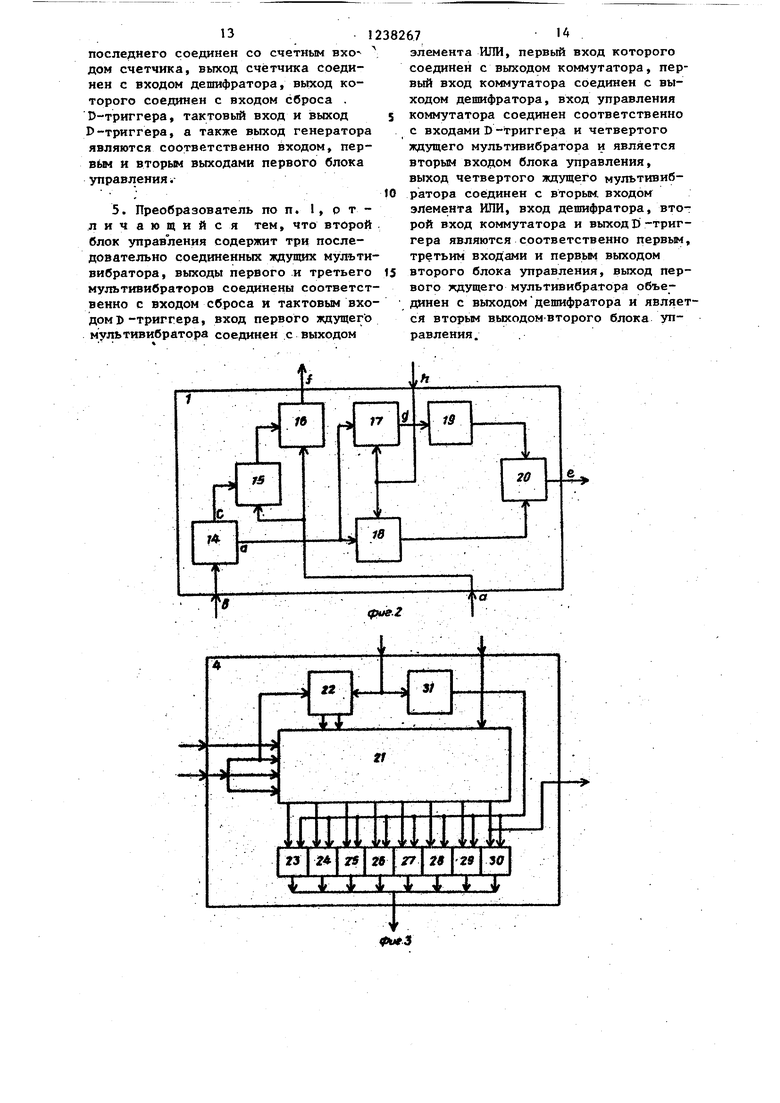

мент И 1.5, первый -триггер 16 , второй)-триггер 17, второй элемент И 18, второй формирователь 19 импульсов и элемент ИЛИ 20. Формирователь 4 сигнала адреса (фиг. З) содержит блок 21 памяти, счетчик 22, элементы И 23-30 и инвертор 31. Матрица блока 21 памяти может быть выполнена в виде набора

D-триггеров, включенных регистром сдвига,

Первый блок 2 управления (фиг. 4) представляет собой генератор, рабо- тающий в старт-стоп режиме, в состав которого могут входить) -триггер 32, генератор 33, счетчик 34 и де- игифратор 35.

Второй блок 10 управления (фиг, 5) представляет собой генератор одиночных импульсов, также работающий в старт-стоп режиме ,и содержит три ждущих мультивибратора 36, 37 и 38, D-триггер 39, элемент ИЛИ 40, коммутатор 41, дешифратор 42 и четвертый ждущий мультивибратор 43.

Блок 5 буферной памяти представляет собой оперативное запоминающее устройство (ОЗУ) малой емкости и высокого быстродействия. Его матрица

может быть выполнена на основе набора параллельных регистров. Запись осуществляется поэлементно вдоль каждой строки, а считьшание происходит построчно.

Блок 8 памяти представляет собой ОЗУ емкостью на полный кадр изображения, полный объем которого с целью повышения быстродействия разбит на несколько каналов 5 при этом выходы каналов через соответствующие выход

т(ые регистры блока 8 объединяются

выходным коммутатором этого блока. Структура блока, 8, блока 5, формирователя А сигнала адреса такова, что число каналов блока 5 буферной памяти равна числу столбцов матрицы бло- 5 ка 5 буферной памяти и равно числу элементов ИЛИ 23-30 формирователя А сигнала адреса.

При рассмотрении работы .преобразователя допустим, что формат кадра О 256x256, блок 8 памяти с целью по- вьшения быстродействия при считьша- нии и сокращении времени записи разделен на восемь каналов.

Преобразователь ТВ стандарта ра- fS ботает следующим образом.

От синхрогенератора выходной развертки на счетный вход и вход/установки третьего счетчика 9 и на второй распределителя 1 временньпс 20 нтервалов поступают импульсы эле- меитов, синхроимпульсы кадров и . строчные гасявдие соответственно. От синхрогенератора входной развертки на первый вход распределителя 1 вре- 25 менных интервалов и на входы сброса первого и второго счетчиков 3, 6 поступают импульсы элементов и синхроимпульсы кадров соответственно.

8процессе преобразования преобразо- ЗО ватель работает s трех режимах: считывания, накопления и записи.

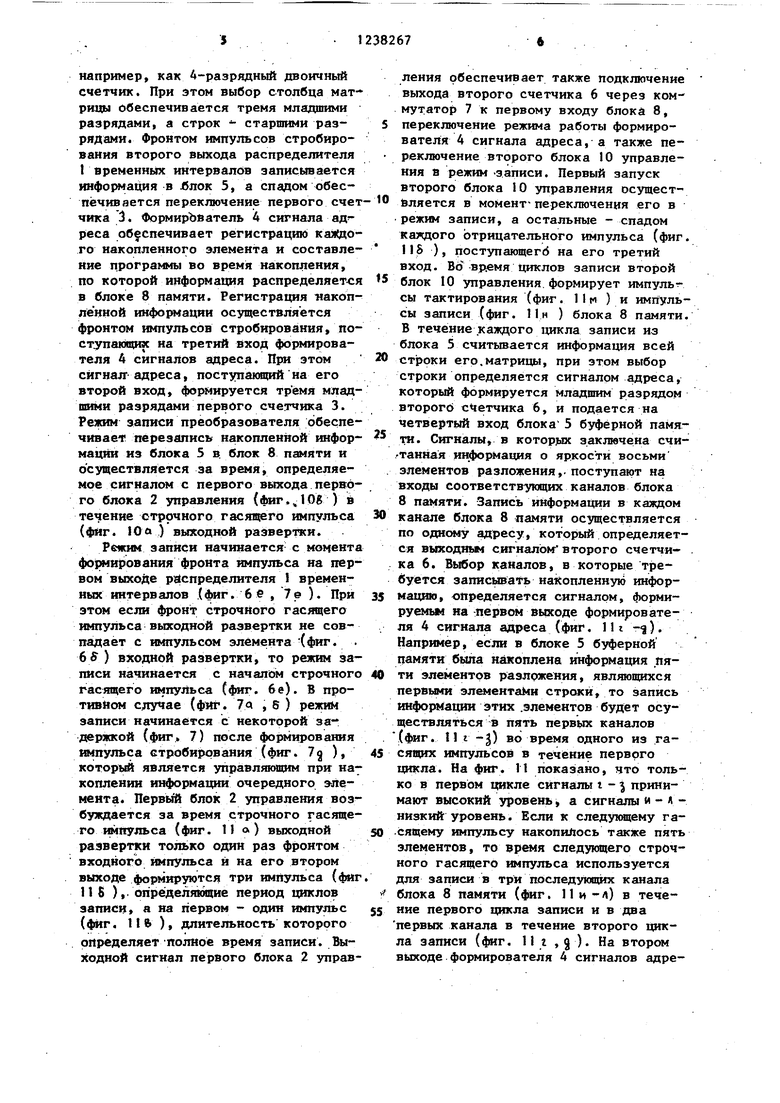

Режим считьгаайия информации с . выхода блока 8 памяти осуществляется в активной части строки выходной ,, развертки (фиг. 9, а- строчный гасящий, ff - импульсы элементов, 6 , н:- пять младших разрядов третьего счетчика 9). Третий счетчик 9 представляет собой 16-разрядный двоичный о счетчик. По считывании он формирует сигналы адреса, из которых тринадцать старших разрядов через коммута- трр 7 подаются на первый вход блока 8 памяти. По одному и тому же адресу 5 одновременно во всех блоках 8 памяти производится считьшание информации, соответствующей восьми смежным эле- мен там. По каждой нулевой кодовой комбинации трех Младших разрядов тре-50 тьего счетчика 9 (фиг. 9& г,) за- дускается второй блок 10 управления, который формирует импульсы тактирования (фиг. 9 3 ) блока 8 основной памяти и импульсы стробирования (фиг. $5

9и ) выходных регистров всех каналов блока 8 памяти. За каждый период импульсов тактирования формируется

цикл считывания, в течение которого во всех каналах-по одному адресу считывается информация, соответствующая восьми смежным элементам и переписывается в выходные регистры. В последующем цикле считывания выходной сигнал с трех младших разрядов третьего счетчика 9 поступает на вход блока 8 памяти, в результате чего происходит поэлементный вывод информации из блока 8 на вход ЦАП 13 и считьгоание новой информации по новому адресу. При такой организации считьшания информация на выходе преобразователя появляется с задержкой на восемь элементов относительно начала считьша- нйя по зад-анному адресу, поэтому третий счетчик 9 формирует сигналы адреса с опережением на восемь элементов относительно строчных гасящих импульсов (фиг. 9d ,Ь -.

Режим накопления заключается в подготовке, информации, соответствующей небольшому числу элементов разложения входной развертки, к записи в блок 8 памяти с помощью блока 5. буферной памяти. Допустим, что его объем позволяет накопить информацию шестнадцати элементов. В этом случае матрица блока 5 буферной памяти состоит из двух строк и восьми столбцов Входной видеосигнал .рри помощи АЦП 12 преобразуется в цифровую форму и подается на второй вход блока 5 буферной памяти. Запись в блок 5 пpoизвot дится после каждого импульса элемен - та разложения входной развертки (фиг. 10 5 ). При этом после фронта каждого импульса элементов (фиг.10S , 65 , 78 , 8S ) на втором выходе распределителя I формируются импульсы стробирования (фиг. 6 , 7j ) В промежутках времени между перезаписью информации из блока 5 в блок В памяти импульсы стробиров.ания формируются синхронно с импульсами элементов. Если же импульс элемента разложения (фиг. 8 &Т поступает на первый вход распределителя 1 временных интервалов в момент, когда на «го третий вход поступает сигнал с первого выхода первого блока 2 управления (фиг. ,3 о ),то до окончания последнего формирование импульса стробиро- ваиия задерживается (фиг. 8«). Сигнал адреса {{ри записи в блок 5 буферной памяти формируется первьм счетчиком 3 фиг .(Юг -ти , выполненньи,

например, как А-разрядный двоичный счетчик. При этом выбор столбца матрицы обеспечивается тремя младшими разрядами, а строк - старшими разрядами. Фронтом импульсов стробиро- вания второго выхода распределителя I временных интервалов записывается информация в Лпок 5, а спадом обеспечивается переключение первого счетчика 3. ФормирЪватель 4 сигнала реса обеспечивает регистрацию каяКяо- го накопленного элемента и составление программы во время накопления, по которой информация распределяется в блоке 8 памяти. Регистрация «акоп- ле нной информации осуществляется фронтом импульсов стробирования, поступающих на третий вход формирователя 4 сигналов адреса. При этом сйгная-адреса, поступающий на его второй вход, формируется тремя млад- щими разрядами первого счетчика 3. Режим записи преобразователя обеспечивает перезапись накопленной информации из блока 5 в. блок 8 памяти и осуществляется за время, определяемое сигналом с первого выхода первого блока 2 управления (фиг.Юв ) в течение строчного гасящего импульса (фиг. Юо ) выходной развертаи.

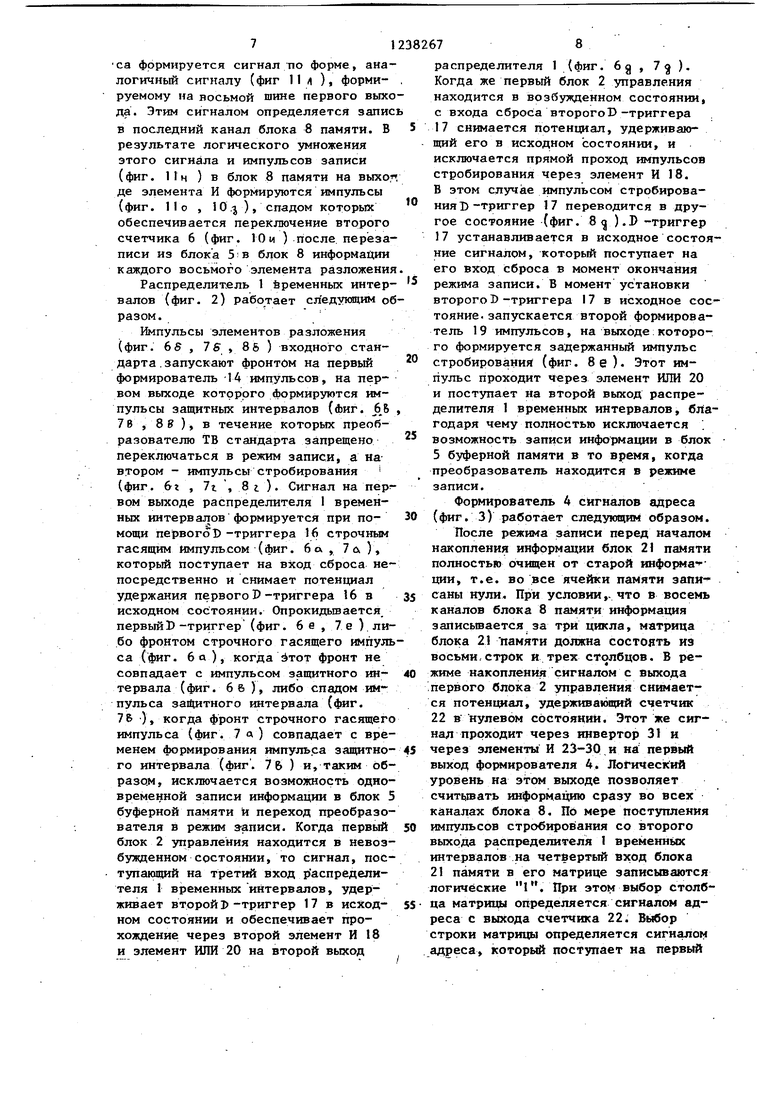

Режим записи начинается- с момента формирования фронта импульса на первом выходе рг(спределителя 1 временных интервалов .(фиг. бе , 7е ). При этом если фронт строчного гасящего импульса выходной развертки не совпадает с импульсом элемента (фиг. . 65 ) входной развертки, то режим записи начинается с началом строчного гасящего импульса (фиг. бе). В противном случае (ф«г. 7а , в ) режим записи начинается с некоторой задержкой (фиг. 7) после формирования кмпупьса стробиррвания (фиг. 7д ), который является управляющим при на коплении информации очередного элемента. ПервШ блок 2 управления возбуждается за время строчного гасящего импульса (фиг. II о) выходной развертки один раз фронтом входного импульса и на его втором выходе формируются три импульса (фиг ПБ ),. опрёделшщие период циклов записи, а на первом - один импульс (фиг. lift ), длительность которого определяет Полное время записи. Вы- ходиой сигнал первого блока 2 управления обеспечивает также подключение выхода второго счетчика 6 через коммутатор 7 к первому входу блока 8, 5 переключение режима работы формирователя 4 сигнала адреса, а также пе- реключение второго блока 10 управления в режим -записи. Первый запуск второго блока 10 управления осущест- йляется в момент-переключения его в режим записи, а остальные - спадом каждого отрицательного импульса (фиг. 118 ), поступающего на его третий вход. Во время циклов записи второй 5 блок 10 управления, формирует ттупь сы Тактирования (фиг. 11м ) и импульсы записи (фиг. Пн ) блока 8 памяти. В течение каждого цикла записи из блока 5 считьгоается информация всей 0 строки его.матрицы, при этом выбор строки определяется сигналом адреса, который формируется младшим разрядом второгб счетчика 6, и подается на четвертый вход блока 5 буферной памя- ти. Сигналы, в которых заключена счи.танна я информация о яркости восьми .элементов разложения,-поступают на

входы соответствующих каналов блока 8 памяти. Запись информации в каждом

0 канале блока 8 памяти осуществляется по ояаону адресу, который определяется выходным сигналом второго счетчи- , ка 6. Выбор каналов, в которые требуется записшать накопленную инфор5 нацию, определяется сигналом, формируемым на :первом выходе формирователя 4 сигнала адреса (фиг. 11г -а). Например, если в блоке 5 буферной памяти была накоплена информация пя0 ти элементов разложения, являющихся первшш элементами строки, то запись информатдаи этих .элементов будет осуществляться в пять первых каналов . (фиг. 1 t -j) во время одного из га5 сящих импульсов в течение первого

цикла. На фиг. М показано, что только в первом цикле сигналы t- принимают высокий уровень, а сигналы и - А- низкий уровень. Если к следующему га0 .сящему импульсу накопилось также пять элементов, то ремя следующего строчного гасящего импульса используется для записи в три последующих канала блока 8 памяти (фиг. 11 и -л) в тече5 нне первого цикла записи и в два первых канала в течение второго цнк- ла записи (фиг. 11 г ,9 ) втором выходе формирователя 4 сигналов адре

ca формируется сигнал /по форме, аналогичный сигналу (фиг 11 л ), форми- руемому на восьмой шине первого выхода. Этим сигналом определяется запис в последний канал блока 8 памяти. В результате логического умножения этого сигнала и импульсов записи (фиг. Пч ) в блок 8 памяти на выхо.п де элемента И формируются импульсы (фиг. 1 I о , 10.), спадом которых обеспечивается переключение второго счетчика 6 (фиг. 10 и ) после перезаписи из блока 5:в блок 8 информации каждого восьмого элемента разложения

Распределитель 1 ёременных интервалов (фиг. 2) работает следующим образом.

Импульсы элементов разложения (фиг. 6S , 76 t 8Ь } входного стандарта . запускают фронтом на первый формирователь 14 импульсов, на первом выходе которого формируются импульсы защитньтх интервалов (фиг. 7В , 8 ), в течение которых преобразователю ТВ стандарта запрещено переключаться в режим записи, а на втором - импульсы стробирования (фиг. 6г , 7г , 8 г. ). Сигнал на пер вом выходе распределителя 1 временных интервалов формируется при помощи первогоD -триггера 16 строчным гасящим импульсом (фиг. 6а , 7й ), который поступает на вход сброса непосредственно и снимает потенциал удержания первогоР-триггера 16 в исходном состоянии. Опрокидьшается, первый)-триггер (фиг. 6 е , 7е ) либо фронтом строчного гасящего импульса (фиг. 6 а ), когда тот фронт ие совпадает с импульсом защитного интервала (фиг. 66 ), либо спадом импульса защитного интервала (фиг. 7 Б ), когда фронт строчного гасящего импульса (фиг. 7 а) совпадает с временем формирования импульса защитно- го интервала (фиг. 76 ) и, таким образом, исключается возможность одновременной записи информации в блок 5 буферной памяти и переход преобразователя в режим З эписи. Когда первый блок 2 управления находится в невозбужденном состоянии, то сигнал, поступающий на третий вход р аспредели- теля 1 временных интервалов, удерживает второй)-триггер 17 в исход- ном состоянии и обеспечивает прохождение через второй элемент И 18 и элемент ИЛИ 20 на второй выход

10

IS

20

25

, ь .

, 4550 55

2382678

распределителя 1 (фиг. 6д , 7 ). Когда же первый блок 2 управления находится в возбужденном состоянии, с входа сброса второгоD-триггера 17 снимается потенциал, удерживающий его в исходном состоянии, и исключается прямой проход импульсой стробирования через элемент И 18. В этом случае импульсом стробирования) -триггер 17 переводится в другое состояние (фиг. 8 ). -триггер 17 устанавливается в исходное состояние сигналом, -который поступает на его вход Сброса в момент окончания режима записи. В момент установки второго D -триггера 17 в исходное состояние, запускается второй формирователь 19 импульсов, на выходе;которого формируется задержанный импульс стробирования (фиг. 8е). Этот импульс проходит Через элемент ИЛИ 20 и поступает на второй выход распределителя 1 временных интервалов, благодаря чему полностью иcкJиoчaeтcя возможность записи информации в блок 5 буферной памяти в то время, когда преобразователь находится в режиме записи.

Формирователь 4 сигналов адреса (фиг. 3) работает следующим образом.

После режима записи перед началом накопления информации блок 21 пшяти полностью очищен от старой информа- ции, т.е. во все ячейки памяти запи саны нули. При условии,- что в восемь каналов блока 8 памяти информация записьшается за три цикла, матрица блока 21 памяти должна состоять из восьми,строк и трех столбцов. В режиме накопления сигналом с выхода первого блока 2 управления снимается потен191ал, удерживающий счетчик 22 в нулевом сОстояииИ. Этот же сигнал проходит через иивертор 31 и через элементы И 23-30,и на первый выход фо ;ширователя 4. Логический уровень иа этом выходе позволяет счит|,гоать информацию сразу во всех каналах блока 8. ПО мере поступления импульсов стробироваиия со второго выхода распределителя I временных интервалов на четвертый вход блока 21 памяти в его матрице записываются

30

35

40

логические 1 . При этом выбор столбца матрицы определяется сигиалом адреса с выхода счетчика 22. Выбор строки матрицы определяется сигналом адреса, который поступает на первый

вход блока 21 памяти, и формируется тремя младшими разрядами первого счетчика 3. В начале заполняется столбец, выходы триггеров которого являются выходами блока 21 памяти. Когда кодовая комбинация на первом входе блока 21 памяти принимает ну- . левое значение, счетчик 22 переключается, что обеспечивает заполнение среднего столбца. После очередного переключения счетчика 22 происходит заполнение последнего столбца. В режиме записи выходной сигнал с первого выхода первого блока 2 управления (фиг. 118 ) поступает на вход счетчика 22 и устанавливает его в нулевое состояние. Выходной сигнал блока 21 памяти проходит через элементы И 23-30. Выходные сигналы со второго

мультивибратора 36. Ждущие мультивибраторы 36, 37 и 38 запускаются поочередно по цепочке, при этом жду- щий мультивибратор 36 формирует сиг5 нал тактирования для блока 8 памяти (фиг. Мм ), а дешифратор 42 - сиг- . нал стробирования выходнбго регистра блока 8 памяти. В момент поступления перепада напряжения с уровня логичесШ кого О в уровень логической 1 (фиг. MR ) на второй вход второго блока 10 управления запускается ждущий мультивибратор 43, выходной сигнал которого проходит через элемент

15 ИЛИ АО и запускает цепочку ждущих мультивибраторов 36, 37 и 38. При этом выходньм сигналом ждущего муль- тргаибратора 38 переводится в противоположное состояние Ь-триггер 39.

выхода первого блока 2 управления Установленный уровень логической М

25

30

поступают на третий вход блока 22 памяти. Спад этих импульсов обеспечивает сдвиг записанной информации в регистрах сдвига и одновременно стирание использованной информации по одному столбцу.

Первый блок 2 управления (фиг. 4) работает следующим образом..

№ пульс, поступающий на вход первого блока 2 управления, переводит D-триггер 32 в. противоположное состояние (фиг. бе, 7е , 116). Выходной Сигнал этого триггера является разрешающим сигналом для запуска генератора 33 и счетчика- 34. При поступлении этого сигнала на вход счетчика 34 он отсчитывает три импульса (фиг. Мб ), после чего выходной .сигнал дешифратора 35 поступает на вход 1 -триггера 32 и устанавливает его В1 40 исходное сЬстояние. Выходной сигнал D-триггера 32 является запрещающим для работы генератора 33, этот же сигнал устанавливает счетчик 34 в исходное состояние.45

Второй блок 10 управления (фиг. 5) работает сле; ;ующим образом.

При поступлении на второй вход блока 10 сигнала, соответствующего уровню логического О, блок 10 на so ходится -в режиме считывания. При поступлении на вход дешифратора 42 3-разрядного цифрового сигнала, ко- довая комбинация которого равна 8, она начинает вырабатьгоать импульсньй 55 сигнал. Эта последовательность импульсов через коммутатор 41, элемент ИЛИ 40 поступает на вход ждущего

на входе блока 10 управления поступает на управляющий вход коммутатора 41 и на вход ждущего мультивибратора 36 через элемент ИЛИ 40 и коммутатор 41 и подключены импульсы, поступающие на третий вход второго блока 10 управления. Эти импульсы запускают цепочку ждущих мультивибраторов 36, 37 и 38. В момент возбуждения звдущего мультивибратора 36 Т) -триггер 39 устанавливается в исходное состояние, а выходным сигна7 лом ждущего мультивибратора 38 -триг гер 39 вновь опрЪкидьшается, т.е. 35 Р-триггер 39 формирует сигнал записи в блок 8 памяти (фиг. 11).

Формула изобретения

1. Преобразователь телевизионного стандарта, содержащий .первый и второй счетчики, входы сброса которых являются входами кадровых синхроимпульсов входной развертки, первый блок управления, первый вход которого соединен с первым входом формирователя сигналов адреса, выходы разрядов второго счетчика соединены с первым входом коммутатора, выход которого соединен с первым входом блока памяти, выход которого соединен с входом цифро-аналогового преобразователя, третий счетчик, счетный вход и вход установки которого являются входами импульсов элементов разложения и кадровых синхроимпульсов выходной развертки соответственно, выходы младших разрядов третьего счетчика

мультивибратора 36. Ждущие мультивибраторы 36, 37 и 38 запускаются поочередно по цепочке, при этом жду- щий мультивибратор 36 формирует сигнал тактирования для блока 8 памяти (фиг. Мм ), а дешифратор 42 - сиг- нал стробирования выходнбго регистра блока 8 памяти. В момент поступления перепада напряжения с уровня логического О в уровень логической 1 (фиг. MR ) на второй вход второго блока 10 управления запускается ждущий мультивибратор 43, выходной сигнал которого проходит через элемент

ИЛИ АО и запускает цепочку ждущих мультивибраторов 36, 37 и 38. При этом выходньм сигналом ждущего муль- тргаибратора 38 переводится в противоположное состояние Ь-триггер 39.

Установленный уровень логической М

на входе блока 10 управления поступает на управляющий вход коммутатора 41 и на вход ждущего мультивибратора 36 через элемент ИЛИ 40 и коммутатор 41 и подключены импульсы, поступающие на третий вход второго блока 10 управления. Эти импульсы запускают цепочку ждущих мультивибраторов 36, 37 и 38. В момент возбуждения звдущего мультивибратора 36 Т) -триггер 39 устанавливается в исходное состояние, а выходным сигна7 лом ждущего мультивибратора 38 -триггер 39 вновь опрЪкидьшается, т.е. Р-триггер 39 формирует сигнал записи в блок 8 памяти (фиг. 11).

Формула изобретения

1. Преобразователь телевизионного стандарта, содержащий .первый и второ счетчики, входы сброса которых являются входами кадровых синхроимпульсов входной развертки, первый блок управления, первый вход которого соединен с первым входом формирователя сигналов адреса, выходы разрядов второго счетчика соединены с первым входом коммутатора, выход которого соединен с первым входом блока памяти, выход которого соединен с входом цифро-аналогового преобразователя, третий счетчик, счетный вход и вход установки которого являются входами импульсов элементов разложения и кадровых синхроимпульсов выходной развертки соответственно, выходы младших разрядов третьего счетчика

n

соединены с первым входом второго блока управления, а. выходы остальных разрядов третьего счетчика - с втр- рым входом коммутатора, вход управления которого соединен с первьм выходом первого блока управления, пер- вь1й и второй выходы второго блока управления соединены соответственно с вторым и третьим, входами блока памяти, .четвертый вход которого соеди - нен с первым вьтходом формирователя сигнала адреса, второй вход формирователя сигнала адреса соединен с выходом первого счетчика, а также апа- лрго-цифровой преобразователь, вход . которого является входом устройства, отлич ающийся тем, что, с целью повышения точности преобра- зования сигнала при произвольных соотношениях и изменении частот входной и выходной разверток, в него введены блок буферной памяти, элемент И и распределитель временных интервалов, первый вход которого является входом импульсов элементов входной развертки, а второй вход - входом строчных гасящих импульсов выходной разв.ертки, первый выход распределителя временных интервалов сое- динен с входом первого блока з равления, а второй выход - со счетным входом первого счетчика, первым входом блока буферной памяти и третьим входом формирователя сигнала адреса,

второй выход которого соединен с 1 ервым входом элемента И, а выход элемента И- - со счетньи входом второго счетчика, второй вход блока буферной памяти соединен с выходов аналоге- цифрового преобразователя, третий вход - с выходом первого счетчика, четвертый-вход - с выходами младших разрядов второго счетчика, а выход блока буферной памяти - с пятым вхо- дом блока памяти, выходы младших разрядов третьего счетчика соединены также с шестым .входом блока памяти, перв ый выход первого блока управления соединен с третьим входом распределителя временных интервалов и вторьм входом второго блока управления, второй выход которого соединен с вторым входом элемента И, второй выход первого блока управления соединен с четвертым входом форми- рователя сигнала адреса и с третьим входом второго блока управления. .

10

25

5 20 -ад 3540 45 50 55

23826712

2.Преобразователь по п. 1, о т - л И: ч а ю щ и и с я тем, что распределитель временных интервалов содержит первый формирователь импуль- сов,, первый выход которого соединен с первым входом первого элемента И,

а выход первого элемента И - с т-акто- вьм входом первогоD-триггера, вход сброса которого соединен с вторьм входом первого элемента И, второй выход первого, формирователя импульсов соединен с первым входом второго элемента И и тактовым входом второго D-триггера, выход которого соединен с входрм вт.орого формирователя импульсов, вьгходы второго элемента И и второго формирователя импульсов соединены с первым и вторым входами элемента ИЛИ соответственно, второй вход второго элемента И соединен с - входом сброса второгоD-триггера, вход первого формирователя импульсов и вторые входы первого и второго элементов И являются cooTBertTBeHHO . первым, вторым и третьим входами распределителя аременных интервалов, выходы первого3 -триггера и элемён TS ИЛИ являются соответственно первым и вторьм выходами распределителя временных интервалов.

3.Преобразователь по п. 1, о т - л и ч а ю (ц и и с Я тем, что формн рователь сигналов адреса содержит . блок, памяти, вхо)ц старшего разряда первого входа которого соединен со счетньм входом с 1етчика, выход счетчика соединен с вгорьм входом блока памяти, а каждагй выход блока памяти соединен с первым входом соответствующего элемента. И, при этом последний выход блока памяти тляется вторьм выходом формирователя сигналов адреса, вход сброса счетчика соединен через швертор с вторыми входами каждого элемента Ни является лервын входом формирователя сигналов адреса, первый, второй,, третий и четвертый входы блока паняти являнхтся со-, ответственно вторым, третьим и чет- вертьм входами, формирователя сигналов адреса, выходы элементов И объединены и являются выходом формир.ова- теля сигнала адреса.

А. Преобразователь по п. 1, о т - И и ч а ю щ и и с я тем, что первый блок управления содержит В-триггер, выход которого соединен с входами сброса счетчика и генератора, выход

13

последнего соединен со счетным вхо дом счетчика, выход счётчика соединен с входом дешифратора, вьпсод которого соединен с входом сброса . D-триггвра, тактовый вход и выход D-триггера, а также выход генератора являются соответственно входом, пер- Btoi и вторым выходами первого блока управления -.

5. Преобразователь по п. 1, о т - лишающийся тем, что второй . блок управления содержит три последовательно соединенных ждущих мультивибратора, выходы первого и третьего мультивибраторов соединены соответственно с входом сброса и тактовым входом -триггера, вход первого ждущегЪ мультивибратора соединен с выходом

/2

L

J LJ LJ U L3 LJ

t3 I 24

1Г1 4 /i J, i 1

t

6714

элемента ИЛИ, первый вход которого соединен с выходом коммутатора, первый вход коммутатора соединен с выходом дешифратора, вход управления коммутатора соединен соответственно с входами D-Триггера и четвертого ждущего мультивибратора и является вторым входом блока управления, выход четвертого ждущего мультивибратора соединен с вторым, входом

элемента ИЛИ, вход дешифратора, втот рой вход коммутатора и выходD-триггера являются соответственно первым, третьим входами и первым выходом

второго блока управления, выход первого ждущего мультивибратора объе- динен с выходом дешифратора и является вторым выходоМ Второго блока управления .

3/

1 г ч

77

29 29

30

/

h

(риг 8

Чюв.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь телевизионных стандартов | 1987 |

|

SU1506591A1 |

| Устройство для преобразования малокадрового телевизионного стандарта | 1985 |

|

SU1256245A1 |

| Устройство для преобразования телевизионного стандарта | 1986 |

|

SU1343562A1 |

| Преобразователь телевизионного стандарта | 1981 |

|

SU1016850A1 |

| Устройство для отображения радиолокационной информации на экране электронно-лучевой трубки | 1989 |

|

SU1691880A1 |

| УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА НЕПОДВИЖНЫХ ИЗОБРАЖЕНИЙ ПО КАНАЛАМ ЭЛЕКТРИЧЕСКОЙ СВЯЗИ | 1990 |

|

RU2007051C1 |

| Устройство для отображения информации на экране цветного видеоконтрольного блока | 1988 |

|

SU1529280A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Устройство для отображения радиолокационной информации на экране электронно-лучевой трубки | 1988 |

|

SU1509985A1 |

| Устройство для измерения координатных искажений фокусирующе-отклоняющей системы и передающей электронно-лучевой трубки | 1989 |

|

SU1660212A1 |

Изобретение относится к телеви- дению и может; использоваться в устройствах сопряжения скорости развертки малокадровых ТВ систем с системами, в которых скорость развертки близка к вещательному стандарту. По- вьпоается точность преобразования сигнала при произвольных соотношениях и изменении частот входной и выходной разверток. Преобразователь ТВ стандарта работает в трех режимах: считьшания, накопления и записи. Во время активной части строки выходной развертки происходит считывание информации КЗ блока памяти (jfJH) 8. Счетчик (СЧ) 9, на который поступа вт импульсы элементов с синхрогенера- тора выходной развертки, формирует коды адреса. Тринадцать старших разрядов кода адреса через коммутатор .7 поступают на ВП 8, а три младших на блок управления 10, который по нулевой кодовой комбинации формирует импульсы тактирования и стробирова- ния для БП 8. Информа хия, соответствующая восьми смежньм элементам, счи- тьюается по одному И тому же адресу из всех БП 8 и по импульсам с трех Младших разрядов СЧ 9 через ЦДЛ 13 поступает на вьпсод. СЧ 9 Формирует сигналы адреса с опережением на восемь элементов относительно строчных гасящих импульсов. Режим -накопления i (Л С to 09 00 О

| Патент США № 4065770, кл | |||

| Питательное приспособление к трепальной машине для лубовых растений | 1923 |

|

SU343A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Патент CPIA № 4057836, кл | |||

| Зажим для канатной тяги | 1919 |

|

SU358A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

Авторы

Даты

1986-06-15—Публикация

1980-10-08—Подача